# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 16                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 768 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                     |

| Data Converters            | A/D 15x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 24-QSOP                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f911-gur |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ~~-                                                                                                                                             |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 22.3.SMBus Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                 |

|    | 22.3.1.Transmitter Vs. Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                 |

|    | 22.3.2.Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |

|    | 22.3.3.Clock Low Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 228                                                                                                                                             |

|    | 22.3.4.SCL Low Timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 228                                                                                                                                             |

|    | 22.3.5.SCL High (SMBus Free) Timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 228                                                                                                                                             |

|    | 22.4.Using the SMBus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                 |

|    | 22.4.1.SMBus Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 230                                                                                                                                             |

|    | 22.4.2.SMB0CN Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                 |

|    | 22.4.3.Hardware Slave Address Recognition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |

|    | 22.4.4.Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                 |

|    | 22.5.SMBus Transfer Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |

|    | 22.5.1.Write Sequence (Master)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                 |

|    | 22.5.2.Read Sequence (Master)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

|    | 22.5.3.Write Sequence (Slave)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                 |

|    | 22.5.4.Read Sequence (Slave)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

| ~~ | 22.6.SMBus Status Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                 |

| 23 | UARTO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                 |

|    | 23.1.Enhanced Baud Rate Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |

|    | 23.2.Operational Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                 |

|    | 23.2.1.8-Bit UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 |

|    | 23.2.2.9-Bit UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 |

|    | 23.3.Multiprocessor Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 250                                                                                                                                             |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                 |

| 24 | . Enhanced Serial Peripheral Interface (SPI0 and SPI1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 255                                                                                                                                             |

| 24 | Enhanced Serial Peripheral Interface (SPI0 and SPI1)<br>24.1.Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>255</b><br>256                                                                                                                               |

| 24 | . Enhanced Serial Peripheral Interface (SPI0 and SPI1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>255</b><br>256                                                                                                                               |

| 24 | Enhanced Serial Peripheral Interface (SPI0 and SPI1)<br>24.1.Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>255</b><br>256<br>256                                                                                                                        |

| 24 | Enhanced Serial Peripheral Interface (SPI0 and SPI1)<br>24.1.Signal Descriptions<br>24.1.1.Master Out, Slave In (MOSI)                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>255</b><br>256<br>256<br>256                                                                                                                 |

| 24 | Enhanced Serial Peripheral Interface (SPI0 and SPI1)<br>24.1.Signal Descriptions<br>24.1.1.Master Out, Slave In (MOSI)<br>24.1.2.Master In, Slave Out (MISO)                                                                                                                                                                                                                                                                                                                                                                                         | <b>255</b><br>256<br>256<br>256<br>256                                                                                                          |

| 24 | Enhanced Serial Peripheral Interface (SPI0 and SPI1)<br>24.1.Signal Descriptions<br>24.1.1.Master Out, Slave In (MOSI)<br>24.1.2.Master In, Slave Out (MISO)<br>24.1.3.Serial Clock (SCK)<br>24.1.4.Slave Select (NSS)                                                                                                                                                                                                                                                                                                                               | <b>255</b><br>256<br>256<br>256<br>256<br>256                                                                                                   |

| 24 | Enhanced Serial Peripheral Interface (SPI0 and SPI1).<br>24.1.Signal Descriptions.<br>24.1.1.Master Out, Slave In (MOSI).<br>24.1.2.Master In, Slave Out (MISO).<br>24.1.3.Serial Clock (SCK).                                                                                                                                                                                                                                                                                                                                                       | <b>255</b><br>256<br>256<br>256<br>256<br>256<br>257                                                                                            |

| 24 | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1).</li> <li>24.1.Signal Descriptions</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                           | 255<br>256<br>256<br>256<br>256<br>256<br>257<br>259                                                                                            |

| 24 | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1).</li> <li>24.1.Signal Descriptions.</li> <li>24.1.1.Master Out, Slave In (MOSI).</li> <li>24.1.2.Master In, Slave Out (MISO).</li> <li>24.1.3.Serial Clock (SCK)</li></ul>                                                                                                                                                                                                                                                                                                             | 255<br>256<br>256<br>256<br>256<br>256<br>257<br>259<br>259                                                                                     |

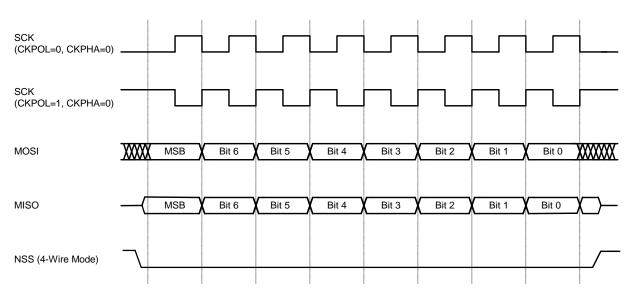

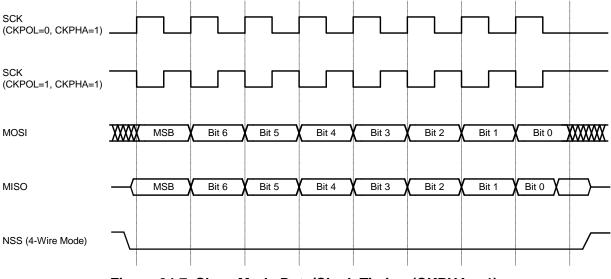

| 24 | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1).</li> <li>24.1.Signal Descriptions.</li> <li>24.1.1.Master Out, Slave In (MOSI).</li> <li>24.1.2.Master In, Slave Out (MISO).</li> <li>24.1.3.Serial Clock (SCK)</li> <li>24.1.4.Slave Select (NSS)</li> <li>24.2.SPI Master Mode Operation .</li> <li>24.3.SPI Slave Mode Operation .</li> <li>24.4.SPI Interrupt Sources .</li> <li>24.5.Serial Clock Phase and Polarity .</li> </ul>                                                                                                | 255<br>256<br>256<br>256<br>256<br>256<br>257<br>259<br>259<br>260                                                                              |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1).</li> <li>24.1.Signal Descriptions.</li> <li>24.1.1.Master Out, Slave In (MOSI).</li> <li>24.1.2.Master In, Slave Out (MISO).</li> <li>24.1.3.Serial Clock (SCK)</li></ul>                                                                                                                                                                                                                                                                                                             | 255<br>256<br>256<br>256<br>256<br>257<br>259<br>259<br>260<br>262                                                                              |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1).</li> <li>24.1.Signal Descriptions.</li> <li>24.1.1.Master Out, Slave In (MOSI).</li> <li>24.1.2.Master In, Slave Out (MISO).</li> <li>24.1.3.Serial Clock (SCK)</li> <li>24.1.4.Slave Select (NSS)</li> <li>24.2.SPI Master Mode Operation.</li> <li>24.3.SPI Slave Mode Operation.</li> <li>24.4.SPI Interrupt Sources.</li> <li>24.5.Serial Clock Phase and Polarity.</li> <li>24.6.SPI Special Function Registers.</li> <li>Timers.</li> </ul>                                     | 255<br>256<br>256<br>256<br>256<br>257<br>259<br>259<br>260<br>262<br>262<br>270                                                                |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1).</li> <li>24.1.Signal Descriptions.</li> <li>24.1.1.Master Out, Slave In (MOSI).</li> <li>24.1.2.Master In, Slave Out (MISO).</li> <li>24.1.3.Serial Clock (SCK).</li> <li>24.1.4.Slave Select (NSS)</li> <li>24.2.SPI Master Mode Operation.</li> <li>24.3.SPI Slave Mode Operation.</li> <li>24.4.SPI Interrupt Sources.</li> <li>24.5.Serial Clock Phase and Polarity.</li> <li>24.6.SPI Special Function Registers.</li> <li>Timers.</li> <li>25.1.Timer 0 and Timer 1.</li> </ul> | 255<br>256<br>256<br>256<br>256<br>257<br>259<br>259<br>260<br>262<br>262<br>270<br>272                                                         |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1).</li> <li>24.1.Signal Descriptions</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                           | 255<br>256<br>256<br>256<br>256<br>257<br>259<br>259<br>259<br>260<br>262<br>260<br>262<br>272<br>272                                           |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 255<br>256<br>256<br>256<br>256<br>257<br>259<br>259<br>260<br>262<br>270<br>272<br>272<br>272                                                  |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 255<br>256<br>256<br>256<br>256<br>257<br>259<br>259<br>260<br>262<br>270<br>272<br>272<br>273<br>273<br>274                                    |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 255<br>256<br>256<br>256<br>257<br>259<br>259<br>260<br>262<br>272<br>272<br>272<br>272<br>273<br>274<br>275                                    |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 255<br>256<br>256<br>256<br>256<br>257<br>259<br>260<br>262<br>270<br>272<br>272<br>272<br>272<br>273<br>274<br>275<br>280                      |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 255<br>256<br>256<br>256<br>256<br>257<br>259<br>259<br>260<br>262<br>270<br>272<br>272<br>273<br>274<br>273<br>274<br>275<br>280<br>280        |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 255<br>256<br>256<br>256<br>257<br>259<br>259<br>260<br>262<br>272<br>272<br>272<br>272<br>273<br>274<br>275<br>280<br>280<br>281               |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0 and SPI1)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 255<br>256<br>256<br>256<br>257<br>259<br>259<br>260<br>262<br>270<br>272<br>272<br>273<br>274<br>273<br>274<br>275<br>280<br>280<br>281<br>282 |

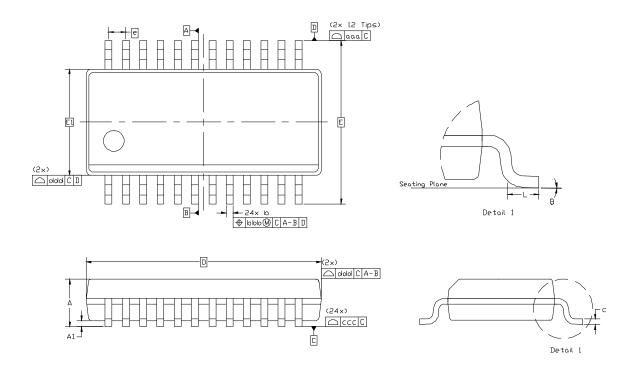

Figure 3.5. QSOP-24 Package Diagram

| Dimension | Min      | Nom      | Max  | ] | Dimension | Min  | Nom       | Ma  |  |

|-----------|----------|----------|------|---|-----------|------|-----------|-----|--|

| А         |          | —        | 1.75 |   | е         |      | 0.635 BSC | •   |  |

| A1        | 0.10     | —        | 0.25 |   | L         | 0.40 | —         | 1.2 |  |

| b         | 0.20     | —        | 0.30 | Ī | θ         | 0°   | _         | 80  |  |

| С         | 0.10     |          | 0.25 | Ī | aaa       |      | 0.20      |     |  |

| D         | 8.65 BSC |          |      | Ī | bbb       |      | 0.18      |     |  |

| E         | 6.00 BSC |          |      | 1 | ссс       |      | 0.10      |     |  |

| E1        |          | 3.90 BSC |      | Ī | ddd       |      | 0.10      |     |  |

Table 3.4. QSOP-24 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- **2.** Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-137, variation AE.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

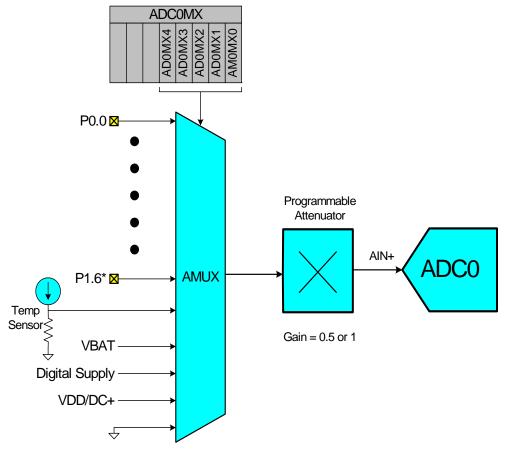

## 5.7. ADC0 Analog Multiplexer

ADC0 on C8051F91x-C8051F90x has an analog multiplexer, referred to as AMUX0.

AMUX0 selects the positive inputs to the single-ended ADC0. Any of the following may be selected as the positive input: Port I/O pins, the on-chip temperature sensor, the VBAT Power Supply, Regulated Digital Supply Voltage (Output of VREG0), VDD/DC+ Supply, or the positive input may be connected to GND. The ADC0 input channels are selected in the ADC0MX register described in SFR Definition 5.12.

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to 0 the corresponding bit in register PnMDIN and disable the digital driver (PnMDOUT = 0 and Port Latch = 1). To force the Crossbar to skip a Port pin, set to 1 the corresponding bit in register PnSKIP. See Section "21. Port Input/Output" on page 205 for more Port I/O configuration details.

## SFR Definition 7.6. CPT1MX: Comparator1 Input Channel Select

| Bit   | 7   | 6    | 5      | 4   | 3          | 2   | 1   | 0   |  |

|-------|-----|------|--------|-----|------------|-----|-----|-----|--|

| Name  |     | CMX1 | N[3:0] |     | CMX1P[3:0] |     |     |     |  |

| Туре  | R/W | R/W  | R/W    | R/W | R/W        | R/W | R/W | R/W |  |

| Reset | 1   | 1    | 1      | 1   | 1          | 1   | 1   | 1   |  |

SFR Page = 0x0; SFR Address = 0x9E

| Bit | Name  | Function                              |                                             |                     |                                   |  |  |  |

|-----|-------|---------------------------------------|---------------------------------------------|---------------------|-----------------------------------|--|--|--|

| 7:4 | CMX1N | Comparator1 Negative Input Selection. |                                             |                     |                                   |  |  |  |

|     |       | Selects the                           | the negative input channel for Comparator1. |                     |                                   |  |  |  |

|     |       | 0000:                                 | P0.1                                        | 1000:               | Reserved                          |  |  |  |

|     |       | 0001:                                 | P0.3                                        | 1001:               | Reserved                          |  |  |  |

|     |       | 0010:                                 | P0.5                                        | 1010:               | Reserved                          |  |  |  |

|     |       | 0011:                                 | P0.7                                        | 1011:               | Reserved                          |  |  |  |

|     |       | 0100:                                 | P1.1                                        | 1100:               | Capacitive Touch Sense<br>Compare |  |  |  |

|     |       | 0101:                                 | P1.3                                        | 1101:               | VDD/DC+ divided by 2              |  |  |  |

|     |       | 0110:                                 | P1.5                                        | 1110:               | Digital Supply Voltage            |  |  |  |

|     |       | 0111:                                 | Reserved                                    | 1111:               | Ground                            |  |  |  |

| 3:0 | CMX1P | Comparat                              | tor1 Positive Input Se                      | election.           |                                   |  |  |  |

|     |       | Selects the                           | e positive input channe                     | el for Comparator1. |                                   |  |  |  |

|     |       | 0000:                                 | P0.0                                        | 1000:               | Reserved                          |  |  |  |

|     |       | 0001:                                 | P0.2                                        | 1001:               | Reserved                          |  |  |  |

|     |       | 0010:                                 | P0.4                                        | 1010:               | Reserved                          |  |  |  |

|     |       | 0011:                                 | P0.6                                        | 1011:               | Reserved                          |  |  |  |

|     |       | 0100:                                 | P1.0                                        | 1100:               | Capacitive Touch Sense<br>Compare |  |  |  |

|     |       | 0101:                                 | P1.2                                        | 1101:               | VDD/DC+ divided by 2              |  |  |  |

|     |       | 0110:                                 | P1.4                                        | 1110:               | VBAT Supply Voltage               |  |  |  |

|     |       | 0111:                                 | P1.6                                        | 1111:               | VDD/DC+ Supply Voltage            |  |  |  |

## **11. Special Function Registers**

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the C8051F91x-C8051F90x's resources and peripherals. The CIP-51 controller core duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the sub-systems unique to the C8051F91x-C8051F90x. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 11.1 and Table 11.2 list the SFRs implemented in the C8051F91x-C8051F90x device family.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g., P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the data sheet, as indicated in Table 11.3, for a detailed description of each register.

| F8 | SPI0CN     | PCA0L         | PCA0H    | PCA0CPL0 | PCA0CPH0 | PCA0CPL4 | PCA0CPH4 | VDM0CN  |

|----|------------|---------------|----------|----------|----------|----------|----------|---------|

| F0 | В          | P0MDIN        | P1MDIN   |          | SMB0ADR  | SMB0ADM  | EIP1     | EIP2    |

| E8 | ADC0CN     | PCA0CPL1      | PCA0CPH1 | PCA0CPL2 | PCA0CPH2 | PCA0CPL3 | PCA0CPH3 | RSTSRC  |

| E0 | ACC        | XBR0          | XBR1     | XBR2     | IT01CF   | FLWR     | EIE1     | EIE2    |

| D8 | PCA0CN     | PCA0MD        | PCA0CPM0 | PCA0CPM1 | PCA0CPM2 | PCA0CPM3 | PCA0CPM4 | PCA0PWM |

| D0 | PSW        | <b>REF0CN</b> | PCA0CPL5 | PCA0CPH5 | P0SKIP   | P1SKIP   |          | POMAT   |

| C8 | TMR2CN     | REG0CN        | TMR2RLL  | TMR2RLH  | TMR2L    | TMR2H    | PCA0CPM5 | P1MAT   |

| C0 | SMB0CN     | SMB0CF        | SMB0DAT  | ADC0GTL  | ADC0GTH  | ADC0LTL  | ADC0LTH  | P0MASK  |

| B8 | IP         | IREF0CN       | ADC0AC   | ADC0MX   | ADC0CF   | ADC0L    | ADC0H    | P1MASK  |

| B0 | SPI1CN     | OSCXCN        | OSCICN   | OSCICL   |          | PMU0CF   | FLSCL    | FLKEY   |

| A8 | IE         | CLKSEL        | EMIOCN   |          | RTC0ADR  | RTC0DAT  | RTC0KEY  |         |

| A0 | P2         | SPI0CFG       | SPI0CKR  | SPI0DAT  | P0MDOUT  | P1MDOUT  | P2MDOUT  | SFRPAGE |

| 98 | SCON0      | SBUF0         | CPT1CN   | CPT0CN   | CPT1MD   | CPT0MD   | CPT1MX   | CPT0MX  |

| 90 | P1         | TMR3CN        | TMR3RLL  | TMR3RLH  | TMR3L    | TMR3H    | DC0CF    | DC0CN   |

| 88 | TCON       | TMOD          | TL0      | TL1      | TH0      | TH1      | CKCON    | PSCTL   |

| 80 | P0         | SP            | DPL      | DPH      | SPI1CFG  | SPI1CKR  | SPI1DAT  | PCON    |

|    | 0(8)       | 1(9)          | 2(A)     | 3(B)     | 4(C)     | 5(D)     | 6(E)     | 7(F)    |

| /h | it addraga | oblo)         |          |          |          |          |          |         |

#### Table 11.1. Special Function Register (SFR) Memory Map (Page 0x0)

(bit addressable)

### Table 11.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved. SFRs highlighted in **blue** are only available on 'F912 and 'F902 devices.

| Register | Address | SFR Page | Description                      | Page |

|----------|---------|----------|----------------------------------|------|

| POMDOUT  | 0xA4    | 0x0      | Port 0 Output Mode Configuration | 219  |

| P0SKIP   | 0xD4    | 0x0      | Port 0 Skip                      | 218  |

| P1       | 0x90    | All      | Port 1 Latch                     | 221  |

| P1DRV    | 0xA5    | 0xF      | Port 1 Drive Strength            | 223  |

| P1MASK   | 0xBF    | 0x0      | Port 1 Mask                      | 216  |

| P1MAT    | 0xCF    | 0x0      | Port 1 Match                     | 216  |

| P1MDIN   | 0xF2    | 0x0      | Port 1 Input Mode Configuration  | 222  |

| P1MDOUT  | 0xA5    | 0x0      | Port 1 Output Mode Configuration | 222  |

| P1SKIP   | 0xD5    | 0x0      | Port 1 Skip                      | 221  |

| P2       | 0xA0    | All      | Port 2 Latch                     | 223  |

| P2DRV    | 0xA6    | 0xF      | Port 2 Drive Strength            | 224  |

| P2MDOUT  | 0xA6    | 0x0      | Port 2 Output Mode Configuration | 224  |

| PCA0CN   | 0xD8    | 0x0      | PCA0 Control                     | 306  |

| PCA0CPH0 | 0xFC    | 0x0      | PCA0 Capture 0 High              | 311  |

| PCA0CPH1 | 0xEA    | 0x0      | PCA0 Capture 1 High              | 311  |

| PCA0CPH2 | 0xEC    | 0x0      | PCA0 Capture 2 High              | 311  |

| PCA0CPH3 | 0xEE    | 0x0      | PCA0 Capture 3 High              | 311  |

| PCA0CPH4 | 0xFE    | 0x0      | PCA0 Capture 4 High              | 311  |

| PCA0CPH5 | 0xD3    | 0x0      | PCA0 Capture 5 High              | 311  |

| PCA0CPL0 | 0xFB    | 0x0      | PCA0 Capture 0 Low               | 311  |

| PCA0CPL1 | 0xE9    | 0x0      | PCA0 Capture 1 Low               | 311  |

| PCA0CPL2 | 0xEB    | 0x0      | PCA0 Capture 2 Low               | 311  |

| PCA0CPL3 | 0xED    | 0x0      | PCA0 Capture 3 Low               | 311  |

| PCA0CPL4 | 0xFD    | 0x0      | PCA0 Capture 4 Low               | 311  |

| PCA0CPL5 | 0xD2    | 0x0      | PCA0 Capture 5 Low               | 311  |

| PCA0CPM0 | 0xDA    | 0x0      | PCA0 Module 0 Mode Register      | 309  |

| PCA0CPM1 | 0xDB    | 0x0      | PCA0 Module 1 Mode Register      | 309  |

| PCA0CPM2 | 0xDC    | 0x0      | PCA0 Module 2 Mode Register      | 309  |

| PCA0CPM3 | 0xDD    | 0x0      | PCA0 Module 3 Mode Register      | 309  |

| PCA0CPM4 | 0xDE    | 0x0      | PCA0 Module 4 Mode Register      | 309  |

| PCA0CPM5 | 0xCE    | 0x0      | PCA0 Module 5 Mode Register      | 309  |

| PCA0H    | 0xFA    | 0x0      | PCA0 Counter High                | 310  |

| PCA0L    | 0xF9    | 0x0      | PCA0 Counter Low                 | 310  |

## **12.3.** Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. If a high priority interrupt preempts a low priority interrupt, the low priority interrupt will finish execution after the high priority interrupt completes. Each interrupt has an associated interrupt priority bit in in the Interrupt Priority and Extended Interrupt Priority registers used to configure its priority level. Low priority is the default.

If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate. See Table 12.1 on page 122 to determine the fixed priority order used to arbitrate between simultaneously recognized interrupts.

### 12.4. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 7 system clock cycles: 1 clock cycle to detect the interrupt, 1 clock cycle to execute a single instruction, and 5 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 19 system clock cycles: 1 clock cycle to detect the interrupt, 5 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 5 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

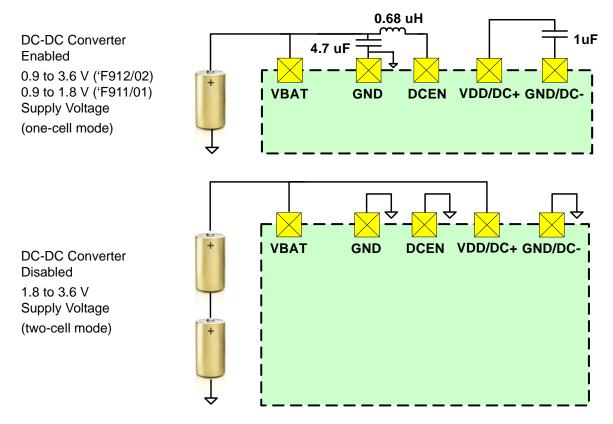

## 16.4. Enabling the DC-DC Converter

On power-on reset, the state of the DCEN pin is sampled to determine if the device will power up in onecell or two-cell mode. In two-cell mode, the dc-dc converter always remains disabled. In one-cell mode, the dc-dc converter remains disabled in Sleep Mode, and enabled in all other power modes. See Section "14. Power Management" on page 143 for complete details on available power modes.

The dc-dc converter is enabled (one-cell mode) in hardware by placing a 0.68  $\mu$ H inductor between DCEN and VBAT. The dc-dc converter is disabled (two-cell mode) by shorting DCEN directly to GND. The DCEN pin should never be left floating. The device can only switch between one-cell and two-cell mode during a power-on reset. See Section "18. Reset Sources" on page 171 for more information regarding reset behavior.

Figure 16.2 shows the two dc-dc converter configuration options.

Figure 16.2. DC-DC Converter Configuration Options

When the dc-dc converter "Enabled" configuration (one-cell mode) is chosen, the following guidelines apply:

- In most cases, the GND/DC- pin should not be externally connected to GND.

- The 0.68 µH inductor should be placed as close as possible to the DCEN pin for maximum efficiency.

- The 4.7 µF capacitor should be placed as close as possible to the inductor.

- The current loop including GND, the 4.7  $\mu$ F capacitor, the 0.68  $\mu$ H inductor and the DCEN pin should be made as short as possible.

- The PCB traces connecting VDD/DC+ to the output capacitor and the output capacitor to GND/DC- should be as short and as thick as possible in order to minimize parasitic inductance.

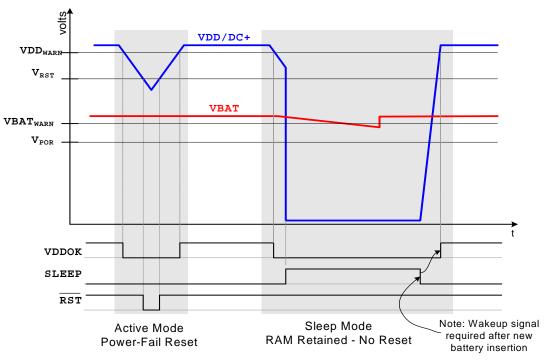

## 18.2. Power-Fail (VDD/DC+ Supply Monitor) Reset

C8051F91x-C8051F90x devices have a VDD/DC+ Supply Monitor that is enabled and selected as a reset source after each power-on or power-fail reset. When enabled and selected as a reset source, <u>any</u> power down transition or power irregularity that causes VDD/DC+ to drop below  $V_{RST}$  will cause the RST pin to be driven low and the CIP-51 will be held in a reset state (see Figure 18.3). When VDD/DC+ returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state.

After a power-fail reset, the PORSF flag reads 1, the contents of RAM invalid, and the VDD/DC+ supply monitor is enabled and selected as a reset source. The enable state of the VDD/DC+ supply monitor and its selection as a reset source is only altered by power-on and power-fail resets. For example, if the VDD/DC+ supply monitor is de-selected as a reset source and disabled by software, then a software reset is performed, the VDD/DC+ supply monitor will remain disabled and de-selected after the reset.

In battery-operated systems, the contents of RAM can be preserved near the end of the battery's usable life if the device is placed in Sleep Mode prior to a power-fail reset occurring. When the device is in Sleep Mode, the power-fail reset is automatically disabled and the contents of RAM are preserved as long as the VBAT supply does not fall below  $V_{POR}$ . A large capacitor can be used to hold the power supply voltage above  $V_{POR}$  while the user is replacing the battery. Upon waking from Sleep mode, the enable and reset source select state of the VDD/DC+ supply monitor are restored to the value last set by the user.

To allow software early notification that a power failure is about to occur, the VDDOK bit is cleared when the VDD/DC+ supply falls below the  $V_{WARN}$  threshold. The VDDOK bit can be configured to generate an interrupt. See Section "12. Interrupt Handler" on page 120 for more details.

**Important Note:** To protect the integrity of Flash contents, **the VDD/DC+ supply monitor must be enabled and selected as a reset source if software contains routines which erase or write Flash memory.** If the VDD/DC+ supply monitor is not enabled, any erase or write performed on Flash memory will cause a Flash Error device reset.

Figure 18.3. Power-Fail Reset Timing Diagram

#### Important Notes:

- The Power-on Reset (POR) delay is not incurred after a VDD/DC+ supply monitor reset. See Section "4. Electrical Characteristics" on page 36 for complete electrical characteristics of the VDD/DC+ monitor.

- Software should take care not to inadvertently disable the V<sub>DD</sub> Monitor as a reset source when writing to RSTSRC to enable other reset sources or to trigger a software reset. All writes to RSTSRC should explicitly set PORSF to 1 to keep the V<sub>DD</sub> Monitor enabled as a reset source.

- The VDD/DC+ supply monitor must be enabled before selecting it as a reset source. Selecting the VDD/DC+ supply monitor as a reset source before it has stabilized may generate a system reset. In systems where this reset would be undesirable, a delay should be introduced between enabling the VDD/DC+ supply monitor and selecting it as a reset source. See Section "4. Electrical Characteristics" on page 36 for minimum VDD/DC+ Supply Monitor turn-on time. No delay should be introduced in systems where software contains routines that erase or write Flash memory. The procedure for enabling the VDD/DC+ supply monitor and selecting it as a reset source is shown below:

- 1. Enable the VDD/DC+ Supply Monitor (VDMEN bit in VDM0CN = 1).

- 2. Wait for the VDD/DC+ Supply Monitor to stabilize (optional).

- 3. Select the VDD/DC+ Supply Monitor as a reset source (PORSF bit in RSTSRC = 1).

## SFR Definition 19.4. OSCXCN: External Oscillator Control

| Bit   | 7       | 6 | 5          | 4   | 3        | 2         | 1   | 0   |  |

|-------|---------|---|------------|-----|----------|-----------|-----|-----|--|

| Name  | XCLKVLD | × | (OSCMD[2:0 | )]  | Reserved | XFCN[2:0] |     |     |  |

| Туре  | R       | R | R/W        | R/W | R/W      | R/W       | R/W | R/W |  |

| Reset | 0       | 0 | 0          | 0   | 0        | 0         | 0   | 0   |  |

SFR Page = 0x0; SFR Address = 0xB1

| Bit | Name     | Function                                                                                                                                                                                                          |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | XCLKVLD  | External Oscillator Valid Flag.                                                                                                                                                                                   |

|     |          | Provides External Oscillator status and is valid at all times for all modes of operation except External CMOS Clock Mode and External CMOS Clock Mode with divide by 2. In these modes, XCLKVLD always returns 0. |

|     |          | <ul><li>0: External Oscillator is unused or not yet stable.</li><li>1: External Oscillator is running and stable.</li></ul>                                                                                       |

| 6:4 | XOSCMD   | External Oscillator Mode Bits.                                                                                                                                                                                    |

|     |          | Configures the external oscillator circuit to the selected mode.                                                                                                                                                  |

|     |          | 00x: External Oscillator circuit disabled.                                                                                                                                                                        |

|     |          | 010: External CMOS Clock Mode.                                                                                                                                                                                    |

|     |          | 011: External CMOS Clock Mode with divide by 2 stage.                                                                                                                                                             |

|     |          | 100: RC Oscillator Mode.                                                                                                                                                                                          |

|     |          | 101: Capacitor Oscillator Mode.                                                                                                                                                                                   |

|     |          | 110: Crystal Oscillator Mode.                                                                                                                                                                                     |

|     |          | 111: Crystal Oscillator Mode with divide by 2 stage.                                                                                                                                                              |

| 3   | Reserved | Reserved.                                                                                                                                                                                                         |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                         |

| 2:0 | XFCN     | External Oscillator Frequency Control Bits.                                                                                                                                                                       |

|     |          | Controls the external oscillator bias current.                                                                                                                                                                    |

|     |          | 000-111: See Table 19.1 on page 181 (Crystal Mode) or Table 19.2 on page 182 (RC or C Mode) for recommended settings.                                                                                             |

| Bit     | Set by Hardware When:                                                                                                                                                                                                                                                                                           | Cleared by Hardware When:                                                                                                                  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| MASTER  | • A START is generated.                                                                                                                                                                                                                                                                                         | <ul><li>A STOP is generated.</li><li>Arbitration is lost.</li></ul>                                                                        |

| TXMODE  | <ul> <li>START is generated.</li> <li>SMB0DAT is written before the start of an SMBus frame.</li> </ul>                                                                                                                                                                                                         | <ul> <li>A START is detected.</li> <li>Arbitration is lost.</li> <li>SMB0DAT is not written before the start of an SMBus frame.</li> </ul> |

| STA     | <ul> <li>A START followed by an address byte is received.</li> </ul>                                                                                                                                                                                                                                            | Must be cleared by software.                                                                                                               |

| STO     | <ul><li>A STOP is detected while addressed as a slave.</li><li>Arbitration is lost due to a detected STOP.</li></ul>                                                                                                                                                                                            | <ul> <li>A pending STOP is generated.</li> </ul>                                                                                           |

| ACKRQ   | <ul> <li>A byte has been received and an ACK<br/>response value is needed (only when hard-<br/>ware ACK is not enabled).</li> </ul>                                                                                                                                                                             | After each ACK cycle.                                                                                                                      |

| ARBLOST | <ul> <li>A repeated START is detected as a MASTER<br/>when STA is low (unwanted repeated START).</li> <li>SCL is sensed low while attempting to gener-<br/>ate a STOP or repeated START condition.</li> <li>SDA is sensed low while transmitting a 1<br/>(excluding ACK bits).</li> </ul>                       | • Each time SI is cleared.                                                                                                                 |

| ACK     | The incoming ACK value is low     (ACKNOWLEDGE).                                                                                                                                                                                                                                                                | • The incoming ACK value is high (NOT ACKNOWLEDGE).                                                                                        |

| SI      | <ul> <li>A START has been generated.</li> <li>Lost arbitration.</li> <li>A byte has been transmitted and an<br/>ACK/NACK received.</li> <li>A byte has been received.</li> <li>A START or repeated START followed by a<br/>slave address + R/W has been received.</li> <li>A STOP has been received.</li> </ul> | • Must be cleared by software.                                                                                                             |

Table 22.3. Sources for Hardware Changes to SMB0CN

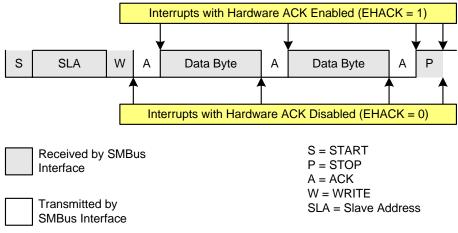

#### 22.5.3. Write Sequence (Slave)

During a write sequence, an SMBus master writes data to a slave device. The slave in this transfer will be a receiver during the address byte, and a receiver during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode when a START followed by a slave address and direction bit (WRITE in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are received.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

The interface exits Slave Receiver Mode after receiving a STOP. Note that the interface will switch to Slave Transmitter Mode if SMB0DAT is written while an active Slave Receiver. Figure 22.7 shows a typical slave write sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 22.7. Typical Slave Write Sequence

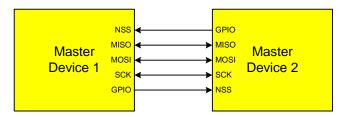

Figure 24.2. Multiple-Master Mode Connection Diagram

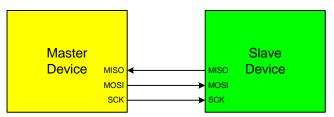

Figure 24.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram

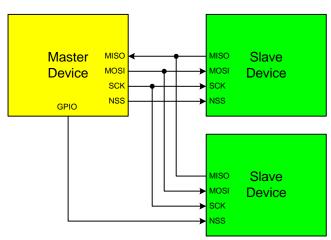

Figure 24.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diagram

## C8051F91x-C8051F90x

| Parameter                 | Description                                                                  | Min                          | Max                     | Units |

|---------------------------|------------------------------------------------------------------------------|------------------------------|-------------------------|-------|

| Master Mode               | <b>Timing</b> <sup>*</sup> (See Figure 24.8 and Figure 24.9)                 |                              |                         | L     |

| т <sub>мскн</sub>         | SCK High Time                                                                | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>MCKL</sub>         | SCK Low Time                                                                 | 1 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>MIS</sub>          | MISO Valid to SCK Shift Edge                                                 | 1 x T <sub>SYSCLK</sub> + 20 | _                       | ns    |

| т <sub>мін</sub>          | SCK Shift Edge to MISO Change                                                | 0                            | _                       | ns    |

| Slave Mode 1              | <b>Fiming</b> <sup>*</sup> (See Figure 24.10 and Figure 24.11)               |                              | L                       | 1     |

| T <sub>SE</sub>           | NSS Falling to First SCK Edge                                                | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SD</sub>           | Last SCK Edge to NSS Rising                                                  | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SEZ</sub>          | NSS Falling to MISO Valid                                                    | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SDZ</sub>          | NSS Rising to MISO High-Z                                                    | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| т <sub>скн</sub>          | SCK High Time                                                                | 5 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>CKL</sub>          | SCK Low Time                                                                 | 5 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>SIS</sub>          | MOSI Valid to SCK Sample Edge                                                | 2 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>SIH</sub>          | SCK Sample Edge to MOSI Change                                               | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| Т <sub>SOH</sub>          | SCK Shift Edge to MISO Change                                                | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SLH</sub>          | Last SCK Edge to MISO Change<br>(CKPHA = 1 ONLY)                             | 6 x T <sub>SYSCLK</sub>      | 8 x T <sub>SYSCLK</sub> | ns    |

| *Note: T <sub>SYSCL</sub> | $_{\rm K}$ is equal to one period of the device system clock (S <sup>V</sup> | YSCLK).                      | 1                       | 1     |

Table 24.1. SPI Slave Timing Parameters

## SFR Definition 25.8. TMR2CN: Timer 2 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1           | 0 |

|-------|------|------|--------|--------|---------|-----|-------------|---|

| Name  | TF2H | TF2L | TF2LEN | TF2CEN | T2SPLIT | TR2 | T2XCLK[1:0] |   |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R/W         |   |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0           | 0 |

#### SFR Page = 0x0; SFR Address = 0xC8; Bit-Addressable

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF2H        | Timer 2 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |             | Set by hardware when the Timer 2 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 2 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                                                                                  |

| 6   | TF2L        | Timer 2 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |             | Set by hardware when the Timer 2 low byte overflows from 0xFF to 0x00. TF2L will be set when the low byte overflows regardless of the Timer 2 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5   | TF2LEN      | Timer 2 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |             | When set to 1, this bit enables Timer 2 Low Byte interrupts. If Timer 2 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 2 over-flows.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |