Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                               |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 16KB (16K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 768 × 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                       |

| Data Converters            | A/D 15x10/12b                                                     |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-WFQFN Exposed Pad                                              |

| Supplier Device Package    | 24-QFN (4x4)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f912-d-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.3. Serial Ports

The C8051F91x-C8051F90x Family includes an SMBus/I<sup>2</sup>C interface, a full-duplex UART with enhanced baud rate configuration, and two Enhanced SPI interfaces. Each of the serial buses is fully implemented in hardware and makes extensive use of the CIP-51's interrupts, thus requiring very little CPU intervention.

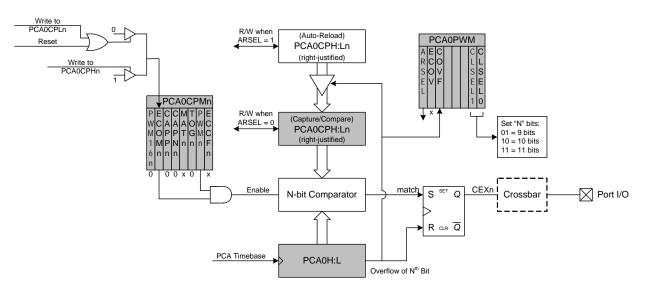

### 1.4. Programmable Counter Array

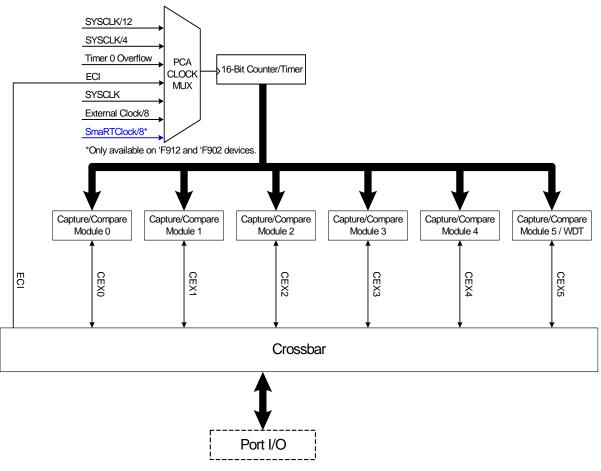

An on-chip Programmable Counter/Timer Array (PCA) is included in addition to the four 16-bit general purpose counter/timers. The PCA consists of a dedicated 16-bit counter/timer time base with six programmable capture/compare modules. The PCA clock is derived from one of six sources: the system clock divided by 12, the system clock divided by 4, Timer 0 overflows, an External Clock Input (ECI), the system clock, or the external oscillator clock source divided by 8. 'F912 and 'F902 devices also support a SmaRTClock divided by 8 clock source.

Each capture/compare module can be configured to operate in a variety of modes: edge-triggered capture, software timer, high-speed output, pulse width modulator (8, 9, 10, 11, or 16-bit), or frequency output. Additionally, Capture/Compare Module 5 offers watchdog timer (WDT) capabilities. Following a system reset, Module 5 is configured and enabled in WDT mode. The PCA Capture/Compare Module I/O and External Clock Input may be routed to Port I/O via the Digital Crossbar.

Figure 1.6. PCA Block Diagram

\*Note: Signal only available on 'F912 and 'F902 devices.

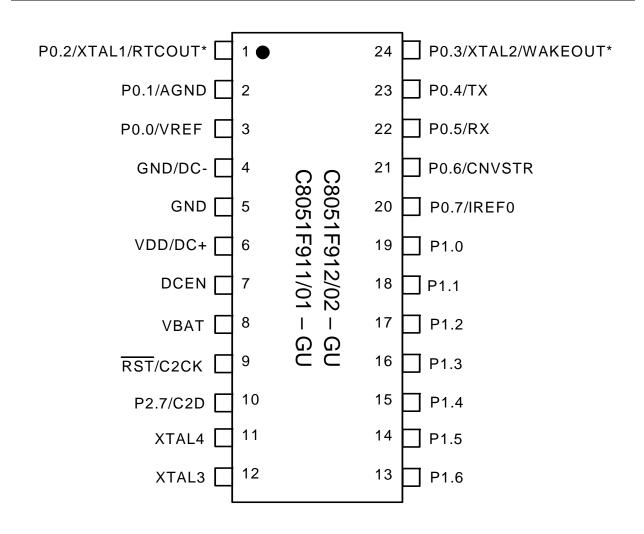

Figure 3.2. QSOP-24 Pinout Diagram F912 (Top View)

#### **Table 4.5. Power Management Electrical Specifications**

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                 | Conditions           | Min | Тур | Max | Units   |

|---------------------------|----------------------|-----|-----|-----|---------|

| Idle Mode Wake-up Time    |                      | 2   | —   | 3   | SYSCLKs |

| Suspend Mode Wake-up Time | Low power oscillator | —   | 400 |     | ns      |

|                           | Precision oscillator | —   | 400 | —   | ns      |

| Sleep Mode Wake-up Time   | Two-cell mode        | _   | 2   | —   | μs      |

|                           | One-cell mode        | —   | 10  | _   | μs      |

#### Table 4.6. Flash Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                                                                       | Conditions  | Min    | Тур  | Max | Units                 |  |  |

|---------------------------------------------------------------------------------|-------------|--------|------|-----|-----------------------|--|--|

| Flash Size                                                                      | C8051F912/1 | 16384* | —    | —   | bytes                 |  |  |

|                                                                                 | C8051F902/1 | 8192   | —    | —   | bytes                 |  |  |

| Scratchpad Size                                                                 |             | 512    | —    | 512 | bytes                 |  |  |

| Endurance                                                                       |             | 1 k    | 90 k | _   | Erase/Write<br>Cycles |  |  |

| Erase Cycle Time                                                                |             | 28     | 32   | 36  | ms                    |  |  |

| Write Cycle Time                                                                |             | 57     | 64   | 71  | μs                    |  |  |

| *Note: On 16 kB devices, 1024 bytes at addresses 0x3C00 to 0x3FFF are reserved. |             |        |      |     |                       |  |  |

#### **Table 4.7. Internal Precision Oscillator Electrical Characteristics**

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified; Using factory-calibrated settings.

| Parameter                                                                           | Conditions                                    | Min | Тур  | Max | Units |  |  |

|-------------------------------------------------------------------------------------|-----------------------------------------------|-----|------|-----|-------|--|--|

| Oscillator Frequency                                                                | –40 to +85 °C,<br>V <sub>DD</sub> = 1.8–3.6 V | 24  | 24.5 | 25  | MHz   |  |  |

| Oscillator Supply Current<br>(from VDD)25 °C; includes bias current<br>of 90–100 µA |                                               | _   | 300* | _   | μΑ    |  |  |

| *Note: Does not include clock divider or clock tree supply current.                 |                                               |     |      |     |       |  |  |

#### Table 4.8. Internal Low-Power Oscillator Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified; Using factory-calibrated settings.

| Parameter                                                           | Conditions                                     | Min | Тур  | Max | Units |  |

|---------------------------------------------------------------------|------------------------------------------------|-----|------|-----|-------|--|

| Oscillator Frequency                                                | –40 to +85 °C,<br>V <sub>DD</sub> = 1.8–3.6 V  | 18  | 20   | 22  | MHz   |  |

| Oscillator Supply Current<br>(from V <sub>DD</sub> )                | 25 °C<br>No separate bias current<br>required. | _   | 100* | _   | μΑ    |  |

| *Note: Does not include clock divider or clock tree supply current. |                                                |     |      |     |       |  |

# C8051F91x-C8051F90x

# SFR Definition 5.13. TOFFH: ADC0 Data Word High Byte

| Bit   | 7         | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |

|-------|-----------|--------|--------|--------|--------|--------|--------|--------|--|

| Name  | TOFF[9:2] |        |        |        |        |        |        |        |  |

| Туре  | R         | R      | R      | R      | R      | R      | R      | R      |  |

| Reset | Varies    | Varies | Varies | Varies | Varies | Varies | Varies | Varies |  |

SFR Page = 0xF; SFR Address = 0x86

| Bit | Name      | Function                                                                   |

|-----|-----------|----------------------------------------------------------------------------|

| 7:0 | TOFF[9:2] | Temperature Sensor Offset High Bits.                                       |

|     |           | Most Significant Bits of the 10-bit temperature sensor offset measurement. |

## SFR Definition 5.14. TOFFL: ADC0 Data Word Low Byte

| Bit   | 7         | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------|--------|---|---|---|---|---|---|

| Name  | TOFF[1:0] |        |   |   |   |   |   |   |

| Туре  | R         | R      |   |   |   |   |   |   |

| Reset | Varies    | Varies | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0xF; SFR Address = 0x85

| Bit | Name      | Function                                                                    |

|-----|-----------|-----------------------------------------------------------------------------|

| 7:6 | TOFF[1:0] | Temperature Sensor Offset Low Bits.                                         |

|     |           | Least Significant Bits of the 10-bit temperature sensor offset measurement. |

| 5:0 | Unused    | Unused.                                                                     |

|     |           | Read = 0; Write = Don't Care.                                               |

# 6. Programmable Current Reference (IREF0)

C8051F91x-C8051F90x devices include an on-chip programmable current reference (source or sink) with two output current settings: Low Power Mode and High Current Mode. The maximum current output in Low Power Mode is 63  $\mu$ A (1  $\mu$ A steps) and the maximum current output in High Current Mode is 504  $\mu$ A (8  $\mu$ A steps).

The current source/sink is controlled though the IREF0CN special function register. It is enabled by setting the desired output current to a non-zero value. It is disabled by writing 0x00 to IREF0CN. The port I/O pin associated with ISRC0 should be configured as an analog input and skipped in the Crossbar. See Section "21. Port Input/Output" on page 205 for more details.

## SFR Definition 6.1. IREF0CN: Current Reference Control

| Bit   | 7    | 6    | 5        | 4   | 3 | 2 | 1 | 0 |  |  |

|-------|------|------|----------|-----|---|---|---|---|--|--|

| Name  | SINK | MODE | IREFODAT |     |   |   |   |   |  |  |

| Туре  | R/W  | R/W  |          | R/W |   |   |   |   |  |  |

| Reset | 0    | 0    | 0        | 0   | 0 | 0 | 0 | 0 |  |  |

#### SFR Page = 0x0; SFR Address = 0xB9

| Bit | Name          | Function                                                                                                                                                                                           |

|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SINK          | IREF0 Current Sink Enable.                                                                                                                                                                         |

|     |               | Selects if IREF0 is a current source or a current sink.                                                                                                                                            |

|     |               | 0: IREF0 is a current source.                                                                                                                                                                      |

|     |               | 1: IREF0 is a current sink.                                                                                                                                                                        |

| 6   | MDSEL         | IREF0 Output Mode Select.                                                                                                                                                                          |

|     |               | Selects Low Power or High Current Mode.                                                                                                                                                            |

|     |               | 0: Low Power Mode is selected (step size = 1 $\mu$ A).                                                                                                                                             |

|     |               | 1: High Current Mode is selected (step size = 8 $\mu$ A).                                                                                                                                          |

| 5:0 | IREF0DAT[5:0] | IREF0 Data Word.                                                                                                                                                                                   |

|     |               | Specifies the number of steps required to achieve the desired output current.<br>Output current = direction x step size x IREF0DAT.<br>IREF0 is in a low power state when IREF0DAT is set to 0x00. |

#### 6.1. PWM Enhanced Mode

On 'F912 and 'F902 devices, the precision of the current reference can be increased by fine tuning the IREF0 output using a PWM signal generated by the PCA. This mode allows the IREF0DAT bits to perform a course adjustment on the IREF0 output. Any available PCA channel can perform a fine adjustment on the IREF0 output. When enabled (PWMEN = 1), the CEX signal selected using the PWMSS bit field is internally routed to IREF0 to control the on time of a current source having the weight of 2 LSBs. With the two least significant bits of IREF0DAT set to 00b, applying a 100% duty cycle on the CEX signal will be equivalent to setting the two LSBs of IREF0DAT to 10b. PWM enhanced mode is enabled and setup using the IREF0CF register.

| Mnemonic           | Description                                | Bytes | Clock<br>Cycles |  |

|--------------------|--------------------------------------------|-------|-----------------|--|

| CLR A              | Clear A                                    | 1     | 1               |  |

| CPL A              | Complement A                               | 1     | 1               |  |

| RL A               | Rotate A left                              | 1     | 1               |  |

| RLC A              | Rotate A left through Carry                | 1     | 1               |  |

| RR A               | Rotate A right                             | 1     | 1               |  |

| RRC A              | Rotate A right through Carry               | 1     | 1               |  |

| SWAP A             | Swap nibbles of A                          | 1     | 1               |  |

|                    | Data Transfer                              |       |                 |  |

| MOV A, Rn          | Move Register to A                         | 1     | 1               |  |

| MOV A, direct      | Move direct byte to A                      | 2     | 2               |  |

| MOV A, @Ri         | Move indirect RAM to A                     | 1     | 2               |  |

| MOV A, #data       | Move immediate to A                        | 2     | 2               |  |

| MOV Rn, A          | Move A to Register                         | 1     | 1               |  |

| MOV Rn, direct     | Move direct byte to Register               | 2     | 2               |  |

| MOV Rn, #data      | Move immediate to Register                 | 2     | 2               |  |

| MOV direct, A      | Move A to direct byte                      | 2     | 2               |  |

| MOV direct, Rn     | Move Register to direct byte               | 2     | 2               |  |

| MOV direct, direct | Move direct byte to direct byte            | 3     | 3               |  |

| MOV direct, @Ri    | Move indirect RAM to direct byte           | 2     | 2               |  |

| MOV direct, #data  | Move immediate to direct byte              | 3     | 3               |  |

| MOV @Ri, A         | Move A to indirect RAM                     | 1     | 2               |  |

| MOV @Ri, direct    | Move direct byte to indirect RAM           | 2     | 2               |  |

| MOV @Ri, #data     | Move immediate to indirect RAM             | 2     | 2               |  |

| MOV DPTR, #data16  | Load DPTR with 16-bit constant             | 3     | 3               |  |

| MOVC A, @A+DPTR    | Move code byte relative DPTR to A          | 1     | 3               |  |

| MOVC A, @A+PC      | Move code byte relative PC to A            | 1     | 3               |  |

| MOVX A, @Ri        | Move external data (8-bit address) to A    | 1     | 3               |  |

| MOVX @Ri, A        | Move A to external data (8-bit address)    | 1     | 3               |  |

| MOVX A, @DPTR      | Move external data (16-bit address) to A   | 1     | 3               |  |

| MOVX @DPTR, A      | Move A to external data (16-bit address)   | 1     | 3               |  |

| PUSH direct        | Push direct byte onto stack                | 2     | 2               |  |

| POP direct         | Pop direct byte from stack                 | 2     | 2               |  |

| XCH A, Rn          | Exchange Register with A                   | 1     | 1               |  |

| XCH A, direct      | Exchange direct byte with A                | 2     | 2               |  |

| XCH A, @Ri         | Exchange indirect RAM with A               | 1     | 2               |  |

| XCHD A, @Ri        | Exchange low nibble of indirect RAM with A | 1     | 2               |  |

|                    | Boolean Manipulation                       | I     | I               |  |

| CLR C              | Clear Carry                                | 1     | 1               |  |

| CLR bit            | Clear direct bit                           | 2     | 2               |  |

| SETB C             | Set Carry                                  | 1     | 1               |  |

| SETB bit           | Set direct bit                             | 2     | 2               |  |

| CPL C              | Complement Carry                           | 1     | 1               |  |

| CPL bit            | Complement direct bit                      | 2     | 2               |  |

| ANL C, bit         | AND direct bit to Carry                    | 2     | 2               |  |

# Table 8.1. CIP-51 Instruction Set Summary (Continued)

# 9. Memory Organization

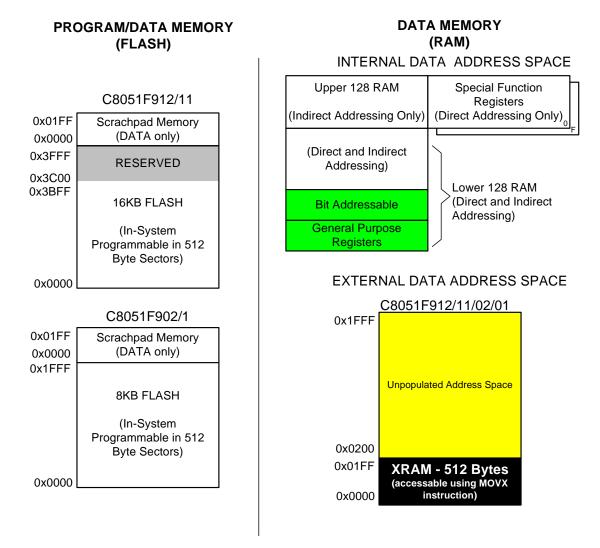

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The memory organization of the C8051F91x-C8051F90x device family is shown in Figure 9.1

Note: Code compatible devices with up to 64 kB Flash and 4 kB RAM are available as the C8051F93x-92x family.

#### Figure 9.1. C8051F91x-C8051F90x Memory Map

### Table 11.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved. SFRs highlighted in **blue** are only available on 'F912 and 'F902 devices.

| Register | Address | SFR Page | Description                 | Page |

|----------|---------|----------|-----------------------------|------|

| TL0      | 0x8A    | 0x0      | Timer/Counter 0 Low         | 278  |

| TL1      | 0x8B    | 0x0      | Timer/Counter 1 Low         | 278  |

| TMOD     | 0x89    | 0x0      | Timer/Counter Mode          | 277  |

| TMR2CN   | 0xC8    | 0x0      | Timer/Counter 2 Control     | 283  |

| TMR2H    | 0xCD    | 0x0      | Timer/Counter 2 High        | 285  |

| TMR2L    | 0xCC    | 0x0      | Timer/Counter 2 Low         | 285  |

| TMR2RLH  | 0xCB    | 0x0      | Timer/Counter 2 Reload High | 284  |

| TMR2RLL  | 0xCA    | 0x0      | Timer/Counter 2 Reload Low  | 284  |

| TMR3CN   | 0x91    | 0x0      | Timer/Counter 3 Control     | 289  |

| TMR3H    | 0x95    | 0x0      | Timer/Counter 3 High        | 291  |

| TMR3L    | 0x94    | 0x0      | Timer/Counter 3 Low         | 291  |

| TMR3RLH  | 0x93    | 0x0      | Timer/Counter 3 Reload High | 290  |

| TMR3RLL  | 0x92    | 0x0      | Timer/Counter 3 Reload Low  | 290  |

| TOFFH    | 0x86    | 0xF      | Temperature Offset High     | 82   |

| TOFFL    | 0x85    | 0xF      | Temperature Offset Low      | 82   |

| VDM0CN   | 0xFF    | 0x0      | VDD Monitor Control         | 175  |

| XBR0     | 0xE1    | 0x0      | Port I/O Crossbar Control 0 | 212  |

| XBR1     | 0xE2    | 0x0      | Port I/O Crossbar Control 1 | 213  |

| XBR2     | 0xE3    | 0x0      | Port I/O Crossbar Control 2 | 214  |

## 12.5. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described in the following register descriptions. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

## 14.7. Determining the Event that Caused the Last Wakeup

When waking from idle mode, the CPU will vector to the interrupt which caused it to wake up. When waking from stop mode, the RSTSRC register may be read to determine the cause of the last reset.

Upon exit from suspend or sleep mode, the wake-up flags in the PMU0CF register can be read to determine the event which caused the device to wake up. After waking up, the wake-up flags will continue to be updated if any of the wake-up events occur. Wake-up flags are always updated, even if they are not enabled as wake-up sources.

All wake-up flags enabled as wake-up sources in PMU0CF must be cleared before the device can enter suspend or sleep mode. After clearing the wake-up flags, each of the enabled wake-up events should be checked in the individual peripherals to ensure that a wake-up event did not occur while the wake-up flags were being cleared.

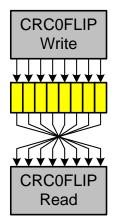

### 15.5. CRC0 Bit Reverse Feature

CRC0 includes hardware to reverse the bit order of each bit in a byte as shown in Figure 15.2. Each byte of data written to CRC0FLIP is read back bit reversed. For example, if 0xC0 is written to CRC0FLIP, the data read back is 0x03. Bit reversal is a useful mathematical function used in algorithms such as the FFT.

Figure 15.2. Bit Reverse Register

## SFR Definition 15.6. CRC0FLIP: CRC0 Bit Flip

| Bit   | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------------|---|---|---|---|---|---|---|

| Name  | CRC0FLIP[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W           |   |   |   |   |   |   |   |

| Reset | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0xF; SFR Address = 0x95

| Bit | Name          | Function                                                                                                              |

|-----|---------------|-----------------------------------------------------------------------------------------------------------------------|

| 7:0 | CRC0FLIP[7:0] | CRC0 Bit Flip.                                                                                                        |

|     |               | Any byte written to CRC0FLIP is read back in a bit-reversed order, i.e. the written LSB becomes the MSB. For example: |

|     |               | If 0xC0 is written to CRC0FLIP, the data read back will be 0x03.                                                      |

|     |               | If 0x05 is written to CRC0FLIP, the data read back will be 0xA0.                                                      |

# 16.2. High Power Applications

The dc-dc converter is designed to provide the system with 65 mW of output power, however, it can safely provide up to 100 mW of output power without any risk of damage to the device. For high power applications, the system should be carefully designed to prevent unwanted VBAT and VDD/DC+ Supply Monitor resets, which are more likely to occur when the dc-dc converter output power exceeds 65mW. In addition, output power above 65 mW causes the dc-dc converter to have relaxed output regulation, high output ripple and more analog noise. At high output power, an inductor with low DC resistance should be chosen in order to minimize power loss and maximize efficiency.

The combination of high output power and low input voltage will result in very high peak and average inductor currents. If the power supply has a high internal resistance, the transient voltage on the VBAT terminal could drop below 0.9 V and trigger a VBAT Supply Monitor Reset, even if the open-circuit voltage is well above the 0.9 V threshold. While this problem is most often associated with operation from very small batteries or batteries that are near the end of their useful life, it can also occur when using bench power supplies that have a slow transient response; the supply's display may indicate a voltage above 0.9 V, but the minimum voltage on the VBAT pin may be lower. A similar problem can occur at the output of the dc-dc converter: using the default low current limit setting (125 mA) can trigger V<sub>DD</sub> Supply Monitor resets if there is a high transient load current, particularly if the programmed output voltage is at or near 1.8 V.

## 16.3. Pulse Skipping Mode

The dc-dc converter allows the user to set the minimum pulse width such that if the duty cycle needs to decrease below a certain width in order to maintain regulation, an entire "clock pulse" will be skipped.

Pulse skipping can provide substantial power savings, particularly at low values of load current. The converter will continue to maintain a minimum output voltage at its programmed value when pulse skipping is employed, though the output voltage ripple can be higher. Another consideration is that the dc-dc will operate with pulse-frequency modulation rather than pulse-width modulation, which makes the switching frequency spectrum less predictable; this could be an issue if the dc-dc converter is used to power a radio. Figure 4.5 and Figure 4.6 on page 45 and 46 show the effect of pulse skipping on power consumption.

#### 20.2.5. Automatic Gain Control (Crystal Mode Only) and SmaRTClock Bias Doubling

Automatic Gain Control allows the SmaRTClock oscillator to trim the oscillation amplitude of a crystal in order to achieve the lowest possible power consumption. Automatic Gain Control automatically detects when the oscillation amplitude has reached a point where it safe to reduce the drive current, therefore, it may be enabled during crystal startup. It is recommended to enable Automatic Gain Control in most systems which use the SmaRTClock oscillator in Crystal Mode. The following are recommended crystal specifications and operating conditions when Automatic Gain Control is enabled:

- ESR < 50 kΩ

- Load Capacitance < 10 pF

- Supply Voltage < 3.0 V</li>

- Temperature > -20 °C

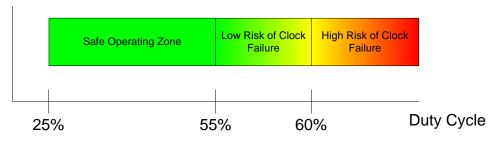

When using Automatic Gain Control, it is recommended to perform an oscillation robustness test to ensure that the chosen crystal will oscillate under the worst case condition to which the system will be exposed. The worst case condition that should result in the least robust oscillation is at the following system conditions: lowest temperature, highest supply voltage, highest ESR, highest load capacitance, and lowest bias current (AGC enabled, Bias Double Disabled).

To perform the oscillation robustness test, the SmaRTClock oscillator should be enabled and selected as the system clock source. Next, the SYSCLK signal should be routed to a port pin configured as a push-pull digital output. The positive duty cycle of the output clock can be used as an indicator of oscillation robustness. As shown in Figure 20.2, duty cycles less than 55% indicate a robust oscillation. As the duty cycle approaches 60%, oscillation becomes less reliable and the risk of clock failure increases. Increasing the bias current (by disabling AGC) will always improve oscillation robustness and will reduce the output clock's duty cycle. This test should be performed at the worst case system conditions, as results at very low temperatures or high supply voltage will vary from results taken at room temperature or low supply voltage.

As an alternative to performing the oscillation robustness test, Automatic Gain Control may be disabled at the cost of increased power consumption (approximately 200 nA). Disabling Automatic Gain Control will provide the crystal oscillator with higher immunity against external factors which may lead to clock failure. Automatic Gain Control must be disabled if using the SmaRTClock oscillator in self-oscillate mode.

Table 20.3 shows a summary of the oscillator bias settings. The SmaRTClock Bias Doubling feature allows the self-oscillation frequency to be increased (almost doubled) and allows a higher crystal drive strength in crystal mode. High crystal drive strength is recommended when the crystal is exposed to poor environmental conditions such as excessive moisture. SmaRTClock Bias Doubling is enabled by setting BIASX2 (RTC0XCN.5) to 1.

#### 20.3.2. Setting a SmaRTClock Alarm

The SmaRTClock alarm function compares the 32-bit value of SmaRTClock Timer to the value of the ALARMn registers. An alarm event is triggered if the SmaRTClock timer is **equal to** the ALARMn registers. If Auto Reset is enabled, the 32-bit timer will be cleared to zero one SmaRTClock cycle after the alarm event.

The SmaRTClock alarm event can be configured to reset the MCU, wake it up from a low power mode, or generate an interrupt. See Section "12. Interrupt Handler" on page 120, Section "14. Power Management" on page 143, and Section "18. Reset Sources" on page 171 for more information.

The following steps can be used to set up a SmaRTClock Alarm:

- 1. Disable SmaRTClock Alarm Events (RTC0AEN = 0).

- 2. Set the ALARMn registers to the desired value.

- 3. Enable SmaRTClock Alarm Events (RTC0AEN = 1).

#### Notes:

- The ALRM bit, which is used as the SmaRTClock Alarm Event flag, is cleared by disabling SmaRTClock Alarm Events (RTC0AEN = 0).

- If AutoReset is disabled, disabling (RTC0AEN = 0) then Re-enabling Alarm Events (RTC0AEN = 1) after a SmaRTClock Alarm without modifying ALARMn registers will automatically schedule the next alarm after 2^32 SmaRTClock cycles (approximately 36 hours using a 32.768 kHz crystal).

- The SmaRTClock Alarm Event flag will remain asserted for a maximum of one SmaRTClock cycle. See Section "14. Power Management" on page 143 for information on how to capture a SmaRTClock Alarm event using a flag which is not automatically cleared by hardware.

#### 20.3.3. Software Considerations for using the SmaRTClock Timer and Alarm

The SmaRTClock timer and alarm have two operating modes to suit varying applications. The two modes are described below:

#### Mode 1:

The first mode uses the SmaRTClock timer as a perpetual timebase which is never reset to zero. Every 36 hours, the timer is allowed to overflow without being stopped or disrupted. The alarm interval is software managed and is added to the ALRMn registers by software after each alarm. This allows the alarm match value to always stay ahead of the timer by one software managed interval. If software uses 32-bit unsigned addition to increment the alarm match value, then it does not need to handle overflows since both the timer and the alarm match value will overflow in the same manner.

This mode is ideal for applications which have a long alarm interval (e.g., 24 or 36 hours) and/or have a need for a perpetual timebase. An example of an application that needs a perpetual timebase is one whose wake-up interval is constantly changing. For these applications, software can keep track of the number of timer overflows in a 16-bit variable, extending the 32-bit (36 hour) timer to a 48-bit (272 year) perpetual timebase.

#### Mode 2:

The second mode uses the SmaRTClock timer as a general purpose up counter which is auto reset to zero by hardware after each alarm. The alarm interval is managed by hardware and stored in the ALRMn registers. Software only needs to set the alarm interval once during device initialization. After each alarm, software should keep a count of the number of alarms that have occurred in order to keep track of time.

This mode is ideal for applications that require minimal software intervention and/or have a fixed alarm interval. This mode is the most power efficient since it requires less CPU time per alarm.

# C8051F91x-C8051F90x

# SFR Definition 21.13. P1: Port1

| Bit   | 7 | 6 | 5       | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|---|---------|---|---|---|---|---|--|

| Name  |   |   | P1[6:0] |   |   |   |   |   |  |

| Туре  |   |   | R/W     |   |   |   |   |   |  |

| Reset | 0 | 1 | 1       | 1 | 1 | 1 | 1 | 1 |  |

SFR Page = All Pages; SFR Address = 0x90; Bit-Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|

| 7   | Unused  | <b>Unused.</b><br>Read =0b; Write = Don't Care                                                                                                | Э.                                                                            |      |

| 6:0 | P1[6:0] | <b>Port 1 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW. |

### SFR Definition 21.14. P1SKIP: Port1 Skip

| Bit   | 7 | 6   | 5           | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-----|-------------|---|---|---|---|---|--|

| Name  |   |     | P1SKIP[6:0] |   |   |   |   |   |  |

| Туре  |   | R/W |             |   |   |   |   |   |  |

| Reset | 0 | 0   | 0           | 0 | 0 | 0 | 0 | 0 |  |

#### SFR Page = 0x0; SFR Address = 0xD5

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused      | Unused.                                                                                                                                                                                                                                                                                                            |

|     |             | Read =0b; Write = Don't Care.                                                                                                                                                                                                                                                                                      |

| 6:0 | P1SKIP[6:0] | Port 1 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 1 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P1.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P1.n pin is skipped by the Crossbar.</li> </ul> |

#### 22.4.3. Hardware Slave Address Recognition

The SMBus hardware has the capability to automatically recognize incoming slave addresses and send an ACK without software intervention. Automatic slave address recognition is enabled by setting the EHACK bit in register SMB0ADM to 1. This will enable both automatic slave address recognition and automatic hardware ACK generation for received bytes (as a master or slave). More detail on automatic hardware ACK generation can be found in Section 22.4.2.2.

The registers used to define which address(es) are recognized by the hardware are the SMBus Slave Address register (SFR Definition 22.3) and the SMBus Slave Address Mask register (SFR Definition 22.4). A single address or range of addresses (including the General Call Address 0x00) can be specified using these two registers. The most-significant seven bits of the two registers are used to define which addresses will be ACKed. A 1 in bit positions of the slave address mask SLVM[6:0] enable a comparison between the received slave address and the hardware's slave address SLV[6:0] for those bits. A 0 in a bit of the slave address mask means that bit will be treated as a "don't care" for comparison purposes. In this case, either a 1 or a 0 value are acceptable on the incoming slave address (0x00). Table 22.4 shows some example parameter settings and the slave addresses that will be recognized by hardware under those conditions.

| Hardware Slave Address<br>SLV[6:0] | Slave Address Mask<br>SLVM[6:0] | GC bit | Slave Addresses Recognized by<br>Hardware |

|------------------------------------|---------------------------------|--------|-------------------------------------------|

| 0x34                               | 0x7F                            | 0      | 0x34                                      |

| 0x34                               | 0x7F                            | 1      | 0x34, 0x00 (General Call)                 |

| 0x34                               | 0x7E                            | 0      | 0x34, 0x35                                |

| 0x34                               | 0x7E                            | 1      | 0x34, 0x35, 0x00 (General Call)           |

| 0x70                               | 0x73                            | 0      | 0x70, 0x74, 0x78, 0x7C                    |

Table 22.4. Hardware Address Recognition Examples (EHACK = 1)

# SFR Definition 24.3. SPInCKR: SPI Clock Rate

| Bit   | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------|---|---|---|---|---|---|---|

| Name  | SCRn[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W       |   |   |   |   |   |   |   |

| Reset | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Addresses: SPI0CKR = 0xA2, SPI1CKR = 0x85 SFR Pages: SPI0CKR = 0x0, SPI1CKR = 0x0

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SCRn | SPI Clock Rate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |      | These bits determine the frequency of the SCK output when the SPI module is<br>configured for master mode operation. The SCK clock frequency is a divided<br>version of the system clock, and is given in the following equation, where SYSCLK<br>is the system clock frequency and SPInCKR is the 8-bit value held in the SPInCKR<br>register.<br>$f_{SCK} = \frac{SYSCLK}{2 \times (SPInCKR[7:0] + 1)}$ for 0 <= SPI0CKR <= 255<br>Example: If SYSCLK = 2 MHz and SPInCKR = 0x04,<br>$f_{SCK} = \frac{2000000}{2 \times (4 + 1)}$ $f_{SCK} = 200kHz$ |

|     |      | $I_{SCK} = 200 \kappa H z$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Parameter                 | Description                                                                  | Min                          | Max                     | Units |

|---------------------------|------------------------------------------------------------------------------|------------------------------|-------------------------|-------|

| Master Mode               | <b>Timing</b> <sup>*</sup> (See Figure 24.8 and Figure 24.9)                 |                              |                         | L     |

| т <sub>мскн</sub>         | SCK High Time                                                                | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>MCKL</sub>         | SCK Low Time                                                                 | 1 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>MIS</sub>          | MISO Valid to SCK Shift Edge                                                 | 1 x T <sub>SYSCLK</sub> + 20 | —                       | ns    |

| т <sub>мін</sub>          | SCK Shift Edge to MISO Change                                                | 0                            | —                       | ns    |

| Slave Mode 1              | <b>Fiming</b> <sup>*</sup> (See Figure 24.10 and Figure 24.11)               |                              |                         | L     |

| T <sub>SE</sub>           | NSS Falling to First SCK Edge                                                | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SD</sub>           | Last SCK Edge to NSS Rising                                                  | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SEZ</sub>          | NSS Falling to MISO Valid                                                    | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SDZ</sub>          | NSS Rising to MISO High-Z                                                    | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| т <sub>скн</sub>          | SCK High Time                                                                | 5 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>CKL</sub>          | SCK Low Time                                                                 | 5 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SIS</sub>          | MOSI Valid to SCK Sample Edge                                                | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SIH</sub>          | SCK Sample Edge to MOSI Change                                               | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| Т <sub>SOH</sub>          | SCK Shift Edge to MISO Change                                                | _                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SLH</sub>          | Last SCK Edge to MISO Change<br>(CKPHA = 1 ONLY)                             | 6 x T <sub>SYSCLK</sub>      | 8 x T <sub>SYSCLK</sub> | ns    |

| *Note: T <sub>SYSCL</sub> | $_{\rm K}$ is equal to one period of the device system clock (S <sup>V</sup> | YSCLK).                      | 1                       | 1     |

Table 24.1. SPI Slave Timing Parameters

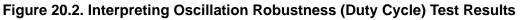

#### 25.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see Section "12.6. External Interrupts INT0 and INT1" on page 130 for details on the external input signals INT0 and INT1).

Figure 25.2. T0 Mode 2 Block Diagram

# C8051F91x-C8051F90x

#### 26.3.5.2. 9/10/11-bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 9/10/11-bit PWM mode should be varied by writing to an "Auto-Reload" Register, which is dual-mapped into the PCA0CPHn and PCA0CPLn register locations. The data written to define the duty cycle should be right-justified in the registers. The auto-reload registers are accessed (read or written) when the bit ARSEL in PCA0PWM is set to 1. The capture/compare registers are accessed when ARSEL is set to 0.

When the least-significant N bits of the PCA0 counter match the value in the associated module's capture/compare register (PCA0CPn), the output on CEXn is asserted high. When the counter overflows from the Nth bit, CEXn is asserted low (see Figure 26.9). Upon an overflow from the Nth bit, the COVF flag is set, and the value stored in the module's auto-reload register is loaded into the capture/compare register. The value of N is determined by the CLSEL bits in register PCA0PWM.

The 9, 10 or 11-bit PWM mode is selected by setting the ECOMn and PWMn bits in the PCA0CPMn register, and setting the CLSEL bits in register PCA0PWM to the desired cycle length (other than 8-bits). If the MATn bit is set to 1, the CCFn flag for the module will be set each time a comparator match (rising edge) occurs. The COVF flag in PCA0PWM can be used to detect the overflow (falling edge), which will occur every 512 (9-bit), 1024 (10-bit) or 2048 (11-bit) PCA clock cycles. The duty cycle for 9/10/11-Bit PWM Mode is given in Equation 26.2, where N is the number of bits in the PWM cycle.

**Important Note About PCA0CPHn and PCA0CPLn Registers**: When writing a 16-bit value to the PCA0CPn registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(2^N - PCA0CPn)}{2^N}$$

Equation 26.3. 9, 10, and 11-Bit PWM Duty Cycle

A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 26.9. PCA 9, 10 and 11-Bit PWM Mode Diagram