# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 16                                                             |

| Program Memory Size        | 16KB (16K × 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 768 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                    |

| Data Converters            | A/D 15x10/12b                                                  |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 24-QSOP                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f912-gu |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 19.2.Low Power Internal Oscillator                                              |       |

|---------------------------------------------------------------------------------|-------|

| 19.3.External Oscillator Drive Circuit                                          | . 180 |

| 19.3.1.External Crystal Mode                                                    | . 180 |

| 19.3.2.External RC Mode                                                         | . 182 |

| 19.3.3.External Capacitor Mode                                                  | . 183 |

| 19.3.4.External CMOS Clock Mode                                                 |       |

| 19.4. Special Function Registers for Selecting and Configuring the System Clock |       |

| 20. SmaRTClock (Real Time Clock)                                                |       |

| 20.1.SmaRTClock Interface                                                       |       |

| 20.1.1.SmaRTClock Lock and Key Functions                                        |       |

| 20.1.2.Using RTC0ADR and RTC0DAT to Access SmaRTClock                           | 100   |

| Internal Registers                                                              | 100   |

| 20.1.3.RTC0ADR Short Strobe Feature                                             | 100   |

| 20.1.4.SmaRTClock Interface Autoread Feature                                    |       |

|                                                                                 |       |

| 20.1.5.RTC0ADR Autoincrement Feature                                            |       |

| 20.2.SmaRTClock Clocking Sources                                                | . 194 |

| 20.2.1.Using the SmaRTClock Oscillator with a Crystal or                        |       |

| External CMOS Clock                                                             | . 194 |

| 20.2.2.Using the SmaRTClock Oscillator in Self-Oscillate Mode                   |       |

| 20.2.3.Using the Low Frequency Oscillator (LFO)                                 |       |

| 20.2.4.Programmable Load Capacitance                                            | . 196 |

| 20.2.5.Automatic Gain Control (Crystal Mode Only) and                           |       |

| SmaRTClock Bias Doubling                                                        | . 197 |

| 20.2.6.Missing SmaRTClock Detector                                              | . 199 |

| 20.2.7.SmaRTClock Oscillator Crystal Valid Detector                             | . 199 |

| 20.3.SmaRTClock Timer and Alarm Function                                        |       |

| 20.3.1.Setting and Reading the SmaRTClock Timer Value                           | . 199 |

| 20.3.2.Setting a SmaRTClock Alarm                                               |       |

| 20.3.3.Software Considerations for using the SmaRTClock Timer and Alarm         |       |

| 21. Port Input/Output                                                           |       |

| 21.1.Port I/O Modes of Operation                                                |       |

| 21.1.1.Port Pins Configured for Analog I/O                                      |       |

| 21.1.2.Port Pins Configured For Digital I/O                                     |       |

| 21.1.3.Interfacing Port I/O to 5 V and 3.3 V Logic                              | 207   |

| 21.1.4.Increasing Port I/O Drive Strength                                       |       |

| 21.2.Assigning Port I/O Pins to Analog and Digital Functions                    | 207   |

| 21.2.1.Assigning Port I/O Pins to Analog Functions                              |       |

| 21.2.2.Assigning Port I/O Pins to Digital Functions                             |       |

|                                                                                 |       |

| 21.2.3.Assigning Port I/O Pins to External Digital Event Capture Functions      |       |

| 21.3.Priority Crossbar Decoder                                                  |       |

| 21.4.Port Match                                                                 |       |

| 21.5. Special Function Registers for Accessing and Configuring Port I/O         |       |

| 22. SMBus                                                                       |       |

| 22.1.Supporting Documents                                                       |       |

| 22.2.SMBus Configuration                                                        | . 226 |

| SFR Definition 21.19. P2MDOUT: Port2 Output Mode                 | 224 |

|------------------------------------------------------------------|-----|

| SFR Definition 21.20. P2DRV: Port2 Drive Strength                |     |

| SFR Definition 22.1. SMB0CF: SMBus Clock/Configuration           | 232 |

| SFR Definition 22.2. SMB0CN: SMBus Control                       |     |

| SFR Definition 22.3. SMB0ADR: SMBus Slave Address                |     |

| SFR Definition 22.4. SMB0ADM: SMBus Slave Address Mask           |     |

| SFR Definition 22.5. SMB0DAT: SMBus Data                         |     |

| SFR Definition 23.1. SCON0: Serial Port 0 Control                |     |

| SFR Definition 23.2. SBUF0: Serial (UART0) Port Data Buffer      |     |

| SFR Definition 24.1. SPInCFG: SPI Configuration                  |     |

| SFR Definition 24.2. SPInCN: SPI Control                         |     |

| SFR Definition 24.3. SPInCKR: SPI Clock Rate                     |     |

| SFR Definition 24.4. SPInDAT: SPI Data                           |     |

| SFR Definition 25.1. CKCON: Clock Control                        |     |

| SFR Definition 25.2. TCON: Timer Control                         |     |

| SFR Definition 25.3. TMOD: Timer Mode                            |     |

| SFR Definition 25.4. TL0: Timer 0 Low Byte                       |     |

| SFR Definition 25.5. TL1: Timer 1 Low Byte                       |     |

| SFR Definition 25.6. TH0: Timer 0 High Byte                      |     |

| SFR Definition 25.7. TH1: Timer 1 High Byte                      |     |

| SFR Definition 25.8. TMR2CN: Timer 2 Control                     |     |

| SFR Definition 25.9. TMR2RLL: Timer 2 Reload Register Low Byte   |     |

| SFR Definition 25.10. TMR2RLH: Timer 2 Reload Register High Byte |     |

| SFR Definition 25.11. TMR2L: Timer 2 Low Byte                    |     |

| SFR Definition 25.12. TMR2H Timer 2 High Byte                    |     |

| SFR Definition 25.13. TMR3CN: Timer 3 Control                    |     |

| SFR Definition 25.14. TMR3RLL: Timer 3 Reload Register Low Byte  |     |

| SFR Definition 25.16. TMR3L: Timer 3 Low Byte                    |     |

| SFR Definition 25.17. TMR3H Timer 3 High Byte                    |     |

| SFR Definition 26.1. PCA0CN: PCA Control                         |     |

| SFR Definition 26.2. PCA0MD: PCA Mode                            |     |

| SFR Definition 26.3. PCA0PWM: PCA PWM Configuration              |     |

| SFR Definition 26.4. PCA0CPMn: PCA Capture/Compare Mode          |     |

| SFR Definition 26.5. PCA0L: PCA Counter/Timer Low Byte           |     |

| SFR Definition 26.6. PCA0H: PCA Counter/Timer High Byte          |     |

| SFR Definition 26.7. PCA0CPLn: PCA Capture Module Low Byte       |     |

| SFR Definition 26.8. PCA0CPHn: PCA Capture Module High Byte      |     |

| C2 Register Definition 27.1. C2ADD: C2 Address                   |     |

| C2 Register Definition 27.2. DEVICEID: C2 Device ID              |     |

| C2 Register Definition 27.3. REVID: C2 Revision ID               |     |

| C2 Register Definition 27.4. FPCTL: C2 Flash Programming Control |     |

| C2 Register Definition 27.5. FPDAT: C2 Flash Programming Data    |     |

|                                                                  |     |

### 1. System Overview

C8051F91x-C8051F90x devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 2.1 for specific product feature selection and part ordering numbers.

- Single/Dual Battery operation with on-chip dc-dc boost converter.

- High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- 10-bit 300 ksps or 12-bit 75 ksps single-ended ADC with analog multiplexer

- 6-Bit Programmable Current Reference. Resolution can be increased with PWM.

- Precision programmable 24.5 MHz internal oscillator with spread spectrum technology.

- 16 kB or 8 kB of on-chip Flash memory

- 768 bytes of on-chip RAM

- SMBus/I<sup>2</sup>C, Enhanced UART, and two Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable Counter/Timer Array (PCA) with six capture/compare modules and Watchdog Timer function

- On-chip Power-On Reset, V<sub>DD</sub> Monitor, and Temperature Sensor

- Two On-chip Voltage Comparators with 15 Capacitive Touch Sense inputs.

- 16 Port I/O (5 V tolerant)

With on-chip Power-On Reset, V<sub>DD</sub> monitor, Watchdog Timer, and clock oscillator, the C8051F91x-C8051F90x devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 0.9 to 1.8 V, 0.9 to 3.6 V or 1.8 to 3.6 V operation over the industrial temperature range (-40 to +85 °C). The Port I/O and RST pins are tolerant of input signals up to 5 V. The C8051F91x-C8051F90x devices are available in 24-pin QFN or QSOP packages. Both package options are lead-free and RoHS compliant. See Table 2.1 for ordering information. Block diagrams are included in Figure 1.1 through Figure 1.4.

### SFR Definition 5.2. ADC0CF: ADC0 Configuration

| Bit   | 7               | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                                                                                                 | 4 | 3        | 2      | 1     | 0      |

|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---|----------|--------|-------|--------|

| Name  | 9               | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AD0SC[4:0]                                                                                                        |   |          | AD08BE | AD0TM | AMP0GN |

| Туре  | •               | R/W R/W R/W R/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |   |          |        |       |        |

| Rese  | t 1             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                 | 1 | 1        | 0      | 0     | 0      |

| SFR P | age = 0x0; SF   | R Address =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | = 0xBC                                                                                                            |   |          |        |       | I      |

| Bit   | Name            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                   |   | Functior | )      |       |        |

| 7:3   | AD0SC[4:0]      | ADC0 SAR Conversion Clock Divider.         SAR Conversion clock is derived from FCLK by the following equation, where         ADOSC refers to the 5-bit value held in bits ADOSC[4:0]. SAR Conversion clock         requirements are given in Table 4.10.         BURSTEN = 0: FCLK is the current system clock.         BURSTEN = 1: FCLK is the 20 MHz low power oscillator, independent of the system clock.         AD0SC = $\frac{FCLK}{CLK_{SAR}} - 1$ *         *Round the result up.         or $CLK_{SAR} = \frac{FCLK}{AD0SC + 1}$ |                                                                                                                   |   |          |        |       |        |

| 2     | AD08BE          | 0: ADC0 op                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ADC0 8-Bit Mode Enable.<br>0: ADC0 operates in 10-bit mode (normal operation).<br>1: ADC0 operates in 8-bit mode. |   |          |        |       |        |

| 0     | AD0TM<br>AMP0GN | <ul> <li>ADC0 Track Mode.</li> <li>Selects between Normal or Delayed Tracking Modes.</li> <li>0: Normal Track Mode: When ADC0 is enabled, conversion begins immediately following the start-of-conversion signal.</li> <li>1: Delayed Track Mode: When ADC0 is enabled, conversion begins 3 SAR clock cycles following the start-of-conversion signal. The ADC is allowed to track during this time.</li> <li>ADC0 Gain Control.</li> </ul>                                                                                                  |                                                                                                                   |   |          |        |       |        |

|       |                 | 0: The on-c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | hip PGA gai<br>hip PGA gai                                                                                        |   |          |        |       |        |

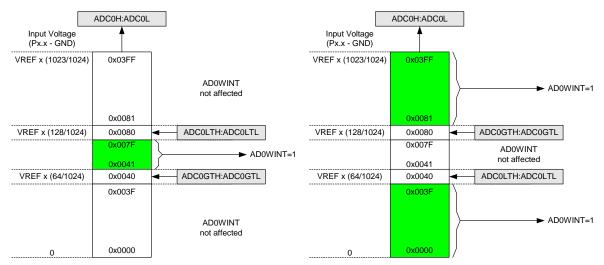

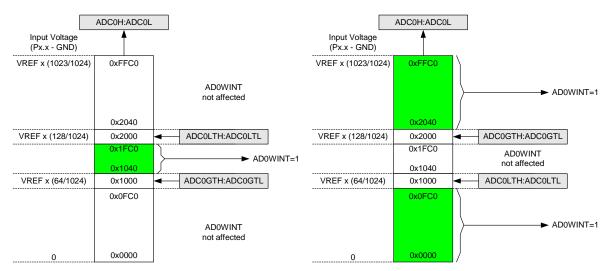

#### 5.6.1. Window Detector In Single-Ended Mode

Figure 5.5 shows two example window comparisons for right-justified with data. ADC0LTH:ADC0LTL = 0x0080 (128d) and ADC0GTH:ADC0GTL = 0x0040 (64d). The input voltage can range from 0 to VREF x (1023/1024) with respect to GND, and is represented by a 10-bit unsigned integer value. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0040 < ADC0H:ADC0L < 0x0080). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0040 or ADC0H:ADC0L > 0x0080). Figure 5.6 shows an example using leftjustified data with the same comparison values.

Figure 5.5. ADC Window Compare Example: Right-Justified Single-Ended Data

Figure 5.6. ADC Window Compare Example: Left-Justified Single-Ended Data

#### 5.6.2. ADC0 Specifications

See "4. Electrical Characteristics" on page 36 for a detailed listing of ADC0 specifications.

#### 7.5. Comparator Register Descriptions

The SFRs used to enable and configure the comparators are described in the following register descriptions. A Comparator must be enabled by setting the CPnEN bit to logic 1 before it can be used. From an enabled state, a comparator can be disabled and placed in a low power state by clearing the CPnEN bit to logic 0.

**Important Note About Comparator Settings:** False rising and falling edges can be detected by the Comparator while powering on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed. The Comparator Power Up Time is specified in Section "Table 4.14. Comparator Electrical Characteristics" on page 58.

#### SFR Definition 7.1. CPT0CN: Comparator 0 Control

| Bit   | 7     | 6      | 5      | 4      | 3     | 2       | 1    | 0       |

|-------|-------|--------|--------|--------|-------|---------|------|---------|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0H) | YP[1:0] | CP0H | YN[1:0] |

| Туре  | R/W   | R      | R/W    | R/W    | R/W   |         | R/   | W       |

| Reset | 0     | 0      | 0      | 0      | 0     | 0       | 0    | 0       |

SFR Page= 0x0; SFR Address = 0x9B

| Bit | Name        | Function                                                                                                                                          |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                                                                                           |

|     |             | 0: Comparator0 Disabled.<br>1: Comparator0 Enabled.                                                                                               |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                                                                                    |

|     |             | 0: Voltage on CP0+ < CP0<br>1: Voltage on CP0+ > CP0                                                                                              |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                                                                                        |

|     |             | <ul><li>0: No Comparator0 Rising Edge has occurred since this flag was last cleared.</li><li>1: Comparator0 Rising Edge has occurred.</li></ul>   |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                                                                                       |

|     |             | <ul><li>0: No Comparator0 Falling-Edge has occurred since this flag was last cleared.</li><li>1: Comparator0 Falling-Edge has occurred.</li></ul> |

| 3-2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                                                                                     |

|     |             | 00: Positive Hysteresis Disabled.                                                                                                                 |

|     |             | 01: Positive Hysteresis = Hysteresis 1.                                                                                                           |

|     |             | <ul><li>10: Positive Hysteresis = Hysteresis 2.</li><li>11: Positive Hysteresis = Hysteresis 3 (Maximum).</li></ul>                               |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                                                                                     |

|     |             | 00: Negative Hysteresis Disabled.                                                                                                                 |

|     |             | 01: Negative Hysteresis = Hysteresis 1.                                                                                                           |

|     |             | 10: Negative Hysteresis = Hysteresis 2.                                                                                                           |

|     |             | 11: Negative Hysteresis = Hysteresis 3 (Maximum).                                                                                                 |

#### SFR Definition 12.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Page = All Pages; SFR Address = 0xA8; Bit-Addressable

| Bit | Name  | Function                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <ul> <li>Enable All Interrupts.</li> <li>Globally enables/disables all interrupts. It overrides individual interrupt mask settings.</li> <li>0: Disable all interrupt sources.</li> <li>1: Enable each interrupt according to its individual mask setting.</li> </ul> |

| 6   | ESPI0 | <ul> <li>Enable Serial Peripheral Interface (SPI0) Interrupt.</li> <li>This bit sets the masking of the SPI0 interrupts.</li> <li>0: Disable all SPI0 interrupts.</li> <li>1: Enable interrupt requests generated by SPI0.</li> </ul>                                 |

| 5   | ET2   | <ul> <li>Enable Timer 2 Interrupt.</li> <li>This bit sets the masking of the Timer 2 interrupt.</li> <li>0: Disable Timer 2 interrupt.</li> <li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li> </ul>                                          |

| 4   | ES0   | Enable UART0 Interrupt.<br>This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.<br>1: Enable UART0 interrupt.                                                                                                                             |

| 3   | ET1   | <ul> <li>Enable Timer 1 Interrupt.</li> <li>This bit sets the masking of the Timer 1 interrupt.</li> <li>0: Disable all Timer 1 interrupt.</li> <li>1: Enable interrupt requests generated by the TF1 flag.</li> </ul>                                                |

| 2   | EX1   | <ul> <li>Enable External Interrupt 1.</li> <li>This bit sets the masking of External Interrupt 1.</li> <li>0: Disable external interrupt 1.</li> <li>1: Enable interrupt requests generated by the INT1 input.</li> </ul>                                             |

| 1   | ET0   | <ul> <li>Enable Timer 0 Interrupt.</li> <li>This bit sets the masking of the Timer 0 interrupt.</li> <li>0: Disable all Timer 0 interrupt.</li> <li>1: Enable interrupt requests generated by the TF0 flag.</li> </ul>                                                |

| 0   | EX0   | <ul> <li>Enable External Interrupt 0.</li> <li>This bit sets the masking of External Interrupt 0.</li> <li>0: Disable external interrupt 0.</li> <li>1: Enable interrupt requests generated by the INTO input.</li> </ul>                                             |

#### 14.2. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

## Note: To ensure the MCU enters a low power state upon entry into Idle Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "18.6. PCA Watchdog Timer Reset" on page 176 for more information on the use and configuration of the WDT.

#### 14.3. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter stop mode as soon as the instruction that sets the bit completes execution. In stop mode the precision internal oscillator and CPU are stopped; the state of the low power oscillator and the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering stop mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout.

Stop mode is a legacy 8051 power mode; it will not result in optimal power savings. Sleep or suspend mode will provide more power savings if the MCU needs to be inactive for a long period of time.

## Note: To ensure the MCU enters a low power state upon entry into Stop Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

#### **16.12. DC-DC Converter Register Descriptions**

The SFRs used to configure the dc-dc converter are described in the following register descriptions. The reset values for these registers can be used as-is in most systems; therefore, no software intervention or initialization is required.

#### SFR Definition 16.1. DC0CN: DC-DC Converter Control

| Bit   | 7   | 6   | 5     | 4        | 3    | 2 | 1    | 0 |

|-------|-----|-----|-------|----------|------|---|------|---|

| Name  | MIN | IPW | SWSEL | Reserved | SYNC |   | VSEL |   |

| Туре  | R/W |     | R/W   | R/W      | R/W  |   | R/W  |   |

| Reset | 0   | 0   | 1     | 0        | 0    | 0 | 0    | 1 |

SFR Page = 0x0; SFR Address = 0x97

| Bit | Name       | Function                                                                                                                                |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | MINPW[1:0] | DC-DC Converter Minimum Pulse Width.                                                                                                    |

|     |            | Specifies the minimum pulse width.                                                                                                      |

|     |            | 00: No minimum duty cycle.                                                                                                              |

|     |            | 01: Minimum pulse width is 20 ns.                                                                                                       |

|     |            | 10: Minimum pulse width is 40 ns.                                                                                                       |

|     |            | 11: Minimum pulse width is 80 ns.                                                                                                       |

| 5   | SWSEL      | DC-DC Converter Switch Select.                                                                                                          |

|     |            | Selects one of two possible converter switch sizes to maximize efficiency.                                                              |

|     |            | 0: The large switches are selected (best efficiency for high output currents).                                                          |

|     |            | 1: The small switches are selected (best efficiency for low output currents).                                                           |

| 4   | Reserved   | Reserved. Always Write to 0.                                                                                                            |

| 3   | SYNC       | ADC0 Synchronization Enable.                                                                                                            |

|     |            | When synchronization is enabled, the ADC0SC[4:0] bits in the ADC0CF register                                                            |

|     |            | must be set to 00000b.                                                                                                                  |

|     |            | 0: The ADC is not synchronized to the dc-dc converter.<br>1: The ADC is synchronized to the dc-dc converter. ADC0 tracking is performed |

|     |            | during the longest quiet time of the dc-dc converter switching cycle and ADC0 SAR                                                       |

|     |            | clock is also synchronized to the dc-dc converter switching cycle.                                                                      |

| 2:0 | VSEL[2:0]  | DC-DC Converter Output Voltage Select.                                                                                                  |

|     |            | Specifies the target output voltage.                                                                                                    |

|     |            | 000: Target output voltage is 1.8 V.                                                                                                    |

|     |            | 001: Target output voltage is 1.9 V.                                                                                                    |

|     |            | 010: Target output voltage is 2.0 V.                                                                                                    |

|     |            | 011: Target output voltage is 2.1 V.                                                                                                    |

|     |            | 100: Target output voltage is 2.4 V.<br>101: Target output voltage is 2.7 V.                                                            |

|     |            | 110: Target output voltage is 3.0 V.                                                                                                    |

|     |            | 111: Target output voltage is 3.3 V.                                                                                                    |

|     |            |                                                                                                                                         |

### SFR Definition 16.3. DC0MD: DC-DC Mode

| Bit   | 7   | 6   | 5   | 4   | 3      | 2    | 1       | 0      |

|-------|-----|-----|-----|-----|--------|------|---------|--------|

| Name  |     |     |     |     | BYPFLG | BYPS | EL[1:0] | PASDEN |

| Туре  | R/W | R/W | R/W | R/W | R      | R/   | W       | R/W    |

| Reset | 0   | 0   | 0   | 0   | Varies | 0    | 0       | 0      |

#### SFR Page = 0xF; SFR Address = 0x94

| Bit | Name        | Function                                                                                                                                 |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Unused      | Unused.                                                                                                                                  |

|     |             | Read = 0000b, Write = don't care.                                                                                                        |

| 3   | BYPFLG      | Bypass Indicator.                                                                                                                        |

|     |             | Indicates when the dc-dc converter is operating in bypass mode. Only available on 'F912 and 'F902 devices.                               |

|     |             | 0: DC0 is not operating in bypass mode.                                                                                                  |

|     |             | 1: DC0 is operating in bypass mode.                                                                                                      |

| 2:1 | BYPSEL[1:0] | Bypass Mode Select.                                                                                                                      |

|     |             | Selects the bypass settings. Only available on 'F912 and 'F902 devices.                                                                  |

|     |             | 00: Bypass mode disabled (highest supply current when the input voltage exceeds the programmed output voltage).                          |

|     |             | 01: Bypass enabled (auto switch), dc-dc oscillator enabled (fast response time)                                                          |

|     |             | 10: Bypass enabled (auto switch), dc-dc oscillator disabled (reduced supply current)                                                     |

|     |             | 11: The dc-dc converter is forced into bypass mode (lowest supply current when the input voltage exceeds the programmed output voltage). |

| 0   | PASDEN      | Passive Diode Mode Enable.                                                                                                               |

|     |             | Passive external diode mode. Only available on 'F912 and 'F902 devices.                                                                  |

|     |             | 0: Passive diode mode disabled.                                                                                                          |

|     |             | 1: Passive diode mode enabled.                                                                                                           |

#### 16.13. DC-DC Converter Specifications

See Table 4.16 on page 60 for a detailed listing of dc-dc converter specifications.

### 17. Voltage Regulator (VREG0)

C8051F91x-C8051F90x devices include an internal voltage regulator (VREG0) to regulate the internal core supply to 1.8 V from a VDD/DC+ supply of 1.8 to 3.6 V. Electrical characteristics for the on-chip regulator are specified in the Electrical Specifications chapter.

The REGOCN register allows the Precision Oscillator Bias to be disabled, reducing supply current in all non-Sleep power modes. This bias should only be disabled when the precision oscillator is not being used.

The internal regulator (VREG0) is disabled when the device enters Sleep Mode and remains enabled when the device enters Suspend Mode. See Section "14. Power Management" on page 143 for complete details about low power modes.

#### SFR Definition 17.1. REG0CN: Voltage Regulator Control

| Bit   | 7 | 6        | 5        | 4       | 3 | 2 | 1 | 0        |

|-------|---|----------|----------|---------|---|---|---|----------|

| Name  |   | Reserved | Reserved | OSCBIAS |   |   |   | Reserved |

| Туре  | R | R/W      | R/W      | R/W     | R | R | R | R/W      |

| Reset | 0 | 0        | 0        | 1       | 0 | 0 | 0 | 0        |

#### SFR Page = 0x0; SFR Address = 0xC9

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                            |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused   | Unused.                                                                                                                                                                                                                                                                                                                             |

|     |          | Read = 0b. Write = Don't care.                                                                                                                                                                                                                                                                                                      |

| 6   | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                           |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                           |

| 5   | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                           |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                           |

| 4   | OSCBIAS  | Precision Oscillator Bias.                                                                                                                                                                                                                                                                                                          |

|     |          | When set to 1, the bias used by the precision oscillator is forced on. If the precision oscillator is not being used, this bit may be cleared to 0 to save approximately 80 $\mu$ A of supply current in all non-Sleep power modes. If disabled then re-enabled, the precision oscillator bias requires 4 $\mu$ s of settling time. |

| 3:1 | Unused   | Unused.                                                                                                                                                                                                                                                                                                                             |

|     |          | Read = 000b. Write = Don't care.                                                                                                                                                                                                                                                                                                    |

| 0   | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                           |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                           |

#### 17.1. Voltage Regulator Electrical Specifications

See Table 4.15 on page 59 for detailed Voltage Regulator Electrical Specifications.

### SFR Definition 19.4. OSCXCN: External Oscillator Control

| Bit   | 7       | 6           | 5   | 4   | 3        | 2         | 1   | 0   |  |

|-------|---------|-------------|-----|-----|----------|-----------|-----|-----|--|

| Name  | XCLKVLD | XOSCMD[2:0] |     |     | Reserved | XFCN[2:0] |     |     |  |

| Туре  | R       | R           | R/W | R/W | R/W      | R/W       | R/W | R/W |  |

| Reset | 0       | 0           | 0   | 0   | 0        | 0         | 0   | 0   |  |

SFR Page = 0x0; SFR Address = 0xB1

| Bit | Name     | Function                                                                                                                                                                                                          |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | XCLKVLD  | External Oscillator Valid Flag.                                                                                                                                                                                   |

|     |          | Provides External Oscillator status and is valid at all times for all modes of operation except External CMOS Clock Mode and External CMOS Clock Mode with divide by 2. In these modes, XCLKVLD always returns 0. |

|     |          | <ul><li>0: External Oscillator is unused or not yet stable.</li><li>1: External Oscillator is running and stable.</li></ul>                                                                                       |

| 6:4 | XOSCMD   | External Oscillator Mode Bits.                                                                                                                                                                                    |

|     |          | Configures the external oscillator circuit to the selected mode.                                                                                                                                                  |

|     |          | 00x: External Oscillator circuit disabled.                                                                                                                                                                        |

|     |          | 010: External CMOS Clock Mode.                                                                                                                                                                                    |

|     |          | 011: External CMOS Clock Mode with divide by 2 stage.                                                                                                                                                             |

|     |          | 100: RC Oscillator Mode.                                                                                                                                                                                          |

|     |          | 101: Capacitor Oscillator Mode.                                                                                                                                                                                   |

|     |          | 110: Crystal Oscillator Mode.                                                                                                                                                                                     |

|     |          | 111: Crystal Oscillator Mode with divide by 2 stage.                                                                                                                                                              |

| 3   | Reserved | Reserved.                                                                                                                                                                                                         |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                         |

| 2:0 | XFCN     | External Oscillator Frequency Control Bits.                                                                                                                                                                       |

|     |          | Controls the external oscillator bias current.                                                                                                                                                                    |

|     |          | 000-111: See Table 19.1 on page 181 (Crystal Mode) or Table 19.2 on page 182 (RC or C Mode) for recommended settings.                                                                                             |

### Internal Register Definition 20.6. RTC0XCF: SmaRTClock Oscillator Configuration

| Bit   | 7       | 6       | 5 | 4 | 3      | 2      | 1      | 0      |

|-------|---------|---------|---|---|--------|--------|--------|--------|

| Name  | AUTOSTP | LOADRDY |   |   |        | LOAE   | DCAP   |        |

| Туре  | R/W     | R       | R | R |        | R/     | W      |        |

| Reset | 0       | 0       | 0 | 0 | Varies | Varies | Varies | Varies |

SmaRTClock Address = 0x06

| Bit | Name    | Function                                                                                                                                                                                                                                                 |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AUTOSTP | Automatic Load Capacitance Stepping Enable.Enables/disables automatic load capacitance stepping.0: Load capacitance stepping disabled.1: Load capacitance stepping enabled.                                                                              |

| 6   | LOADRDY | <ul> <li>Load Capacitance Ready Indicator.</li> <li>Set by hardware when the load capacitance matches the programmed value.</li> <li>0: Load capacitance is currently stepping.</li> <li>1: Load capacitance has reached it programmed value.</li> </ul> |

| 5:4 | Unused  | <b>Unused.</b><br>Read = 00b; Write = Don't Care.                                                                                                                                                                                                        |

| 3:0 | LOADCAP | Load Capacitance Programmed Value.<br>Holds the user's desired value of the load capacitance. See Table 20.2 on<br>page 196.                                                                                                                             |

#### Internal Register Definition 20.7. RTC0PIN: SmaRTClock Pin Configuration

| Bit   | 7       | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---------|--------|--------|--------|--------|--------|--------|--------|

| Name  | RTC0PIN |        |        |        |        |        |        |        |

| Туре  | W       | R/W    |

| Reset | 0       | Varies |

SmaRTClock Address = 0x07

| Bit | Name     | Function                                                                                                                                                                 |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RTC0PIN  | SmaRTClock Pin Configuration.                                                                                                                                            |

|     |          | 0: XTAL3 and XTAL4 in their normal configuration.                                                                                                                        |

|     |          | 1: XTAL3 and XTAL4 internally shorted for use with Self Oscillate Mode.                                                                                                  |

| 6:0 | Reserved | Reserved.                                                                                                                                                                |

|     |          | Read = Varies. Software should not modify the value of these bits. To change the RTC0PIN setting, the entire register contents should be read, modified, then rewritten. |

#### 21.5. Special Function Registers for Accessing and Configuring Port I/O

All Port I/O are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

Each Port has a corresponding PnSKIP register which allows its individual Port pins to be assigned to digital functions or skipped by the Crossbar. All Port pins used for analog functions, GPIO, or dedicated digital functions such as the EMIF should have their PnSKIP bit set to 1.

The Port input mode of the I/O pins is defined using the Port Input Mode registers (PnMDIN). Each Port cell can be configured for analog or digital I/O. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is P2.7, which can only be used for digital I/O.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings.

The drive strength of the output drivers are controlled by the Port Drive Strength (PnDRV) registers. The default is low drive strength. See Section "4. Electrical Characteristics" on page 36 for the difference in output drive strength between the two modes.

### SFR Definition 22.3. SMB0ADR: SMBus Slave Address

| Bit   | 7        | 6   | 5 | 4 | 3 | 2 | 1 | 0   |

|-------|----------|-----|---|---|---|---|---|-----|

| Name  | SLV[6:0] |     |   |   |   |   |   | GC  |

| Туре  |          | R/W |   |   |   |   |   | R/W |

| Reset | 0        | 0   | 0 | 0 | 0 | 0 | 0 | 0   |

SFR Page = 0x0; SFR Address = 0xF4

| Bit | Name     | Function                                                                                                                                                                                                                                                                   |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLV[6:0] | SMBus Hardware Slave Address.                                                                                                                                                                                                                                              |

|     |          | Defines the SMBus Slave Address(es) for automatic hardware acknowledgement.<br>Only address bits which have a 1 in the corresponding bit position in SLVM[6:0]<br>are checked against the incoming address. This allows multiple addresses to be<br>recognized.            |

| 0   | GC       | General Call Address Enable.                                                                                                                                                                                                                                               |

|     |          | <ul> <li>When hardware address recognition is enabled (EHACK = 1), this bit will determine whether the General Call Address (0x00) is also recognized by hardware.</li> <li>0: General Call Address is ignored.</li> <li>1: General Call Address is recognized.</li> </ul> |

#### SFR Definition 22.4. SMB0ADM: SMBus Slave Address Mask

| Bit   | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0   |

|-------|---|-----------|---|---|---|---|---|-----|

| Name  |   | SLVM[6:0] |   |   |   |   |   |     |

| Туре  |   | R/W       |   |   |   |   |   | R/W |

| Reset | 1 | 1         | 1 | 1 | 1 | 1 | 1 | 0   |

#### SFR Page = 0x0; SFR Address = 0xF5

| Bit | Name      | Function                                                                                                                                                                                                                                                                           |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLVM[6:0] | SMBus Slave Address Mask.                                                                                                                                                                                                                                                          |

|     |           | Defines which bits of register SMB0ADR are compared with an incoming address byte, and which bits are ignored. Any bit set to 1 in SLVM[6:0] enables comparisons with the corresponding bit in SLV[6:0]. Bits set to 0 are ignored (can be either 0 or 1 in the incoming address). |

| 0   | EHACK     | Hardware Acknowledge Enable.                                                                                                                                                                                                                                                       |

|     |           | Enables hardware acknowledgement of slave address and received data bytes.<br>0: Firmware must manually acknowledge all incoming address and data bytes.<br>1: Automatic Slave Address Recognition and Hardware Acknowledge is Enabled.                                            |

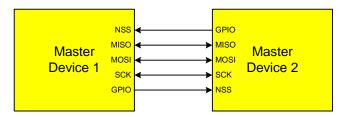

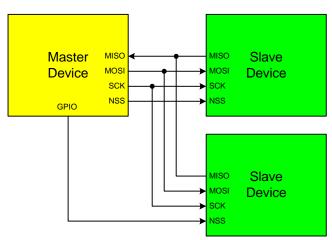

Figure 24.2. Multiple-Master Mode Connection Diagram

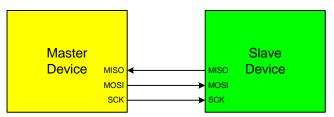

Figure 24.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram

Figure 24.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diagram

#### SFR Definition 24.2. SPInCN: SPI Control

| Bit   | 7     | 6     | 5     | 4       | 3       | 2       | 1      | 0      |

|-------|-------|-------|-------|---------|---------|---------|--------|--------|

| Name  | SPIFn | WCOLn | MODFn | RXOVRNn | NSSnMD1 | NSSnMD0 | TXBMTn | SPInEN |

| Туре  | R/W   | R/W   | R/W   | R/W     | R/W     | R/W     | R      | R/W    |

| Reset | 0     | 0     | 0     | 0       | 0       | 1       | 1      | 0      |

SFR Addresses: SPI0CN = 0xF8, Bit-Addressable; SPI1CN = 0xB0, Bit-Addressable SFR Pages: SPI0CN = 0x0, SPI1CN = 0x0

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIFn       | <b>SPIn Interrupt Flag.</b><br>This bit is set to logic 1 by hardware at the end of a data transfer. If interrupts are enabled, setting this bit causes the CPU to vector to the SPIn interrupt service routine. This bit is not automatically cleared by hardware. It must be cleared by software.                                                                                                                                                          |

| 6   | WCOLn       | Write Collision Flag.<br>This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) to indicate a<br>write to the SPI0 data register was attempted while a data transfer was in progress.<br>It must be cleared by software.                                                                                                                                                                                                                    |

| 5   | MODFn       | <b>Mode Fault Flag.</b><br>This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) when a master mode collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01).<br>This bit is not automatically cleared by hardware. It must be cleared by software.                                                                                                                                                                              |

| 4   | RXOVRNn     | <b>Receive Overrun Flag (valid in slave mode only).</b><br>This bit is set to logic 1 by hardware (and generates a SPIn interrupt) when the receive buffer still holds unread data from a previous transfer and the last bit of the current transfer is shifted into the SPI shift register. This bit is not automatically cleared by hardware. It must be cleared by software.                                                                              |

| 3:2 | NSSnMD[1:0] | <ul> <li>Slave Select Mode.</li> <li>Selects between the following NSS operation modes:<br/>(See Section 24.2 and Section 24.3).</li> <li>00: 3-Wire Slave or 3-Wire Master Mode. NSS signal is not routed to a port pin.</li> <li>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is an input to the device.</li> <li>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the device and will assume the value of NSSMD0.</li> </ul> |

| 1   | TXBMTn      | <b>Transmit Buffer Empty.</b><br>This bit will be set to logic 0 when new data has been written to the transmit buffer.<br>When data in the transmit buffer is transferred to the SPI shift register, this bit will<br>be set to logic 1, indicating that it is safe to write a new byte to the transmit buffer.                                                                                                                                             |

| 0   | SPInEN      | <b>SPIn Enable.</b><br>0: SPIn disabled.<br>1: SPIn enabled.                                                                                                                                                                                                                                                                                                                                                                                                 |

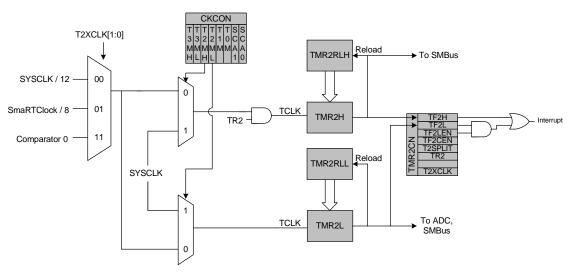

#### 25.2.2. 8-bit Timers with Auto-Reload

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 25.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, SmaRTClock divided by 8 or Comparator 0 output. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bits (T2XCLK[1:0] in TMR2CN), as follows:

| T2MH | T2XCLK[1:0] | TMR2H Clock<br>Source |

|------|-------------|-----------------------|

| 0    | 00          | SYSCLK / 12           |

| 0    | 01          | SmaRTClock / 8        |

| 0    | 10          | Reserved              |

| 0    | 11          | Comparator 0          |

| 1    | Х           | SYSCLK                |

| T2ML | T2XCLK[1:0] | TMR2L Clock<br>Source |

|------|-------------|-----------------------|

| 0    | 00          | SYSCLK / 12           |

| 0    | 01          | SmaRTClock / 8        |

| 0    | 10          | Reserved              |

| 0    | 11          | Comparator 0          |

| 1    | Х           | SYSCLK                |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 25.5. Timer 2 8-Bit Mode Block Diagram

#### SFR Definition 26.7. PCA0CPLn: PCA Capture Module Low Byte

| Bit   | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|--------------|-----|-----|-----|-----|-----|-----|

| Name  |     | PCA0CPn[7:0] |     |     |     |     |     |     |

| Туре  | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Addresses: PCA0CPL0 = 0xFB, PCA0CPL1 = 0xE9, PCA0CPL2 = 0xEB, PCA0CPL3 = 0xED, PCA0CPL4 = 0xFD, PCA0CPL5 = 0xD2

SFR Pages: PCA0CPL0 = 0x0, PCA0CPL1 = 0x0, PCA0CPL2 = 0x0, PCA0CPL3 = 0x0, PCA0CPL4 = 0x0, PCA0CPL5 = 0x0

| Bit   | Name                                                                            | Function                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | PCA0CPn[7:0]                                                                    | PCA Capture Module Low Byte.                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|       |                                                                                 | The PCA0CPLn register holds the low byte (LSB) of the 16-bit capture module n.<br>This register address also allows access to the low byte of the corresponding<br>PCA channel's auto-reload value for 9, 10, or 11-bit PWM mode. The ARSEL bit<br>in register PCA0PWM controls which register is accessed. |  |  |  |  |  |

| Note: | <b>Note:</b> A write to this register will clear the module's ECOMn bit to a 0. |                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

#### SFR Definition 26.8. PCA0CPHn: PCA Capture Module High Byte

| Bit   | 7   | 6             | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|---------------|-----|-----|-----|-----|-----|-----|

| Name  |     | PCA0CPn[15:8] |     |     |     |     |     |     |

| Туре  | R/W | R/W           | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0             | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Addresses: PCA0CPH0 = 0xFC, PCA0CPH1 = 0xEA, PCA0CPH2 = 0xEC, PCA0CPH3 = 0xEE, PCA0CPH4 = 0xFE, PCA0CPH5 = 0xD3

SFR Pages: PCA0CPH0 = 0x0, PCA0CPH1 = 0x0, PCA0CPH2 = 0x0, PCA0CPH3 = 0x0, PCA0CPH3 = 0x0, PCA0CPH5 = 0x0

| Bit  | Name                                                                   | Function                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0  | PCA0CPn[15:8]                                                          | PCA Capture Module High Byte.                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|      |                                                                        | The PCA0CPHn register holds the high byte (MSB) of the 16-bit capture module n.<br>This register address also allows access to the high byte of the corresponding<br>PCA channel's auto-reload value for 9, 10, or 11-bit PWM mode. The ARSEL bit in<br>register PCA0PWM controls which register is accessed. |  |  |  |  |  |

| Note | Note: A write to this register will set the module's ECOMn bit to a 1. |                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

## **CONTACT INFORMATION**

#### Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701

Please visit the Silicon Labs Technical Support web page: https://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc. Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.