Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | HCS12X                                                                 |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 80MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SCI, SPI              |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 91                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 4K x 8                                                                 |

| RAM Size                   | 14K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 112-LQFP                                                               |

| Supplier Device Package    | 112-LQFP (20x20)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12xd256cal |

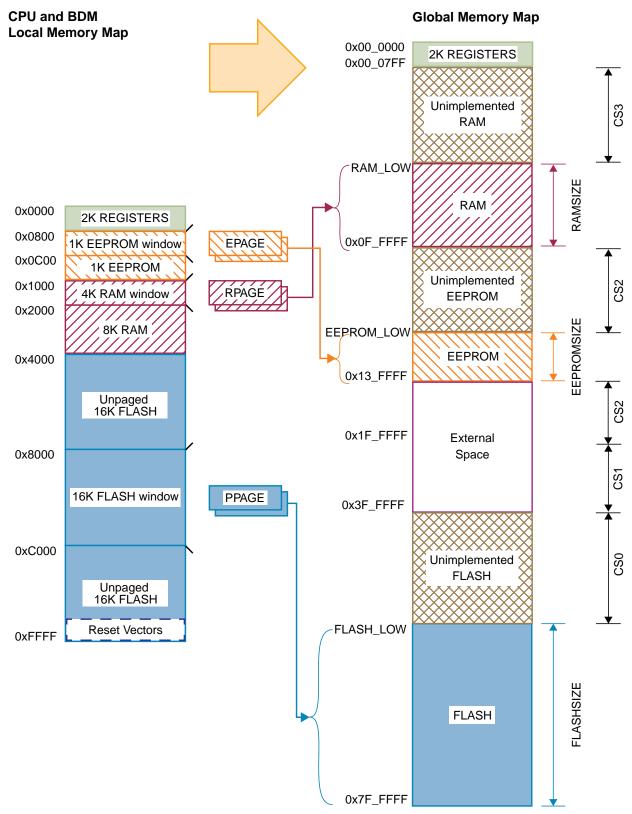

Figure 1-3. S12X CPU & BDM Global Address Mapping

MC9S12XDP512 Data Sheet, Rev. 2.21

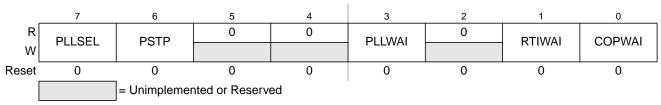

### 2.3.2.6 CRG Clock Select Register (CLKSEL)

This register controls CRG clock selection. Refer to Figure 2-17 for more details on the effect of each bit.

Figure 2-9. CRG Clock Select Register (CLKSEL)

Read: Anytime

Write: Refer to each bit for individual write conditions

**Table 2-4. CLKSEL Field Descriptions**

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PLLSEL | PLL Select Bit — Write anytime. Writing a1 when LOCK = 0 and AUTO = 1, or TRACK = 0 and AUTO = 0 has no effect This prevents the selection of an unstable PLLCLK as SYSCLK. PLLSEL bit is cleared when the MCU enters self clock mode, Stop mode or wait mode with PLLWAI bit set.  0 System clocks are derived from OSCCLK (Bus Clock = OSCCLK / 2).  1 System clocks are derived from PLLCLK (Bus Clock = PLLCLK / 2).                                                                                              |

| 6<br>PSTP   | Pseudo Stop Bit Write: Anytime This bit controls the functionality of the oscillator during stop mode.  O Oscillator is disabled in stop mode.  Oscillator continues to run in stop mode (pseudo stop).  Note: Pseudo stop mode allows for faster STOP recovery and reduces the mechanical stress and aging of the resonator in case of frequent STOP conditions at the expense of a slightly increased power consumption.                                                                                            |

| 3<br>PLLWAI | PLL Stops in Wait Mode Bit Write: Anytime If PLLWAI is set, the CRG will clear the PLLSEL bit before entering wait mode. The PLLON bit remains set during wait mode, but the PLL is powered down. Upon exiting wait mode, the PLLSEL bit has to be set manually if PLL clock is required. While the PLLWAI bit is set, the AUTO bit is set to 1 in order to allow the PLL to automatically lock on the selected target frequency after exiting wait mode.  O PLL keeps running in wait mode.  PLL stops in wait mode. |

| 1<br>RTIWAI | RTI Stops in Wait Mode Bit Write: Anytime 0 RTI keeps running in wait mode. 1 RTI stops and initializes the RTI dividers whenever the part goes into wait mode.                                                                                                                                                                                                                                                                                                                                                       |

| 0<br>COPWAI | COP Stops in Wait Mode Bit Normal modes: Write once Special modes: Write anytime 0 COP keeps running in wait mode. 1 COP stops and initializes the COP counter whenever the part goes into wait mode.                                                                                                                                                                                                                                                                                                                 |

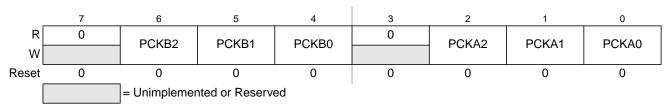

### **NOTE**

Register bits PCLK0 to PCLK7 can be written anytime. If a clock select is changed while a PWM signal is being generated, a truncated or stretched pulse can occur during the transition.

**Table 8-3. PWMCLK Field Descriptions**

| Field      | Description                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PCLK7 | Pulse Width Channel 7 Clock Select  0 Clock B is the clock source for PWM channel 7.  1 Clock SB is the clock source for PWM channel 7. |

| 6<br>PCLK6 | Pulse Width Channel 6 Clock Select  O Clock B is the clock source for PWM channel 6.  Clock SB is the clock source for PWM channel 6.   |

| 5<br>PCLK5 | Pulse Width Channel 5 Clock Select  O Clock A is the clock source for PWM channel 5.  Clock SA is the clock source for PWM channel 5.   |

| 4<br>PCLK4 | Pulse Width Channel 4 Clock Select  O Clock A is the clock source for PWM channel 4.  Clock SA is the clock source for PWM channel 4.   |

| 3<br>PCLK3 | Pulse Width Channel 3 Clock Select  O Clock B is the clock source for PWM channel 3.  Clock SB is the clock source for PWM channel 3.   |

| 2<br>PCLK2 | Pulse Width Channel 2 Clock Select  O Clock B is the clock source for PWM channel 2.  Clock SB is the clock source for PWM channel 2.   |

| 1<br>PCLK1 | Pulse Width Channel 1 Clock Select  0 Clock A is the clock source for PWM channel 1.  1 Clock SA is the clock source for PWM channel 1. |

| 0<br>PCLK0 | Pulse Width Channel 0 Clock Select  0 Clock A is the clock source for PWM channel 0.  1 Clock SA is the clock source for PWM channel 0. |

# 8.3.2.4 PWM Prescale Clock Select Register (PWMPRCLK)

This register selects the prescale clock source for clocks A and B independently.

Figure 8-6. PWM Prescale Clock Select Register (PWMPRCLK)

Read: Anytime Write: Anytime

#### 10 Freescale's Scalable Controller Area Network (S12MSCANV3)

Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1), except bits IDHITx, which are

read-only

### Table 10-16. CANIDAC Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                         |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:4<br>IDAM[1:0]  | Identifier Acceptance Mode — The CPU sets these flags to define the identifier acceptance filter organization (see Section 10.4.3, "Identifier Acceptance Filter"). Table 10-17 summarizes the different settings. In filter closed mode, no message is accepted such that the foreground buffer is never reloaded. |

| 2:0<br>IDHIT[2:0] | Identifier Acceptance Hit Indicator — The MSCAN sets these flags to indicate an identifier acceptance hit (see Section 10.4.3, "Identifier Acceptance Filter"). Table 10-18 summarizes the different settings.                                                                                                      |

**Table 10-17. Identifier Acceptance Mode Settings**

| IDAM1 | IDAM0 | Identifier Acceptance Mode     |  |  |

|-------|-------|--------------------------------|--|--|

| 0     | 0     | Two 32-bit acceptance filters  |  |  |

| 0     | 1     | Four 16-bit acceptance filters |  |  |

| 1     | 0     | Eight 8-bit acceptance filters |  |  |

| 1     | 1     | Filter closed                  |  |  |

**Table 10-18. Identifier Acceptance Hit Indication**

| IDHIT2 | IDHIT1 | IDHIT0 | Identifier Acceptance Hit |

|--------|--------|--------|---------------------------|

| 0      | 0      | 0      | Filter 0 hit              |

| 0      | 0      | 1      | Filter 1 hit              |

| 0      | 1      | 0      | Filter 2 hit              |

| 0      | 1      | 1      | Filter 3 hit              |

| 1      | 0      | 0      | Filter 4 hit              |

| 1      | 0      | 1      | Filter 5 hit              |

| 1      | 1      | 0      | Filter 6 hit              |

| 1      | 1      | 1      | Filter 7 hit              |

The IDHITx indicators are always related to the message in the foreground buffer (RxFG). When a message gets shifted into the foreground buffer of the receiver FIFO the indicators are updated as well.

# 10.3.2.13 MSCAN Reserved Register

This register is reserved for factory testing of the MSCAN module and is not available in normal system operation modes.

### 11 Serial Communication Interface (S12SCIV5)

- Programmable transmitter output parity

- Two receiver wakeup methods:

- Idle line wakeup

- Address mark wakeup

- Interrupt-driven operation with eight flags:

- Transmitter empty

- Transmission complete

- Receiver full

- Idle receiver input

- Receiver overrun

- Noise error

- Framing error

- Parity error

- Receive wakeup on active edge

- Transmit collision detect supporting LIN

- Break Detect supporting LIN

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

### 11.1.3 Modes of Operation

The SCI functions the same in normal, special, and emulation modes. It has two low power modes, wait and stop modes.

- Run mode

- Wait mode

- Stop mode

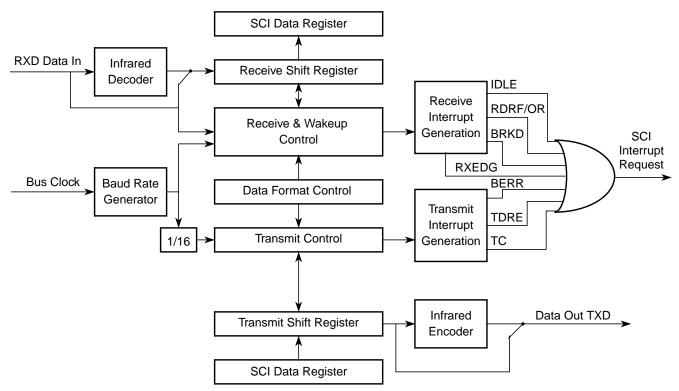

# 11.1.4 Block Diagram

Figure 11-1 is a high level block diagram of the SCI module, showing the interaction of various function blocks.

Figure 11-1. SCI Block Diagram

| Table 11-2 | IRSCL | Transmit | Pulse | Width |

|------------|-------|----------|-------|-------|

|            |       |          |       |       |

| TNP[1:0] | Narrow Pulse Width |

|----------|--------------------|

| 11       | 1/4                |

| 10       | 1/32               |

| 01       | 1/16               |

| 00       | 3/16               |

### 11.3.2.2 SCI Control Register 1 (SCICR1)

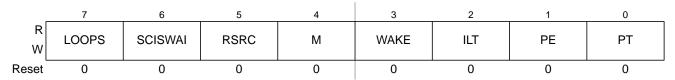

Figure 11-5. SCI Control Register 1 (SCICR1)

Read: Anytime, if AMAP = 0. Write: Anytime, if AMAP = 0.

### **NOTE**

This register is only visible in the memory map if AMAP = 0 (reset condition).

**Table 11-3. SCICR1 Field Descriptions**

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOOPS   | Loop Select Bit — LOOPS enables loop operation. In loop operation, the RXD pin is disconnected from the SCI and the transmitter output is internally connected to the receiver input. Both the transmitter and the receiver must be enabled to use the loop function.  O Normal operation enabled  1 Loop operation enabled  The receiver input is determined by the RSRC bit. |

| 6<br>SCISWAI | SCI Stop in Wait Mode Bit — SCISWAI disables the SCI in wait mode.  0 SCI enabled in wait mode  1 SCI disabled in wait mode                                                                                                                                                                                                                                                    |

| 5<br>RSRC    | Receiver Source Bit — When LOOPS = 1, the RSRC bit determines the source for the receiver shift register input. See Table 11-4.  O Receiver input internally connected to transmitter output  Receiver input connected externally to transmitter                                                                                                                               |

| 4<br>M       | Data Format Mode Bit — MODE determines whether data characters are eight or nine bits long.  One start bit, eight data bits, one stop bit  One start bit, nine data bits, one stop bit                                                                                                                                                                                         |

| 3<br>WAKE    | Wakeup Condition Bit — WAKE determines which condition wakes up the SCI: a logic 1 (address mark) in the most significant bit position of a received data character or an idle condition on the RXD pin.  O Idle line wakeup  1 Address mark wakeup                                                                                                                            |

### 19.4.5.3.3 Trace Buffer Reset State

The trace buffer contents are not initialized by a system reset. Thus should a system reset occur, the trace session information from immediately before the reset occurred can be read out. The DBGCNT bits are not cleared by a system reset. Thus should a reset occur, the number of valid lines in the trace buffer is indicated by DBGCNT. The internal pointer to the current trace buffer address is initialized by unlocking the trace buffer thus points to the oldest valid data even if a reset occurred during the tracing session. Generally debugging occurrences of system resets is best handled using mid or end-trigger alignment since the reset may occur before the trace trigger, which in the begin-trigger alignment case means no information would be stored in the trace buffer.

## **19.4.6 Tagging**

A tag follows program information as it advances through the instruction queue. When a tagged instruction reaches the head of the queue a tag hit occurs and triggers the state sequencer.

Each comparator control register features a TAG bit, which controls whether the comparator match will cause a trigger immediately or tag the opcode at the matched address. If a comparator is enabled for tagged comparisons, the address stored in the comparator match address registers must be an opcode address for the trigger to occur.

Both CPU and XGATE opcodes can be tagged with the comparator register TAG bits.

Using a begin-aligned trigger together with tagging, if the tagged instruction is about to be executed then the transition to the next state sequencer state occurs. If the transition is to the final state, tracing is started. Only upon completion of the tracing session can a breakpoint be generated. Similarly using a mid-aligned trigger with tagging, if the tagged instruction is about to be executed then the trace is continued for another 32 lines. Upon tracing completion the breakpoint is generated. Using an end-aligned trigger, when the tagged instruction is about to be executed and the next transition is to final state then a breakpoint is generated immediately, before the tagged instruction is carried out.

R/W monitoring is not useful for tagged operations since the trigger occurs based on the tagged opcode reaching the execution stage of the instruction queue. Similarly access size (SZ) monitoring and data bus monitoring is not useful if tagged triggering is selected, since the tag is attached to the opcode at the matched address and is not dependent on the data bus nor on the size of access. Thus these bits are ignored if tagged triggering is selected.

When configured for range comparisons and tagging, the ranges are accurate only to word boundaries.

CPU tagging is disabled when the BDM becomes active. Conversely, BDM firmware commands are not processed while tagging is active. XGATE tagging is possible when the BDM is active.

During BDM hardware accesses and whilst the BDM module is active, S12XCPU monitoring is disabled. Thus breakpoints, comparators, and bus tracing mapped to the S12XCPU are disabled but XGATE bus monitoring accessing the S12XDBG registers, including comparator registers, is still possible. While in active BDM or during hardware BDM accesses, XGATE activity can still be compared, traced and can be used to generate a breakpoint to the XGATE module. When the S12XCPU enters active BDM Mode through a BACKGROUND command, with the S12XDBG module armed, the S12XDBG remains armed.

The S12XDBG module tracing is disabled if the MCU is secure. However, breakpoints can still be generated if the MCU is secure.

| BDM<br>Enable | BDM<br>Active | MCU<br>Secure | Comparator Breakpoints Tagging Matches Enabled Possible Possible |            | Tracing<br>Possible |            |

|---------------|---------------|---------------|------------------------------------------------------------------|------------|---------------------|------------|

| х             | х             | 1             | Yes                                                              | Yes        | Yes                 | No         |

| 0             | 0             | 0             | Yes                                                              | Only SWI   | Yes                 | Yes        |

| 0             | 1             | 0             | Active BDM not possible when not enabled                         |            |                     | d          |

| 1             | 0             | 0             | Yes                                                              | Yes        | Yes                 | Yes        |

| 1             | 1             | 0             | XGATE only                                                       | XGATE only | XGATE only          | XGATE only |

**Table 20-1. Mode Dependent Restriction Summary**

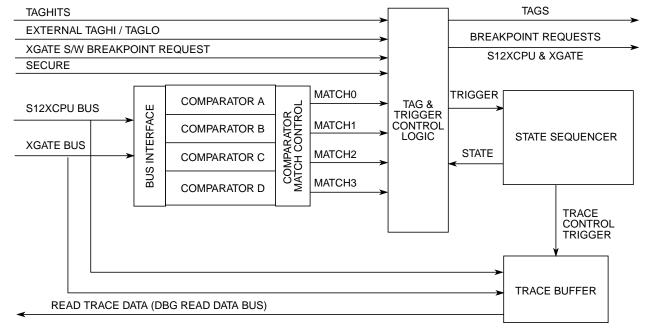

### 20.1.5 Block Diagram

Figure 20-1. Debug Module Block Diagram

# 20.2 External Signal Description

The S12XDBG sub-module features two external tag input signals. See Device User Guide (DUG) for the mapping of these signals to device pins. These tag pins may be used for the external tagging in emulation modes only.

MC9S12XDP512 Data Sheet, Rev. 2.21

### Table 21-3. Input Threshold Levels on External Signals

| ITHRS | External Signal            | NS       | SS                | NX                    | ES                  | EX                    | ST       |         |

|-------|----------------------------|----------|-------------------|-----------------------|---------------------|-----------------------|----------|---------|

|       | DATA[15:8]<br>TAGHI, TAGLO | Standard | Standard          |                       | Reduced             | Reduced               |          |         |

| 0     | DATA[7:0]                  |          |                   | Standard              | Standard Standard   | Standard              |          |         |

|       | EWAIT                      |          |                   |                       | Standard            | Standard              |          |         |

|       | DATA[15:8]<br>TAGHI, TAGLO |          | Standard Standard |                       | Reduced if HDBE = 1 | Reduced               | Reduced  | Reduced |

| 1     | DATA[7:0]                  | Standard |                   | Reduced               |                     |                       |          |         |

|       | EWAIT                      |          |                   | Reduced if EWAITE = 1 | Standard            | Reduced if EWAITE = 1 | Standard |         |

**Table 21-4. External Address Bus Size**

| ASIZ[4:0]  | Available External Address Lines |

|------------|----------------------------------|

| 00000      | None                             |

| 00001      | ŪDS                              |

| 00010      | ADDR1, UDS                       |

| 00011      | ADDR[2:1], UDS                   |

| :          | :                                |

| 10110      | ADDR[21:1], UDS                  |

| 10111      | ADDR[22:1], UDS                  |

| :<br>11111 |                                  |

| Register<br>Name |                             | Bit 7     | 6         | 5         | 4         | 3         | 2         | 1         | Bit 0     |

|------------------|-----------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Name             | R<br>W                      | DDR1AD07  | DDR1AD06  | DDR1AD05  | DDR1AD04  | DDR1AD03  | DDR1AD02  | DDR1AD01  | DDR1AD00  |

| Reserved         | R                           | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

|                  | W                           |           |           |           |           |           |           |           |           |

| RDR1AD0          | R<br>W                      | RDR1AD07  | RDR1AD06  | RDR1AD05  | RDR1AD04  | RDR1AD03  | RDR1AD02  | RDR1AD01  | RDR1AD00  |

| Reserved         | R                           | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

|                  | W                           |           |           |           |           |           |           |           |           |

| PER1AD0          | R<br>W                      | PER1AD07  | PER1AD06  | PER1AD05  | PER1AD04  | PER1AD03  | PER1AD02  | PER1AD01  | PER1AD00  |

| PT0AD1           | R<br>W                      | PT0AD123  | PT0AD122  | PT0AD121  | PT0AD120  | PT0AD119  | PT0AD118  | PT0AD117  | PT0AD116  |

| PT1AD1           | R<br>W                      | PT1AD115  | PT1AD114  | PT1AD113  | PT1AD112  | PT1AD111  | PT1AD110  | PT1AD19   | PT1AD18   |

| DDR0AD1          | R<br>W                      | DDR0AD123 | DDR0AD122 | DDR0AD121 | DDR0AD120 | DDR0AD119 | DDR0AD118 | DDR0AD117 | DDR0AD116 |

| DDR1AD1          | R<br>W                      | DDR1AD115 | DDR1AD114 | DDR1AD113 | DDR1AD112 | DDR1AD111 | DDR1AD110 | DDR1AD19  | DDR1AD18  |

| RDR0AD1          | R<br>W                      | RDR0AD123 | RDR0AD122 | RDR0AD121 | RDR0AD120 | RDR0AD119 | RDR0AD118 | RDR0AD117 | RDR0AD116 |

| RDR1AD1          | R<br>W                      | RDR1AD115 | RDR1AD114 | RDR1AD113 | RDR1AD112 | RDR1AD111 | RDR1AD110 | RDR1AD19  | RDR1AD18  |

| PER0AD1          | R<br>W                      | PER0AD123 | PER0AD122 | PER0AD121 | PER0AD120 | PER0AD119 | PER0AD118 | PER0AD117 | PER0AD116 |

| PER1AD1          | R<br>W                      | PER1AD115 | PER1AD114 | PER1AD113 | PER1AD112 | PER1AD111 | PER1AD110 | PER1AD19  | PER1AD18  |

|                  | = Unimplemented or Reserved |           |           |           |           |           |           |           |           |

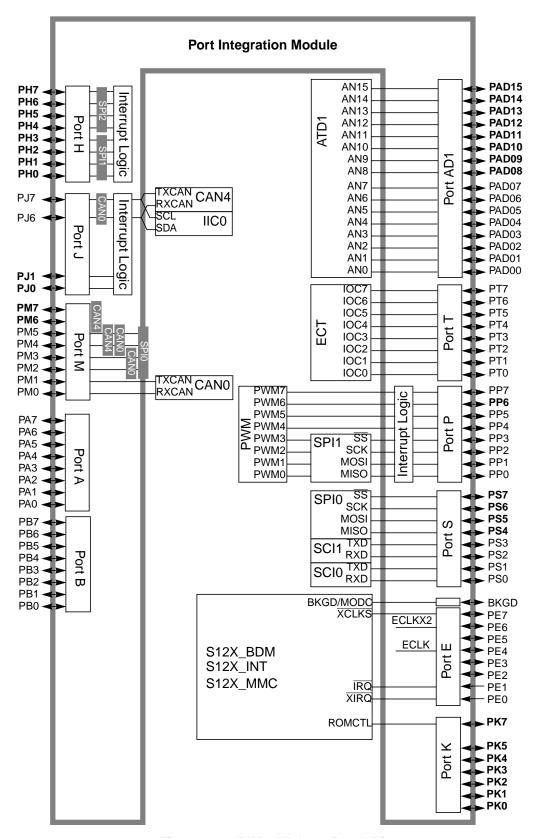

Figure 22-2. PIM Register Summary (Sheet 6 of 6)

Figure 24-1. PIM\_9XDG128 Block Diagram

### Table 24-1. Pin Functions and Priorities (Sheet 3 of 5)

| Port | Pin Name | Pin Function and Priority | I/O | Description                                                                                                                                 | Pin Function after Reset |  |

|------|----------|---------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|

| M    | DMZ      | TXCAN4                    | 0   | MSCAN4 transmit pin                                                                                                                         |                          |  |

|      | PM7      | GPIO                      | I/O | General-purpose I/O                                                                                                                         |                          |  |

|      | PM6      | RXCAN4                    | I   | MSCAN4 receive pin                                                                                                                          |                          |  |

|      | PIVIO    | GPIO                      | I/O | General-purpose I/O                                                                                                                         |                          |  |

|      |          | TXCAN0                    | 0   | MSCAN0 transmit pin                                                                                                                         |                          |  |

|      |          | TXCAN4                    | 0   | MSCAN4 transmit pin                                                                                                                         |                          |  |

|      | PM5      | SCK0                      | I/O | Serial Peripheral Interface 0 serial clock pin If CAN0 is routed to PM[3:2] the SPI0 can still be used in bidirectional master mode.        |                          |  |

|      |          | GPIO                      | I/O | General-purpose I/O                                                                                                                         |                          |  |

|      |          | RXCAN0                    | I   | MSCAN0 receive pin                                                                                                                          | GPIO                     |  |

|      |          | RXCAN4                    | I   | MSCAN4 receive pin                                                                                                                          |                          |  |

|      | PM4      | MOSI0                     | I/O | Serial Peripheral Interface 0 master out/slave in pin If CAN0 is routed to PM[3:2] the SPI0 can still be used in bidirectional master mode. |                          |  |

|      |          | GPIO                      | I/O | General-purpose I/O                                                                                                                         |                          |  |

|      |          | TXCAN0                    | 0   | MSCAN0 transmit pin                                                                                                                         |                          |  |

|      | PM3      | SS0                       | I/O | Serial Peripheral Interface 0 slave select output in master mode, input for slave mode or master mode.                                      |                          |  |

|      |          | GPIO                      | I/O | General-purpose I/O                                                                                                                         |                          |  |

|      |          | RXCAN0                    | I   | MSCAN0 receive pin                                                                                                                          |                          |  |

|      | PM2      | MISO0                     | I/O | Serial Peripheral Interface 0 master in/slave out pin                                                                                       |                          |  |

|      |          | GPIO                      | I/O | General-purpose I/O                                                                                                                         |                          |  |

|      | PM1      | TXCAN0                    | 0   | MSCAN0 transmit pin                                                                                                                         | -                        |  |

|      | FIVII    | GPIO                      | I/O | General-purpose I/O                                                                                                                         |                          |  |

|      | PM0      | RXCAN0                    | I   | MSCAN0 receive pin                                                                                                                          |                          |  |

|      | FIVIU    | GPIO                      | I/O | General-purpose I/O                                                                                                                         |                          |  |

Port K pin PE[7] is configured for reduced input threshold in certain modes (refer to S12X\_EBI section).

### NOTE

Port K is not available in 80-pin packages.

### 24.0.7.5 Port T

This port is associated with the ECT module. Port T pins PT[7:0] can be used for either general-purpose I/O, or with the channels of the enhanced capture timer.

### 24.0.7.6 Port S

This port is associated with SCI0, SCI1 and SPI0. Port S pins PS[7:0] can be used either for general-purpose I/O, or with the SCI and SPI subsystems.

The SPI0 pins can be re-routed. Refer to Section 24.0.5.33, "Module Routing Register (MODRR)".

#### NOTE

PS[7:4] are not available in 80-pin packages.

### 24.0.7.7 Port M

This port is associated with the CAN4 and 0 and SPI0. Port M pins PM[7:0] can be used for either general purpose I/O, or with the CAN, SCI and SPI subsystems.

The CAN0, CAN4 and SPI0 pins can be re-routed. *Refer to Section 24.0.5.33, "Module Routing Register (MODRR)"*.

#### NOTE

PM[7:6] are not available in 80-pin packages.

#### 24.0.7.8 Port P

This port is associated with the PWM, SPI1. Port P pins PP[7:0] can be used for either general purpose I/O, or with the PWM and SPI subsystems.

The pins are shared between the PWM channels and the SPI1. If the PWM is enabled the pins become PWM output channels with the exception of pin 7 which can be PWM input or output. If SPI1is enabled and PWM is disabled, the respective pin configuration is determined by status bits in the SPI.

The SPI1 pins can be re-routed. Refer to Section 24.0.5.33, "Module Routing Register (MODRR)".

Port P offers 8 I/O pins with edge triggered interrupt capability in wired-OR fashion (Section 24.0.8, "Pin Interrupts").

### NOTE

PP[6] is not available in 80-pin packages.

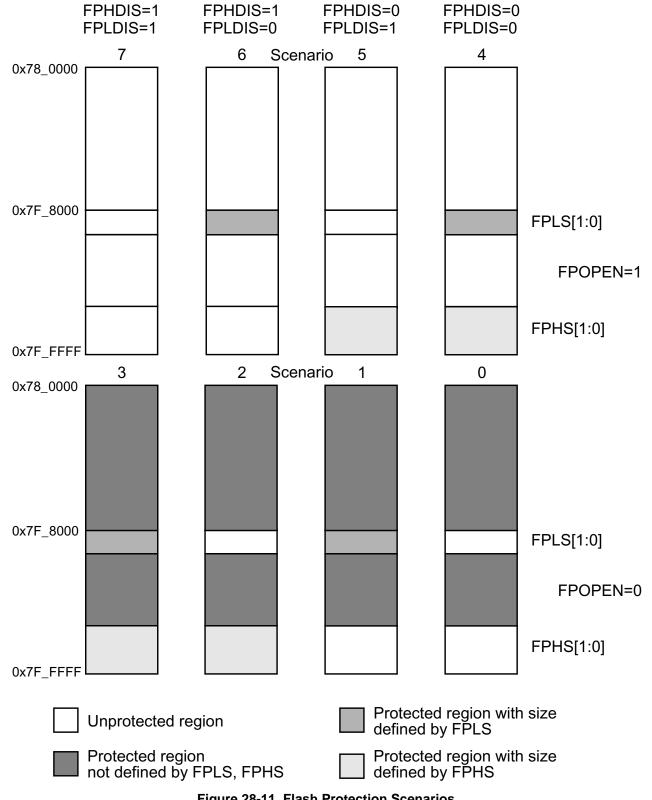

Figure 28-11. Flash Protection Scenarios

MC9S12XDP512 Data Sheet, Rev. 2.21

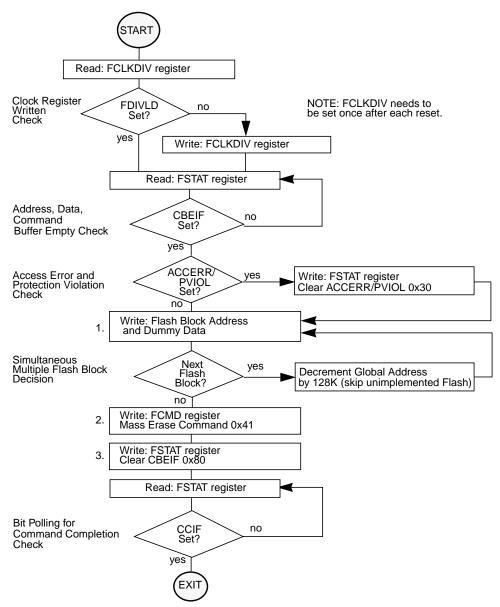

Figure 28-30. Example Mass Erase Command Flow

MC9S12XDP512 Data Sheet, Rev. 2.21

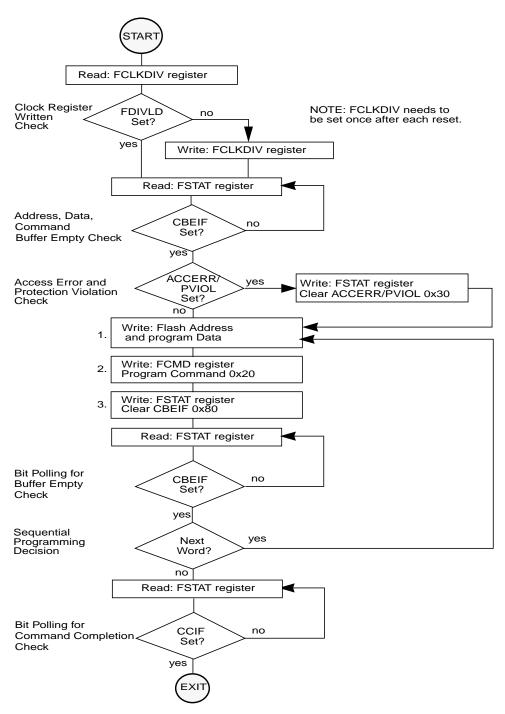

Figure 29-26. Example Program Command Flow

### 29.4.2.6 Sector Erase Abort Command

The sector erase abort operation will terminate the active sector erase operation so that other sectors in a Flash block are available for read and program operations without waiting for the sector erase operation to complete.

An example flow to execute the sector erase abort operation is shown in Figure 29-29. The sector erase abort command write sequence is as follows:

- 1. Write to any Flash block address to start the command write sequence for the sector erase abort command. The address and data written are ignored.

- 2. Write the sector erase abort command, 0x47, to the FCMD register.

- 3. Clear the CBEIF flag in the FSTAT register by writing a 1 to CBEIF to launch the sector erase abort command.

If the sector erase abort command is launched resulting in the early termination of an active sector erase operation, the ACCERR flag will set once the operation completes as indicated by the CCIF flag being set. The ACCERR flag sets to inform the user that the Flash sector may not be fully erased and a new sector erase command must be launched before programming any location in that specific sector. If the sector erase abort command is launched but the active sector erase operation completes normally, the ACCERR flag will not set upon completion of the operation as indicated by the CCIF flag being set. Therefore, if the ACCERR flag is not set after the sector erase abort command has completed, a Flash sector being erased when the abort command was launched will be fully erased. The maximum number of cycles required to abort a sector erase operation is equal to four FCLK periods (see Section 29.4.1.1, "Writing the FCLKDIV Register") plus five bus cycles as measured from the time the CBEIF flag is cleared until the CCIF flag is set.

#### NOTE

Since the ACCERR bit in the FSTAT register may be set at the completion of the sector erase abort operation, a command write sequence is not allowed to be buffered behind a sector erase abort command write sequence. The CBEIF flag will not set after launching the sector erase abort command to indicate that a command should not be buffered behind it. If an attempt is made to start a new command write sequence with a sector erase abort operation active, the ACCERR flag in the FSTAT register will be set. A new command write sequence may be started after clearing the ACCERR flag, if set.

#### NOTE

The sector erase abort command should be used sparingly since a sector erase operation that is aborted counts as a complete program/erase cycle.

Table A-9. shows the configuration of the peripherals for run current measurement.

### Table A-9. Peripheral Configurations for Run Supply Current Measurements

| Peripheral | Configuration                                                                                                                                                                                    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSCAN      | configured to loop-back mode using a bit rate of 1Mbit/s                                                                                                                                         |

| SPI        | configured to master mode,<br>continously transmit data (0x55 or<br>0xAA) at 1Mbit/s                                                                                                             |

| SCI        | configured into loop mode,<br>continously transmit data (0x55) at<br>speed of 57600 baud                                                                                                         |

| IIC        | operate in master mode and continously transmit data (0x55 or 0xAA) at the bit rate of 100Kbit/s                                                                                                 |

| PWM        | configured to toggle its pins at the rate of 40kHz                                                                                                                                               |

| ECT        | the peripheral shall be configured to output compare mode, Pulse accumulator and modulus counter enabled.                                                                                        |

| ATD        | the peripheral is configured to operate at its maximum specified frequency and to continuously convert voltages on all input channels in sequence.                                               |

| XGATE      | XGATE fetches code from RAM,<br>XGATE runs in an infinite loop, it<br>reads the Status and Flag registers<br>of CAN's, SPI's, SCI's in sequence<br>and does some bit manipulation on<br>the data |

| COP        | COP Warchdog Rate 2 <sup>24</sup>                                                                                                                                                                |

| RTI        | enabled, RTI Control Register<br>(RTICTL) set to \$FF                                                                                                                                            |

| API        | the module is configured to run from the RC oscillator clock source.                                                                                                                             |

| PIT        | PIT is enabled, Micro-timer register 0 and 1 loaded with \$0F and timer registers 0 to 3 are loaded with \$03/07/0F/1F.                                                                          |

| DBG        | the module is enabled and the comparators are configured to trigger in outside range. The range covers all the code executed by the core.                                                        |

MC9S12XDP512 Data Sheet, Rev. 2.21

# A.8 External Bus Timing

The following conditions are assumed for all following external bus timing values:

- Crystal input within 45% to 55% duty

- Equal loads of pins

- Pad full drive (reduced drive must be off)

# A.8.1 Normal Expanded Mode (External Wait Feature Disabled)

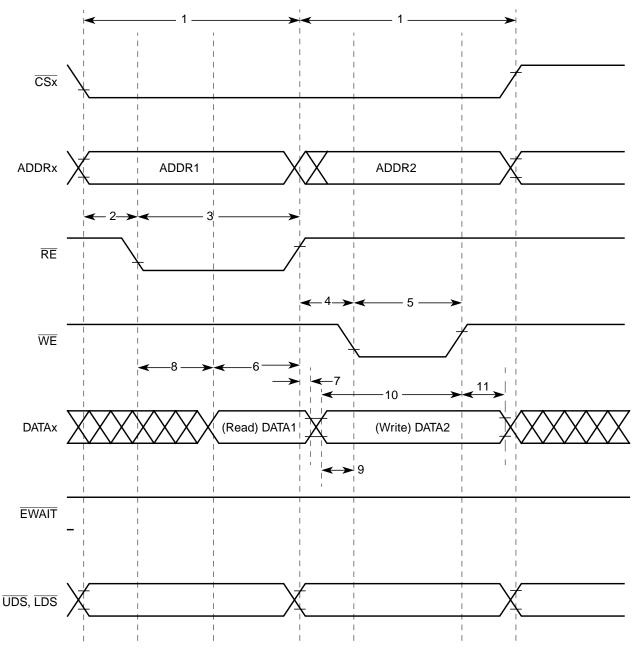

Figure A-11. Example 1a: Normal Expanded Mode — Read Followed by Write