Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HCS12X                                                      |

| Core Size                  | 16-Bit                                                      |

| Speed                      | 80MHz                                                       |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SCI, SPI   |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 91                                                          |

| Program Memory Size        | 256KB (256K x 8)                                            |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 4K x 8                                                      |

| RAM Size                   | 14K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.5V                                                |

| Data Converters            | A/D 16x10b                                                  |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 112-LQFP                                                    |

| Supplier Device Package    | 112-LQFP (20x20)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12xd256val |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# BHI

# Branch if Higher

# BHI

## Operation

If C | Z = 0, then PC +  $0002 + (REL9 \le 1) \Rightarrow PC$

Branch instruction to compare unsigned numbers.

Branch if RS1 > RS2:

SUB R0,RS1,RS2 BHI REL9

## **CCR Effects**

- N: Not affected.

- Z: Not affected.

- V: Not affected.

- C: Not affected.

## Code and CPU Cycles

| Source Form | Address<br>Mode |   |   |   |   |   |   | Mad | chine Code | Cycles |

|-------------|-----------------|---|---|---|---|---|---|-----|------------|--------|

| BHI REL9    | REL9            | 0 | 0 | 1 | 1 | 0 | 0 | 0   | REL9       | PP/P   |

#### Subtract Immediate 8 bit Constant (High Byte)

#### Operation

RD - IMM8:  $\$00 \Rightarrow RD$

Subtracts a signed immediate 8 bit constant from the content of high byte of register RD and using binary subtraction and stores the result in the high byte of destination register RD. This instruction can be used after an SUBL for a 16 bit immediate subtraction.

Example:

SUBLR2,#LOWBYTESUBHR2,#HIGHBYTE; R2 = R2 - 16 bit immediate

#### **CCR Effects**

| Ν | Ζ | V | С |

|---|---|---|---|

|   |   |   |   |

| $\Delta$ $\Delta$ $\Delta$ | $\Delta \Delta$ |

|----------------------------|-----------------|

|----------------------------|-----------------|

- N: Set if bit 15 of the result is set; cleared otherwise.

- Z: Set if the result is \$0000; cleared otherwise.

- V: Set if a two's complement overflow resulted from the operation; cleared otherwise.  $RD[15]_{old} \& \overline{IMM8[7]} \& \overline{RD[15]}_{new} | \overline{RD[15]}_{old} \& IMM8[7] \& RD[15]_{new}$

- C: Set if there is a carry from the bit 15 of the result; cleared otherwise.  $\overline{\text{RD}[15]}_{\text{old}} \& \text{IMM8[7]} | \overline{\text{RD}[15]}_{\text{old}} \& \text{RD}[15]_{\text{new}} | \text{IMM8[7]} \& \text{RD}[15]_{\text{new}}$

#### **Code and CPU Cycles**

| Source Form    | Address<br>Mode |   |   |   |   |   | Machin | e Code | Cycles |

|----------------|-----------------|---|---|---|---|---|--------|--------|--------|

| SUBH RD, #IMM8 | IMM8            | 1 | 1 | 0 | 0 | 1 | RD     | IMM8   | Р      |

#### \*8 Pulse-Width Modulator (S12PWM8B8CV1)

Either left aligned or center aligned output mode can be used in concatenated mode and is controlled by the low order CAEx bit. The high order CAEx bit has no effect.

Table 8-11 is used to summarize which channels are used to set the various control bits when in 16-bit mode.

| CONxx | PWMEx | PPOLx | PCLKx | CAEx | PWMx<br>Output |

|-------|-------|-------|-------|------|----------------|

| CON67 | PWME7 | PPOL7 | PCLK7 | CAE7 | PWM7           |

| CON45 | PWME5 | PPOL5 | PCLK5 | CAE5 | PWM5           |

| CON23 | PWME3 | PPOL3 | PCLK3 | CAE3 | PWM3           |

| CON01 | PWME1 | PPOL1 | PCLK1 | CAE1 | PWM1           |

Table 8-11. 16-bit Concatenation Mode Summary

#### 8.4.2.8 PWM Boundary Cases

Table 8-12 summarizes the boundary conditions for the PWM regardless of the output mode (left aligned or center aligned) and 8-bit (normal) or 16-bit (concatenation).

| PWMDTYx                     | PWMPERx                                    | PPOLx | PWMx Output |

|-----------------------------|--------------------------------------------|-------|-------------|

| \$00<br>(indicates no duty) | >\$00                                      | 1     | Always low  |

| \$00<br>(indicates no duty) | >\$00                                      | 0     | Always high |

| XX                          | \$00 <sup>1</sup><br>(indicates no period) | 1     | Always high |

| XX                          | \$00 <sup>1</sup><br>(indicates no period) | 0     | Always low  |

| >= PWMPERx                  | XX                                         | 1     | Always high |

| >= PWMPERx                  | XX                                         | 0     | Always low  |

Table 8-12. PWM Boundary Cases

<sup>1</sup> Counter = \$00 and does not count.

# 8.5 Resets

The reset state of each individual bit is listed within the Section 8.3.2, "Register Descriptions" which details the registers and their bit-fields. All special functions or modes which are initialized during or just following reset are described within this section.

- The 8-bit up/down counter is configured as an up counter out of reset.

- All the channels are disabled and all the counters do not count.

#### 11 Serial Communication Interface (S12SCIV5)

#### 11.4.6.6.1 Idle Input line Wakeup (WAKE = 0)

In this wakeup method, an idle condition on the RXD pin clears the RWU bit and wakes up the SCI. The initial frame or frames of every message contain addressing information. All receivers evaluate the addressing information, and receivers for which the message is addressed process the frames that follow. Any receiver for which a message is not addressed can set its RWU bit and return to the standby state. The RWU bit remains set and the receiver remains on standby until another idle character appears on the RXD pin.

Idle line wakeup requires that messages be separated by at least one idle character and that no message contains idle characters.

The idle character that wakes a receiver does not set the receiver idle bit, IDLE, or the receive data register full flag, RDRF.

The idle line type bit, ILT, determines whether the receiver begins counting logic 1s as idle character bits after the start bit or after the stop bit. ILT is in SCI control register 1 (SCICR1).

#### 11.4.6.6.2 Address Mark Wakeup (WAKE = 1)

In this wakeup method, a logic 1 in the most significant bit (MSB) position of a frame clears the RWU bit and wakes up the SCI. The logic 1 in the MSB position marks a frame as an address frame that contains addressing information. All receivers evaluate the addressing information, and the receivers for which the message is addressed process the frames that follow. Any receiver for which a message is not addressed can set its RWU bit and return to the standby state. The RWU bit remains set and the receiver remains on standby until another address frame appears on the RXD pin.

The logic 1 MSB of an address frame clears the receiver's RWU bit before the stop bit is received and sets the RDRF flag.

Address mark wakeup allows messages to contain idle characters but requires that the MSB be reserved for use in address frames.

#### NOTE

With the WAKE bit clear, setting the RWU bit after the RXD pin has been idle can cause the receiver to wake up immediately.

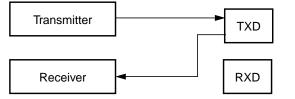

# 11.4.7 Single-Wire Operation

Normally, the SCI uses two pins for transmitting and receiving. In single-wire operation, the RXD pin is disconnected from the SCI. The SCI uses the TXD pin for both receiving and transmitting.

Figure 11-30. Single-Wire Operation (LOOPS = 1, RSRC = 1)

# 12.4 Functional Description

The SPI module allows a duplex, synchronous, serial communication between the MCU and peripheral devices. Software can poll the SPI status flags or SPI operation can be interrupt driven.

The SPI system is enabled by setting the SPI enable (SPE) bit in SPI control register 1. While SPE is set, the four associated SPI port pins are dedicated to the SPI function as:

- Slave select  $(\overline{SS})$

- Serial clock (SCK)

- Master out/slave in (MOSI)

- Master in/slave out (MISO)

The main element of the SPI system is the SPI data register. The 8-bit data register in the master and the 8-bit data register in the slave are linked by the MOSI and MISO pins to form a distributed 16-bit register. When a data transfer operation is performed, this 16-bit register is serially shifted eight bit positions by the S-clock from the master, so data is exchanged between the master and the slave. Data written to the master SPI data register becomes the output data for the slave, and data read from the master SPI data register after a transfer operation is the input data from the slave.

A read of SPISR with SPTEF = 1 followed by a write to SPIDR puts data into the transmit data register. When a transfer is complete and SPIF is cleared, received data is moved into the receive data register. This 8-bit data register acts as the SPI receive data register for reads and as the SPI transmit data register for writes. A single SPI register address is used for reading data from the read data buffer and for writing data to the transmit data register.

The clock phase control bit (CPHA) and a clock polarity control bit (CPOL) in the SPI control register 1 (SPICR1) select one of four possible clock formats to be used by the SPI system. The CPOL bit simply selects a non-inverted or inverted clock. The CPHA bit is used to accommodate two fundamentally different protocols by sampling data on odd numbered SCK edges or on even numbered SCK edges (see Section 12.4.3, "Transmission Formats").

The SPI can be configured to operate as a master or as a slave. When the MSTR bit in SPI control register 1 is set, master mode is selected, when the MSTR bit is clear, slave mode is selected.

## NOTE

A change of CPOL or MSTR bit while there is a received byte pending in the receive shift register will destroy the received byte and must be avoided.

| Chip Modes            | ROMON | EROMON                                                                                                   | DATA SOURCE <sup>1</sup> | Stretch <sup>2</sup> |

|-----------------------|-------|----------------------------------------------------------------------------------------------------------|--------------------------|----------------------|

| Normal Single Chip    | Х     | XInternal Flash0Emulation Memory1Internal FlashXExternal ApplicationXInternal FlashXExternal Application |                          | N                    |

| Special Single Chip   |       |                                                                                                          |                          |                      |

| Emulation Single Chip | Х     | 0                                                                                                        | Emulation Memory         | N                    |

|                       | Х     | 1                                                                                                        | Internal Flash           |                      |

| Normal Expanded       | 0     | Х                                                                                                        | External Application     | Y                    |

|                       | 1     | Х                                                                                                        | Internal Flash           | N                    |

| Emulation Expanded    | 0     | Х                                                                                                        | External Application     | Y                    |

|                       | 1     | 0                                                                                                        | Emulation Memory         | N                    |

|                       | 1     | 1                                                                                                        | Internal Flash           |                      |

| Special Test          | 0     | Х                                                                                                        | External Application     | N                    |

|                       | 1     | Х                                                                                                        | Internal Flash           |                      |

Table 18-11. Data Sources when CPU or BDM is Accessing Flash Area

<sup>1</sup> Internal Flash means Flash resources inside the MCU are read/written. Emulation memory means resources inside the emulator are read/written (PRU registers, flash replacement, RAM, EEPROM and register space are always considered internal). External application means resources residing outside the MCU are read/written.

<sup>2</sup> The external access stretch mechanism is part of the EBI module (refer to EBI Block Guide for details).

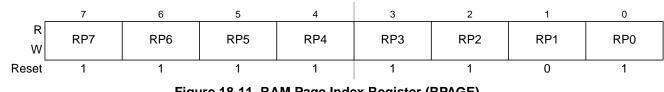

## 18.3.2.6 RAM Page Index Register (RPAGE)

Address: 0x0016

Figure 18-11. RAM Page Index Register (RPAGE)

Read: Anytime

Write: Anytime

These eight index bits are used to page 4 KByte blocks into the RAM page window located in the local (CPU or BDM) memory map from address 0x1000 to address 0x1FFF (see Figure 18-12). This supports accessing up to 1022 Kbytes of RAM (in the Global map) within the 64 KByte Local map. The RAM page index register is effectively used to construct paged RAM addresses in the Local map format.

#### CAUTION

XGATE write access to this register during an CPU access which makes use of this register could lead to unexpected results.

## 19.4.7.5 DBG Breakpoint Priorities

XGATE software breakpoints have the highest priority. Active tracing sessions are terminated immediately.

If a TRIG triggers occur after begin or mid aligned tracing has already been triggered by a comparator instigated transition to final state, then TRIG no longer has an effect. When the associated tracing session is complete, the breakpoint occurs. Similarly if a TRIG is followed by a subsequent trigger from a comparator channel whose BRK=0, it has no effect, since tracing has already started.

If a comparator tag hit occurs simultaneously with an external TAGHI/TAGLO hit, the state sequencer enters State0. TAGHI/TAGLO triggers are always end aligned, to end tracing immediately, independent of the tracing trigger alignment bits TALIGN[1:0].

#### 19.4.7.5.1 DBG Breakpoint priorities, mapping and BDM interfacing

Breakpoint operation is dependent on the state of the BDM module. If the BDM module is active, the CPU is executing out of BDM firmware and S12X breakpoints are disabled. In addition, while executing a BDM TRACE command, tagging into BDM is disabled.

| DBGBRK[1]<br>(DBGC1[3]) <sup>1</sup> | BDM bit<br>(DBGC1[4]) | BDM<br>enabled | BDM active | Type of Debug Session                           |

|--------------------------------------|-----------------------|----------------|------------|-------------------------------------------------|

| 0                                    | Х                     | Х              | Х          | No Breakpoint                                   |

| 1                                    | 0                     | 0              | 0          | Breakpoint to SWI                               |

| 1                                    | 0                     | 1              | Х          | Illegal Configuration. Do Not Use. <sup>2</sup> |

| 1                                    | 1                     | 0              | 0          | Illegal Configuration. Do Not Use. <sup>3</sup> |

| 1                                    | 1                     | 1              | 0          | Breakpoint to BDM                               |

| 1                                    | 1                     | 1              | 1          | No Breakpoint                                   |

Table 19-45. Breakpoint Mapping Summary

<sup>1</sup> All sources except XGATE software BKP, which are independent of this bit.

<sup>2</sup>The DBGC1[4] bit (BDM) must be set if using the BDM interface together with the DBG module. Failure to set this bit could result in XGATE generated breakpoints to SWI during BDM firmware execution corrupting the S12X PC return address, should the user have entered BDM via the BACKGROUND command or BGND instruction.

<sup>3</sup>End aligned tagged Breakpoint to SWI. Begin, Mid aligned and Forced Breakpoints disabled

If BDM is not active, the breakpoint will give priority to BDM requests over SWI requests if the breakpoint happens to coincide with a SWI instruction in the user's code. On returning from BDM, the SWI from user

happens to coincide with a SWI instruction in the user's code. On returning from BDM, the SWI from user code gets executed.

BDM cannot be entered from a breakpoint unless the ENABLE bit is set in the BDM. If entry to BDM via a BGND instruction is attempted and the ENABLE bit in the BDM is cleared, the CPU actually executes the BDM firmware code. It checks the ENABLE and returns if ENABLE is not set. If not serviced by the monitor then the breakpoint is re-asserted when the BDM returns to normal CPU flow.

If the comparator register contents coincide with the SWI/BDM vector address then an SWI in user code and DBG breakpoint could occur simultaneously. The CPU ensures that BDM requests have a higher priority than SWI requests. Returning from the BDM/SWI service routine care must be taken to avoid re-triggering a breakpoint.

| ITHRS | External Signal                        | NS       | SS       | NX                       | ES       | EX                       | ST       |

|-------|----------------------------------------|----------|----------|--------------------------|----------|--------------------------|----------|

|       | DATA[15:8]<br>TAGHĪ, TAGLO<br>Standard |          | Reduced  | Reduced                  |          |                          |          |

| 0     | DATA[7:0]                              | Standard | Standard | Standard                 |          |                          | Standard |

|       | EWAIT                                  |          |          |                          | Standard | Standard                 |          |

|       | Data[15:8]<br>Taghi, Taglo             |          |          | Reduced<br>if HDBE = 1   | Reduced  | Reduced                  | Reduced  |

| 1     | DATA[7:0]                              | Standard | Standard | Reduced                  |          |                          |          |

|       | EWAIT                                  |          |          | Reduced<br>if EWAITE = 1 | Standard | Reduced<br>if EWAITE = 1 | Standard |

Table 21-3. Input Threshold Levels on External Signals

#### Table 21-4. External Address Bus Size

| ASIZ[4:0]  | Available External Address Lines |

|------------|----------------------------------|

| 00000      | None                             |

| 00001      | UDS                              |

| 00010      | ADDR1, UDS                       |

| 00011      | ADDR[2:1], UDS                   |

| :          | :                                |

| 10110      | ADDR[21:1], UDS                  |

| 10111      | ADDR[22:1], UDS                  |

| :<br>11111 |                                  |

# 21.4.2.2.2 Write Access Timing

|                           | Acce       | ss #0     | Acce   | ss #1    | Access #2 |          |  |

|---------------------------|------------|-----------|--------|----------|-----------|----------|--|

| Bus cycle ->              | <br>1      |           | 2      | 2        | 3         |          |  |

| ECLK phase                | <br>high   | low       | high   | low      | high      | low      |  |

| ADDR[22:20] / ACC[2:0]    |            | acc 0     |        | acc 1    |           | acc 2    |  |

| ADDR[19:16] / IQSTAT[3:0] | <br>addr 0 | iqstat -1 | addr 1 | iqstat 0 | addr 2    | iqstat 1 |  |

| ADDR[15:0] / IVD[15:0]    |            | ?         |        | x        |           | х        |  |

| DATA[15:0] (write)        | <br>?      | dat       | data 0 |          | a 1       | data 2   |  |

| R/W                       | <br>0      | 0         | 1      | 1        | 1         | 1        |  |

Table 21-12. Write Access (1 Cycle)

#### Table 21-13. Write Access (2 Cycles)

|                           |            | Acce     | ss #0  |          | Acce   | ss #1 |  |

|---------------------------|------------|----------|--------|----------|--------|-------|--|

| Bus cycle ->              | <br>1      |          | 2      |          | 3      |       |  |

| ECLK phase                | <br>high   | low      | high   | low      | high   | low   |  |

| ADDR[22:20] / ACC[2:0]    |            | acc 0    |        | 000      |        | acc 1 |  |

| ADDR[19:16] / IQSTAT[3:0] | <br>addr 0 | iqstat-1 | addr 0 | iqstat 0 | addr 1 | 0000  |  |

| ADDR[15:0] / IVD[15:0]    |            | ?        |        | x        |        | x     |  |

| DATA[15:0] (write)        | <br>?      | data 0   |        |          | х      |       |  |

| R/W                       | <br>0      | 0        | 0      | 0        | 1      | 1     |  |

#### Table 21-14. Write Access (n-1 Cycles)

|                           |              |          | Acc    | ess #0   |        |      | Acce       | ss #1 |  |

|---------------------------|--------------|----------|--------|----------|--------|------|------------|-------|--|

| Bus cycle ->              | <br>1        |          | 2      |          | 3      |      | <br>n      |       |  |

| ECLK phase                | <br>high     | low      | high   | low      | high   | low  | <br>high   | low   |  |

| ADDR[22:20] / ACC[2:0]    |              | acc 0    |        | 000      |        | 000  |            | acc 1 |  |

| ADDR[19:16] / IQSTAT[3:0] | <br>addr 0   | iqstat-1 | addr 0 | iqstat 0 | addr 0 | 0000 | <br>addr 1 | 0000  |  |

| ADDR[15:0] / IVD[15:0]    |              | ?        |        | x        |        | x    |            | x     |  |

| DATA[15:0] (write)        | <br>? data 0 |          | х      |          |        |      |            |       |  |

| R/W                       | <br>0        | 0        | 0      | 0        | 0      | 0    | <br>1      | 1     |  |

# 21.5.2 Emulation Modes

In emulation mode applications, the development systems use a custom PRU device to rebuild the single-chip or expanded bus functions which are lost due to the use of the external bus with an emulator.

Accesses to a set of registers controlling the related ports in normal modes (refer to SoC section) are directed to the external bus in emulation modes which are substituted by PRR as part of the PRU. Accesses to these registers take a constant time of 2 cycles.

Depending on the setting of ROMON and EROMON (refer to S12X\_MMC section), the program code can be executed from internal memory or an optional external emulation memory (EMULMEM). No wait state operation (stretching) of the external bus access is done in emulation modes when accessing internal memory or emulation memory addresses.

In both modes observation of the internal operation is supported through the external bus (internal visibility).

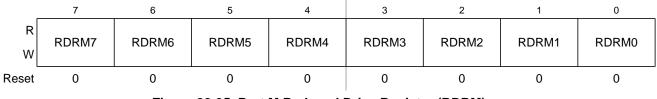

# 22.3.2.33 Port M Reduced Drive Register (RDRM)

Read: Anytime.

Write: Anytime.

This register configures the drive strength of each Port M output pin as either full or reduced. If the port is used as input this bit is ignored.

| Field            | Description                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>RDRM[7:0] | <ul> <li>Reduced Drive Port M</li> <li>Full drive strength at output.</li> <li>Associated pin drives at about 1/6 of the full drive strength.</li> </ul> |

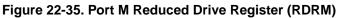

# 22.3.2.34 Port M Pull Device Enable Register (PERM)

Figure 22-36. Port M Pull Device Enable Register (PERM)

Read: Anytime.

Write: Anytime.

This register configures whether a pull-up or a pull-down device is activated, if the port is used as input or wired-OR output. This bit has no effect if the port is used as push-pull output. Out of reset no pull device is enabled.

| Field     | Description                                        |

|-----------|----------------------------------------------------|

| 7–0       | Pull Device Enable Port M                          |

| PERM[7:0] | 0 Pull-up or pull-down device is disabled.         |

|           | 1 Either a pull-up or pull-down device is enabled. |

Chapter 22 DP512 Port Integration Module (S12XDP512PIMV2)

#### Table 23-42. PPSP Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0       | Polarity Select Port P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PPSP[7:0] | <ol> <li>Falling edge on the associated port P pin sets the associated flag bit in the PIFP register. A pull-up device is connected to the associated port P pin, if enabled by the associated bit in register PERP and if the port is used as input.</li> <li>Rising edge on the associated port P pin sets the associated flag bit in the PIFP register. A pull-down device is connected to the associated port P pin, if enabled by the associated bit in register PERP and if the port is used as input.</li> </ol> |

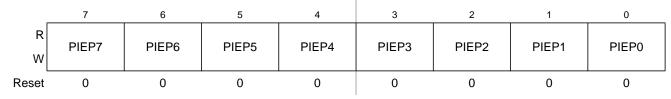

## 23.0.5.44 Port P Interrupt Enable Register (PIEP)

Figure 23-46. Port P Interrupt Enable Register (PIEP)

Read: Anytime.

Write: Anytime.

This register disables or enables on a per-pin basis the edge sensitive external interrupt associated with Port P.

| Table 23-43. | PIEP | Field | Descriptions |

|--------------|------|-------|--------------|

|              |      |       |              |

| Field | Description                                                                 |

|-------|-----------------------------------------------------------------------------|

|       | Interrupt Enable Port P<br>0 Interrupt is disabled (interrupt flag masked). |

|       | 1 Interrupt is enabled.                                                     |

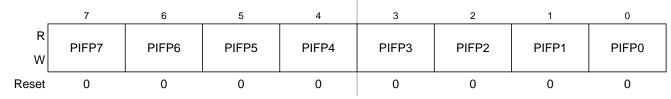

## 23.0.5.45 Port P Interrupt Flag Register (PIFP)

Figure 23-47. Port P Interrupt Flag Register (PIFP)

Read: Anytime.

Write: Anytime.

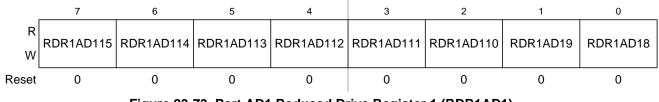

## 23.0.5.71 Port AD1 Reduced Drive Register 1 (RDR1AD1)

Figure 23-73. Port AD1 Reduced Drive Register 1 (RDR1AD1)

Read: Anytime.

Write: Anytime.

This register configures the drive strength of each PAD[15:8] output pin as either full or reduced. If the port is used as input this bit is ignored.

| Table 23-64. RDR | 1AD1 Field | Descriptions |

|------------------|------------|--------------|

|------------------|------------|--------------|

| Field                | Description                                                                                                                     |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>RDR1AD1[15:8] | Reduced Drive Port AD1 Register 10Full drive strength at output.1Associated pin drives at about 1/6 of the full drive strength. |

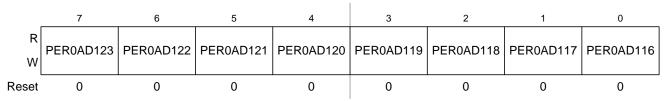

# 23.0.5.72 Port AD1 Pull Up Enable Register 0 (PER0AD1)

Figure 23-74. Port AD1 Pull Up Enable Register 0 (PER0AD1)

Read: Anytime.

Write: Anytime.

This register activates a pull-up device on the respective PAD[23:16] pin if the port is used as input. This bit has no effect if the port is used as output. Out of reset no pull-up device is enabled.

#### Table 23-65. PER0AD1 Field Descriptions

| Field | Description                                                                                                       |

|-------|-------------------------------------------------------------------------------------------------------------------|

|       | Pull Device Enable Port AD1 Register 0         0 Pull-up device is disabled.         1 Pull-up device is enabled. |

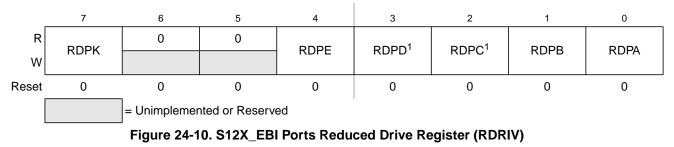

## 24.0.5.8 S12X\_EBI Ports Reduced Drive Register (RDRIV)

1. Register implemented, function disabled: Written values can be read back.

Read: Anytime.

Write: Anytime.

This register is used to select reduced drive for the pins associated with ports A, B, E, and K. If enabled, the pins drive at about 1/6 of the full drive strength. The reduced drive function is independent of which function is being used on a particular pin.

The reduced drive functionality does not take effect on the pins in emulation modes.

#### Table 24-11. RDRIV Field Descriptions

| Field     | Description                                                                                                                                     |  |  |  |  |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 7<br>RDPK | Reduced Drive of Port K         0 All port K output pins have full drive enabled.         1 All port K output pins have reduced drive enabled.  |  |  |  |  |  |  |  |  |

| 4<br>RDPE | Reduced Drive of Port E         0 All port E output pins have full drive enabled.         1 All port E output pins have reduced drive enabled.  |  |  |  |  |  |  |  |  |

| 1<br>RDPB | Reduced Drive of Port B         0 All port B output pins have full drive enabled.         1 All port B output pins have reduced drive enabled.  |  |  |  |  |  |  |  |  |

| 0<br>RDPA | Reduced Drive of Ports A         0 All Port A output pins have full drive enabled.         1 All port A output pins have reduced drive enabled. |  |  |  |  |  |  |  |  |

## 24.0.7.9 Port H

This port is associated with the SPI1, . Port H pins PH[7:0] can be used for either general purpose I/O, or with the SPI and SCI subsystems. Port H pins can be used with the routed SPI1. *Refer to Section 24.0.5.33, "Module Routing Register (MODRR)"*.

Port H offers 8 I/O pins with edge triggered interrupt capability (Section 24.0.8, "Pin Interrupts").

#### NOTE

Port H is not available in 80-pin packages.

## 24.0.7.10 Port J

This port is associated with CAN4, CAN0, IIC0. Port J pins PJ[7:4] and PJ[2:0] can be used for either general purpose I/O, or with the CAN, IIC, or SCI subsystems. If IIC takes precedence the associated pins become IIC open-drain output pins. The CAN4 pins can be re-routed. *Refer to Section 24.0.5.33, "Module Routing Register (MODRR)"*.

Port J pins can be used with the routed CAN0 modules. *Refer to Section 24.0.5.33, "Module Routing Register (MODRR)"*.

Port J offers 7 I/O pins with edge triggered interrupt capability (Section 24.0.8, "Pin Interrupts").

#### NOTE

PJ[5,4,2,1,0] are not available in 80-pin packages.

#### 24.0.7.11 Port AD1

This port is associated with the ATD1. Port AD1 pins PAD15–PAD0 can be used for either general purpose I/O, or with the ATD1 subsystem.

#### NOTE

PAD[15:8] are not available in 80-pin packages.

# 24.0.8 Pin Interrupts

Ports P, H and J offer pin interrupt capability. The interrupt enable as well as the sensitivity to rising or falling edges can be individually configured on per-pin basis. All bits/pins in a port share the same interrupt vector. Interrupts can be used with the pins configured as inputs or outputs.

An interrupt is generated when a bit in the port interrupt flag register and its corresponding port interrupt enable bit are both set. The pin interrupt feature is also capable to wake up the CPU when it is in STOP or WAIT mode.

A digital filter on each pin prevents pulses (Figure 24-70) shorter than a specified time from generating an interrupt. The minimum time varies over process conditions, temperature and voltage (Figure 24-69 and Table 24-62).

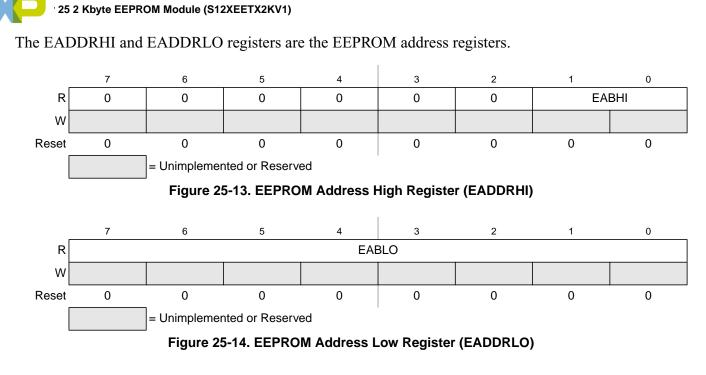

All EABHI and EABLO bits read 0 and are not writable in normal modes.

All EABHI and EABLO bits are readable and writable in special modes.

The MCU address bit AB0 is not stored in the EADDR registers since the EEPROM block is not byte addressable.

# 25.3.2.9 EEPROM Data Registers (EDATA)

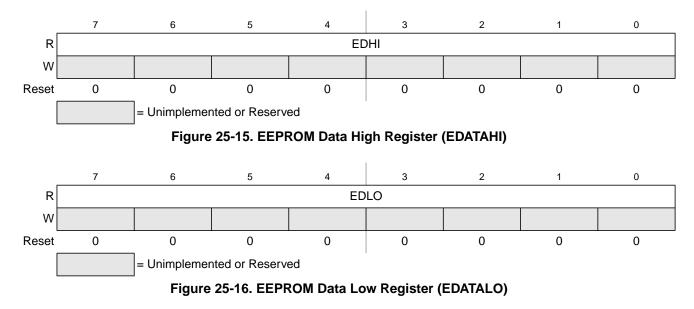

The EDATAHI and EDATALO registers are the EEPROM data registers.

All EDHI and EDLO bits read 0 and are not writable in normal modes.

#### MC9S12XDP512 Data Sheet, Rev. 2.21

unaffected by the backdoor key access sequence. After the next reset of the MCU, the security state of the Flash module is determined by the Flash security byte (0x7F\_FF0F). The backdoor key access sequence has no effect on the program and erase protections defined in the Flash protection register.

It is not possible to unsecure the MCU in special single chip mode by using the backdoor key access sequence in background debug mode (BDM).

# 28.6.2 Unsecuring the MCU in Special Single Chip Mode using BDM

The MCU can be unsecured in special single chip mode by erasing the Flash module by the following method:

• Reset the MCU into special single chip mode, delay while the erase test is performed by the BDM secure ROM, send BDM commands to disable protection in the Flash module, and execute a mass erase command write sequence to erase the Flash memory.

After the CCIF flag sets to indicate that the mass operation has completed, reset the MCU into special single chip mode. The BDM secure ROM will verify that the Flash memory is erased and will assert the UNSEC bit in the BDM status register. This BDM action will cause the MCU to override the Flash security state and the MCU will be unsecured. All BDM commands will be enabled and the Flash security byte may be programmed to the unsecure state by the following method:

• Send BDM commands to execute a word program sequence to program the Flash security byte to the unsecured state and reset the MCU.

# 28.7 Resets

## 28.7.1 Flash Reset Sequence

On each reset, the Flash module executes a reset sequence to hold CPU activity while loading the following registers from the Flash memory according to Table 28-1:

- FPROT Flash Protection Register (see Section 28.3.2.5).

- FCTL Flash Control Register (see Section 28.3.2.8).

- FSEC Flash Security Register (see Section 28.3.2.2).

# 28.7.2 Reset While Flash Command Active

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.

# 28.8 Interrupts

The Flash module can generate an interrupt when all Flash command operations have completed, when the Flash address, data and command buffers are empty.

# E.5 Peripheral Sets S12XD - Family

| Device     | Package | XGATE                                            | CAN | SCI | SPI | IIC | ECT | PIT | ATD0             | ATD1              | I/O |

|------------|---------|--------------------------------------------------|-----|-----|-----|-----|-----|-----|------------------|-------------------|-----|

| 9S12XDP512 | 144LQFP |                                                  | 5   | 6   | 3   | 2   | 8   | 4   | 8ch <sup>1</sup> | 16ch <sup>2</sup> | 119 |

|            | 112LQFP |                                                  | 5   | 6   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> | 8ch <sup>3</sup>  | 91  |

|            | 144LQFP | -                                                | 3   | 6   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> | 16ch <sup>2</sup> | 119 |

| 9S12XDT512 | 112LQFP |                                                  | 3   | 6   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> | 8ch <sup>3</sup>  | 91  |

|            | 80QFP   |                                                  | 3   | 2   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> |                   | 59  |

|            | 144LQFP |                                                  | 3   | 4   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> | 16ch <sup>2</sup> | 119 |

| 9S12XDT384 | 112LQFP |                                                  | 3   | 4   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> | 8ch <sup>3</sup>  | 91  |

|            | 80QFP   |                                                  | 3   | 2   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> |                   | 59  |

|            | 144LQFP |                                                  | 4   | 4   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> | 16ch <sup>2</sup> | 119 |

| 9S12XDQ256 | 112LQFP | -                                                | 4   | 4   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> | 8ch <sup>3</sup>  | 91  |

|            | 80QFP   | yes                                              | 4   | 2   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> |                   | 59  |

|            | 144LQFP |                                                  | 3   | 4   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> | 16ch <sup>2</sup> | 119 |

| 9S12XDT256 | 112LQFP |                                                  | 3   | 4   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> | 8ch <sup>3</sup>  | 91  |

|            | 80QFP   |                                                  | 3   | 2   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> |                   | 59  |

|            | 144LQFP |                                                  | 1   | 4   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> | 16ch <sup>2</sup> | 119 |

| 9S12XD256  | 112LQFP |                                                  | 1   | 4   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> | 8ch <sup>3</sup>  | 91  |

|            | 80QFP   |                                                  | 1   | 2   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> |                   | 59  |

|            | 144LQFP |                                                  | 3   | 4   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> | 16ch <sup>2</sup> | 119 |

| 3S12XDT256 | 112LQFP |                                                  | 3   | 4   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> | 8ch <sup>3</sup>  | 91  |

|            | 80QFP   |                                                  | 3   | 2   | 3   | 1   | 8   | 4   | 8ch <sup>1</sup> |                   | 59  |

| 0040200400 | 112LQFP |                                                  | 2   | 2   | 2   | 1   | 8   | 4   |                  | 16ch <sup>4</sup> | 91  |

| 9S12XDG128 | 80QFP   | yes<br>but<br>XGATE<br>has no<br>Flash<br>Access | 2   | 2   | 2   | 1   | 8   | 4   |                  | 8ch <sup>5</sup>  | 59  |

| 0040200400 | 112LQFP |                                                  | 2   | 2   | 2   | 1   | 8   | 4   |                  | 16ch <sup>4</sup> | 91  |

| 3S12XDG128 | 80QFP   |                                                  | 2   | 2   | 2   | 1   | 8   | 4   |                  | 8ch <sup>5</sup>  | 59  |

| 004020400  | 112LQFP |                                                  | 1   | 2   | 2   | 1   | 8   | 4   |                  | 16ch <sup>4</sup> | 91  |

| 9S12XD128  | 80QFP   | 100000                                           | 1   | 2   | 2   | 1   | 8   | 4   |                  | 8ch <sup>5</sup>  | 59  |

| 9S12XD64   | 80QFP   |                                                  | 1   | 2   | 2   | 1   | 8   | 2   |                  | 8ch <sup>5</sup>  | 59  |

#### Table E-5. S12XD Peripherals

<sup>1</sup> ATD0 routed to PAD[7:0]

#### 0x0138–0x013F Asynchronous Serial Interface (SCI5) Map (continued)

| Address | Name    |      | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|---------|---------|------|--------|-------|-------|-------|--------|-------|-------|-------|

| 0x013D  | SCI5SR2 | R    | AMAP 0 | 0     | TXPOL | RXPOL | BRK13  | TXDIR | RAF   |       |

|         |         | `- W | ,,     |       |       |       | 104 02 |       |       |       |

| 0x013E  | SCI5DRH | R    | R8     | Т8    | 0     | 0     | 0      | 0     | 0     | 0     |

|         |         | W    |        |       |       |       |        |       |       |       |

| 0x013F  | SCI5DRL | R    | R7     | R6    | R5    | R4    | R3     | R2    | R1    | R0    |

|         |         | W    | T7     | T6    | T5    | T4    | Т3     | T2    | T1    | Т0    |

<sup>1</sup> Those registers are accessible if the AMAP bit in the SCI5SR2 register is set to zero

<sup>2</sup> Those registers are accessible if the AMAP bit in the SCI5SR2 register is set to one

#### 0x0140–0x017F Freescale Scalable CAN — MSCAN (CAN0) Map

| Address | Name      |        | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|---------|-----------|--------|--------|--------|---------|---------|---------|---------|--------|--------|

| 0x0140  | CAN0CTL0  | R<br>W | RXFRM  | RXACT  | CSWAI   | SYNCH   | TIME    | WUPE    | SLPRQ  | INITRQ |

| 0x0141  | CAN0CTL1  | R<br>W | CANE   | CLKSRC | LOOPB   | LISTEN  | BORM    | WUPM    | SLPAK  | INITAK |

| 0x0142  | CAN0BTR0  | R<br>W | SJW1   | SJW0   | BRP5    | BRP4    | BRP3    | BRP2    | BRP1   | BRP0   |

| 0x0143  | CAN0BTR1  | R<br>W | SAMP   | TSEG22 | TSEG21  | TSEG20  | TSEG13  | TSEG12  | TSEG11 | TSEG10 |

| 0x0144  | CANORFLG  | R<br>W | WUPIF  | CSCIF  | RSTAT1  | RSTAT0  | TSTAT1  | TSTAT0  | OVRIF  | RXF    |

| 0x0145  | CANORIER  | R<br>W | WUPIE  | CSCIE  | RSTATE1 | RSTATE0 | TSTATE1 | TSTATE0 | OVRIE  | RXFIE  |

| 0x0146  | CAN0TFLG  | R<br>W | 0      | 0      | 0       | 0       | 0       | TXE2    | TXE1   | TXE0   |

| 0x0147  | CAN0TIER  | R<br>W | 0      | 0      | 0       | 0       | 0       | TXEIE2  | TXEIE1 | TXEIE0 |

| 0x0148  | CAN0TARQ  | R<br>W | 0      | 0      | 0       | 0       | 0       | ABTRQ2  | ABTRQ1 | ABTRQ0 |

| 0x0149  | CAN0TAAK  | R<br>W | 0      | 0      | 0       | 0       | 0       | ABTAK2  | ABTAK1 | ABTAK0 |

| 0x014A  | CAN0TBSEL | R<br>W | 0      | 0      | 0       | 0       | 0       | TX2     | TX1    | TX0    |

| 0x014B  | CAN0IDAC  | R<br>W | 0      | 0      | IDAM1   | IDAM0   | 0       | IDHIT2  | IDHIT1 | IDHIT0 |

| 0x014C  | Reserved  | R<br>W | 0      | 0      | 0       | 0       | 0       | 0       | 0      | 0      |

| 0x014D  | CAN0MISC  | R<br>W | 0      | 0      | 0       | 0       | 0       | 0       | 0      | BOHOLD |

| 0x014E  | CANORXERR | R<br>W | RXERR7 | RXERR6 | RXERR5  | RXERR4  | RXERR3  | RXERR2  | RXERR1 | RXERR0 |

| 0x014F  | CAN0TXERR | R<br>W | TXERR7 | TXERR6 | TXERR5  | TXERR4  | TXERR3  | TXERR2  | TXERR1 | TXERR0 |