# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 12                                                                      |

| Program Memory Size        | 768B (512 x 12)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 25 x 8                                                                  |

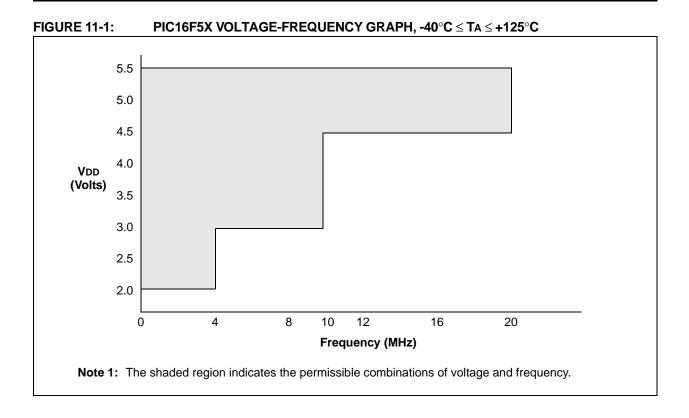

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

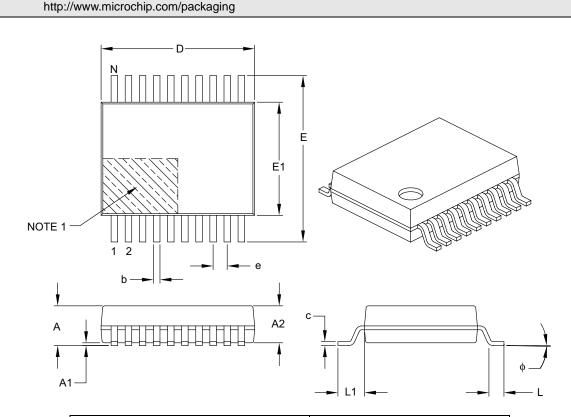

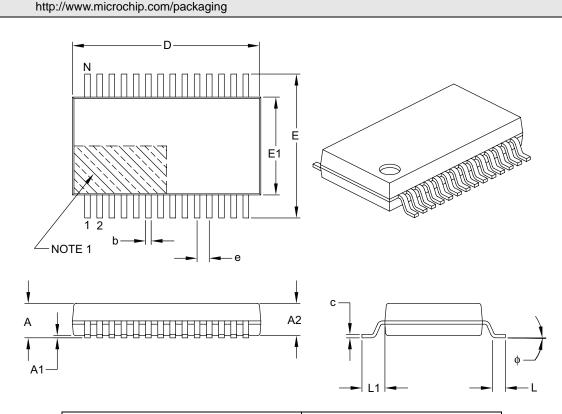

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 20-SSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f54-i-ss |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

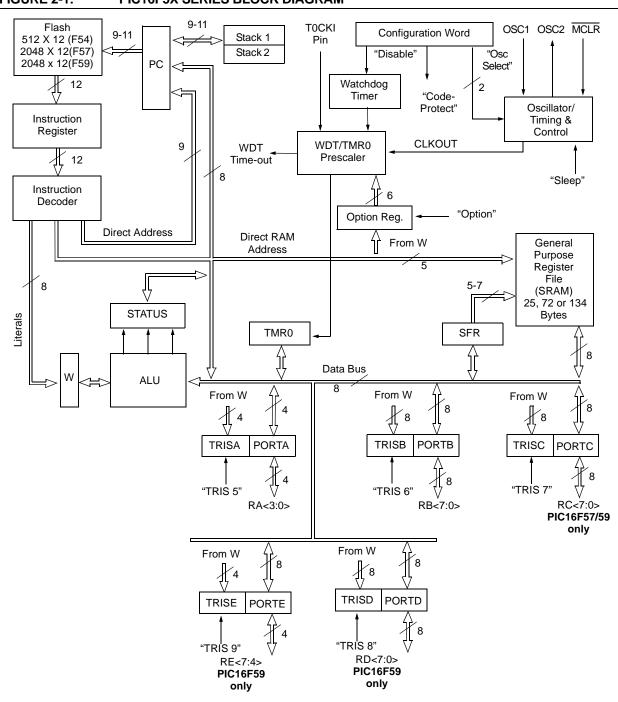

FIGURE 2-1: PIC16F5X SERIES BLOCK DIAGRAM

| Name        | Function                        | Input<br>Type | Output<br>Type | Description                                                                                                                         |  |  |  |  |  |

|-------------|---------------------------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RA0         | RA0                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |  |  |  |

| RA1         | RA1                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |  |  |  |

| RA2         | RA2                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |  |  |  |

| RA3         | RA3                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |  |  |  |

| RB0         | RB0                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |  |  |  |

| RB1         | RB1                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |  |  |  |

| RB2         | RB2                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |  |  |  |

| RB3         | RB3                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |  |  |  |

| RB4         | RB4                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |  |  |  |

| RB5         | RB5                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |  |  |  |

| RB6/ICSPCLK | RB6                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |  |  |  |

|             | ICSPCLK                         | ST            | _              | Serial Programming Clock                                                                                                            |  |  |  |  |  |

| RB7/ICSPDAT | RB7                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |  |  |  |

|             | ICSPDAT                         | ST            | CMOS           | Serial Programming I/O                                                                                                              |  |  |  |  |  |

| TOCKI       | TOCKI                           | ST            | —              | Clock input to Timer0. Must be tied to Vss or VDD, if not in use, reduce current consumption.                                       |  |  |  |  |  |

| MCLR/Vpp    | MCLR                            | ST            | —              | Active-low Reset to device. Voltage on the MCLR/VPP pin must<br>not exceed VDD to avoid unintended entering of Programming<br>mode. |  |  |  |  |  |

|             | Vpp                             | ΗV            | _              | Programming voltage input                                                                                                           |  |  |  |  |  |

| OSC1/CLKIN  | OSC1                            | XTAL          | —              | Oscillator crystal input                                                                                                            |  |  |  |  |  |

|             | CLKIN                           | ST            | _              | External clock source input                                                                                                         |  |  |  |  |  |

| OSC2/CLKOUT | OSC2                            | —             | XTAL           | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode.                                             |  |  |  |  |  |

|             | CLKOUT                          | —             | CMOS           | In RC mode, OSC2 pin can output CLKOUT, which has 1/4 the frequency of OSC1.                                                        |  |  |  |  |  |

| Vdd         | Vdd                             | Power         |                | Positive supply for logic and I/O pins                                                                                              |  |  |  |  |  |

| Vss         | Vss                             | Power         |                | Ground reference for logic and I/O pins                                                                                             |  |  |  |  |  |

| O =         | input<br>output<br>Schmitt Trig | ger input     | I/O<br>—<br>TT | = input/outputCMOS= CMOS output= Not UsedXTAL= Crystal input/outputL= TTL inputHV= High Voltage                                     |  |  |  |  |  |

TABLE 2-1: PIC16F54 PINOUT DESCRIPTION

| RA0<br>RA1<br>RA2<br>RA3<br>RB0<br>RB1<br>RB2<br>RB3<br>RB4<br>RB5<br>RB6<br>CSPCLK<br>RB7<br>CSPDAT | Type           TTL           TTL | Type<br>CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS | Bidirectional I/O pin<br>Bidirectional I/O pin |  |  |  |  |

|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RA1<br>RA2<br>RA3<br>RB0<br>RB1<br>RB2<br>RB3<br>RB4<br>RB5<br>RB6<br>CSPCLK<br>RB7                  | TTL                                                                                                                                                            | CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS                 | Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin                                                   |  |  |  |  |

| RA3<br>RB0<br>RB1<br>RB2<br>RB3<br>RB4<br>RB5<br>RB6<br>CSPCLK<br>RB7                                | TTL<br>TTL<br>TTL<br>TTL<br>TTL<br>TTL<br>TTL                                                                                                                                                                                                                                                              | CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS                 | Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin                                                                                                     |  |  |  |  |

| RA3<br>RB0<br>RB1<br>RB2<br>RB3<br>RB4<br>RB5<br>RB6<br>CSPCLK<br>RB7                                | TTL<br>TTL<br>TTL<br>TTL<br>TTL<br>TTL<br>TTL                                                                                                                                                                                                                                                              | CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS                         | Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin                                                                                                     |  |  |  |  |

| RB0<br>RB1<br>RB2<br>RB3<br>RB4<br>RB5<br>RB6<br>CSPCLK<br>RB7                                       | TTL<br>TTL<br>TTL<br>TTL<br>TTL<br>TTL                                                                                                                                                                                                                                                                     | CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS                                 | Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin                                                                                                                              |  |  |  |  |

| RB1<br>RB2<br>RB3<br>RB4<br>RB5<br>RB6<br>CSPCLK<br>RB7                                              | TTL<br>TTL<br>TTL<br>TTL<br>TTL                                                                                                                                                                                                                                                                            | CMOS<br>CMOS<br>CMOS<br>CMOS                                         | Bidirectional I/O pin<br>Bidirectional I/O pin<br>Bidirectional I/O pin                                                                                                                                                       |  |  |  |  |

| RB2<br>RB3<br>RB4<br>RB5<br>RB6<br>CSPCLK<br>RB7                                                     | TTL<br>TTL<br>TTL<br>TTL                                                                                                                                                                                                                                                                                   | CMOS<br>CMOS<br>CMOS                                                 | Bidirectional I/O pin<br>Bidirectional I/O pin                                                                                                                                                                                |  |  |  |  |

| RB3<br>RB4<br>RB5<br>RB6<br>CSPCLK<br>RB7                                                            | TTL<br>TTL<br>TTL                                                                                                                                                                                                                                                                                          | CMOS<br>CMOS                                                         | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RB4<br>RB5<br>RB6<br>CSPCLK<br>RB7                                                                   | TTL<br>TTL                                                                                                                                                                                                                                                                                                 | CMOS                                                                 |                                                                                                                                                                                                                               |  |  |  |  |

| RB5<br>RB6<br>CSPCLK<br>RB7                                                                          | TTL                                                                                                                                                                                                                                                                                                        |                                                                      |                                                                                                                                                                                                                               |  |  |  |  |

| RB6<br>CSPCLK<br>RB7                                                                                 |                                                                                                                                                                                                                                                                                                            |                                                                      | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| CSPCLK<br>RB7                                                                                        |                                                                                                                                                                                                                                                                                                            | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RB7                                                                                                  | ST                                                                                                                                                                                                                                                                                                         |                                                                      | Serial programming clock                                                                                                                                                                                                      |  |  |  |  |

|                                                                                                      | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| COFDAI                                                                                               | ST                                                                                                                                                                                                                                                                                                         | CMOS                                                                 | Serial programming I/O                                                                                                                                                                                                        |  |  |  |  |

| RC0                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RC1                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RC2                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RC3                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RC4                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RC4<br>RC5                                                                                           | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

|                                                                                                      |                                                                                                                                                                                                                                                                                                            |                                                                      |                                                                                                                                                                                                                               |  |  |  |  |

| RC6                                                                                                  |                                                                                                                                                                                                                                                                                                            | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RC7                                                                                                  |                                                                                                                                                                                                                                                                                                            | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RD0                                                                                                  |                                                                                                                                                                                                                                                                                                            | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RD1                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RD2                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RD3                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RD4                                                                                                  |                                                                                                                                                                                                                                                                                                            | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RD5                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RD6                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RD7                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RE4                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RE5                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RE6                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| RE7                                                                                                  | TTL                                                                                                                                                                                                                                                                                                        | CMOS                                                                 | Bidirectional I/O pin                                                                                                                                                                                                         |  |  |  |  |

| TOCKI                                                                                                | ST                                                                                                                                                                                                                                                                                                         |                                                                      | Clock input to Timer0. Must be tied to VSS or VDD, if not in use, to reduc<br>current consumption.                                                                                                                            |  |  |  |  |

| MCLR                                                                                                 | ST                                                                                                                                                                                                                                                                                                         | —                                                                    | Active-low Reset to device. Voltage on the MCLR/VPP pin must not exceed VDD to avoid unintended entering of Programming mode.                                                                                                 |  |  |  |  |

| Vpp                                                                                                  | ΗV                                                                                                                                                                                                                                                                                                         | -                                                                    | Programming voltage input                                                                                                                                                                                                     |  |  |  |  |

| OSC1                                                                                                 | XTAL                                                                                                                                                                                                                                                                                                       | _                                                                    | Oscillator crystal input                                                                                                                                                                                                      |  |  |  |  |

| CLKIN                                                                                                | ST                                                                                                                                                                                                                                                                                                         |                                                                      | External clock source input                                                                                                                                                                                                   |  |  |  |  |

| OSC2                                                                                                 | _                                                                                                                                                                                                                                                                                                          | XTAL                                                                 |                                                                                                                                                                                                                               |  |  |  |  |

| CLKOUT                                                                                               | _                                                                                                                                                                                                                                                                                                          | CMOS                                                                 | In RC mode, OSC2 pin outputs CLKOUT, which has 1/4 the frequency o OSC1.                                                                                                                                                      |  |  |  |  |

| VDD                                                                                                  | Power                                                                                                                                                                                                                                                                                                      | _                                                                    | Positive supply for logic and I/O pins                                                                                                                                                                                        |  |  |  |  |

| Vss                                                                                                  | Power                                                                                                                                                                                                                                                                                                      | _                                                                    | Ground reference for logic and I/O pins                                                                                                                                                                                       |  |  |  |  |

|                                                                                                      | •                                                                                                                                                                                                                                                                                                          | I/O =                                                                | input/output CMOS = CMOS output                                                                                                                                                                                               |  |  |  |  |

| t                                                                                                    |                                                                                                                                                                                                                                                                                                            |                                                                      | Not Used XTAL = Crystal input/output                                                                                                                                                                                          |  |  |  |  |

|                                                                                                      | DSC1<br>SLKIN<br>DSC2<br>KOUT<br>VDD<br>VSS                                                                                                                                                                                                                                                                | DSC1 XTAL<br>SLKIN ST<br>DSC2 —<br>KOUT —<br>VDD Power               | DSC1 XTAL —<br>SLKIN ST —<br>DSC2 — XTAL<br>KOUT — CMOS<br>VDD Power —<br>VSS Power —<br>I/O =<br>— =                                                                                                                         |  |  |  |  |

TABLE 2-3: PIC16F59 PINOUT DESCRIPTION

### 3.0 MEMORY ORGANIZATION

PIC16F5X memory is organized into program memory and data memory. For the PIC16F57 and PIC16F59, which have more than 512 words of program memory, a paging scheme is used. Program memory pages are accessed using one or two STATUS register bits. For the PIC16F57 and PIC16F59, which have a data memory register file of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Selection Register (FSR).

#### 3.1 Program Memory Organization

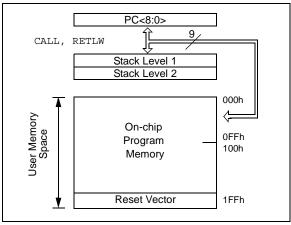

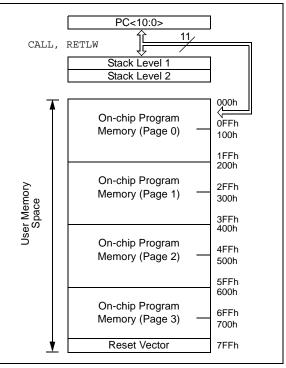

The PIC16F54 has a 9-bit Program Counter (PC) capable of addressing a 512 x 12 program memory space (Figure 3-1). The PIC16F57 and PIC16F59 have an 11-bit Program Counter capable of addressing a 2K x 12 program memory space (Figure 3-2). Accessing a location above the physically implemented address will cause a wraparound.

A NOP at the Reset vector location will cause a restart at location 000h. The Reset vector for the PIC16F54 is at 1FFh. The Reset vector for the PIC16F57 and PIC16F59 is at 7FFh. See **Section 3.5 "Program Counter"** for additional information using CALL and GOTO instructions.

#### FIGURE 3-2:

#### PIC16F57/PIC16F59 PROGRAM MEMORY MAP AND STACK

#### 3.3 **STATUS Register**

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bits for program memories larger than 512 words.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

Therefore, it is recommended that only BCF, BSF, MOVWF and SWAPF instructions be used to alter the STATUS register because these instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions which do affect Status bits, see Section 9.0 "Instruction Set Summary".

#### **REGISTER 3-1:** STATUS REGISTER (ADDRESS: 03h)

|         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                               | R/W-0                   | R-1            | R-1            | R/W-x                                      | R/W-x          | R/W-x       |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------|----------------|----------------|--------------------------------------------|----------------|-------------|--|

|         | PA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PA1                                                 | PA0                     | TO             | PD             | Z                                          | DC             | С           |  |

|         | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                     |                         |                |                |                                            |                | bit 0       |  |

| bit 7   | Use of the P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ved, do not us<br>A2 bit as a ge<br>/ with future p | neral purpos            | e read/write I | oit is not rec | ommended, sin                              | ce this may af | fect upward |  |

| bit 6-5 | <pre>PA&lt;1:0&gt;: Program Page Preselect bits (PIC16F57/PIC16F59) 00 = Page 0 (000h-1FFh) 01 = Page 1 (200h-3FFh) 10 = Page 2 (400h-5FFh) 11 = Page 3 (600h-7FFh) Each page is 512 words. Using the PA&lt;1:0&gt; bits as general purpose read/write bits in devices which do not use them for program page preselect is not recommended. This may affect upward compatibility with future products.</pre>                                                                                   |                                                     |                         |                |                |                                            |                |             |  |

| bit 4   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ut bit<br>wer-up, CLRM<br>time-out occu             |                         | on or SLEEP    | instruction    |                                            |                |             |  |

| bit 3   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Down bit<br>wer-up or by<br>ution of the S          |                         |                |                |                                            |                |             |  |

| bit 2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ult of an arith<br>ult of an arith                  |                         |                |                |                                            |                |             |  |

| bit 1   | <ul> <li>0 = The result of an arithmetic or logic operation is not zero</li> <li>DC: Digit Carry/Borrow bit (for ADDWF and SUBWF instructions)</li> <li>ADDWF</li> <li>1 = A carry to the 4th low order bit of the result occurred</li> <li>0 = A carry from the 4th low order bit of the result did not occur</li> <li>SUBWF</li> <li>1 = A borrow to the 4th low order bit of the result did not occur</li> <li>0 = A borrow to the 4th low order bit of the result did not occur</li> </ul> |                                                     |                         |                |                |                                            |                |             |  |

| bit 0   | 1 = A carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | rrow bit (for A<br>occurred<br>did not occur        | <u>SUBWI</u><br>1 = A b |                | occur Lo       | ons)<br><u>RF or RLF</u><br>paded with LSb | or MSb, resp   | ectively    |  |

|         | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |                         |                |                |                                            |                |             |  |

|         | R = Readab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ole bit                                             | W = W                   | /ritable bit   | U = Un         | implemented bi                             | t, read as '0' |             |  |

|         | - n = Value a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | at POR                                              | '1' = B                 | it is set      | '0' = Bit      | t is cleared                               | x = Bit is un  | known       |  |

### PIC16F5X

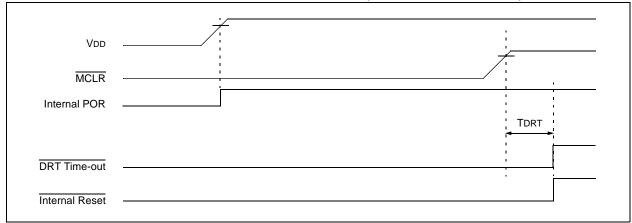

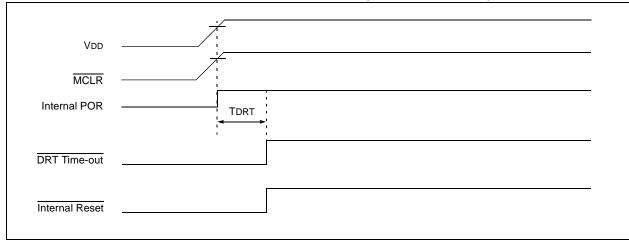

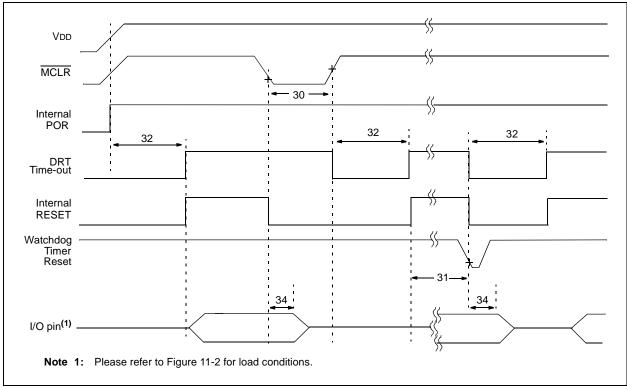

#### FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

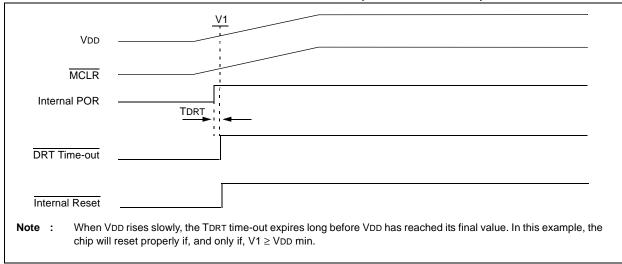

#### FIGURE 5-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

#### TABLE 6-1: SUMMARY OF PORT REGISTERS

| Address | Name                 | Bit 7   | Bit 6     | Bit 5     | Bit 4    | Bit 3    | Bit 2   | Bit 1   | Bit 0  | Value on<br>Power-on<br>Reset | <u>Value</u> on<br>MCLR and<br>WDT Reset |

|---------|----------------------|---------|-----------|-----------|----------|----------|---------|---------|--------|-------------------------------|------------------------------------------|

| N/A     | TRIS                 | I/O Con | trol Regi | sters (TI | RISA, TF | RISB, TR | ISC, TR | ISD and | TRISE) | 1111 1111                     | 1111 1111                                |

| 05h     | PORTA                | _       |           |           | _        | RA3      | RA2     | RA1     | RA0    | xxxx                          | uuuu                                     |

| 06h     | PORTB                | RB7     | RB6       | RB5       | RB4      | RB3      | RB2     | RB1     | RB0    | xxxx xxxx                     | uuuu uuuu                                |

| 07h     | PORTC <sup>(1)</sup> | RC7     | RC6       | RC5       | RC4      | RC3      | RC2     | RC1     | RC0    | xxxx xxxx                     | uuuu uuuu                                |

| 08h     | PORTD <sup>(2)</sup> | RD7     | RD6       | RD5       | RD4      | RD3      | RD2     | RD1     | RD0    | xxxx xxxx                     | uuuu uuuu                                |

| 09h     | PORTE <sup>(2)</sup> | RE7     | RE6       | RE5       | RE4      |          |         |         |        | xxxx                          | uuuu                                     |

**Legend:** Shaded cells = unimplemented, read as '0', - = unimplemented, read as '0', x = unknown, u = unchanged

Note 1: File address 07h is a General Purpose Register on the PIC16F54.

2: File address 08h and 09h are General Purpose Registers on the PIC16F54 and PIC16F57.

#### 6.8 I/O Programming Considerations

#### 6.8.1 BIDIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit 5 of PORTB will cause all eight bits of PORTB to be read into the CPU, bit 5 to be set and the PORTB value to be written to the output latches. If another bit of PORTB is used as a bidirectional I/O pin (say bit '0'), and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit '0' is switched into Output mode later on, the content of the data latch may now be unknown

Example 6-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}, \ {\tt BSF}, \mbox{etc.})$  on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 6-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ;Initial PORT Settings                             |  |  |  |  |  |  |  |

|----------------------------------------------------|--|--|--|--|--|--|--|

| ;PORTB<7:4> Inputs                                 |  |  |  |  |  |  |  |

| ;PORTB<3:0> Outputs                                |  |  |  |  |  |  |  |

| ;PORTB<7:6> have external pull-ups and are         |  |  |  |  |  |  |  |

| ;not connected to other circuitry                  |  |  |  |  |  |  |  |

| ;                                                  |  |  |  |  |  |  |  |

| ; PORT latch PORT pins                             |  |  |  |  |  |  |  |

| ;                                                  |  |  |  |  |  |  |  |

| BCF PORTB, 7 ;01pp pppp 11pp pppp                  |  |  |  |  |  |  |  |

| BCF PORTB, 6 ;10pp pppp 11pp pppp                  |  |  |  |  |  |  |  |

| MOVLW H'3F' ;                                      |  |  |  |  |  |  |  |

| TRIS PORTB ;10pp pppp 10pp pppp                    |  |  |  |  |  |  |  |

| ;                                                  |  |  |  |  |  |  |  |

| ;Note that the user may have expected the          |  |  |  |  |  |  |  |

| pin                                                |  |  |  |  |  |  |  |

| ;values to be 00pp pppp. The 2nd BCF caused        |  |  |  |  |  |  |  |

| ;RB7 to be latched as the pin value (High).        |  |  |  |  |  |  |  |

| pin<br>;values to be 00pp pppp. The 2nd BCF caused |  |  |  |  |  |  |  |

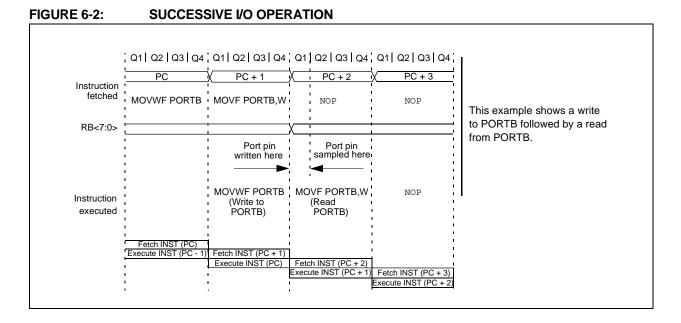

### 6.8.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (see Figure 6-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### © 2007 Microchip Technology Inc.

#### FIGURE 7-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALER 1:2

| (Program               | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4            | Q1 Q2 Q3 Q4            | Q1 Q2 Q3 Q4            | Q1 Q2 Q3 Q4            | Q1 Q2 Q3 Q4            | Q1 Q2 Q3 Q4                |

|------------------------|-------------|-------------|------------------------|------------------------|------------------------|------------------------|------------------------|----------------------------|

| Counter)               | PC - 1      | PC PC       | ( PC + 1 )             | PC + 2                 | PC + 3                 | PC + 4                 | PC+5                   | PC + 6                     |

| Instruction<br>Fetch   |             | MOVWF TMR0  | MOVF TMR0,W            | ,<br>,<br>,<br>,           |

| Fimer0                 | το χ        | T0 + 1      |                        |                        | NTO                    |                        | X_                     | NT0 + 1                    |

| Instruction<br>Execute |             | ,<br>,<br>, | Write TMR0<br>executed | Read TMR0<br>reads NT0 + 1 |

#### TABLE 7-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7  | Bit 6      | Bit 5     | Bit 4     | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | <u>Value</u> on<br>MCLR and<br>WDT Reset |

|---------|--------|--------|------------|-----------|-----------|-------|-------|-------|-------|-------------------------------|------------------------------------------|

| 01h     | TMR0   | Timer0 | - 8-bit re | al-time c | clock/cou | inter |       |       |       | xxxx xxxx                     | uuuu uuuu                                |

| N/A     | OPTION |        | _          | TOCS      | T0SE      | PSA   | PS2   | PS1   | PS0   | 11 1111                       | 11 1111                                  |

**Legend:** Shaded cells not used by Timer0, - = unimplemented, x = unknown, u = unchanged.

# 8.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits that deal with the needs of realtime applications. The PIC16F5X family of microcontrollers have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide powersaving operating modes and offer code protection. These features are:

- Oscillator Selection

- Reset

- Power-on Reset

- Device Reset Timer

- Watchdog Timer (WDT)

- Sleep

- Code protection

- User ID locations

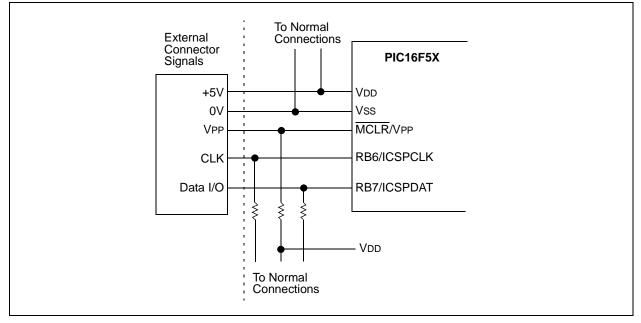

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

The PIC16F5X family has a Watchdog Timer which can be shut off only through Configuration bit WDTE. It runs off of its own RC oscillator for added reliability. There is an 18 ms delay provided by the Device Reset Timer (DRT), intended to keep the chip in Reset until the crystal oscillator is stable. With this timer on-chip, most applications need no external Reset circuitry.

#### REGISTER 8-1: CONFIGURATION WORD FOR PIC16F5X

|           |                          |            |                           |               | -         |           | -             |            | -           |             |            |

|-----------|--------------------------|------------|---------------------------|---------------|-----------|-----------|---------------|------------|-------------|-------------|------------|

| —         | —                        | —          | —                         | —             |           |           |               | CP         | WDTE        | FOSC1       | FOSC0      |

| bit 11    |                          |            |                           |               |           |           |               |            |             |             | bit 0      |

|           |                          |            |                           |               |           |           |               |            |             |             |            |

| bit 11-4: | Unimpleme                | ented:     | Read as ':                | 1'            |           |           |               |            |             |             |            |

| bit 3:    | CP: Code F               | Protection | on bit.                   |               |           |           |               |            |             |             |            |

|           | 1 = Code p               |            |                           |               |           |           |               |            |             |             |            |

|           | 0 = Code p               |            |                           |               |           |           |               |            |             |             |            |

| bit 2:    | WDTE: Wa                 | -          |                           | able bit      |           |           |               |            |             |             |            |

|           | 1 = WDTe                 |            |                           |               |           |           |               |            |             |             |            |

|           | 0 = WDT d                |            | -                         |               | ••        |           |               |            |             |             |            |

| bit 1-0:  | FOSC1:FO                 |            | scillator S               | selection t   | oits      |           |               |            |             |             |            |

|           | 00 = LP os<br>01 = XT os |            |                           |               |           |           |               |            |             |             |            |

|           | 10 = HS os               |            |                           |               |           |           |               |            |             |             |            |

|           | 11 = RC os               | cillator   |                           |               |           |           |               |            |             |             |            |

|           | Note 1:                  | Refer t    | o the PIC1                | 6F54, PIC     | C16F57 ar | nd PIC16F | 59 Progra     | mming Sp   | ecificatior | ns to deter | mine how   |

|           |                          |            | ess the Co<br>nicrochip.c | •             | n Word. T | hese docu | iments ca     | n be found | d on the M  | icrochip w  | eb site at |

|           |                          |            |                           |               |           |           |               |            |             |             |            |

|           | Legend:                  |            |                           |               |           |           |               |            |             |             |            |

|           | R = Readat               | ole bit    | V                         | V = Writab    | ole bit   | U =       | Unimpler      | nented bit | , read as ' | 0'          |            |

|           | -n = Value a             | at POR     | ٢.                        | 1' = bit is s | set       | 'O' =     | = bit is clea | ared       | x = bi      | t is unknov | wn         |

The Sleep mode is designed to offer a very low-current Power-down mode. The user can wake-up from Sleep through external Reset or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of Configuration bits are used to select various options.

### 8.1 Configuration Bits

Configuration bits can be programmed to select various device configurations. Two bits are for the selection of the oscillator type; one bit is the Watchdog Timer enable bit; one bit is for code protection for the PIC16F5X devices (Register 8-1).

#### FIGURE 8-1: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> CONNECTION

# PIC16F5X

| IORLW            | Inclusive OR literal with W                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |

| Operands:        | $0 \le k \le 255$                                                                                                         |

| Operation:       | (W) .OR. (k) $\rightarrow$ (W)                                                                                            |

| Status Affected: | Z                                                                                                                         |

| Encoding:        | 1101 kkkk kkkk                                                                                                            |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |

| Words:           | 1                                                                                                                         |

| Cycles:          | 1                                                                                                                         |

| Example:         | IORLW 0x35                                                                                                                |

| Before Instru    | uction                                                                                                                    |

| • •              | 0x9A                                                                                                                      |

| After Instruc    |                                                                                                                           |

| W =              | 0xBF                                                                                                                      |

| Z =              | 0                                                                                                                         |

| IORWF                                                           | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:                                                         | [ <i>label</i> ] IORWF f, d                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Operands:                                                       | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                            |  |  |  |  |  |  |  |  |

| Operation:                                                      | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                            |  |  |  |  |  |  |  |  |

| Status Affected:                                                | Z                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| Encoding:                                                       | 0001 00df ffff                                                                                                                                                              |  |  |  |  |  |  |  |  |

| Description:                                                    | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1',<br>the result is placed back in<br>register 'f'. |  |  |  |  |  |  |  |  |

| Words:                                                          | 1                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| Cycles:                                                         | 1                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| Example:                                                        | IORWF RESULT, 0                                                                                                                                                             |  |  |  |  |  |  |  |  |

| Before Instru<br>RESUL<br>W<br>After Instruc<br>RESUL<br>W<br>Z | T = 0x13<br>= 0x91<br>tion                                                                                                                                                  |  |  |  |  |  |  |  |  |

| MOVF                 | Move f                                                                                                                                                                                                                                                       |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:              | [ <i>label</i> ] MOVF f, d                                                                                                                                                                                                                                   |

| Operands:            | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                    |

| Operation:           | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                     |

| Status Affected:     | Z                                                                                                                                                                                                                                                            |

| Encoding:            | 0010 00df ffff                                                                                                                                                                                                                                               |

| Description:         | The contents of register 'f' is<br>moved to destination 'd'. If 'd' is '0',<br>destination is the W register. If 'd'<br>is '1', the destination is file<br>register 'f'. 'd' is '1' is useful to test<br>a file register since Status flag Z is<br>affected. |

| Words:               | 1                                                                                                                                                                                                                                                            |

| Cycles:              | 1                                                                                                                                                                                                                                                            |

| Example:             | MOVF FSR, 0                                                                                                                                                                                                                                                  |

| After Instruc<br>W = | tion<br>= value in FSR register                                                                                                                                                                                                                              |

| MOVLW                         | Move Literal to W |                            |      |      |  |

|-------------------------------|-------------------|----------------------------|------|------|--|

| Syntax:                       | [ label ]         | MOVLW                      | k    |      |  |

| Operands:                     | $0 \le k \le 2$   | 55                         |      |      |  |