Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 768B (512 x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 25 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f54t-e-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, PS logo, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PIC<sup>®</sup> MCUs and dsPIC<sup>®</sup> DSCs, KEELOO<sup>®</sup> code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified. NOTES:

| Name        | Function                        | Input<br>Type | Output<br>Type | Description                                                                                                                         |  |  |

|-------------|---------------------------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RA0         | RA0                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |

| RA1         | RA1                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |

| RA2         | RA2                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |

| RA3         | RA3                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |

| RB0         | RB0                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |

| RB1         | RB1                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |

| RB2         | RB2                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |

| RB3         | RB3                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |

| RB4         | RB4                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |

| RB5         | RB5                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |

| RB6/ICSPCLK | RB6                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |

|             | ICSPCLK                         | ST            | _              | Serial Programming Clock                                                                                                            |  |  |

| RB7/ICSPDAT | RB7                             | TTL           | CMOS           | Bidirectional I/O pin                                                                                                               |  |  |

|             | ICSPDAT                         | ST            | CMOS           | Serial Programming I/O                                                                                                              |  |  |

| TOCKI       | TOCKI                           | ST            | —              | Clock input to Timer0. Must be tied to Vss or VDD, if not in use, to reduce current consumption.                                    |  |  |

| MCLR/Vpp    | MCLR                            | ST            | —              | Active-low Reset to device. Voltage on the MCLR/VPP pin must<br>not exceed VDD to avoid unintended entering of Programming<br>mode. |  |  |

|             | Vpp                             | ΗV            | _              | Programming voltage input                                                                                                           |  |  |

| OSC1/CLKIN  | OSC1                            | XTAL          | —              | Oscillator crystal input                                                                                                            |  |  |

|             | CLKIN                           | ST            | _              | External clock source input                                                                                                         |  |  |

| OSC2/CLKOUT | OSC2                            | —             | XTAL           | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode.                                             |  |  |

|             | CLKOUT                          | —             | CMOS           | In RC mode, OSC2 pin can output CLKOUT, which has 1/4 the frequency of OSC1.                                                        |  |  |

| Vdd         | Vdd                             | Power         |                | Positive supply for logic and I/O pins                                                                                              |  |  |

| Vss         | Vss                             | Power         |                | Ground reference for logic and I/O pins                                                                                             |  |  |

| O =         | input<br>output<br>Schmitt Trig | ger input     | I/O<br>—<br>TT | = input/outputCMOS= CMOS output= Not UsedXTAL= Crystal input/outputL= TTL inputHV= High Voltage                                     |  |  |

TABLE 2-1: PIC16F54 PINOUT DESCRIPTION

#### 3.3 **STATUS Register**

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bits for program memories larger than 512 words.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

Therefore, it is recommended that only BCF, BSF, MOVWF and SWAPF instructions be used to alter the STATUS register because these instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions which do affect Status bits, see Section 9.0 "Instruction Set Summary".

#### **REGISTER 3-1:** STATUS REGISTER (ADDRESS: 03h)

|         | R/W-0                                                                   | R/W-0                                                                                  | R/W-0                                        | R-1                                                | R-1                                    | R/W-x                                      | R/W-x          | R/W-x       |

|---------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------|----------------------------------------|--------------------------------------------|----------------|-------------|

|         | PA2                                                                     | PA1                                                                                    | PA0                                          | TO                                                 | PD                                     | Z                                          | DC             | С           |

|         | bit 7                                                                   |                                                                                        |                                              |                                                    |                                        |                                            |                | bit 0       |

| bit 7   | Use of the P                                                            | ved, do not us<br>A2 bit as a ge<br>/ with future p                                    | neral purpos                                 | e read/write I                                     | oit is not rec                         | ommended, sin                              | ce this may af | fect upward |

| bit 6-5 | 00 = Page 0<br>01 = Page 1<br>10 = Page 2<br>11 = Page 3<br>Each page i | n for program                                                                          | )<br>)<br>)<br>Using the P/                  | \<br>\<1:0> bits a:                                | s general pu                           | )<br>urpose read/writ<br>This may affect   |                |             |

| bit 4   |                                                                         | ut bit<br>wer-up, CLRM<br>time-out occu                                                |                                              | on or SLEEP                                        | instruction                            |                                            |                |             |

| bit 3   |                                                                         | Down bit<br>wer-up or by<br>ution of the S                                             |                                              |                                                    |                                        |                                            |                |             |

| bit 2   |                                                                         | ult of an arith<br>ult of an arith                                                     |                                              |                                                    |                                        |                                            |                |             |

| bit 1   | ADDWF<br>1 = A carry 1<br>0 = A carry 1<br>SUBWF<br>1 = A borrow        | arry/Borrow b<br>to the 4th low<br>from the 4th l<br>w to the 4th lc<br>w from the 4th | order bit of<br>ow order bit<br>ow order bit | the result occ<br>of the result<br>of the result c | curred<br>did not occu<br>lid not occu | ır                                         |                |             |

| bit 0   | 1 = A carry                                                             | rrow bit (for A<br>occurred<br>did not occur                                           | <u>SUBWI</u><br>1 = A b                      |                                                    | occur Lo                               | ons)<br><u>RF or RLF</u><br>paded with LSb | or MSb, resp   | ectively    |

|         | Legend:                                                                 |                                                                                        |                                              |                                                    |                                        |                                            |                |             |

|         | R = Readab                                                              | ole bit                                                                                | W = W                                        | /ritable bit                                       | U = Un                                 | implemented bi                             | t, read as '0' |             |

|         | - n = Value a                                                           | at POR                                                                                 | '1' = B                                      | it is set                                          | '0' = Bit                              | t is cleared                               | x = Bit is un  | known       |

# 4.0 OSCILLATOR CONFIGURATIONS

### 4.1 Oscillator Types

The PIC16F5X devices can be operated in four different oscillator modes. The user can program two Configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LP: Low-power Crystal

- XT: Crystal/Resonator

- HS: High-speed Crystal/Resonator

- RC: Resistor/Capacitor

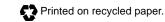

# 4.2 Crystal Oscillator/Ceramic Resonators

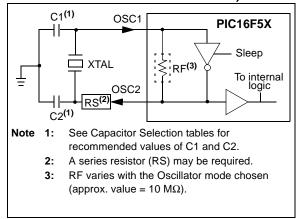

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 4-1). The PIC16F5X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency outside of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source drive the OSC1/CLKIN pin (Figure 4-2).

#### FIGURE 4-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

FIGURE 4-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

# TABLE 4-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Osc<br>Type | Resonator<br>Freq. | Cap. Range<br>C1 | Cap. Range<br>C2 |

|-------------|--------------------|------------------|------------------|

| XT          | 455 kHz            | 68-100 pF        | 68-100 pF        |

|             | 2.0 MHz            | 15-33 pF         | 15-33 pF         |

|             | 4.0 MHz            | 10-22 pF         | 10-22 pF         |

| HS          | 8.0 MHz            | 10-22 pF         | 10-22 pF         |

|             | 16.0 MHz           | 10 pF            | 10 pF            |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### TABLE 4-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Crystal<br>Freq.      | Cap.Range<br>C1                                                                                              | Cap. Range<br>C2                                                                                                                                                                                                                                                                                                         |

|-----------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32 kHz <sup>(1)</sup> | 15 pF                                                                                                        | 15 pF                                                                                                                                                                                                                                                                                                                    |

| 100 kHz               | 15-30 pF                                                                                                     | 200-300 pF                                                                                                                                                                                                                                                                                                               |

| 200 kHz               | 15-30 pF                                                                                                     | 100-200 pF                                                                                                                                                                                                                                                                                                               |

| 455 kHz               | 15-30 pF                                                                                                     | 15-100 pF                                                                                                                                                                                                                                                                                                                |

| 1 MHz                 | 15-30 pF                                                                                                     | 15-30 pF                                                                                                                                                                                                                                                                                                                 |

| 2 MHz                 | 15 pF                                                                                                        | 15 pF                                                                                                                                                                                                                                                                                                                    |

| 4 MHz                 | 15 pF                                                                                                        | 15 pF                                                                                                                                                                                                                                                                                                                    |

| 4 MHz                 | 15 pF                                                                                                        | 15 pF                                                                                                                                                                                                                                                                                                                    |

| 8 MHz                 | 15 pF                                                                                                        | 15 pF                                                                                                                                                                                                                                                                                                                    |

| 20 MHz                | 15 pF                                                                                                        | 15 pF                                                                                                                                                                                                                                                                                                                    |

|                       | Freq.<br>32 kHz <sup>(1)</sup><br>100 kHz<br>200 kHz<br>455 kHz<br>1 MHz<br>2 MHz<br>4 MHz<br>4 MHz<br>8 MHz | Freq.         C1           32 kHz <sup>(1)</sup> 15 pF           100 kHz         15-30 pF           200 kHz         15-30 pF           455 kHz         15-30 pF           1 MHz         15-30 pF           2 MHz         15 pF           4 MHz         15 pF           4 MHz         15 pF           8 MHz         15 pF |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specifications. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

2: The user should verify that the device oscillator starts and performs as expected. Adjusting the loading capacitor values and/or the Oscillator mode may be required.

Note 1: This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.

# PIC16F5X

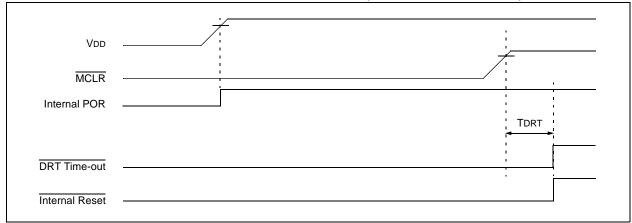

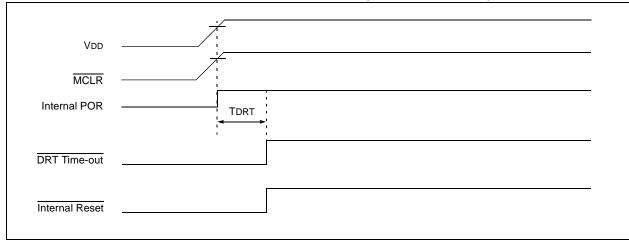

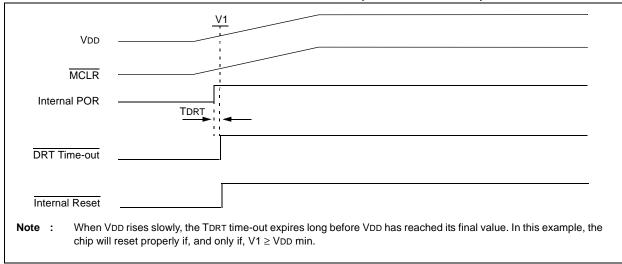

# FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

## FIGURE 5-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

# 6.8 I/O Programming Considerations

### 6.8.1 BIDIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit 5 of PORTB will cause all eight bits of PORTB to be read into the CPU, bit 5 to be set and the PORTB value to be written to the output latches. If another bit of PORTB is used as a bidirectional I/O pin (say bit '0'), and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit '0' is switched into Output mode later on, the content of the data latch may now be unknown

Example 6-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}, \ {\tt BSF}, \mbox{etc.})$  on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 6-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ;Initial PORT Settings<br>;PORTB<7:4> Inputs       |

|----------------------------------------------------|

| -                                                  |

| ;PORTB<3:0> Outputs                                |

| ;PORTB<7:6> have external pull-ups and are         |

| ;not connected to other circuitry                  |

| ;                                                  |

| ; PORT latch PORT pins                             |

| ;                                                  |

| BCF PORTB, 7 ;01pp pppp 11pp pppp                  |

| BCF PORTB, 6 ;10pp pppp 11pp pppp                  |

| MOVLW H'3F' ;                                      |

| TRIS PORTB ;10pp pppp 10pp pppp                    |

| ;                                                  |

| ;Note that the user may have expected the          |

| pin                                                |

| ;values to be 00pp pppp. The 2nd BCF caused        |

| ;RB7 to be latched as the pin value (High).        |

| pin<br>;values to be 00pp pppp. The 2nd BCF caused |

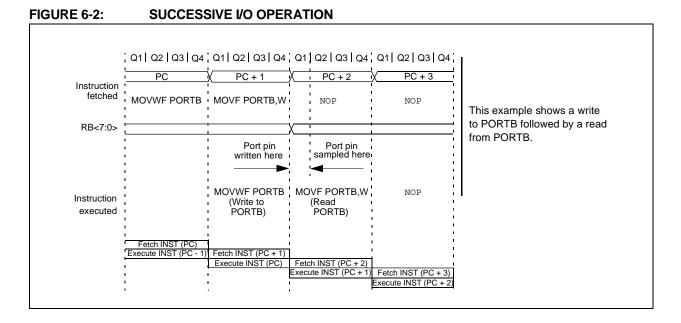

# 6.8.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (see Figure 6-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### © 2007 Microchip Technology Inc.

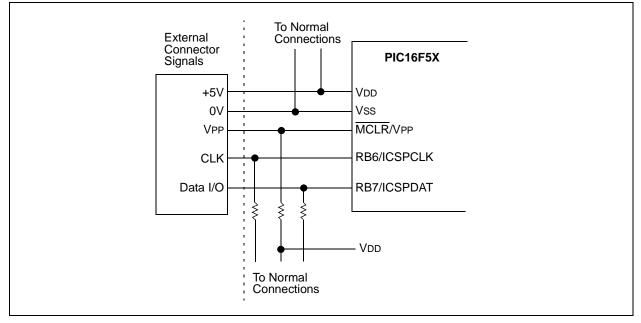

#### FIGURE 8-1: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> CONNECTION

| <b>TABLE 9-2:</b> | INSTRUCTION SET | SUMMARY |

|-------------------|-----------------|---------|

|-------------------|-----------------|---------|

| Mnemonic, Description C |           | Cycles                                           | 12-1             | Bit Opc   | ode       | Status    | Notes     |          |

|-------------------------|-----------|--------------------------------------------------|------------------|-----------|-----------|-----------|-----------|----------|

| Opera                   | nds       | Description                                      | Cycles           | MSb       |           | LSb       | Affected  | Notes    |

| ADDWF                   | f, d      | Add W and f                                      | 1                | 0001      | 11df      | ffff      | C,DC,Z    | 1, 2, 4  |

| ANDWF                   | f, d      | AND W with f                                     | 1                | 0001      | 01df      | ffff      | Z         | 2, 4     |

| CLRF                    | f         | Clear f                                          | 1                | 0000      | 011f      | ffff      | Z         | 4        |

| CLRW                    | —         | Clear W                                          | 1                | 0000      | 0100      | 0000      | Z         |          |

| COMF                    | f, d      | Complement f                                     | 1                | 0010      | 01df      | ffff      | Z         |          |

| DECF                    | f, d      | Decrement f                                      | 1                | 0000      | 11df      | ffff      | Z         | 2, 4     |

| DECFSZ                  | f, d      | Decrement f, Skip if 0                           | 1 <sup>(2)</sup> | 0010      | 11df      | ffff      | None      | 2, 4     |

| INCF                    | f, d      | Increment f                                      | 1                | 0010      | 10df      | ffff      | Z         | 2, 4     |

| INCFSZ                  | f, d      | Increment f, Skip if 0                           | 1 <sup>(2)</sup> | 0011      | 11df      | ffff      | None      | 2, 4     |

| IORWF                   | f, d      | Inclusive OR W with f                            | 1                | 0001      | 00df      | ffff      | Z         | 2, 4     |

| MOVF                    | f, d      | Move f                                           | 1                | 0010      | 00df      | ffff      | Z         | 2, 4     |

| MOVWF                   | f         | Move W to f                                      | 1                | 0000      | 001f      | ffff      | None      | 1, 4     |

| NOP                     | _         | No Operation                                     | 1                | 0000      | 0000      | 0000      | None      |          |

| RLF                     | f, d      | Rotate left f through Carry                      | 1                | 0011      | 01df      | ffff      | С         | 2, 4     |

| RRF                     | f, d      | Rotate right f through Carry                     | 1                | 0011      | 00df      | ffff      | С         | 2,4      |

| SUBWF                   | f, d      | Subtract W from f                                | 1                | 0000      | 10df      | ffff      | C,DC,Z    | 1, 2, 4  |

| SWAPF                   | f, d      | Swap f                                           | 1                | 0011      | 10df      | ffff      | None      | 2, 4     |

| XORWF                   | f, d      | Exclusive OR W with f                            | 1                | 0001      | 10df      | ffff      | Z         | 2, 4     |

| <b>BIT-ORIEN</b>        | TED FIL   | E REGISTER OPERATIONS                            | -                | -         |           |           |           | -        |

| BCF                     | f, b      | Bit Clear f                                      | 1                | 0100      | bbbf      | ffff      | None      | 2, 4     |

| BSF                     | f, b      | Bit Set f                                        | 1                | 0101      | bbbf      | ffff      | None      | 2, 4     |

| BTFSC                   | f, b      | Bit Test f, Skip if Clear                        | 1 <sup>(2)</sup> | 0110      | bbbf      | ffff      | None      |          |

| BTFSS                   | f, b      | Bit Test f, Skip if Set                          | 1 <sup>(2)</sup> | 0111      | bbbf      | ffff      | None      |          |

| LITERAL A               |           | ITROL OPERATIONS                                 | -                | -         |           |           |           |          |

| ANDLW                   | k         | AND literal with W                               | 1                | 1110      | kkkk      | kkkk      | Z         |          |

| CALL                    | k         | Subroutine Call                                  | 2                | 1001      | kkkk      | kkkk      | None      | 1        |

| CLRWDT                  | —         | Clear Watchdog Timer                             | 1                | 0000      | 0000      | 0100      | TO, PD    |          |

| GOTO                    | k         | Unconditional branch                             | 2                | 101k      | kkkk      | kkkk      | None      |          |

| IORLW                   | k         | Inclusive OR Literal with W                      | 1                | 1101      | kkkk      | kkkk      | Z         |          |

| MOVLW                   | k         | Move Literal to W                                | 1                | 1100      | kkkk      | kkkk      | None      |          |

| OPTION                  | —         | Load OPTION register                             | 1                | 0000      | 0000      | 0010      | None      |          |

| RETLW                   | k         | Return, place Literal in W                       | 2                | 1000      | kkkk      | kkkk      | None      |          |

| SLEEP                   | —         | Go into Standby mode                             | 1                | 0000      | 0000      | 0011      | TO, PD    |          |

| TRIS                    | f         | Load TRIS register                               | 1                | 0000      | 0000      | Offf      | None      | 3        |

| XORLW                   | k         | Exclusive OR Literal to W                        | 1                | 1111      | kkkk      | kkkk      | Z         |          |

| Note 1:                 | The 9th h | it of the program counter will be forced to a '0 | ' hy any i       | nstructio | on that y | writes to | the PC ex | cont for |

**Note 1:** The 9th bit of the program counter will be forced to a '0' by any instruction that writes to the PC except for GOTO (see Section 3.5 "Program Counter" for more on program counter).

2: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**3:** The instruction TRIS f, where f = 5, 6 or 7 causes the contents of the W register to be written to the tri-state latches of PORTA, B or C, respectively. A '1' forces the pin to a high-impedance state and disables the output buffers.

4: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

| CALL                                                                                                               | Subroutine Call                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                                                                            | [ <i>label</i> ] CALL k                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Operands:                                                                                                          | $0 \le k \le 255$                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Operation:                                                                                                         | $\begin{array}{l} (\text{PC}) + 1 \rightarrow \text{TOS}; \\ k \rightarrow \text{PC}{<}7:0{>}; \\ (\text{Status}{<}6:5{>}) \rightarrow \text{PC}{<}10:9{>}; \\ 0 \rightarrow \text{PC}{<}8{>} \end{array}$                                                           |  |  |  |  |  |  |

| Status Affected:                                                                                                   | fected: None                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Encoding:                                                                                                          | 1001 kkkk kkkk                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Description:                                                                                                       | Subroutine call. First, return<br>address (PC + 1) is pushed onto<br>the stack. The eight-bit immediate<br>address is loaded into PC bits<br><7:0>. The upper bits PC<10:9><br>are loaded from STATUS<6:5>,<br>PC<8> is cleared. CALL is a<br>two-cycle instruction. |  |  |  |  |  |  |

| Words:                                                                                                             | 1                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Cycles:                                                                                                            | 2                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Example:                                                                                                           | HERE CALL THERE                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Before Instruction<br>PC = address (HERE)<br>After Instruction<br>PC = address (THERE)<br>TOS = address (HERE + 1) |                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| CLRW             | Clear W                                                              |      |      |  |

|------------------|----------------------------------------------------------------------|------|------|--|

| Syntax:          | [ label ]                                                            | CLRW |      |  |

| Operands:        | None                                                                 |      |      |  |

| Operation:       | $\begin{array}{c} 00h \rightarrow (V \\ 1 \rightarrow Z \end{array}$ | V);  |      |  |

| Status Affected: | Z                                                                    |      |      |  |

| Encoding:        | 0000                                                                 | 0100 | 0000 |  |

| Description:     | Description: The W register is cleared. Zero bit                     |      |      |  |

|                  | (Z) is set                                                           |      |      |  |

| Words:           | 1                                                                    |      |      |  |

| Cycles:          | 1                                                                    |      |      |  |

| Example:         | CLRW                                                                 |      |      |  |

| Before Instru    | ction                                                                |      |      |  |

| W =              | 0x5A                                                                 |      |      |  |

| After Instruct   | ion                                                                  |      |      |  |

| W =              | 0x00                                                                 |      |      |  |

| Z =              | 1                                                                    |      |      |  |

#### CLRF Clear f

| -                                                          |                                                                      |                         |                               |

|------------------------------------------------------------|----------------------------------------------------------------------|-------------------------|-------------------------------|

| Syntax:                                                    | [ label ]                                                            | CLRF f                  |                               |

| Operands:                                                  | $0 \le f \le 3^{2}$                                                  | 1                       |                               |

| Operation:                                                 | $\begin{array}{c} 00h \rightarrow (f \\ 1 \rightarrow Z \end{array}$ | );                      |                               |

| Status Affected:                                           | Z                                                                    |                         |                               |

| Encoding:                                                  | 0000                                                                 | 011f                    | ffff                          |

| Description:                                               |                                                                      | ents of re<br>and the Z | gister 'f' are<br>bit is set. |

| Words:                                                     | 1                                                                    |                         |                               |

| Cycles:                                                    | 1                                                                    |                         |                               |

| Example:                                                   | CLRF                                                                 | FLAG_RE                 | IG                            |

| Before Instru<br>FLAG_RI<br>After Instruct<br>FLAG_RI<br>Z | EG =<br>ion                                                          | 0x5A<br>0x00<br>1       |                               |

| CLRWDT                                                                                      | Clear Wa                                                                                                                          | tchdog                                 | Timer                                 |              |  |  |  |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------|--------------|--|--|--|

| Syntax:                                                                                     | [label] CLRWDT                                                                                                                    |                                        |                                       |              |  |  |  |

| Operands:                                                                                   | None                                                                                                                              |                                        |                                       |              |  |  |  |

| Operation:                                                                                  | $\begin{array}{l} 00h \rightarrow W\\ 0 \rightarrow WDT\\ 1 \rightarrow \overline{TO};\\ 1 \rightarrow \overline{PD} \end{array}$ |                                        | er (if assi                           | gned);       |  |  |  |

| Status Affected:                                                                            | TO, PD                                                                                                                            |                                        |                                       |              |  |  |  |

| Encoding:                                                                                   | 0000                                                                                                                              | 0000                                   | 0100                                  |              |  |  |  |

| Description:                                                                                | The CLR<br>WDT. It a<br>the presc<br>WDT and<br>TO and P                                                                          | lso resets<br>aler is as<br>I not Time | s the pres<br>signed to<br>er0. Statu | caler if the |  |  |  |

| Words:                                                                                      | 1                                                                                                                                 |                                        |                                       |              |  |  |  |

| Cycles:                                                                                     | 1                                                                                                                                 |                                        |                                       |              |  |  |  |

| Example:                                                                                    | CLRWDT                                                                                                                            |                                        |                                       |              |  |  |  |

| Before Instru<br>WDT con<br>After Instruct<br>WDT con<br><u>WD</u> T pre<br><u>TO</u><br>PD | unter =<br>tion                                                                                                                   | ?<br>0x00<br>0<br>1<br>1               |                                       |              |  |  |  |

# PIC16F5X

| COMF                                                 | Complement f                                                                                                                                                                |  |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                              | [ <i>label</i> ] COMF f, d                                                                                                                                                  |  |  |  |

| Operands:                                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                |  |  |  |

| Operation:                                           | $(\overline{f}) \rightarrow (dest)$                                                                                                                                         |  |  |  |

| Status Affected:                                     | Z                                                                                                                                                                           |  |  |  |

| Encoding:                                            | 0010 01df ffff                                                                                                                                                              |  |  |  |

| Description:                                         | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back in<br>register 'f'. |  |  |  |

| Words:                                               | 1                                                                                                                                                                           |  |  |  |

| Cycles:                                              | 1                                                                                                                                                                           |  |  |  |

| Example:                                             | COMF REG1,0                                                                                                                                                                 |  |  |  |

| Before Instru<br>REG1<br>After Instruct<br>REG1<br>W | = 0x13                                                                                                                                                                      |  |  |  |

| DECF                                        | Decrement f                                                                                                                                       |  |  |  |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                     | [label] DECF f, d                                                                                                                                 |  |  |  |

| Operands:                                   | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                  |  |  |  |

| Operation:                                  | $(f) - 1 \rightarrow (dest)$                                                                                                                      |  |  |  |

| Status Affected:                            | Z                                                                                                                                                 |  |  |  |

| Encoding:                                   | 0000 11df ffff                                                                                                                                    |  |  |  |

| Description:                                | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |

| Words:                                      | 1                                                                                                                                                 |  |  |  |

| Cycles:                                     | 1                                                                                                                                                 |  |  |  |

| Example:                                    | DECF CNT, 1                                                                                                                                       |  |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct | = 0x01<br>= 0                                                                                                                                     |  |  |  |

| CNT<br>Z                                    | = 0x00<br>= 1                                                                                                                                     |  |  |  |

| DECFSZ                               | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                              | [label] DECFSZ f, d                                                                                                                                                                                                                                                                                                                        |

| Operands:                            | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                                                  |

| Operation:                           | $(f) - 1 \rightarrow d;$ skip if result = 0                                                                                                                                                                                                                                                                                                |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                            | 0010 11df ffff                                                                                                                                                                                                                                                                                                                             |

| Description:                         | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1'. the result is placed back in<br>register 'f'. If the result is '0', the<br>next instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a<br>two-cycle instruction. |

| Words:                               | 1                                                                                                                                                                                                                                                                                                                                          |

| Cycles:                              | 1(2)                                                                                                                                                                                                                                                                                                                                       |

| Example:                             | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                         |

| Before Instru<br>PC<br>After Instruc | = address (HERE)                                                                                                                                                                                                                                                                                                                           |

| CNT<br>if CNT<br>PC<br>if CNT<br>PC  | <pre>= CNT - 1;<br/>= 0,<br/>= address (CONTINUE);<br/>≠ 0,<br/>= address (HERE+1)</pre>                                                                                                                                                                                                                                                   |

### 10.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

# 10.12 PICkit 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

# 10.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart<sup>®</sup> battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest *"Product Selector Guide"* (DS00148) for the complete list of demonstration, development and evaluation kits.

# 11.0 ELECTRICAL SPECIFICATIONS FOR PIC16F59 (continued)

| -                                                                                                               | -                    |

|-----------------------------------------------------------------------------------------------------------------|----------------------|

| Absolute Maximum Ratings <sup>(†)</sup>                                                                         |                      |

| Ambient Temperature under bias                                                                                  | 40°C to +125°C       |

| Storage Temperature                                                                                             | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                                                              | 0V to +6.5V          |

| Voltage on MCLR with respect to Vss <sup>(1)</sup>                                                              | 0V to +13.5V         |

| Voltage on all other pins with respect to Vss                                                                   | 0.6V to (VDD + 0.6V) |

| Total power dissipation <sup>(2)</sup>                                                                          | 900 mW               |

| Max. current out of Vss pins                                                                                    | 250 mA               |

| Max. current into Vod pins                                                                                      | 200 mA               |

| Max. current into an input pin (T0CKI only)                                                                     | ±500 μA              |

| Input clamp current, Iк (Vi < 0 or Vi > Vod)                                                                    | ±20 mA               |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                  | ±20 mA               |

| Max. output current sunk by any I/O pin                                                                         | 25 mA                |

| Max. output current sourced by any I/O pin                                                                      | 25 mA                |

| Max. output current sourced by a single I/O port (PORTA, B, C, D or E)                                          | 100 mA               |

| Max. output current sunk by a single I/O port (PORTA, B, C, D or E)                                             | 100 mA               |

| Note 1. Voltage environmental holes $\sqrt{20}$ of the $\overline{MCLP}$ his inducing surroute greater then $S$ |                      |

- **Note 1:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50 to 100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

- 2: Power Dissipation is calculated as follows: Pdis = VDD x {IDD  $\Sigma$  IOH} +  $\Sigma$  {(VDD VOH) x IOH} +  $\Sigma$ (VOL x IOL)

†NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

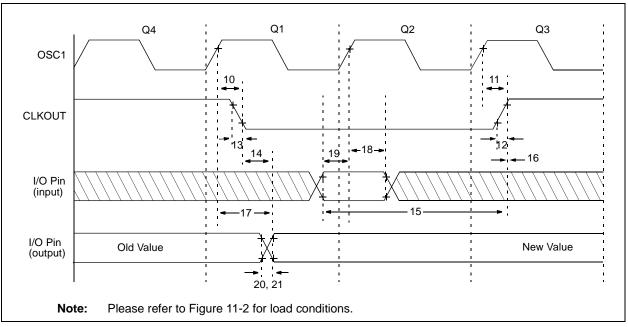

| Param<br>No. | Sym.     | Characteristic                                                        | Min.         | Тур† | Max. | Units |

|--------------|----------|-----------------------------------------------------------------------|--------------|------|------|-------|

| 10           | TosH2CKL | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                       | —            | 15   | 30** | ns    |

| 11           | TosH2CKH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑(1)</sup>                           | —            | 15   | 30** | ns    |

| 12           | TCKR     | CLKOUT rise time <sup>(1)</sup>                                       | —            | 5.0  | 15** | ns    |

| 13           | ТскF     | CLKOUT fall time <sup>(1)</sup>                                       | —            | 5.0  | 15** | ns    |

| 14           | TCKL2IOV | CLKOUT↓ to Port out valid <sup>(1)</sup>                              | —            | _    | 40** | ns    |

| 15           | ТюV2скН  | Port in valid before CLKOUT <sup>(1)</sup>                            | 0.25 TCY+30* | _    |      | ns    |

| 16           | TCKH2IOI | Port in hold after CLKOUT <sup>(1)</sup>                              | 0*           | _    | _    | ns    |

| 17           | TosH2IoV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2)</sup>         | —            | _    | 100* | ns    |

| 18           | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time) | TBD          | —    | _    | ns    |

| 19           | TIOV20sH | Port input valid to OSC1↑<br>(I/O in setup time)                      | TBD          | _    | _    | ns    |

| 20           | TIOR     | Port output rise time <sup>(2, 3)</sup>                               | —            | 10   | 25** | ns    |

| 20           | TIOR     | Port output rise time <sup>(2, 4)</sup>                               | —            | 10   | 50** | ns    |

| 21           | TIOF     | Port output fall time <sup>(2, 3)</sup> — 10 25**                     |              | 25** | ns   |       |

| 21           | TIOF     | Port output fall time <sup>(2, 4)</sup> — 10 50**                     |              | 50** | ns   |       |

TABLE 11-2: CLKOUT AND I/O TIMING REQUIREMENTS – PIC16F5X

**Legend:** TBD = To Be Determined.

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

**2:** Please refer to Figure 11-2 for load conditions.

3: PIC16F54/57 only.

4: PIC16F59 only.

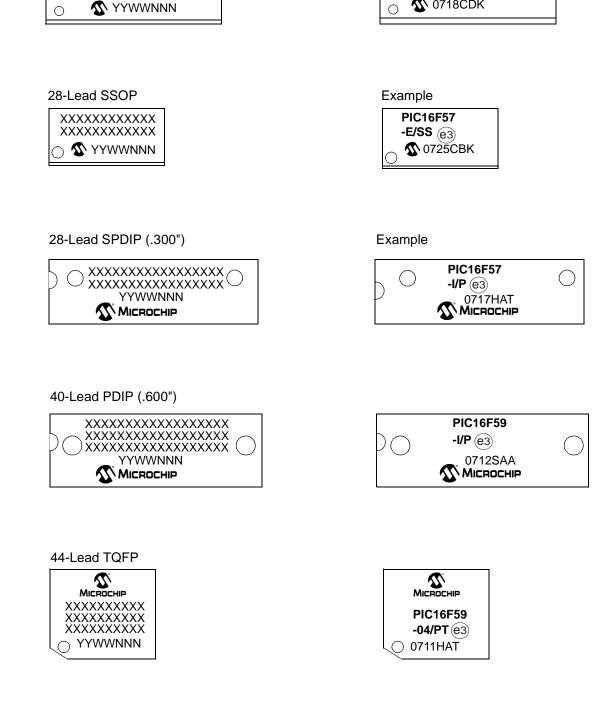

28-Lead SOIC

For the most current package drawings, please see the Microchip Packaging Specification located at

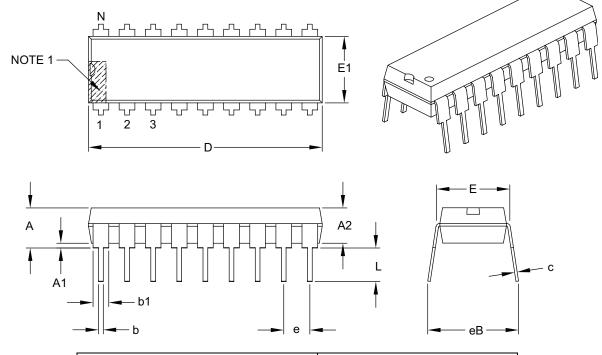

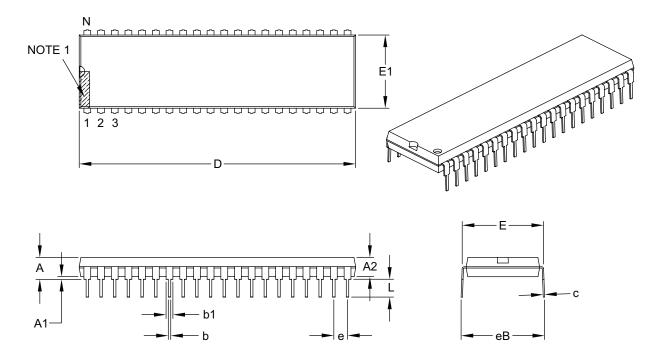

#### 18-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

http://www.microchip.com/packaging

INCHES Units **Dimension Limits** MIN NOM MAX Number of Pins 18 Ν Pitch .100 BSC е Top to Seating Plane .210 А \_ \_ Molded Package Thickness A2 .115 .130 .195 Base to Seating Plane A1 .015 \_ Shoulder to Shoulder Width Е .300 .310 .325 Molded Package Width .240 .250 .280 E1 **Overall Length** D .880 .900 .920 .130 Tip to Seating Plane .115 .150 L Lead Thickness .008 .010 .014 С Upper Lead Width b1 .045 .060 .070 Lower Lead Width b .014 .018 .022 Overall Row Spacing § .430 eВ

#### Notes:

Note:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-007B

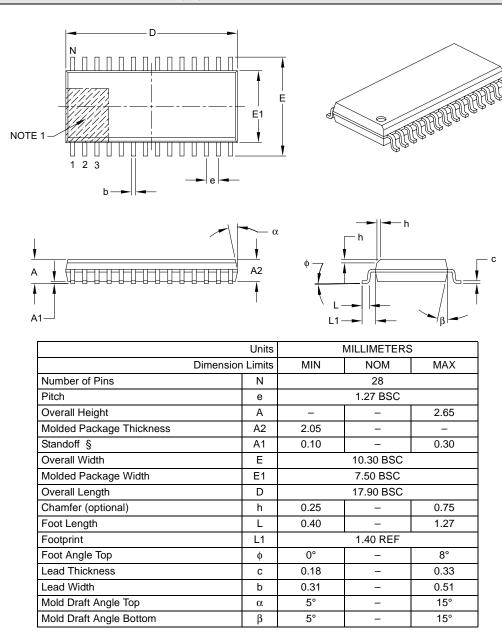

# 28-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-052B

# 40-Lead Plastic Dual In-Line (P) – 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES   |       |  |

|----------------------------|------------------|-------|----------|-------|--|

| Dimer                      | Dimension Limits |       |          | MAX   |  |

| Number of Pins             | N                |       | 40       |       |  |

| Pitch                      | е                |       | .100 BSC |       |  |

| Top to Seating Plane       | Α                | -     | -        | .250  |  |

| Molded Package Thickness   | A2               | .125  | -        | .195  |  |

| Base to Seating Plane      | A1               | .015  | -        | -     |  |

| Shoulder to Shoulder Width | E                | .590  | -        | .625  |  |

| Molded Package Width       | E1               | .485  | -        | .580  |  |

| Overall Length             | D                | 1.980 | -        | 2.095 |  |

| Tip to Seating Plane       | L                | .115  | -        | .200  |  |

| Lead Thickness             | С                | .008  | -        | .015  |  |

| Upper Lead Width           | b1               | .030  | -        | .070  |  |

| Lower Lead Width           | b                | .014  | -        | .023  |  |

| Overall Row Spacing §      | eB               | -     | -        | .700  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B

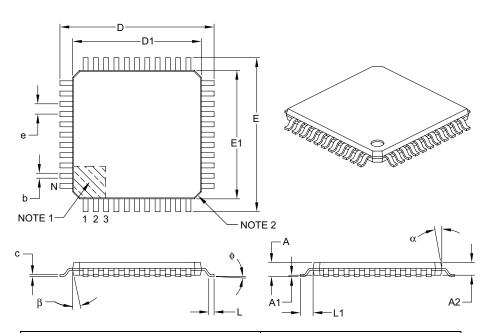

### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |      | ;         |      |

|--------------------------|------------------|------|-----------|------|

|                          | Dimension Limits | MIN  | NOM       | MAX  |

| Number of Leads          | N                |      | 44        |      |

| Lead Pitch               | е                |      | 0.80 BSC  |      |

| Overall Height           | А                | -    | _         | 1.20 |

| Molded Package Thickness | A2               | 0.95 | 1.00      | 1.05 |

| Standoff                 | A1               | 0.05 | -         | 0.15 |

| Foot Length              | L                | 0.45 | 0.60      | 0.75 |

| Footprint                | L1               |      | 1.00 REF  |      |

| Foot Angle               | φ                | 0°   | 3.5°      | 7°   |

| Overall Width            | E                |      | 12.00 BSC |      |

| Overall Length           | D                |      | 12.00 BSC |      |

| Molded Package Width     | E1               |      | 10.00 BSC |      |

| Molded Package Length    | D1               |      | 10.00 BSC |      |

| Lead Thickness           | С                | 0.09 | -         | 0.20 |

| Lead Width               | b                | 0.30 | 0.37      | 0.45 |

| Mold Draft Angle Top     | α                | 11°  | 12°       | 13°  |

| Mold Draft Angle Bottom  | β                | 11°  | 12°       | 13°  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B