Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 768B (512 x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 25 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 18-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f54t-i-so |

|                            |                                                                          |

### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, PS logo, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

NOTES:

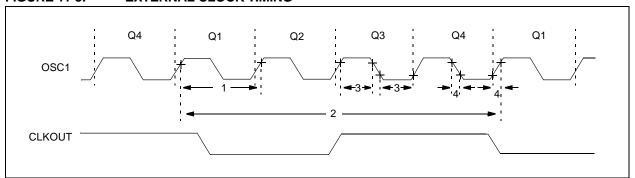

# 2.1 Clocking Scheme/Instruction Cycle

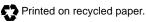

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the Program Counter (PC) is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 2-2 and Example 2-1.

## 2.2 Instruction Flow/Pipelining

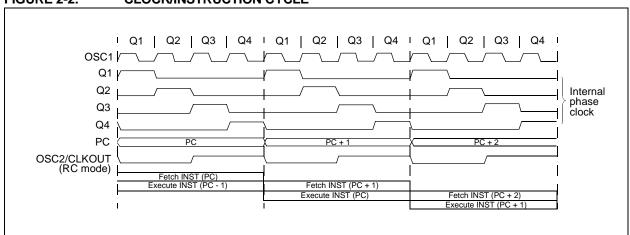

An instruction cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the Program Counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 2-1).

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the instruction register in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

FIGURE 2-2: CLOCK/INSTRUCTION CYCLE

# **EXAMPLE 2-1: INSTRUCTION PIPELINE FLOW**

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

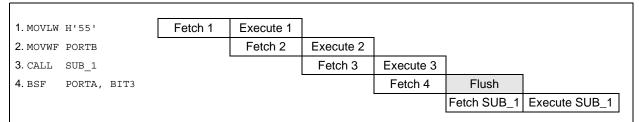

### 3.2 Data Memory Organization

Data memory is composed of registers or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers (SFR) and General Purpose Registers (GPR).

The Special Function Registers include the TMR0 register, the Program Counter (PC), the STATUS register, the I/O registers (ports) and the File Select Register (FSR). In addition, Special Purpose Registers are used to control the I/O port configuration and prescaler options.

The General Purpose Registers are used for data and control information under command of the instructions.

For the PIC16F54, the register file is composed of 7 Special Function Registers and 25 General Purpose Registers (Figure 3-3).

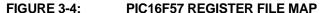

For the PIC16F57, the register file is composed of 8 Special Function Registers, 8 General Purpose Registers and 64 additional General Purpose Registers that may be addressed using a banking scheme (Figure 3-4).

For the PIC16F59, the register file is composed of 10 Special Function Registers, 6 General Purpose Registers and 128 additional General Purpose Registers that may be addressed using a banking scheme (Figure 3-5).

# 3.2.1 GENERAL PURPOSE REGISTER FILE

The register file is accessed either directly or indirectly through the File Select Register (FSR). The FSR register is described in Section 3.7 "Indirect Data Addressing; INDF and FSR Registers".

FIGURE 3-3: PIC16F54 REGISTER FILE MAP

Note 1: Not a physical register. See Section 3.7 "Indirect Data Addressing; INDF and FSR Registers".

# 3.5 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one, every instruction cycle, unless an instruction changes the PC.

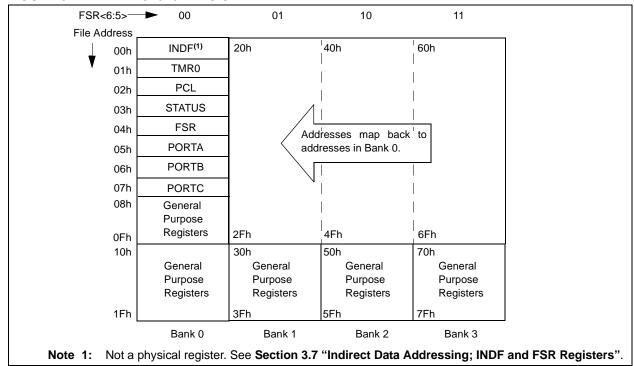

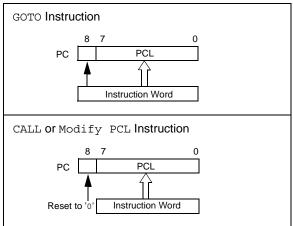

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The PC Latch (PCL) is mapped to PC<7:0> (Figure 3-6 and Figure 3-7).

For the PIC16F57 and PIC16F59, a page number must be supplied as well. Bit 5 and bit 6 of the STATUS register provide page information to bit 9 and bit 10 of the PC (Figure 3-6 and Figure 3-7).

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 3-6 and Figure 3-7).

Instructions where the PCL is the destination or modify PCL instructions, include  ${\tt MOVWF}$   ${\tt PCL}$ ,  ${\tt ADDWF}$   ${\tt PCL}$ , and  ${\tt BSF}$   ${\tt PCL}$ , 5 .

For the PIC16F57 and PIC16F59, a page number again must be supplied. Bit 5 and bit 6 of the STATUS register provide page information to bit 9 and bit 10 of the PC (Figure 3-6 and Figure 3-7).

Note: Because PC<8> is cleared in the CALL instruction or any modified PCL instruction, all subroutine calls or computed jumps are limited to the first 256 locations of any program memory page (512 words long).

FIGURE 3-6: LOADING OF PC BRANCH INSTRUCTIONS – PIC16F54

# FIGURE 3-7: LOADING OF PC BRANCH INSTRUCTIONS – PIC16F57 AND PIC16F59

# 3.5.1 PAGING CONSIDERATIONS PIC16F57 AND PIC16F59

If the PC is pointing to the last address of a selected memory page, when it increments, it will cause the program to continue in the next higher page. However, the page preselect bits in the STATUS register will not be updated. Therefore, the next GOTO, CALL or MODIFY PCL instruction will send the program to the page specified by the page preselect bits (PAO or PA<1:0>).

For example, a NOP at location 1FFh (page 0) increments the PC to 200h (page 1). A GOTO xxx at 200h will return the program to address xxh on page 0 (assuming that PA<1:0> are clear).

To prevent this, the page preselect bits must be updated under program control.

### 3.5.2 EFFECTS OF RESET

The PC is set upon a Reset, which means that the PC addresses the last location in the last page (i.e., the Reset vector).

The STATUS register page preselect bits are cleared upon a Reset, which means that page 0 is preselected.

Therefore, upon a Reset, a GOTO instruction at the Reset vector location will automatically cause the program to jump to page 0.

### 3.6 Stack

The PIC16F54 device has a 9-bit wide, two-level hardware PUSH/POP stack. The PIC16F57 and PIC16F59 devices have an 11-bit wide, two-level hardware PUSH/POP stack.

A CALL instruction will PUSH the current value of stack 1 into stack 2 and then PUSH the current program counter value, incremented by one, into stack level 1. If more than two sequential CALL's are executed, only the most recent two return addresses are stored.

A RETLW instruction will POP the contents of stack level 1 into the program counter and then copy stack level 2 contents into level 1. If more than two sequential RETLW's are executed, the stack will be filled with the address previously stored in level 2.

Note: The W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

For the RETLW instruction, the PC is loaded with the Top-of-Stack (TOS) contents. All of the devices covered in this data sheet have a two-level stack. The stack has the same bit width as the device PC, therefore, paging is not an issue when returning from a subroutine.

### 3.7 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR Register (FSR is a pointer). This is indirect addressing.

### **EXAMPLE 3-1:** INDIRECT ADDRESSING

- · Register file 08 contains the value 10h

- Register file 09 contains the value 0Ah

- Load the value 08 into the FSR register

- · A read of the INDF register will return the value

- · Increment the value of the FSR register by one (FSR = 09h)

- · A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 3-2.

### **HOW TO CLEAR RAM EXAMPLE 3-2:** USING INDIRECT **ADDRESSING**

```

MOVLW H'10'

;initialize pointer

MOVWF FSR

; to RAM

;clear INDF Register

NEXT

INDF

CLRF

INCF

FSR, F ; inc pointer

BTFSC FSR,4 ;all done?

;NO, clear next

GOTO

NEXT

CONTINUE

; YES, continue

```

The FSR is either a 5-bit (PIC16F54), 7-bit (PIC16F57) or 8-bit (PIC16F59) wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

PIC16F54: This does not use banking. FSR<7:5> bits are unimplemented and read as '1's.

**PIC16F57:** FSR<7> bit is unimplemented and read as '1'. FSR<6:5> are the bank select bits and are used to select the bank to be addressed (00 = Bank 0, 01 = Bank 1, 10 = Bank 2, 11 = Bank 3).

PIC16F59: FSR<7:5> are the bank select bits and are used to select the bank to be addressed

(000 = Bank 0, 001 = Bank 1, 010 = Bank 2,

011 = Bank 3, 100 = Bank 4, 101 = Bank 5,

110 = Bank 6, 111 = Bank 7).

Note: A CLRF FSR instruction may not result in an FSR value of 00h if there are unimplemented bits present in the FSR.

# 4.0 OSCILLATOR CONFIGURATIONS

# 4.1 Oscillator Types

The PIC16F5X devices can be operated in four different oscillator modes. The user can program two Configuration bits (FOSC1:FOSC0) to select one of these four modes:

LP: Low-power Crystal

• XT: Crystal/Resonator

• HS: High-speed Crystal/Resonator

RC: Resistor/Capacitor

# 4.2 Crystal Oscillator/Ceramic Resonators

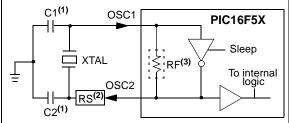

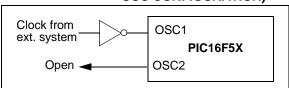

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 4-1). The PIC16F5X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency outside of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source drive the OSC1/CLKIN pin (Figure 4-2).

FIGURE 4-1: CRYSTAL/CERAMIC

RESONATOR OPERATION

(HS, XT OR LP OSC

CONFIGURATION)

**Note 1:** See Capacitor Selection tables for recommended values of C1 and C2.

**2:** A series resistor (RS) may be required.

3: RF varies with the Oscillator mode chosen (approx. value = 10 M $\Omega$ ).

FIGURE 4-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

TABLE 4-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Osc<br>Type | Resonator Freq. | Cap. Range<br>C1 | Cap. Range<br>C2 |  |  |  |  |

|-------------|-----------------|------------------|------------------|--|--|--|--|

| XT          | 455 kHz         | 68-100 pF        | 68-100 pF        |  |  |  |  |

|             | 2.0 MHz         | 15-33 pF         | 15-33 pF         |  |  |  |  |

|             | 4.0 MHz         | 10-22 pF         | 10-22 pF         |  |  |  |  |

| HS          | 8.0 MHz         | 10-22 pF         | 10-22 pF         |  |  |  |  |

|             | 16.0 MHz        | 10 pF            | 10 pF            |  |  |  |  |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

TABLE 4-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Osc<br>Type | Crystal<br>Freq.      | Cap.Range<br>C1 | Cap. Range<br>C2 |

|-------------|-----------------------|-----------------|------------------|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |

| XT          | 100 kHz               | 15-30 pF        | 200-300 pF       |

|             | 200 kHz               | 15-30 pF        | 100-200 pF       |

|             | 455 kHz               | 15-30 pF        | 15-100 pF        |

|             | 1 MHz                 | 15-30 pF        | 15-30 pF         |

|             | 2 MHz                 | 15 pF           | 15 pF            |

|             | 4 MHz                 | 15 pF           | 15 pF            |

| HS          | 4 MHz                 | 15 pF           | 15 pF            |

|             | 8 MHz                 | 15 pF           | 15 pF            |

|             | 20 MHz                | 15 pF           | 15 pF            |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specifications. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

# Note 1: This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.

2: The user should verify that the device oscillator starts and performs as expected. Adjusting the loading capacitor values and/or the Oscillator mode may be required.

TABLE 6-1: SUMMARY OF PORT REGISTERS

| Address | Name                 | Bit 7   | Bit 6    | Bit 5      | Bit 4    | Bit 3    | Bit 2   | Bit 1   | Bit 0  | Value on<br>Power-on<br>Reset | Value on MCLR and WDT Reset |

|---------|----------------------|---------|----------|------------|----------|----------|---------|---------|--------|-------------------------------|-----------------------------|

| N/A     | TRIS                 | I/O Con | trol Reg | isters (TI | RISA, TF | RISB, TR | ISC, TR | ISD and | TRISE) | 1111 1111                     | 1111 1111                   |

| 05h     | PORTA                | _       | _        | _          | _        | RA3      | RA2     | RA1     | RA0    | xxxx                          | uuuu                        |

| 06h     | PORTB                | RB7     | RB6      | RB5        | RB4      | RB3      | RB2     | RB1     | RB0    | xxxx xxxx                     | uuuu uuuu                   |

| 07h     | PORTC <sup>(1)</sup> | RC7     | RC6      | RC5        | RC4      | RC3      | RC2     | RC1     | RC0    | xxxx xxxx                     | uuuu uuuu                   |

| 08h     | PORTD <sup>(2)</sup> | RD7     | RD6      | RD5        | RD4      | RD3      | RD2     | RD1     | RD0    | xxxx xxxx                     | uuuu uuuu                   |

| 09h     | PORTE <sup>(2)</sup> | RE7     | RE6      | RE5        | RE4      |          | _       | _       |        | xxxx                          | uuuu                        |

**Legend:** Shaded cells = unimplemented, read as '0', - = unimplemented, read as '0', x = unknown,

u = unchanged

**Note 1:** File address 07h is a General Purpose Register on the PIC16F54.

2: File address 08h and 09h are General Purpose Registers on the PIC16F54 and PIC16F57.

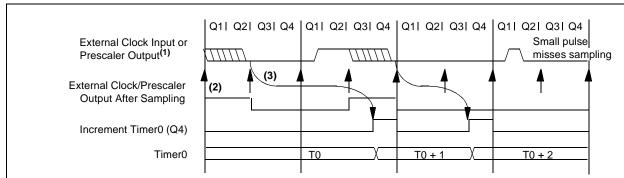

# 7.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

# 7.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock is the Timer0 input. The synchronization of ToCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-4). Therefore, it is necessary for ToCKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 7.1.2 TIMERO INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-4 shows the delay from the external clock edge to the timer incrementing.

### FIGURE 7-4: TIMERO TIMING WITH EXTERNAL CLOCK

- Note 1: External clock if no prescaler selected; prescaler output otherwise.

- 2: The arrows indicate the points in time where sampling occurs.

- 3: Delay from clock input change to Timer0 increment is 3Tosc to 7Tosc (duration of Q = Tosc). Therefore, the error in measuring the interval between two edges on Timer0 input = ± 4Tosc max.

### 7.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer (WDT), respectively (Section 8.2.1 "WDT Period"). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a Reset, the prescaler contains all '0's.

| IORLW            | Inclusive OR literal with W                                                                                       |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] IORLW k                                                                                                 |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                               |  |  |  |  |

| Operation:       | (W) .OR. $(k) \rightarrow (W)$                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                 |  |  |  |  |

| Encoding:        | 1101 kkkk kkkk                                                                                                    |  |  |  |  |

| Description:     | The contents of the W register are OR'ed with the eight-bit literal 'k'.  The result is placed in the W register. |  |  |  |  |

| Words:           | 1                                                                                                                 |  |  |  |  |

| Cycles:          | 1                                                                                                                 |  |  |  |  |

| Example:         | IORLW 0x35                                                                                                        |  |  |  |  |

|                  | 0x9A                                                                                                              |  |  |  |  |

| 7 –              | 0                                                                                                                 |  |  |  |  |

| IORWF                                                              | Inclusive OR W with f                                                                                                                                           |  |  |  |  |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                            | [ label ] IORWF f, d                                                                                                                                            |  |  |  |  |

| Operands:                                                          | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                               |  |  |  |  |

| Operation:                                                         | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                |  |  |  |  |

| Status Affected:                                                   | Z                                                                                                                                                               |  |  |  |  |

| Encoding:                                                          | 0001 00df ffff                                                                                                                                                  |  |  |  |  |

| Description:                                                       | Inclusive OR the W register with register 'f'. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |  |  |

| Words:                                                             | 1                                                                                                                                                               |  |  |  |  |

| Cycles:                                                            | 1                                                                                                                                                               |  |  |  |  |

| Example:                                                           | IORWF RESULT, 0                                                                                                                                                 |  |  |  |  |

| Before Instru<br>RESULT<br>W<br>After Instruct<br>RESULT<br>W<br>Z | $\Gamma = 0x13$<br>= 0x91<br>tion                                                                                                                               |  |  |  |  |

| MOVF                   | Move f                                                                                                                                                                                                                                     |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                | [ label ] MOVF f, d                                                                                                                                                                                                                        |

| Operands:              | $\begin{aligned} 0 &\leq f \leq 31 \\ d &\in [0,1] \end{aligned}$                                                                                                                                                                          |

| Operation:             | $(f) \to (dest)$                                                                                                                                                                                                                           |

| Status Affected:       | Z                                                                                                                                                                                                                                          |

| Encoding:              | 0010 00df ffff                                                                                                                                                                                                                             |

| Description:           | The contents of register 'f' is moved to destination 'd'. If 'd' is 'o', destination is the W register. If 'd' is '1', the destination is file register 'f'. 'd' is '1' is useful to test a file register since Status flag Z is affected. |

| Words:                 | 1                                                                                                                                                                                                                                          |

| Cycles:                | 1                                                                                                                                                                                                                                          |

| Example:               | MOVF FSR, 0                                                                                                                                                                                                                                |

| After Instructi<br>W = | on<br>value in FSR register                                                                                                                                                                                                                |

| Syntax:          | [ label ]       | MOVLW                      | k    |     |

|------------------|-----------------|----------------------------|------|-----|

| Operands:        | $0 \le k \le 2$ | 55                         |      |     |

| Operation:       | $k\to(W)$       |                            |      |     |

| Status Affected: | None            |                            |      |     |

| Encoding:        | 1100            | kkkk                       | kkkk |     |

| Description:     | •               | t-bit litera<br>V register |      | ded |

| Words:           | 1               |                            |      |     |

| Cyclos           | 1               |                            |      |     |

| Cycles:          |                 |                            |      |     |

| MOVWF                   | Move W                | to f       |           |         |

|-------------------------|-----------------------|------------|-----------|---------|

| Syntax:                 | [ label]              | MOVWF      | f         |         |

| Operands:               | $0 \le f \le 31$      | 1          |           |         |

| Operation:              | $(W) \rightarrow (f)$ | )          |           |         |

| Status Affected:        | None                  |            |           |         |

| Encoding:               | 0000                  | 001f       | ffff      |         |

| Description:            | Move da               | ta from th | e W regis | ster to |

| Words:                  | 1                     |            |           |         |

| Cycles:                 | 1                     |            |           |         |

| Example:                | MOVWF                 | TEMP_RE    | EG        |         |

| Before Instru<br>TEMP I |                       | 0xFF       |           |         |

| W                       |                       | 0x4F       |           |         |

| After Instruct          |                       | 0.45       |           |         |

| TEMP_I                  |                       | 0x4F       |           |         |

| W                       | =                     | 0x4F       |           |         |

| OPTION           | Load Of             | PTION R     | egister |  |

|------------------|---------------------|-------------|---------|--|

| Syntax:          | [ label ]           | OPTION      | ١       |  |

| Operands:        | None                |             |         |  |

| Operation:       | $(W) \rightarrow C$ | PTION       |         |  |

| Status Affected: | None                |             |         |  |

| Encoding:        | 0000                | 0000        | 0010    |  |

| Description:     |                     | tent of the | J       |  |

| Words:           | 1                   |             |         |  |

| Cycles:          | 1                   |             |         |  |

| Example:         | OPTION              |             |         |  |

| Before Instru    | ction               |             |         |  |

| W                | = 0x                | 07          |         |  |

| After Instructi  | on                  |             |         |  |

| OPTION           | = 0x                | 07          |         |  |

|                  |                     |             |         |  |

| NOP              | No Operation |        |      |  |  |

|------------------|--------------|--------|------|--|--|

| Syntax:          | [ label]     | NOP    |      |  |  |

| Operands:        | None         |        |      |  |  |

| Operation:       | No operation |        |      |  |  |

| Status Affected: | None         |        |      |  |  |

| Encoding:        | 0000         | 0000   | 0000 |  |  |

| Description:     | No opera     | ation. |      |  |  |

| Words:           | 1            |        |      |  |  |

| Cycles:          | 1            |        |      |  |  |

| Example:         | NOP          |        |      |  |  |

```

RETLW

Return with Literal in W

Syntax:

[label] RETLW k

Operands:

0 \le k \le 255

Operation:

k \rightarrow (W);

\mathsf{TOS} \to \mathsf{PC}

Status Affected:

None

Encoding:

1000

kkkk

kkkk

Description:

The W register is loaded with the

eight-bit literal 'k'. The program

counter is loaded from the top of

the stack (the return address). This

is a two-cycle instruction.

Words:

Cycles:

2

Example:

CALL TABLE; W contains

;table offset

; value.

;W now has table

;value.

TABLE

ADDWF PC ;W = offset

RETLW k1

;Begin table

RETLW k2

RETLW kn ; End of table

Before Instruction

W

0x07

After Instruction

W

value of k8

```

| RLF                   | Rotate Left f through Carry                                                                                                                                                                                       |      |       |    |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----|--|

| Syntax:               | [ labe                                                                                                                                                                                                            | /] R | LF f, | d  |  |

| Operands:             | $0 \le f \le d \in [0]$                                                                                                                                                                                           |      |       |    |  |

| Operation:            | See description below                                                                                                                                                                                             |      |       |    |  |

| Status Affected:      | С                                                                                                                                                                                                                 |      |       |    |  |

| Encoding:             | 0011 01df ffff                                                                                                                                                                                                    |      |       |    |  |

| Description:          | The contents of register 'f' are rotated one bit to the left through the Carry Flag (STATUS<0>). If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is stored back in register 'f'. |      |       |    |  |

| Words:                | 1                                                                                                                                                                                                                 |      |       |    |  |

| Cycles:               | 1                                                                                                                                                                                                                 |      |       |    |  |

| Example:              | RLF                                                                                                                                                                                                               | RI   | EG1,0 |    |  |

| Before Instru         | uction                                                                                                                                                                                                            |      |       |    |  |

| REG1                  | =                                                                                                                                                                                                                 | 111  | 0 011 | .0 |  |

| C                     | =                                                                                                                                                                                                                 | 0    |       |    |  |

| After Instruc<br>REG1 | uon<br>=                                                                                                                                                                                                          | 111  | 0 011 | 0  |  |

| W                     | =                                                                                                                                                                                                                 |      | 0 110 | -  |  |

|                       |                                                                                                                                                                                                                   |      |       | -  |  |

1

| RRF                                                            | Rotate Right f through Carry                                                                                                                                                                                       |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                        | [ label ] RRF f, d                                                                                                                                                                                                 |

| Operands:                                                      | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                                                  |

| Operation:                                                     | See description below                                                                                                                                                                                              |

| Status Affected:                                               | С                                                                                                                                                                                                                  |

| Encoding:                                                      | 0011 00df ffff                                                                                                                                                                                                     |

| Description:                                                   | The contents of register 'f' are rotated one bit to the right through the Carry Flag (STATUS<0>). If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |

| Words:                                                         | 1                                                                                                                                                                                                                  |

| Cycles:                                                        | 1                                                                                                                                                                                                                  |

| Example:                                                       | RRF REG1,0                                                                                                                                                                                                         |

| Before Instru<br>REG1<br>C<br>After Instruct<br>REG1<br>W<br>C | = 1110 0110<br>= 0                                                                                                                                                                                                 |

| Sleep            | Go into Standby Mode                                                                         |                                                             |                                                             |                        |  |  |

|------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|------------------------|--|--|

| Syntax:          | [ label ] Sleep                                                                              |                                                             |                                                             |                        |  |  |

| Operands:        | None                                                                                         |                                                             |                                                             |                        |  |  |

| Operation:       | 00h → WDT;<br>0 → WDT prescaler; if assigned<br>1 → $\overline{TO}$ ;<br>0 → $\overline{PD}$ |                                                             |                                                             |                        |  |  |

| Status Affected: | TO, PD                                                                                       |                                                             |                                                             |                        |  |  |

| Encoding:        | 0000 0000 0011                                                                               |                                                             |                                                             |                        |  |  |

| Description:     | Time-out power-do cleared. prescaler The proc mode wit See sectidetails.                     | own Statu<br>The WDT<br>are clea<br>essor is p<br>h the osc | is bit (PD<br>and its<br>red.<br>out into S<br>cillator sto | ) is<br>leep<br>opped. |  |  |

| Words:           | 1                                                                                            |                                                             |                                                             |                        |  |  |

| Cycles:          | 1                                                                                            |                                                             |                                                             |                        |  |  |

| Example:         | SLEEP                                                                                        |                                                             |                                                             |                        |  |  |

С

| SUBWF                    | Subtract W from f                                                                                         | SWAPF                                 | Swap Nibbles in f                                                                                           |

|--------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Syntax:                  | [ label ] SUBWF f, d                                                                                      | Syntax:                               | [ label] SWAPF f, d                                                                                         |

| Operands:                | $0 \le f \le 31$<br>$d \in [0,1]$                                                                         | Operands:                             | $0 \le f \le 31$<br>$d \in [0,1]$                                                                           |

| Operation:               | $ (f) - (W) \rightarrow (dest) $                                                                          | Operation:                            | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                   |

| Status Affected:         | C, DC, Z                                                                                                  | Status Affected:                      | None                                                                                                        |

| Encoding:                | 0000 10df ffff                                                                                            | Encoding:                             | 0011 10df ffff                                                                                              |

| Description:             | Subtract (2's complement method)<br>the W register from register 'f'. If 'd'                              | Description:                          | The upper and lower nibbles of                                                                              |

|                          | is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. | Boompton.                             | register 'f' are exchanged. If 'd' is '0', the result is placed in W register. If 'd' is '1', the result is |

| Words:                   | 1                                                                                                         |                                       | placed in register 'f'.                                                                                     |

| Cycles:                  | 1                                                                                                         | Words:                                | 1                                                                                                           |

| Example 1:               | SUBWF REG1, 1                                                                                             | Cycles:                               | 1                                                                                                           |

| Before Instru            | uction                                                                                                    | Example:                              | SWAPF REG1, 0                                                                                               |

| REG1<br>W<br>C           | = 3<br>= 2<br>= ?                                                                                         | Before Instr<br>REG1<br>After Instruc | = 0xA5                                                                                                      |

| After Instruct           |                                                                                                           | REG1<br>W                             | = 0xA5                                                                                                      |

| REG1<br>W                | = 1<br>= 2                                                                                                | VV                                    | = 0x5A                                                                                                      |

| Ċ                        | = 1 ; result is positive                                                                                  |                                       |                                                                                                             |

| Example 2:               |                                                                                                           | TRIS                                  | Load TRIS Register                                                                                          |

| Before Instru            |                                                                                                           | Syntax:                               | [label] TRIS f                                                                                              |

| REG1<br>W                | = 2<br>= 2                                                                                                | Operands:                             | f = 5, 6, 7, 8 or 9                                                                                         |

| Č                        | = ?                                                                                                       | •                                     |                                                                                                             |

| After Instruc            | tion                                                                                                      | Operation:                            | (W) → TRIS register f                                                                                       |

| REG1                     | = 0                                                                                                       | Status Affected:                      | None                                                                                                        |

| W                        | = 2                                                                                                       | Encoding:                             | 0000 0000 0fff                                                                                              |

| C<br>Everante 2:         | = 1 ; result is zero                                                                                      | Description:                          | TRIS register 'f' $(f = 5, 6 \text{ or } 7)$ is                                                             |

| Example 3:<br>Before Ins | etruction                                                                                                 |                                       | loaded with the contents of the W                                                                           |

| REG1                     | = 1                                                                                                       |                                       | register.                                                                                                   |

| W                        | = 2                                                                                                       | Words:                                | 1                                                                                                           |

| С                        | = ?                                                                                                       | Cycles:                               | 1                                                                                                           |

| After Instruc            |                                                                                                           | Example:                              | TRIS PORTB                                                                                                  |

| REG1                     | = 0xFF                                                                                                    | Before Instru                         | uction                                                                                                      |

| W                        | = 2                                                                                                       | W                                     | = 0xA5                                                                                                      |

| С                        | = 0 ; result is negative                                                                                  | After Instruc<br>TRISB                | tion<br>= 0xA5                                                                                              |

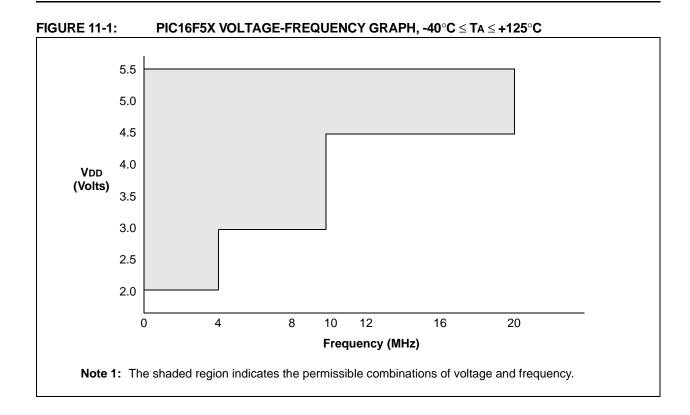

# 11.0 ELECTRICAL SPECIFICATIONS FOR PIC16F59 (continued)

# Absolute Maximum Ratings(†)

| <del></del>                                                                  | 1000 / 10500         |

|------------------------------------------------------------------------------|----------------------|

| Ambient Temperature under bias                                               | 40°C to +125°C       |

| Storage Temperature                                                          | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                           | 0V to +6.5V          |

| Voltage on MCLR with respect to Vss <sup>(1)</sup>                           | 0V to +13.5V         |

| Voltage on all other pins with respect to Vss                                | 0.6V to (VDD + 0.6V) |

| Total power dissipation <sup>(2)</sup>                                       | 900 mW               |

| Max. current out of Vss pins                                                 | 250 mA               |

| Max. current into VDD pins                                                   | 200 mA               |

| Max. current into an input pin (T0CKI only)                                  | ±500 μA              |

| Input clamp current, IiK (VI < 0 or VI > VDD)                                | ±20 mA               |

| Output clamp current, IOK (VO < 0 or VO > VDD)                               | ±20 mA               |

| Max. output current sunk by any I/O pin                                      | 25 mA                |

| Max. output current sourced by any I/O pin                                   | 25 mA                |

| Max. output current sourced by a single I/O port (PORTA, B, C, D or E)       | 100 mA               |

| Max. output current sunk by a single I/O port (PORTA, B, C, D or E)          | 100 mA               |

| Note 4. Vallege entire below Vocatiles MOLD at a traduction assessed and the | 00 4                 |

- **Note 1:** Voltage spikes below Vss at the  $\overline{MCLR}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50 to  $100\Omega$  should be used when applying a "low" level to the  $\overline{MCLR}$  pin rather than pulling this pin directly to Vss.

- 2: Power Dissipation is calculated as follows: Pdis = VDD x {IDD  $-\sum IOH$ } +  $\sum {(VDD VOH) \times IOH}$  +  $\sum (VOL \times IOL)$

†NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 11.1 DC Characteristics: PIC16F5X (Industrial)

| IDC CHARACIERISTICS |      |                                               | Standard Operating Conditions (unless otherwise specified) Operating Temperature -40 $^{\circ}$ C $\leq$ TA $\leq$ +85 $^{\circ}$ C for industrial |      |      |       |                                                                      |

|---------------------|------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|----------------------------------------------------------------------|

| Param<br>No.        | Sym. | Characteristic/Device                         | Min.                                                                                                                                               | Тур† | Max. | Units | Conditions                                                           |

| D001                | Vdd  | Supply Voltage                                | 2.0                                                                                                                                                | —    | 5.5  | V     |                                                                      |

| D002                | Vdr  | RAM Data Retention Voltage <sup>(1)</sup>     | _                                                                                                                                                  | 1.5* | _    | V     | Device in Sleep mode                                                 |

| D003                | VPOR | VDD Start Voltage to ensure<br>Power-on Reset | _                                                                                                                                                  | Vss  | _    | V     | See Section 5.1 "Power-on Reset (POR)" for details on Power-on Reset |

| D004                | SVDD | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*                                                                                                                                              | _    | _    | V/ms  | See Section 5.1 "Power-on Reset (POR)" for details on Power-on Reset |

| D010                | IDD  | Supply Current <sup>(2)</sup>                 |                                                                                                                                                    |      |      |       |                                                                      |

|                     |      |                                               | _                                                                                                                                                  | 170  | 350  | μА    | Fosc = 4 MHz, VDD = 2.0V, XT or RC mode <sup>(3)</sup>               |

|                     |      |                                               | _                                                                                                                                                  | 0.4  | 1.0  | mΑ    | FOSC = 10 MHz, VDD = 3.0V, HS mode                                   |

|                     |      |                                               | _                                                                                                                                                  | 1.7  | 5.0  |       | FOSC = 20 MHz, VDD = 5.0V, HS mode                                   |

|                     |      |                                               | _                                                                                                                                                  | 15   | 22.5 | μΑ    | $FOSC = 32 \text{ kHz}, VDD = 2.0V, LP mode,}$                       |

|                     |      |                                               |                                                                                                                                                    |      |      |       | WDT disabled                                                         |

| D020                | IPD  | Power-down Current <sup>(2)</sup>             |                                                                                                                                                    |      |      |       |                                                                      |

|                     |      |                                               | _                                                                                                                                                  | 1.0  | 6.0  | μΑ    | VDD = 2.0V, WDT enabled                                              |

|                     |      |                                               | _                                                                                                                                                  | 0.5  | 2.5  | μΑ    | VDD = 2.0V, WDT disabled                                             |

<sup>\*</sup> These parameters are characterized but not tested.

- Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature, also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in Sleep mode. The Power-down Current in Sleep mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in  $k\Omega$ .

<sup>†</sup> Data in "Typ" column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

# 11.2 DC Characteristics: PIC16F5X (Extended)

|              |      | Standard Operating Conditions (unless otherwise specified) Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |       |      |      |       |                                                                      |

|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|----------------------------------------------------------------------|

| Param<br>No. | Sym. | Characteristic/Device                                                                                                                                      | Min.  | Тур† | Max. | Units | Conditions                                                           |

| D001         | Vdd  | Supply Voltage                                                                                                                                             | 2.0   | _    | 5.5  | V     |                                                                      |

| D002         | Vdr  | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                                  | _     | 1.5* | _    | V     | Device in Sleep mode                                                 |

| D003         | VPOR | VDD Start Voltage to ensure<br>Power-on Reset                                                                                                              | _     | Vss  | _    | V     | See Section 5.1 "Power-on Reset (POR)" for details on Power-on Reset |

| D004         | SVDD | VDD Rise Rate to ensure<br>Power-on Reset                                                                                                                  | 0.05* | _    | _    | V/ms  | See Section 5.1 "Power-on Reset (POR)" for details on Power-on Reset |

| D010         | IDD  | Supply Current <sup>(2)</sup>                                                                                                                              |       |      |      |       |                                                                      |

|              |      |                                                                                                                                                            | _     | 170  | 450  | μА    | FOSC = 4 MHz, $VDD = 2.0V$ , XT or RC mode <sup>(3)</sup>            |

|              |      |                                                                                                                                                            | _     | 0.4  | 2.0  | mA    | FOSC = 10 MHz, VDD = 3.0V, HS mode                                   |

|              |      |                                                                                                                                                            | _     | 1.7  | 7.0  | mA    | FOSC = 20 MHz, VDD = 5.0V, HS mode                                   |

|              |      |                                                                                                                                                            | _     | 15   | 40   | μΑ    | FOSC = 32 kHz, VDD = 2.0V, LP mode,                                  |

|              |      |                                                                                                                                                            |       |      |      |       | WDT disabled                                                         |

| D020         | IPD  | Power-down Current <sup>(2)</sup>                                                                                                                          |       |      |      |       |                                                                      |

|              |      |                                                                                                                                                            | _     | 1.0  | 15.0 | μΑ    | VDD = 2.0V, WDT enabled                                              |

|              |      |                                                                                                                                                            | _     | 0.5  | 8.0  | μΑ    | VDD = 2.0V, WDT disabled                                             |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature, also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in Sleep mode. The Power-down Current in Sleep mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in  $k\Omega$ .

# 11.4 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| T |                                         |   |      |

|---|-----------------------------------------|---|------|

| F | Frequency                               | Т | Time |

| 1 | reas a lettera (nm) and their meanings. |   |      |

Lowercase letters (pp) and their meanings:

|     | energes letters (pp) and then meanings. |                    |  |  |  |  |

|-----|-----------------------------------------|--------------------|--|--|--|--|

| pp  |                                         |                    |  |  |  |  |

| 2   | to                                      | mc MCLR            |  |  |  |  |

| ck  | CLKOUT                                  | osc oscillator     |  |  |  |  |

| су  | cycle time                              | os OSC1            |  |  |  |  |

| drt | device reset timer                      | t0 T0CKI           |  |  |  |  |

| io  | I/O port                                | wdt watchdog timer |  |  |  |  |

Uppercase letters and their meanings:

| S | 3.                       |   |                |

|---|--------------------------|---|----------------|

| F | Fall                     | Р | Period         |

| Н | High                     | R | Rise           |

| 1 | Invalid (High-impedance) | V | Valid          |

| L | Low                      | Z | High-impedance |

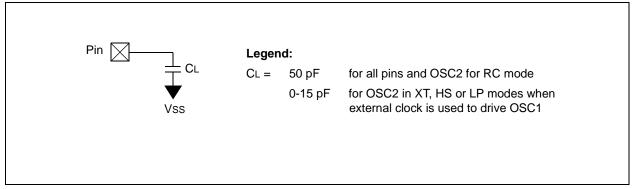

# FIGURE 11-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS – PIC16F5X

# 11.5 Timing Diagrams and Specifications

### FIGURE 11-3: EXTERNAL CLOCK TIMING

| A                                                      |      | G                                                 |       |

|--------------------------------------------------------|------|---------------------------------------------------|-------|

| Absolute Maximum Ratings                               |      | GOTO19                                            | 9, 47 |

| PIC1654/57                                             | 57   |                                                   | •     |

| PIC1659                                                | 58   | Н                                                 |       |

| ADDWF                                                  | 43   | High-Performance RISC CPU                         | 1     |

| ALU                                                    | 7    | 1                                                 |       |

| ANDLW                                                  | 43   | I                                                 |       |

| ANDWF                                                  | 43   | I/O Interfacing                                   | 29    |

| Applications                                           | 5    | I/O Ports                                         | 29    |

| Architectural Overview                                 |      | I/O Programming Considerations                    | 31    |

| Assembler                                              |      | ID Locations                                      | 7, 39 |

| MPASM Assembler                                        | 54   | INCF                                              | 47    |

| n                                                      |      | INCFSZ                                            |       |

| В                                                      |      | INDF Register                                     | 20    |

| Block Diagram                                          |      | Value on Reset                                    |       |

| On-Chip Reset Circuit                                  |      | Indirect Data Addressing                          |       |

| PIC16F5X Series                                        | 8    | Instruction Cycle                                 | 12    |

| Timer0                                                 | 33   | Instruction Flow/Pipelining                       |       |

| TMR0/WDT Prescaler                                     | 36   | Instruction Set Summary                           |       |

| Watchdog Timer                                         | 38   | Internet Address                                  | 83    |