Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | PIC                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | -                                                                      |

| Peripherals                | POR, WDT                                                               |

| Number of I/O              | 20                                                                     |

| Program Memory Size        | 3KB (2K x 12)                                                          |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 72 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                              |

| Data Converters            | -                                                                      |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

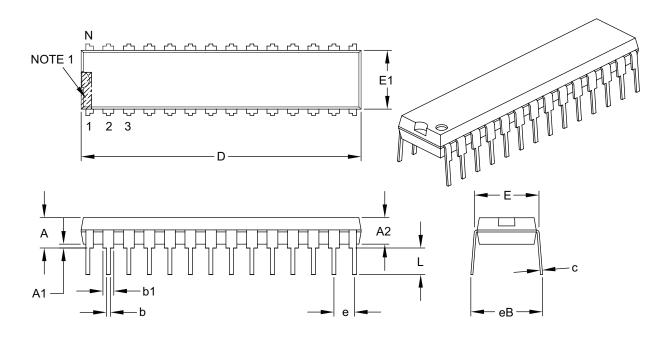

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                               |

| Supplier Device Package    | 28-PDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f57-e-p |

|                            |                                                                        |

NOTES:

TABLE 2-3: PIC16F59 PINOUT DESCRIPTION

| Name        | Function | Input<br>Type | Output<br>Type | Description                                                                                                                   |  |  |  |

|-------------|----------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RA0         | RA0      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RA1         | RA1      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RA2         | RA2      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RA3         | RA3      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RB0         | RB0      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RB1         | RB1      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RB2         | RB2      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RB3         | RB3      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RB4         | RB4      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RB5         | RB5      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RB6/ICSPCLK | RB6      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

|             | ICSPCLK  | ST            | _              | Serial programming clock                                                                                                      |  |  |  |

| RB7/ICSPDAT | RB7      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

|             | ICSPDAT  | ST            | CMOS           | Serial programming I/O                                                                                                        |  |  |  |

| RC0         | RC0      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RC1         | RC1      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RC2         | RC2      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RC3         | RC3      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RC4         | RC4      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RC5         | RC5      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RC6         | RC6      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RC7         | RC7      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RD0         | RD0      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RD1         | RD1      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RD2         | RD2      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RD3         | RD3      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RD4         | RD4      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RD5         | RD5      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RD6         | RD6      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RD7         | RD7      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RE4         | RE4      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RE5         | RE5      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RE6         | RE6      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| RE7         | RE7      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |  |  |  |

| TOCKI       | T0CKI    | ST            | _              | Clock input to Timer0. Must be tied to Vss or VDD, if not in use, to reduce current consumption.                              |  |  |  |

| MCLR/VPP    | MCLR     | ST            | _              | Active-low Reset to device. Voltage on the MCLR/VPP pin must not exceed VDD to avoid unintended entering of Programming mode. |  |  |  |

|             | VPP      | HV            | _              | Programming voltage input                                                                                                     |  |  |  |

| OSC1/CLKIN  | OSC1     | XTAL          | _              | Oscillator crystal input                                                                                                      |  |  |  |

|             | CLKIN    | ST            | _              | External clock source input                                                                                                   |  |  |  |

| OSC2/CLKOUT | OSC2     | _             | XTAL           | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode.                                       |  |  |  |

|             | CLKOUT   | _             | CMOS           | In RC mode, OSC2 pin outputs CLKOUT, which has 1/4 the frequency of OSC1.                                                     |  |  |  |

| VDD         | VDD      | Power         | _              | Positive supply for logic and I/O pins                                                                                        |  |  |  |

| Vss         | Vss      | Power         | _              | Ground reference for logic and I/O pins                                                                                       |  |  |  |

#### 3.0 MEMORY ORGANIZATION

PIC16F5X memory is organized into program memory and data memory. For the PIC16F57 and PIC16F59, which have more than 512 words of program memory, a paging scheme is used. Program memory pages are accessed using one or two STATUS register bits. For the PIC16F57 and PIC16F59, which have a data memory register file of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Selection Register (FSR).

#### 3.1 Program Memory Organization

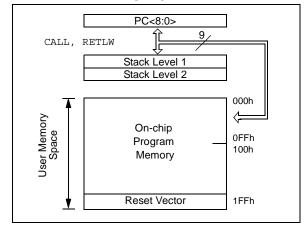

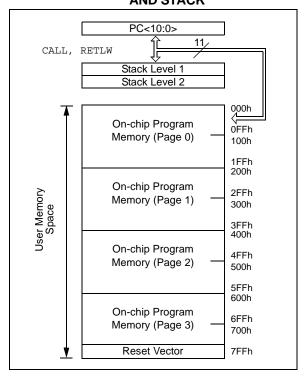

The PIC16F54 has a 9-bit Program Counter (PC) capable of addressing a 512 x 12 program memory space (Figure 3-1). The PIC16F57 and PIC16F59 have an 11-bit Program Counter capable of addressing a 2K x 12 program memory space (Figure 3-2). Accessing a location above the physically implemented address will cause a wraparound.

A NOP at the Reset vector location will cause a restart at location 000h. The Reset vector for the PIC16F54 is at 1FFh. The Reset vector for the PIC16F57 and PIC16F59 is at 7FFh. See **Section 3.5 "Program Counter"** for additional information using CALL and GOTO instructions.

FIGURE 3-1: PIC16F54 PROGRAM MEMORY MAP AND STACK

FIGURE 3-2: PIC16F57/PIC16F59

PROGRAM MEMORY MAP

AND STACK

#### 3.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFR) are registers used by the CPU and peripheral functions to control the operation of the device (Table 3-1).

The Special Function Registers can be classified into two sets. The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

TABLE 3-1: SPECIAL FUNCTION REGISTER SUMMARY

| Address | Name                      | Bit 7               | Bit 6          | Bit 5     | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0  | Value on<br>Power-on<br>Reset | Details<br>on Page |

|---------|---------------------------|---------------------|----------------|-----------|-----------|----------|----------|----------|--------|-------------------------------|--------------------|

| N/A     | TRIS                      | I/O Con             | trol Regi      | sters (T  | RISA, T   | RISB, TI | RISC, TE | RISD, TE | RISE)  | 1111 1111                     | 29                 |

| N/A     | OPTION                    | Contain<br>prescale | s contro<br>er | bits to o | configure | e Timer0 | and Tim  | ner0/WD  | T      | 11 1111                       | 18                 |

| 00h     | INDF                      | Uses co<br>register | ontents o      | f FSR to  | addres    | s data m | nemory ( | not a ph | ysical | xxxx xxxx                     | 20                 |

| 01h     | TMR0                      | Timer0              | Module I       | Register  |           |          |          |          |        | xxxx xxxx                     | 34                 |

| 02h     | PCL <sup>(1)</sup>        | Low ord             | ler 8 bits     | of PC     |           |          |          |          |        | 1111 1111                     | 19                 |

| 03h     | STATUS                    | PA2                 | PA1            | PA0       | OT        | PD       | Z        | DC       | С      | 0001 1xxx                     | 17                 |

| 04h     | FSR <sup>(3)</sup>        | Indirect            | data me        | mory Ac   | ldress F  | ointer   |          |          | •      | 111x xxxx                     | 20                 |

| 04h     | FSR <sup>(4)</sup>        | Indirect            | data me        | mory Ac   | ldress F  | ointer   |          |          |        | 1xxx xxxx                     | 20                 |

| 04h     | FSR <sup>(5)</sup>        | Indirect            | data me        | mory Ac   | ldress P  | ointer   |          |          |        | xxxx xxxx                     | 20                 |

| 05h     | PORTA <sup>(6)</sup>      | _                   | _              | _         | _         | RA3      | RA2      | RA1      | RA0    | xxxx                          | 29                 |

| 06h     | PORTB                     | RB7                 | RB6            | RB5       | RB4       | RB3      | RB2      | RB1      | RB0    | xxxx xxxx                     | 29                 |

| 07h     | PORTC <sup>(2)</sup>      | RC7                 | RC6            | RC5       | RC4       | RC3      | RC2      | RC1      | RC0    | xxxx xxxx                     | 29                 |

| 08h     | PORTD <sup>(7)</sup>      | RD7                 | RD6            | RD5       | RD4       | RD3      | RD2      | RD1      | RD0    | xxxx xxxx                     | 29                 |

| 09h     | PORTE <sup>(6), (7)</sup> | RE7                 | RE6            | RE5       | RE4       |          | _        |          | _      | xxxx                          | 29                 |

**Legend:** Shaded cells = unimplemented or unused, - = unimplemented, read as '0' (if applicable), x = unknown, u = unchanged

- Note 1: The upper byte of the Program Counter is not directly accessible. See Section 3.5 "Program Counter" for an explanation of how to access these bits.

- 2: File address 07h is a General Purpose Register on the PIC16F54.

- 3: PIC16F54 only.

- 4: PIC16F57 only.

- 5: PIC16F59 only.

- 6: Unimplemented bits are read as '0's.

- 7: File address 08h and 09h are General Purpose Registers on the PIC16F54 and PIC16F57.

#### 3.6 Stack

The PIC16F54 device has a 9-bit wide, two-level hardware PUSH/POP stack. The PIC16F57 and PIC16F59 devices have an 11-bit wide, two-level hardware PUSH/POP stack.

A CALL instruction will PUSH the current value of stack 1 into stack 2 and then PUSH the current program counter value, incremented by one, into stack level 1. If more than two sequential CALL's are executed, only the most recent two return addresses are stored.

A RETLW instruction will POP the contents of stack level 1 into the program counter and then copy stack level 2 contents into level 1. If more than two sequential RETLW's are executed, the stack will be filled with the address previously stored in level 2.

Note: The W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

For the RETLW instruction, the PC is loaded with the Top-of-Stack (TOS) contents. All of the devices covered in this data sheet have a two-level stack. The stack has the same bit width as the device PC, therefore, paging is not an issue when returning from a subroutine.

#### 3.7 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR Register (FSR is a pointer). This is indirect addressing.

#### **EXAMPLE 3-1:** INDIRECT ADDRESSING

- · Register file 08 contains the value 10h

- Register file 09 contains the value 0Ah

- Load the value 08 into the FSR register

- · A read of the INDF register will return the value

- · Increment the value of the FSR register by one (FSR = 09h)

- · A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 3-2.

#### **HOW TO CLEAR RAM EXAMPLE 3-2:** USING INDIRECT **ADDRESSING**

```

MOVLW H'10'

;initialize pointer

MOVWF FSR

; to RAM

;clear INDF Register

NEXT

INDF

CLRF

INCF

FSR, F ; inc pointer

BTFSC FSR,4 ;all done?

;NO, clear next

GOTO

NEXT

CONTINUE

; YES, continue

```

The FSR is either a 5-bit (PIC16F54), 7-bit (PIC16F57) or 8-bit (PIC16F59) wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

PIC16F54: This does not use banking. FSR<7:5> bits are unimplemented and read as '1's.

**PIC16F57:** FSR<7> bit is unimplemented and read as '1'. FSR<6:5> are the bank select bits and are used to select the bank to be addressed (00 = Bank 0, 01 = Bank 1, 10 = Bank 2, 11 = Bank 3).

PIC16F59: FSR<7:5> are the bank select bits and are used to select the bank to be addressed

(000 = Bank 0, 001 = Bank 1, 010 = Bank 2,

011 = Bank 3, 100 = Bank 4, 101 = Bank 5,

110 = Bank 6, 111 = Bank 7).

Note: A CLRF FSR instruction may not result in an FSR value of 00h if there are unimplemented bits present in the FSR.

TABLE 5-3: RESET CONDITIONS FOR ALL REGISTERS

| Register             | Address | Power-on Reset | MCLR or WDT Reset |

|----------------------|---------|----------------|-------------------|

| W                    | N/A     | xxxx xxxx      | uuuu uuuu         |

| TRIS                 | N/A     | 1111 1111      | 1111 1111         |

| OPTION               | N/A     | 11 1111        | 11 1111           |

| INDF                 | 00h     | xxxx xxxx      | uuuu uuuu         |

| TMR0                 | 01h     | xxxx xxxx      | uuuu uuuu         |

| PCL                  | 02h     | 1111 1111      | 1111 1111         |

| STATUS               | 03h     | 0001 1xxx      | 000q quuu         |

| FSR <sup>(1)</sup>   | 04h     | 111x xxxx      | 111u uuuu         |

| FSR <sup>(2)</sup>   | 04h     | 1xxx xxxx      | 1uuu uuuu         |

| FSR <sup>(3)</sup>   | 04h     | xxxx xxxx      | uuuu uuuu         |

| PORTA                | 05h     | xxxx           | uuuu              |

| PORTB                | 06h     | xxxx xxxx      | uuuu uuuu         |

| PORTC <sup>(4)</sup> | 07h     | xxxx xxxx      | uuuu uuuu         |

| PORTD <sup>(5)</sup> | 08h     | xxxx xxxx      | uuuu uuuu         |

| PORTE <sup>(5)</sup> | 09h     | xxxx           | uuuu              |

**Legend:** u = unchanged, x = unknown, - = unimplemented, read as '0', q = see tables in Table 5-1 for possible values.

Note 1: PIC16F54 only.

**2:** PIC16F57 only.

3: PIC16F59 only.

**4:** General purpose register file on PIC16F54.

5: General purpose register file on PIC16F54 and PIC16F57.

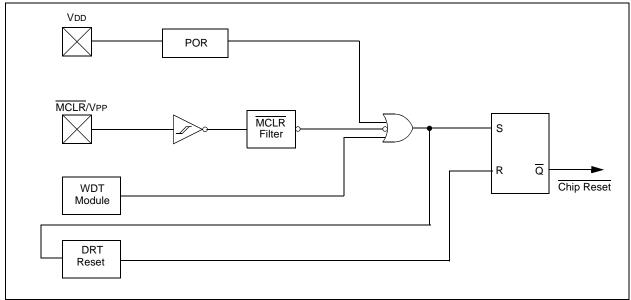

FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

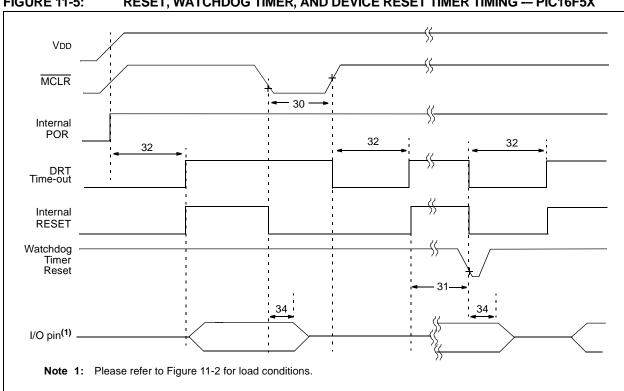

#### 5.2 Device Reset Timer (DRT)

The Device Reset Timer (DRT) provides an 18 ms nominal time-out on Reset regardless of the oscillator mode used. The DRT operates on an internal RC oscillator. The processor is kept in Reset as long as the DRT is active. The DRT delay allows VDD to rise above VDD min. and for the chosen oscillator to stabilize.

Oscillator circuits, based on crystals or ceramic resonators, require a certain time after power-up to establish a stable oscillation. The on-chip DRT keeps the device in a Reset condition for approximately 18 ms after the voltage on the  $\overline{MCLR}/VPP$  pin has reached a logic high (VIH) level. Thus, external RC networks connected to the  $\overline{MCLR}$  input are not required in most cases, allowing for savings in cost-sensitive and/or space restricted applications.

The device Reset time delay will vary from chip-to-chip due to VDD, temperature and process variation. See AC parameters for details.

The DRT will also be triggered upon a Watchdog Timer time-out. This is particularly important for applications using the WDT to wake the PIC16F5X from Sleep mode automatically.

#### 5.3 Reset on Brown-Out

A Brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a Brown-out.

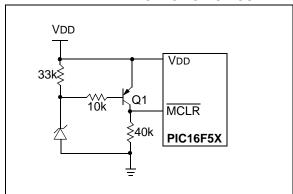

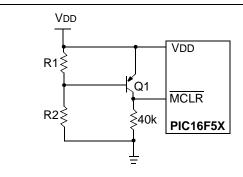

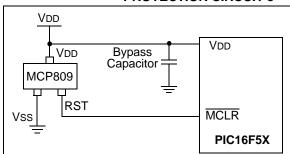

To reset PIC16F5X devices when a Brown-out occurs, external Brown-out protection circuits may be built, as shown in Figure 5-6, Figure 5-7 and Figure 5-8.

FIGURE 5-6: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

This circuit will activate Reset when VDD goes below Vz + 0.7V (where  $Vz = Zener \ voltage$ ).

# FIGURE 5-7: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, although less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$VDD \bullet \frac{R1}{R1 + R2} = 0.7V$$

## FIGURE 5-8: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both "active-high and active-low" Reset pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

# 7.0 TIMERO MODULE AND TMRO REGISTER

The Timer0 module has the following features:

- 8-bit Timer/Counter register, TMR0

- Readable and writable

- · 8-bit software programmable prescaler

- · Internal or external clock select

- Edge select for external clock

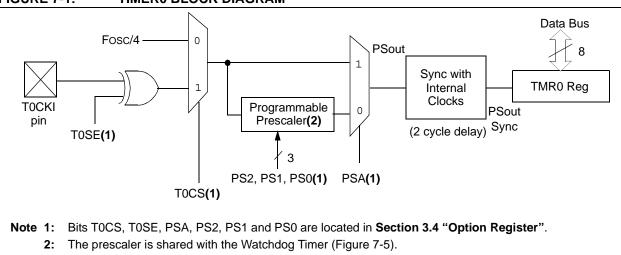

Figure 7-1 is a simplified block diagram of the Timer0 module.

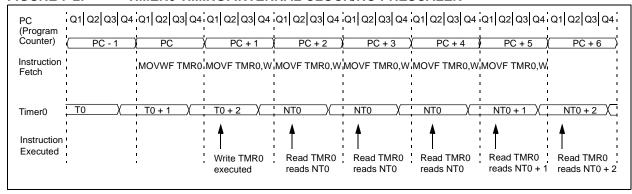

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the TOCS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin TOCKI. The incrementing edge is determined by the source edge select bit TOSE (OPTION<4>). Clearing the TOSE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in **Section 7.1** "Using Timer0 with an External Clock".

**Note:** The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both.

The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. **Section 7.2 "Prescaler"** details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 7-1.

#### FIGURE 7-1: TIMERO BLOCK DIAGRAM

#### FIGURE 7-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALER

#### 8.3 Power-Down Mode (Sleep)

A device may be powered down (Sleep) and later powered up (wake-up from Sleep).

#### 8.3.1 SLEEP

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared <u>but</u> keeps running, the  $\overline{\text{TO}}$  bit (STATUS<4>) is set, the  $\overline{\text{PD}}$  bit (STATUS<3>) is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low or high-impedance).

It should be noted that a Reset generated by a WDT time-out does not drive the MCLR/VPP pin low.

For lowest current consumption while powered down, the T0CKI input should be at VDD or Vss and the  $\overline{\text{MCLR}}/\text{VPP}$  pin must be at a logic high level  $\overline{\text{(MCLR}} = \text{VIH)}$ .

#### 8.3.2 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. An external Reset input on MCLR/VPP pin.

- A Watchdog Timer time-out Reset (if WDT was enabled).

Both of these events cause a device Reset. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits can be used to determine the cause of device Reset. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up). The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked.

The WDT is cleared when the device wakes from Sleep, regardless of the wake-up source.

# 8.4 Program Verification/Code Protection

If the code protection bit has not been programmed, the on-chip program memory can be read out for verification purposes.

Once code protection is enabled, all program memory locations above 0x3F read all 'o's. Program memory locations 0x00-0x3F are always unprotected. The user ID locations and the Configuration Word read out in an unprotected fashion. It is possible to program the user ID locations and the Configuration Word after code protect is enabled.

#### 8.5 User ID Locations

Four memory locations are designated as user ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify.

Use only the lower 4 bits of the user ID locations and always program the upper 8 bits as '1's.

Note: Microchip will assign a unique pattern number for QTP and SQTP requests. This pattern number will be unique and traceable to the submitted code.

# 8.6 In-Circuit Serial Programming™ (ICSP™)

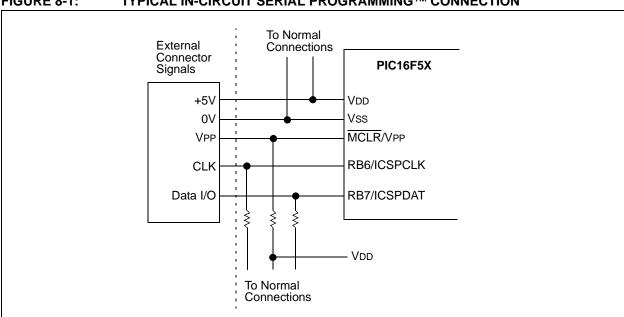

The PIC16F5X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. Thus, the most recent firmware or custom firmware can be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a Load or a Read. For complete details of serial programming, please refer to the respective Programming Specifications: "PIC16F54 Memory Programming Specification" (DS41207), "PIC16F57 Memory Programming Specification" (DS41208), and "PIC16F59 Memory Programming Specification" (DS41243).

A typical In-Circuit Serial Programming connection is shown in Figure 8-1.

TYPICAL IN-CIRCUIT SERIAL PROGRAMMING™ CONNECTION FIGURE 8-1:

#### 9.0 INSTRUCTION SET SUMMARY

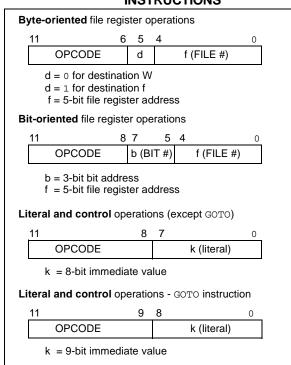

Each PIC16F5X instruction is a 12-bit word divided into an opcode, which specifies the instruction type, and one or more operands which further specify the operation of the instruction. The PIC16F5X instruction set summary in Table 9-2 groups the instructions into byteoriented, bit-oriented, and literal and control operations. Table 9-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator is used to specify which one of the 32 file registers in that bank is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8- or 9-bit constant or literal value.

TABLE 9-1: OPCODE FIELD DESCRIPTIONS

| Field                                     | Description                               |  |  |  |  |  |  |

|-------------------------------------------|-------------------------------------------|--|--|--|--|--|--|

| f                                         | Register file address (0x00 to 0x1F)      |  |  |  |  |  |  |

| W                                         | Working register (accumulator)            |  |  |  |  |  |  |

| b                                         | Bit address within an 8-bit file register |  |  |  |  |  |  |

| k                                         | Literal field, constant data or label     |  |  |  |  |  |  |

| х                                         | Don't care location (= 0 or 1)            |  |  |  |  |  |  |

|                                           | The assembler will generate code with     |  |  |  |  |  |  |

|                                           | x = 0. It is the recommended form of use  |  |  |  |  |  |  |

|                                           | for compatibility with all Microchip      |  |  |  |  |  |  |

|                                           | software tools.                           |  |  |  |  |  |  |

| d                                         | Destination select;                       |  |  |  |  |  |  |

|                                           | d = 0 (store result in W)                 |  |  |  |  |  |  |

| d = 1 (store result in file register 'f') |                                           |  |  |  |  |  |  |

|                                           | Default is d = 1                          |  |  |  |  |  |  |

| label                                     | Label name                                |  |  |  |  |  |  |

| TOS                                       | Top-of-Stack                              |  |  |  |  |  |  |

| PC                                        | Program Counter                           |  |  |  |  |  |  |

| WDT                                       | Watchdog Timer Counter                    |  |  |  |  |  |  |

| TO                                        | Time-out bit                              |  |  |  |  |  |  |

| PD                                        | Power-down bit                            |  |  |  |  |  |  |

| dest                                      | Destination, either the W register or the |  |  |  |  |  |  |

|                                           | specified register file location          |  |  |  |  |  |  |

| [ ]                                       | Options                                   |  |  |  |  |  |  |

| ( )                                       | Contents                                  |  |  |  |  |  |  |

| $\rightarrow$                             | Assigned to                               |  |  |  |  |  |  |

| < >                                       | Register bit field                        |  |  |  |  |  |  |

| €                                         | In the set of                             |  |  |  |  |  |  |

| italics                                   | User defined term                         |  |  |  |  |  |  |

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time would be 1  $\mu s.$  If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time would be 2  $\mu s.$

Figure 9-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

## FIGURE 9-1: GENERAL FORMAT FOR INSTRUCTIONS

| RLF                   | Rotate Left f through Carry                                                                                                                                                                                       |     |       |      |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|--|--|--|--|

| Syntax:               | [label] RLF f, d                                                                                                                                                                                                  |     |       |      |  |  |  |  |

| Operands:             | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                                                 |     |       |      |  |  |  |  |

| Operation:            | See description below                                                                                                                                                                                             |     |       |      |  |  |  |  |

| Status Affected:      | С                                                                                                                                                                                                                 |     |       |      |  |  |  |  |

| Encoding:             | 0013                                                                                                                                                                                                              | 1 ( | 1df   | ffff |  |  |  |  |

| Description:          | The contents of register 'f' are rotated one bit to the left through the Carry Flag (STATUS<0>). If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is stored back in register 'f'. |     |       |      |  |  |  |  |

| Words:                | 1                                                                                                                                                                                                                 |     |       |      |  |  |  |  |

| Cycles:               | 1                                                                                                                                                                                                                 |     |       |      |  |  |  |  |

| Example:              | RLF                                                                                                                                                                                                               | RI  | EG1,0 |      |  |  |  |  |

| Before Instru         | truction                                                                                                                                                                                                          |     |       |      |  |  |  |  |

| REG1                  | =                                                                                                                                                                                                                 | 111 | 0 011 | .0   |  |  |  |  |

| C                     | =                                                                                                                                                                                                                 | 0   |       |      |  |  |  |  |

| After Instruc<br>REG1 | uon<br>=                                                                                                                                                                                                          | 111 | 0 011 | 0    |  |  |  |  |

| W                     | =                                                                                                                                                                                                                 |     | 0 110 | -    |  |  |  |  |

|                       |                                                                                                                                                                                                                   |     |       | -    |  |  |  |  |

1

| RRF                                                            | Rotate Right f through Carry                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:                                                        | [ label ] RRF f, d                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Operands:                                                      | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Operation:                                                     | See description below                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| Status Affected:                                               | C                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Encoding:                                                      | 0011 00df ffff                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Description:                                                   | The contents of register 'f' are rotated one bit to the right through the Carry Flag (STATUS<0>). If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |  |  |  |  |  |  |

| Words:                                                         | 1                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Cycles:                                                        | 1                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Example:                                                       | RRF REG1,0                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Before Instru<br>REG1<br>C<br>After Instruct<br>REG1<br>W<br>C | = 1110 0110<br>= 0                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Sleep            | Go into Standby Mode                                                                                                                                                                                                                                           |       |      |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|--|--|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                                                                      | Sleep |      |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                                           |       |      |  |  |  |  |  |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT}; \\ \text{0} \rightarrow \underline{\text{WDT}} \text{ prescaler}; \text{ if assigned} \\ \text{1} \rightarrow \overline{\underline{\text{TO}}}; \\ \text{0} \rightarrow \overline{\text{PD}} \end{array}$ |       |      |  |  |  |  |  |

| Status Affected: | $\overline{TO}, \overline{PD}$                                                                                                                                                                                                                                 |       |      |  |  |  |  |  |

| Encoding:        | 0000                                                                                                                                                                                                                                                           | 0000  | 0011 |  |  |  |  |  |

| Description:     | Time-out Status bit (TO) is set. The power-down Status bit (PD) is cleared. The WDT and its prescaler are cleared. The processor is put into Sleep mode with the oscillator stopped. See section on Sleep for more details.                                    |       |      |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                              |       |      |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                              |       |      |  |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                          |       |      |  |  |  |  |  |

С

| SUBWF                    | Subtract W from f                                                                                         | SWAPF                                  | Swap Nibbles in f                                                                                           |

|--------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Syntax:                  | [ label ] SUBWF f, d                                                                                      | Syntax:                                | [ label] SWAPF f, d                                                                                         |

| Operands:                | $0 \le f \le 31$<br>$d \in [0,1]$                                                                         | Operands:                              | $0 \le f \le 31$<br>$d \in [0,1]$                                                                           |

| Operation:               | $ (f) - (W) \rightarrow (dest) $                                                                          | Operation:                             | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                   |

| Status Affected:         | C, DC, Z                                                                                                  | Status Affected:                       | None                                                                                                        |

| Encoding:                | 0000 10df ffff                                                                                            | Encoding:                              | 0011 10df ffff                                                                                              |

| Description:             | Subtract (2's complement method)<br>the W register from register 'f'. If 'd'                              | Description:                           | The upper and lower nibbles of                                                                              |

|                          | is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. | Boompton                               | register 'f' are exchanged. If 'd' is '0', the result is placed in W register. If 'd' is '1', the result is |

| Words:                   | 1                                                                                                         |                                        | placed in register 'f'.                                                                                     |

| Cycles:                  | 1                                                                                                         | Words:                                 | 1                                                                                                           |

| Example 1:               | SUBWF REG1, 1                                                                                             | Cycles:                                | 1                                                                                                           |

| Before Instru            | uction                                                                                                    | Example:                               | SWAPF REG1, 0                                                                                               |

| REG1<br>W<br>C           | = 3<br>= 2<br>= ?                                                                                         | Before Instru<br>REG1<br>After Instruc | = 0xA5                                                                                                      |

| After Instruct           |                                                                                                           | REG1<br>W                              | = 0xA5                                                                                                      |

| REG1<br>W                | = 1<br>= 2                                                                                                | VV                                     | = 0x5A                                                                                                      |

| C                        | = 1 ; result is positive                                                                                  |                                        |                                                                                                             |

| Example 2:               |                                                                                                           | TRIS                                   | Load TRIS Register                                                                                          |

| Before Instru            |                                                                                                           | Syntax:                                | [label] TRIS f                                                                                              |

| REG1<br>W                | = 2<br>= 2                                                                                                | Operands:                              | f = 5, 6, 7, 8 or 9                                                                                         |

| Č                        | = ?                                                                                                       | •                                      |                                                                                                             |

| After Instruc            | tion                                                                                                      | Operation:                             | (W) → TRIS register f                                                                                       |

| REG1                     | = 0                                                                                                       | Status Affected:                       | None                                                                                                        |

| W                        | = 2                                                                                                       | Encoding:                              | 0000 0000 Offf                                                                                              |

| C                        | = 1 ; result is zero                                                                                      | Description:                           | TRIS register 'f' ( $f = 5, 6 \text{ or } 7$ ) is                                                           |

| Example 3:<br>Before Ins | truction                                                                                                  |                                        | loaded with the contents of the W                                                                           |

| REG1                     | = 1                                                                                                       |                                        | register.                                                                                                   |

| W                        | = 2                                                                                                       | Words:                                 | 1                                                                                                           |

| С                        | = ?                                                                                                       | Cycles:                                | 1                                                                                                           |

| After Instruc            |                                                                                                           | Example:                               | TRIS PORTB                                                                                                  |

| REG1                     | = 0xFF                                                                                                    | Before Instru                          | uction                                                                                                      |

| W                        | = 2                                                                                                       | W                                      | = 0xA5                                                                                                      |

| С                        | = 0 ; result is negative                                                                                  | After Instruc<br>TRISB                 | tion<br>= 0xA5                                                                                              |

#### 10.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

#### 10.12 PICkit 2 Development Programmer

The PICkit™ 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC™ Lite C compiler, and is designed to help get up to speed quickly using PIC® microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

# 10.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>TM</sup> and dsPICDEM<sup>TM</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, Keeloq® security ICs, CAN, IrDA®, PowerSmart® battery management, Seevaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest "Product Selector Guide" (DS00148) for the complete list of demonstration, development and evaluation kits.

#### 11.3 DC Characteristics PIC16F5X

| DC CH        | ARAC <sup>-</sup> | TERISTICS                          | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |      |          |       |                                      |  |  |

|--------------|-------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|--------------------------------------|--|--|

| Param<br>No. | Sym.              | Characteristic                     | Min.                                                                                                                                                                                                                                   | Тур† | Max.     | Units | Conditions                           |  |  |

|              | VIL               | Input Low Voltage                  |                                                                                                                                                                                                                                        |      |          |       |                                      |  |  |

| D030         |                   | I/O Ports                          | Vss                                                                                                                                                                                                                                    | _    | 0.8V     | V     | 4.5V <vdd 5.5v<="" td="" ≤=""></vdd> |  |  |

|              |                   | I/O Ports                          | Vss                                                                                                                                                                                                                                    | _    | 0.15 VDD | V     | VDD ≤ 4.5V                           |  |  |

|              |                   | MCLR (Schmitt Trigger)             | Vss                                                                                                                                                                                                                                    | _    | 0.15 VDD | V     |                                      |  |  |

|              |                   | T0CKI (Schmitt Trigger)            | Vss                                                                                                                                                                                                                                    | _    | 0.15 VDD | V     |                                      |  |  |

|              |                   | OSC1 (Schmitt Trigger)             | Vss                                                                                                                                                                                                                                    | _    | 0.15 VDD | V     | RC mode <sup>(3)</sup>               |  |  |

|              |                   | OSC1                               | Vss                                                                                                                                                                                                                                    | _    | 0.3 Vdd  | V     | HS mode                              |  |  |

|              |                   |                                    | Vss                                                                                                                                                                                                                                    | _    | 0.3      | V     | XT mode                              |  |  |

|              |                   |                                    | Vss                                                                                                                                                                                                                                    | _    | 0.3      | V     | LP mode                              |  |  |

|              | VIH               | Input High Voltage                 |                                                                                                                                                                                                                                        |      |          |       |                                      |  |  |

| D040         |                   | I/O ports                          | 2.0                                                                                                                                                                                                                                    | _    | Vdd      | V     | 4.5V < VDD ≤ 5.5V                    |  |  |

|              |                   | I/O ports                          | 0.25  Vdd + 0.8                                                                                                                                                                                                                        | _    | VDD      | V     | VDD ≤ 4.5V                           |  |  |

|              |                   | MCLR (Schmitt Trigger)             | 0.85 VDD                                                                                                                                                                                                                               | _    | VDD      | V     |                                      |  |  |

|              |                   | T0CKI (Schmitt Trigger)            | 0.85 VDD                                                                                                                                                                                                                               | _    | Vdd      | V     |                                      |  |  |

|              |                   | OSC1 (Schmitt Trigger)             | 0.85 VDD                                                                                                                                                                                                                               | _    | Vdd      | V     | RC mode <sup>(3)</sup>               |  |  |

|              |                   | OSC1                               | 0.7 VDD                                                                                                                                                                                                                                | _    | Vdd      | V     | HS mode                              |  |  |

|              |                   |                                    | 1.6                                                                                                                                                                                                                                    | _    | Vdd      | V     | XT mode                              |  |  |

|              |                   |                                    | 1.6                                                                                                                                                                                                                                    | _    | Vdd      | V     | LP mode                              |  |  |

|              | lıL               | Input Leakage Current <sup>(</sup> | 1, 2)                                                                                                                                                                                                                                  |      |          |       |                                      |  |  |

| D060         |                   | I/O ports                          | _                                                                                                                                                                                                                                      | _    | ±1.0     | μΑ    | $VSS \leq VPIN \leq VDD,$            |  |  |

|              |                   |                                    |                                                                                                                                                                                                                                        |      |          |       | pin at high-impedance                |  |  |

|              |                   | MCLR                               | _                                                                                                                                                                                                                                      | _    | ±5.0     | μA    | VSS ≤ VPIN ≤ VDD                     |  |  |

|              |                   | T0CKI                              | _                                                                                                                                                                                                                                      | _    | ±5.0     | μA    | Vss ≤ Vpin ≤ Vdd                     |  |  |

|              |                   | OSC1                               | _                                                                                                                                                                                                                                      | _    | ±5.0     | μΑ    | VSS ≤ VPIN ≤ VDD,                    |  |  |

|              |                   |                                    |                                                                                                                                                                                                                                        |      |          |       | XT, HS and LP modes                  |  |  |

|              | Vol               | Output Low Voltage                 |                                                                                                                                                                                                                                        |      |          | 1     | ,                                    |  |  |

| D080         |                   | I/O ports                          | _                                                                                                                                                                                                                                      | _    | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V             |  |  |

| D083         |                   | OSC2/CLKOUT                        | _                                                                                                                                                                                                                                      | _    | 0.6      | V     | IOL = 1.6 mA, VDD = 4.5V             |  |  |

|              |                   | (RC mode)                          |                                                                                                                                                                                                                                        |      |          |       |                                      |  |  |

|              | Vон               | Output High Voltage <sup>(2)</sup> |                                                                                                                                                                                                                                        |      |          |       |                                      |  |  |

| D090         |                   | I/O ports <sup>(2)</sup>           | VDD - 0.7                                                                                                                                                                                                                              | _    |          | V     | IOH = -3.0 mA, VDD = 4.5V            |  |  |

| D092         |                   | OSC2/CLKOUT                        | VDD - 0.7                                                                                                                                                                                                                              | _    | _        | V     | IOH = -1.3 mA, VDD = 4.5V            |  |  |

|              |                   | (RC mode)                          |                                                                                                                                                                                                                                        |      |          |       |                                      |  |  |

|              | * The             | and parameters are abore           |                                                                                                                                                                                                                                        |      | 1        |       | 1                                    |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

- 2: Negative current is defined as coming out of the pin.

- **3:** For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F5X be driven with external clock in RC mode.

<sup>†</sup> Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

TABLE 11-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARAG     | CTERISTICS | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |      |        |        |       |               |  |

|---------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|--------|-------|---------------|--|

| Parameter No. | Sym.       | Characteristic                                                                                                                                                                                                                         | Min. | Typ†   | Max.   | Units | Conditions    |  |

|               | Fosc       | External CLKIN Frequency <sup>(1)</sup>                                                                                                                                                                                                | DC   |        | 4.0    | MHz   | XT Osc mode   |  |

|               |            |                                                                                                                                                                                                                                        | DC   | _      | 20     | MHz   | HS Osc mode   |  |

|               |            |                                                                                                                                                                                                                                        | DC   | _      | 200    | kHz   | LP Osc mode   |  |

|               |            | Oscillator Frequency <sup>(1)</sup>                                                                                                                                                                                                    | DC   | _      | 4.0    | MHz   | RC Osc mode   |  |

|               |            |                                                                                                                                                                                                                                        | 0.1  | _      | 4.0    | MHz   | XT Osc mode   |  |

|               |            |                                                                                                                                                                                                                                        | 4.0  | _      | 20     | MHz   | HS Osc mode   |  |

|               |            |                                                                                                                                                                                                                                        | 5.0  | _      | 200    | kHz   | LP Osc mode   |  |

| 1             | Tosc       | External CLKIN Period <sup>(1)</sup>                                                                                                                                                                                                   | 250  | _      | _      | ns    | XT Osc mode   |  |

|               |            |                                                                                                                                                                                                                                        | 50   | _      | _      | ns    | HS Osc mode   |  |

|               |            |                                                                                                                                                                                                                                        | 5.0  | _      | _      | μs    | LP Osc mode   |  |