#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 20                                                                      |

| Program Memory Size        | 3KB (2K x 12)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 72 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

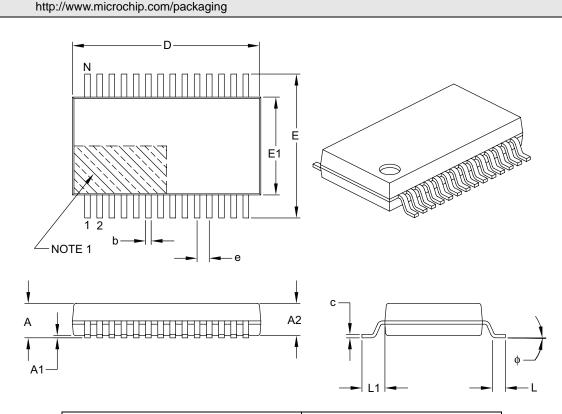

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 28-SSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f57-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**PIC16F5X**

# Flash-Based, 8-Bit CMOS Microcontroller Series

#### High-Performance RISC CPU:

- Only 33 single-word instructions to learn

- All instructions are single cycle except for program branches which are two-cycle

- Two-level deep hardware stack

- Direct, Indirect and Relative Addressing modes for data and instructions

- · Operating speed:

- DC 20 MHz clock speed

- DC 200 ns instruction cycle time

- On-chip Flash program memory:

- 512 x 12 on PIC16F54

- 2048 x 12 on PIC16F57

- 2048 x 12 on PIC16F59

- General Purpose Registers (SRAM):

- 25 x 8 on PIC16F54

- 72 x 8 on PIC16F57

- 134 x 8 on PIC16F59

#### **Special Microcontroller Features:**

- Power-on Reset (POR)

- Device Reset Timer (DRT)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Programmable Code Protection

- Power-Saving Sleep mode

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Selectable oscillator options:

- RC: Low-cost RC oscillator

- XT: Standard crystal/resonator

- HS: High-speed crystal/resonator

- LP: Power-saving, low-frequency crystal

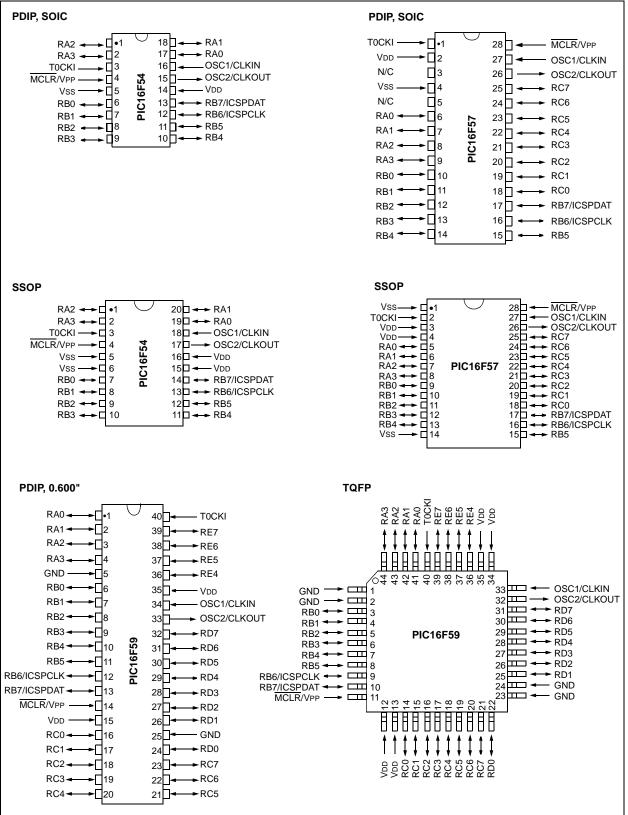

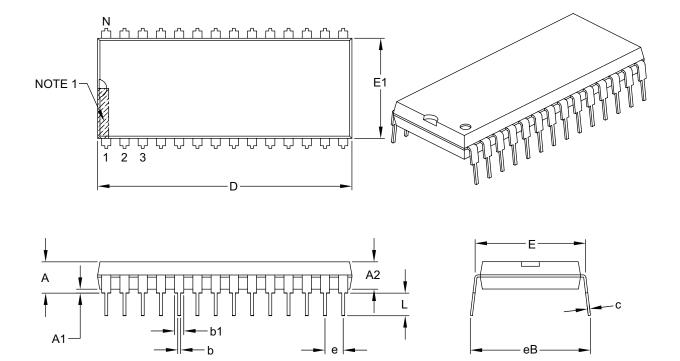

- Packages:

- 18-pin PDIP and SOIC for PIC16F54

- 20-pin SSOP for PIC16F54

- 28-pin PDIP, SOIC and SSOP for PIC16F57

- 40-pin PDIP for PIC16F59

- 44-pin TQFP for PIC16F59

#### Low-Power Features:

- Operating Current:

- 170 μA @ 2V, 4 MHz, typical

- 15 μA @ 2V, 32 kHz, typical

- Standby Current:

- 500 nA @ 2V, typical

#### **Peripheral Features:**

- 12/20/32 I/O pins:

- Individual direction control

- High current source/sink

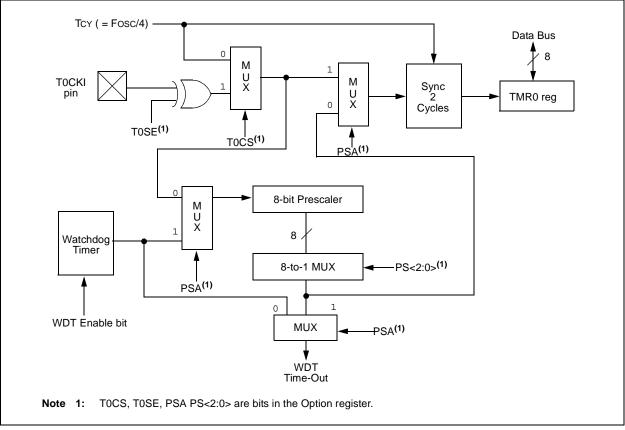

- 8-bit real-time clock/counter (TMR0) with 8-bit programmable prescaler

### **CMOS Technology:**

- Wide operating voltage range:

- Industrial: 2.0V to 5.5V

- Extended: 2.0V to 5.5V

- Wide temperature range:

- Industrial: -40°C to 85°C

- Extended: -40°C to 125°C

- High-endurance Flash:

- 100K write/erase cycles

- > 40-year retention

| Device   | Program Memory             | Data Memory | I/O | Timers |  |

|----------|----------------------------|-------------|-----|--------|--|

| Device   | Flash (words) SRAM (bytes) |             | 1/0 | 8-bit  |  |

| PIC16F54 | 512                        | 25          | 12  | 1      |  |

| PIC16F57 | 2048                       | 72          | 20  | 1      |  |

| PIC16F59 | 2048                       | 134         | 32  | 1      |  |

### Pin Diagrams

# 1.0 GENERAL DESCRIPTION

The PIC16F5X from Microchip Technology is a family of low-cost, high-performance, 8-bit, fully static, Flashbased CMOS microcontrollers. It employs a RISC architecture with only 33 single-word/single-cycle instructions. All instructions are single cycle except for program branches which take two cycles. The PIC16F5X delivers performance an order of magnitude higher than its competitors in the same price category. The 12-bit wide instructions are highly symmetrical resulting in 2:1 code compression over other 8-bit microcontrollers in its class. The easy-to-use and easyto-remember instruction set reduces development time significantly.

The PIC16F5X products are equipped with special features that reduce system cost and power requirements. The Power-on Reset (POR) and Device Reset Timer (DRT) eliminate the need for external Reset circuitry. There are four oscillator configurations to choose from, including the power-saving LP (Low Power) oscillator and cost saving RC oscillator. Power-saving Sleep mode, Watchdog Timer and code protection features improve system cost, power and reliability.

The PIC16F5X products are supported by a full-featured macro assembler, a software simulator, a low-cost development programmer and a full featured programmer. All the tools are supported on IBM<sup>®</sup> PC and compatible machines.

### 1.1 Applications

The PIC16F5X series fits perfectly in applications ranging from high-speed automotive and appliance motor control to low-power remote transmitters/receivers, pointing devices and telecom processors. The Flash technology makes customizing application programs codes. motor (transmitter speeds. receiver frequencies, etc.) extremely fast and convenient. The small footprint packages, for through hole or surface mounting, make this microcontroller series perfect for applications with space limitations. Low-cost, lowpower, high performance, ease of use and I/O flexibility make the PIC16F5X series very versatile, even in areas where no microcontroller use has been considered before (e.g., timer functions, replacement of "glue" logic in larger systems, co-processor applications).

| Features                         | PIC16F54                         | PIC16F57                         | PIC16F59                |  |  |  |

|----------------------------------|----------------------------------|----------------------------------|-------------------------|--|--|--|

| Maximum Operation Frequency      | 20 MHz                           | 20 MHz                           | 20 MHz                  |  |  |  |

| Flash Program Memory (x12 words) | 512                              | 2K                               | 2K                      |  |  |  |

| RAM Data Memory (bytes)          | 25                               | 72                               | 134                     |  |  |  |

| Timer Module(s)                  | TMR0                             | TMR0                             | TMR0                    |  |  |  |

| I/O Pins                         | 12                               | 20                               | 32                      |  |  |  |

| Number of Instructions           | 33                               | 33                               | 33                      |  |  |  |

| Packages                         | 18-pin DIP, SOIC;<br>20-pin SSOP | 28-pin DIP, SOIC;<br>28-pin SSOP | 40-pin DIP, 44-pin TQFP |  |  |  |

#### TABLE 1-1: PIC16F5X FAMILY OF DEVICES

**Note:** All PIC<sup>®</sup> Family devices have Power-on Reset, selectable Watchdog Timer, selectable code-protect and high I/O current capability.

NOTES:

| Name        | Function                      | Input<br>Type | Output<br>Type | Description                                                                                                                   |

|-------------|-------------------------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------|

| RA0         | RA0                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RA1         | RA1                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RA2         | RA2                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RA3         | RA3                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RB0         | RB0                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RB1         | RB1                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RB2         | RB2                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RB3         | RB3                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RB4         | RB4                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RB5         | RB5                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RB6/ICSPCLK | RB6                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

|             | ICSPCLK                       | ST            |                | Serial programming clock                                                                                                      |

| RB7/ICSPDAT | RB7                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

|             | ICSPDAT                       | ST            | CMOS           | Serial programming I/O                                                                                                        |

| RC0         | RC0                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RC1         | RC1                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RC2         | RC2                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RC3         | RC3                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RC4         | RC4                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RC5         | RC5                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RC6         | RC6                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| RC7         | RC7                           | TTL           | CMOS           | Bidirectional I/O pin                                                                                                         |

| TOCKI       | TOCKI                         | ST            | —              | Clock input to Timer0. Must be tied to Vss or VDD, if not in use, to reduce current consumption.                              |

| MCLR/Vpp    | MCLR                          | ST            | _              | Active-low Reset to device. Voltage on the MCLR/VPP pin must not exceed VDD to avoid unintended entering of Programming mode. |

|             | Vpp                           | ΗV            | _              | Programming voltage input                                                                                                     |

| OSC1/CLKIN  | OSC1                          | XTAL          | —              | Oscillator crystal input                                                                                                      |

|             | CLKIN                         | ST            | —              | External clock source input                                                                                                   |

| OSC2/CLKOUT | OSC2                          |               | XTAL           | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode.                                       |

|             | CLKOUT                        | —             | CMOS           | In RC mode, OSC2 pin outputs CLKOUT, which has 1/4 the frequency of OSC1.                                                     |

| Vdd         | Vdd                           | Power         | —              | Positive supply for logic and I/O pins                                                                                        |

| Vss         | Vss                           | Power         | _              | Ground reference for logic and I/O pins                                                                                       |

| N/C         | N/C                           | _             | _              | Unused, do not connect                                                                                                        |

|             | put<br>utput<br>chmitt Trigge | r input       | — =            | input/outputCMOS = CMOS outputNot UsedXTAL = Crystal input/outputTTL inputHV = High Voltage                                   |

# TABLE 2-2: PIC16F57 PINOUT DESCRIPTION

#### 3.3 **STATUS Register**

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bits for program memories larger than 512 words.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

Therefore, it is recommended that only BCF, BSF, MOVWF and SWAPF instructions be used to alter the STATUS register because these instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions which do affect Status bits, see Section 9.0 "Instruction Set Summary".

#### **REGISTER 3-1:** STATUS REGISTER (ADDRESS: 03h)

|         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                               | R/W-0                   | R-1            | R-1            | R/W-x                                      | R/W-x          | R/W-x       |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------|----------------|----------------|--------------------------------------------|----------------|-------------|

|         | PA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PA1                                                 | PA0                     | TO             | PD             | Z                                          | DC             | С           |

|         | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     |                         |                |                |                                            |                | bit 0       |

| bit 7   | Use of the P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ved, do not us<br>A2 bit as a ge<br>/ with future p | neral purpos            | e read/write I | oit is not rec | ommended, sin                              | ce this may af | fect upward |

| bit 6-5 | PA<1:0>: Program Page Preselect bits (PIC16F57/PIC16F59) 00 = Page 0 (000h-1FFh) 01 = Page 1 (200h-3FFh) 10 = Page 2 (400h-5FFh) 11 = Page 3 (600h-7FFh) Each page is 512 words. Using the PA<1:0> bits as general purpose read/write bits in devices which do not use them for program page preselect is not recommended. This may affect upward compatibility with future products.                                                                                                                                                             |                                                     |                         |                |                |                                            |                |             |

| bit 4   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ut bit<br>wer-up, CLRM<br>time-out occu             |                         | on or SLEEP    | instruction    |                                            |                |             |

| bit 3   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Down bit<br>wer-up or by<br>ution of the S          |                         |                |                |                                            |                |             |

| bit 2   | <ul> <li>Z: Zero bit</li> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                                                                                                                                                                                                                                                                                                                                                                       |                                                     |                         |                |                |                                            |                |             |

| bit 1   | DC: Digit Carry/Borrow bit (for ADDWF and SUBWF instructions)          ADDWF         1 = A carry to the 4th low order bit of the result occurred         0 = A carry from the 4th low order bit of the result did not occur         SUBWF         1 = A borrow to the 4th low order bit of the result did not occur         0 = A borrow to the 4th low order bit of the result did not occur         0 = A borrow to the 4th low order bit of the result did not occur         0 = A borrow to the 4th low order bit of the result did not occur |                                                     |                         |                |                |                                            |                |             |

| bit 0   | 1 = A carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | rrow bit (for A<br>occurred<br>did not occur        | <u>SUBWI</u><br>1 = A b |                | occur Lo       | ons)<br><u>RF or RLF</u><br>paded with LSb | or MSb, resp   | ectively    |

|         | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |                         |                |                |                                            |                |             |

|         | R = Readab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ole bit                                             | W = W                   | /ritable bit   | U = Un         | implemented bi                             | t, read as '0' |             |

|         | - n = Value a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | at POR                                              | '1' = B                 | it is set      | '0' = Bit      | t is cleared                               | x = Bit is un  | known       |

## 3.6 Stack

The PIC16F54 device has a 9-bit wide, two-level hardware PUSH/POP stack. The PIC16F57 and PIC16F59 devices have an 11-bit wide, two-level hardware PUSH/POP stack.

A CALL instruction will PUSH the current value of stack 1 into stack 2 and then PUSH the current program counter value, incremented by one, into stack level 1. If more than two sequential CALL's are executed, only the most recent two return addresses are stored.

A RETLW instruction will POP the contents of stack level 1 into the program counter and then copy stack level 2 contents into level 1. If more than two sequential RETLW's are executed, the stack will be filled with the address previously stored in level 2.

| Note: | The W register will be loaded with the      |

|-------|---------------------------------------------|

|       | literal value specified in the instruction. |

|       | This is particularly useful for the         |

|       | implementation of data look-up tables       |

|       | within the program memory.                  |

For the RETLW instruction, the PC is loaded with the Top-of-Stack (TOS) contents. All of the devices covered in this data sheet have a two-level stack. The stack has the same bit width as the device PC, therefore, paging is not an issue when returning from a subroutine.

# 3.7 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR Register (FSR is a *pointer*). This is indirect addressing.

#### EXAMPLE 3-1: INDIRECT ADDRESSING

- Register file 08 contains the value 10h

- Register file 09 contains the value 0Ah

- Load the value 08 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 09h)

- A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 3-2.

#### EXAMPLE 3-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | MOVLW<br>MOVWF | H'10'<br>FSR | ;initialize pointer<br>;to RAM |

|----------|----------------|--------------|--------------------------------|

| NEXT     | CLRF           | INDF         | ;clear INDF Register           |

|          | INCF           | FSR,F        | ;inc pointer                   |

|          | BTFSC          | FSR,4        | ;all done?                     |

|          | GOTO           | NEXT         | ;NO, clear next                |

| CONTINUE |                |              |                                |

|          | :              |              | ;YES, continue                 |

The FSR is either a 5-bit (PIC16F54), 7-bit (PIC16F57) or 8-bit (PIC16F59) wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC16F54:** This does not use banking. FSR<7:5> bits are unimplemented and read as '1's.

**PIC16F57:** FSR<7> bit is unimplemented and read as '1'. FSR<6:5> are the bank select bits and are used to select the bank to be addressed (00 = Bank 0, 01 = Bank 1, 10 = Bank 2, 11 = Bank 3).

**PIC16F59:** FSR<7:5> are the bank select bits and are used to select the bank to be addressed (000 = Bank 0, 001 = Bank 1, 010 = Bank 2,

011 = Bank 3, 100 = Bank 4, 101 = Bank 5, 110 = Bank 6, 111 = Bank 7).

Note: A CLRF FSR instruction may not result in an FSR value of 00h if there are unimplemented bits present in the FSR.

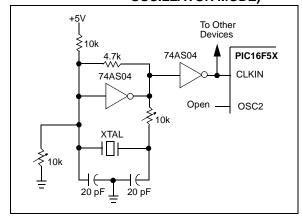

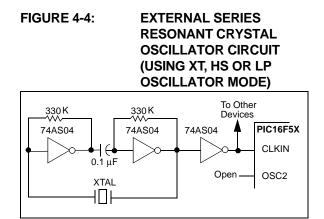

# 4.3 External Crystal Oscillator Circuit

Either a pre-packaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Pre-packaged oscillators provide a wide operating range and better stability. A well designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance or one with series resonance.

Figure 4-3 shows an implementation example of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

#### FIGURE 4-3:

RESONANT CRYSTAL OSCILLATOR CIRCUIT (USING XT, HS OR LP OSCILLATOR MODE)

EXTERNAL PARALLEL

Figure 4-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverters perform a 360° phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

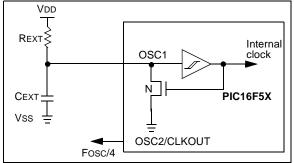

## 4.4 RC Oscillator

For applications where precise timing is not a requirement, the RC oscillator option is available. The operation and functionality of the RC oscillator is dependent upon a number of variables. The RC oscillator frequency is a function of:

- · Supply voltage

- Resistor (REXT) and capacitor (CEXT) values

- Operating temperature.

The oscillator frequency will vary from unit to unit due to normal process parameter variation. The difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to account for the tolerance of the external R and C components. Figure 4-5 shows how the R/C combination is connected.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin and can be used for test purposes or to synchronize other logic.

# 5.0 RESET

The PIC16F5X devices may be reset in one of the following ways:

- Power-on Reset (POR)

- MCLR Reset (normal operation)

- MCLR Wake-up Reset (from Sleep)

- WDT Reset (normal operation)

- WDT Wake-up Reset (from Sleep)

Table 5-1 shows these Reset conditions for the PCL and STATUS registers.

Some registers are not affected in any Reset condition. Their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset (POR), MCLR or WDT Reset. A MCLR or WDT wake-up from Sleep also results in a device Reset and not a continuation of operation before Sleep. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits (STATUS <4:3>) are set or cleared depending on the different Reset conditions (Table 5-1). These bits may be used to determine the nature of the Reset.

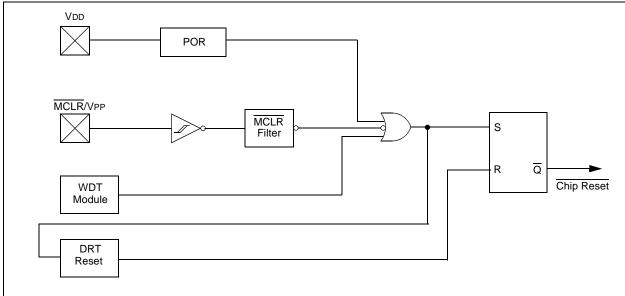

Table 5-3 lists a full description of Reset states of all registers. Figure 5-1 shows a simplified block diagram of the on-chip Reset circuit.

#### TABLE 5-1:STATUS BITS AND THEIR SIGNIFICANCE

| Condition                     | то | PD |

|-------------------------------|----|----|

| Power-on Reset                | 1  | 1  |

| MCLR Reset (normal operation) | u  | u  |

| MCLR Wake-up (from Sleep)     | 1  | 0  |

| WDT Reset (normal operation)  | 0  | 1  |

| WDT Wake-up (from Sleep)      | 0  | 0  |

**Legend:** u = unchanged, x = unknown, — = unimplemented read as '0'.

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH RESET

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | <u>Value</u> on<br>MCLR and<br>WDT Reset |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------|------------------------------------------|

| 03h     | STATUS | PA2   | PA1   | PA0   | TO    | PD    | Z     | DC    | С     | 0001 1xxx       | 000q quuu                                |

**Legend:** u = unchanged, x = unknown, q = see Table 5-1 for possible values.

| TABLE 5-3: | RESET CONDITIONS FOR ALL REGISTERS |

|------------|------------------------------------|

|------------|------------------------------------|

| Register             | Address    | Power-on Reset | MCLR or WDT Reset |  |

|----------------------|------------|----------------|-------------------|--|

| W                    | N/A        | xxxx xxxx      | սսսս սսսս         |  |

| TRIS                 | N/A        | 1111 1111      | 1111 1111         |  |

| OPTION               | N/A        | 11 1111        | 11 1111           |  |

| INDF                 | 00h        | XXXX XXXX      | uuuu uuuu         |  |

| TMR0                 | 01h        | XXXX XXXX      | uuuu uuuu         |  |

| PCL                  | 02h        | 1111 1111      | 1111 1111         |  |

| STATUS               | 03h        | 0001 1xxx      | 000q quuu         |  |

| FSR <sup>(1)</sup>   | 04h 111x x |                | 111u uuuu         |  |

| FSR <sup>(2)</sup>   | 04h        | 1xxx xxxx      | luuu uuuu         |  |

| FSR <sup>(3)</sup>   | 04h        | xxxx xxxx      | uuuu uuuu         |  |

| PORTA                | 05h        | xxxx           | uuuu              |  |

| PORTB                | 06h        | xxxx xxxx      | uuuu uuuu         |  |

| PORTC <sup>(4)</sup> | 07h        | xxxx xxxx      | uuuu uuuu         |  |

| PORTD <sup>(5)</sup> | 08h        | xxxx xxxx      | uuuu uuuu         |  |

| PORTE <sup>(5)</sup> | 09h        | xxxx           | uuuu              |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented, read as '0', q = see tables in Table 5-1 for possible values.

Note 1: PIC16F54 only.

2: PIC16F57 only.

3: PIC16F59 only.

4: General purpose register file on PIC16F54.

5: General purpose register file on PIC16F54 and PIC16F57.

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 7.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

# EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

|        | •           | ,                        |

|--------|-------------|--------------------------|

| CLRWDT |             | ;Clear WDT               |

| CLRF   | TMR0        | ;Clear TMR0 & ;Prescaler |

| MOVLW  | B'00xx1111' | ;Last 3 instructions     |

|        |             | ; in this example        |

| OPTION |             | ;are required only if    |

|        |             | ;desired                 |

| CLRWDT |             | ;PS<2:0> are 000 or 001  |

| MOVLW  | B'00xx1xxx′ | ;Set Prescaler to        |

| OPTION |             | ;desired WDT rate        |

|        |             |                          |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

| EXAMPLE 7-2: | CHANGING PRESCALER |  |  |

|--------------|--------------------|--|--|

|              | (WDT→TIMER0)       |  |  |

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| MOVLW  | B'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

|        |             | ;clock source       |

| OPTION |             |                     |

# FIGURE 7-5: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

# 9.0 INSTRUCTION SET SUMMARY

Each PIC16F5X instruction is a 12-bit word divided into an opcode, which specifies the instruction type, and one or more operands which further specify the operation of the instruction. The PIC16F5X instruction set summary in Table 9-2 groups the instructions into byteoriented, bit-oriented, and literal and control operations. Table 9-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator is used to specify which one of the 32 file registers in that bank is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8- or 9-bit constant or literal value.

| TABLE 9-1: | OPCODE FIELD |

|------------|--------------|

|            | DESCRIPTIONS |

| DESCRIPTIONS  |                                           |  |  |

|---------------|-------------------------------------------|--|--|

| Field         | Description                               |  |  |

| f             | Register file address (0x00 to 0x1F)      |  |  |

| W             | Working register (accumulator)            |  |  |

| b             | Bit address within an 8-bit file register |  |  |

| k             | Literal field, constant data or label     |  |  |

| x             | Don't care location (= 0 or 1)            |  |  |

|               | The assembler will generate code with     |  |  |

|               | x = 0. It is the recommended form of use  |  |  |

|               | for compatibility with all Microchip      |  |  |

|               | software tools.                           |  |  |

| d             | Destination select;                       |  |  |

|               | d = 0 (store result in W)                 |  |  |

|               | d = 1 (store result in file register 'f') |  |  |

|               | Default is d = 1                          |  |  |

| label         | Label name                                |  |  |

| TOS           | Top-of-Stack                              |  |  |

| PC            | Program Counter                           |  |  |

| WDT           | Watchdog Timer Counter                    |  |  |

| TO            | Time-out bit                              |  |  |

| PD            | Power-down bit                            |  |  |

| dest          | Destination, either the W register or the |  |  |

|               | specified register file location          |  |  |

| []            | Options                                   |  |  |

| ( )           | Contents                                  |  |  |

| $\rightarrow$ | Assigned to                               |  |  |

| < >           | Register bit field                        |  |  |

| ∈             | In the set of                             |  |  |

| italics       | User defined term                         |  |  |

|               |                                           |  |  |

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time would be 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time would be 2  $\mu$ s.

Figure 9-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

#### FIGURE 9-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                                                                   |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <b>11 6 5 4</b> 0                                                                                                                        |  |  |  |  |

| OPCODE d f (FILE #)                                                                                                                      |  |  |  |  |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 5-bit file register address                                                    |  |  |  |  |

| Bit-oriented file register operations                                                                                                    |  |  |  |  |

| <b>11 8 7 5 4</b> 0                                                                                                                      |  |  |  |  |

| OPCODE b (BIT #) f (FILE #)                                                                                                              |  |  |  |  |

| <ul> <li>b = 3-bit bit address</li> <li>f = 5-bit file register address</li> <li>Literal and control operations (except GOTO)</li> </ul> |  |  |  |  |

| <u>11 8 7 0</u>                                                                                                                          |  |  |  |  |

| OPCODE k (literal)                                                                                                                       |  |  |  |  |

| k = 8-bit immediate value                                                                                                                |  |  |  |  |

| Literal and control operations - GOTO instruction                                                                                        |  |  |  |  |

| <b>11 9 8</b> 0                                                                                                                          |  |  |  |  |

| OPCODE k (literal)                                                                                                                       |  |  |  |  |

| k = 9-bit immediate value                                                                                                                |  |  |  |  |

# PIC16F5X

| BSF                                                                           | Bit Set f                                                          |             |           |  |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------|-----------|--|

| Syntax:                                                                       | [label] BSF f, b                                                   |             |           |  |

| Operands:                                                                     | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |             |           |  |

| Operation:                                                                    | $1 \rightarrow (f < b >)$                                          |             |           |  |

| Status Affected:                                                              | None                                                               |             |           |  |

| Encoding:                                                                     | 0101                                                               | bbbf        | ffff      |  |

| Description:                                                                  | Bit 'b' in ı                                                       | register 'f | ' is set. |  |

| Words:                                                                        | 1                                                                  |             |           |  |

| Cycles:                                                                       | 1                                                                  |             |           |  |

| Example:                                                                      | BSF                                                                | FLAG_RE     | EG, 7     |  |

| Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG_REG = 0x8A |                                                                    |             |           |  |

| BTFSC                                                 | Bit Test f, Skip if Clear                                                                                                                                                                                                                                                   |  |  |  |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                               | [label] BTFSC f, b                                                                                                                                                                                                                                                          |  |  |  |

| Operands:                                             | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                          |  |  |  |

| Operation:                                            | skip if $(f < b >) = 0$                                                                                                                                                                                                                                                     |  |  |  |

| Status Affected:                                      | None                                                                                                                                                                                                                                                                        |  |  |  |

| Encoding:                                             | 0110 bbbf ffff                                                                                                                                                                                                                                                              |  |  |  |

| Description:                                          | If bit 'b' in register 'f' is '0', then the<br>next instruction is skipped.<br>If bit 'b' is '0', then the next instruc-<br>tion fetched during the current<br>instruction execution is discarded<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |  |  |  |

| Words:                                                | 1                                                                                                                                                                                                                                                                           |  |  |  |

| Cycles:                                               | 1(2)                                                                                                                                                                                                                                                                        |  |  |  |

| <u>Example</u> :                                      | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                                                                                                                                                                                                                 |  |  |  |

| Before Instru<br>PC<br>After Instruc<br>if FLAG<br>PC | <pre>= address (HERE) tion &lt;1&gt; = 0,                        = address (TRUE);</pre>                                                                                                                                                                                    |  |  |  |

| if FLAG<br>PC                                         | <1> = 1,<br>= address(FALSE)                                                                                                                                                                                                                                                |  |  |  |

| BTFSS                                    | Bit Test f, Skip if Set                                                                                                                                                                                                                                                     |                                                                 |                        |  |  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------|--|--|

| Syntax:                                  | [ label ]                                                                                                                                                                                                                                                                   | BTFSS f                                                         | , b                    |  |  |

| Operands:                                |                                                                                                                                                                                                                                                                             | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b < 7 \end{array}$ |                        |  |  |

| Operation:                               | skip if (f<                                                                                                                                                                                                                                                                 | :b>) = 1                                                        |                        |  |  |

| Status Affected:                         | None                                                                                                                                                                                                                                                                        |                                                                 |                        |  |  |

| Encoding:                                | 0111                                                                                                                                                                                                                                                                        | bbbf                                                            | ffff                   |  |  |

| Description:                             | If bit 'b' in register 'f' is '1', then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next instruc-<br>tion fetched during the current<br>instruction execution is discarded<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |                                                                 |                        |  |  |

| Words:                                   | 1                                                                                                                                                                                                                                                                           |                                                                 |                        |  |  |

| Cycles:                                  | 1(2)                                                                                                                                                                                                                                                                        |                                                                 |                        |  |  |

| <u>Example</u> :                         | HERE<br>FALSE<br>TRUE                                                                                                                                                                                                                                                       | BTFSS<br>GOTO<br>•                                              | FLAG,1<br>PROCESS_CODE |  |  |

| Before Inst                              | ruction                                                                                                                                                                                                                                                                     |                                                                 |                        |  |  |

| PC                                       | =                                                                                                                                                                                                                                                                           | addres                                                          | SS (HERE)              |  |  |

| After Instru<br>If FLAG<br>PC<br>if FLAG | <1> =                                                                                                                                                                                                                                                                       | 0,<br>addres<br>1,                                              | SS (FALSE);            |  |  |

| PC                                       | =                                                                                                                                                                                                                                                                           | addres                                                          | SS (TRUE)              |  |  |

# PIC16F5X

| COMF                                                 | Complement f                                                                                                                                                                |  |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                              | [ <i>label</i> ] COMF f, d                                                                                                                                                  |  |  |  |

| Operands:                                            | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                           |  |  |  |

| Operation:                                           | $(\overline{f}) \rightarrow (\text{dest})$                                                                                                                                  |  |  |  |

| Status Affected:                                     | Z                                                                                                                                                                           |  |  |  |

| Encoding:                                            | 0010 01df ffff                                                                                                                                                              |  |  |  |

| Description:                                         | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back in<br>register 'f'. |  |  |  |

| Words:                                               | 1                                                                                                                                                                           |  |  |  |

| Cycles:                                              | 1                                                                                                                                                                           |  |  |  |

| Example:                                             | COMF REG1,0                                                                                                                                                                 |  |  |  |

| Before Instru<br>REG1<br>After Instruct<br>REG1<br>W | = 0x13                                                                                                                                                                      |  |  |  |

| DECF                                        | Decrement f                                                                                                                                       |  |  |  |  |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                     | [ <i>label</i> ] DECF f, d                                                                                                                        |  |  |  |  |

| Operands:                                   | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                 |  |  |  |  |

| Operation:                                  | $(f) - 1 \rightarrow (dest)$                                                                                                                      |  |  |  |  |

| Status Affected:                            | Z                                                                                                                                                 |  |  |  |  |

| Encoding:                                   | 0000 11df ffff                                                                                                                                    |  |  |  |  |

| Description:                                | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |

| Words:                                      | 1                                                                                                                                                 |  |  |  |  |

| Cycles:                                     | 1                                                                                                                                                 |  |  |  |  |

| Example:                                    | DECF CNT, 1                                                                                                                                       |  |  |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct | = 0x01<br>= 0                                                                                                                                     |  |  |  |  |

| CNT<br>Z                                    | = 0x00<br>= 1                                                                                                                                     |  |  |  |  |

| DECFSZ                               | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                     |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                              | [label] DECFSZ f, d                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Operands:                            | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                          |  |  |  |

| Operation:                           | $(f) - 1 \rightarrow d;$ skip if result = 0                                                                                                                                                                                                                                                                                                |  |  |  |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Encoding:                            | 0010 11df ffff                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Description:                         | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1'. the result is placed back in<br>register 'f'. If the result is '0', the<br>next instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a<br>two-cycle instruction. |  |  |  |

| Words:                               | 1                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Cycles:                              | 1(2)                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Example:                             | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                         |  |  |  |

| Before Instru<br>PC<br>After Instruc | = address (HERE)                                                                                                                                                                                                                                                                                                                           |  |  |  |

| CNT<br>if CNT<br>PC<br>if CNT<br>PC  | <pre>= CNT - 1;<br/>= 0,<br/>= address (CONTINUE);<br/>≠ 0,<br/>= address (HERE+1)</pre>                                                                                                                                                                                                                                                   |  |  |  |

| GOTO                   | Unconditional Branch                                                                                                                                                                        |         |      |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--|

| Syntax:                | [ label ]                                                                                                                                                                                   | GOTO    | k    |  |

| Operands:              | $0 \le k \le 5$                                                                                                                                                                             | 11      |      |  |

| Operation:             | $k \rightarrow PC < 8:0>;$<br>STATUS<6:5> $\rightarrow PC < 10:9>$                                                                                                                          |         |      |  |

| Status Affected:       | None                                                                                                                                                                                        |         |      |  |

| Encoding:              | 101k                                                                                                                                                                                        | kkkk    | kkkk |  |

| Description:           | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS<6:5>. GOTO is a two-<br>cycle instruction. |         |      |  |

| Words:                 | 1                                                                                                                                                                                           |         |      |  |

| Cycles:                | 2                                                                                                                                                                                           |         |      |  |

| Example:               | GOTO THERE                                                                                                                                                                                  |         |      |  |

| After Instruct<br>PC = | ion<br>address                                                                                                                                                                              | G (THER | E)   |  |

| INCF                                                    | Increment f                                                                                                                                                                |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                 | [ <i>label</i> ] INCF f, d                                                                                                                                                 |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                           |

| Operation:                                              | (f) + 1 $\rightarrow$ (dest)                                                                                                                                               |

| Status Affected:                                        | Z                                                                                                                                                                          |

| Encoding:                                               | 0010 10df ffff                                                                                                                                                             |

| Description:                                            | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| Words:                                                  | 1                                                                                                                                                                          |

| Cycles:                                                 | 1                                                                                                                                                                          |

| Example:                                                | INCF CNT, 1                                                                                                                                                                |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                              |

| INCFSZ                                                                          | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                          |  |  |  |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                                                         | [label] INCFSZ f, d                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Operands:                                                                       | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                                                       |  |  |  |

| Operation:                                                                      | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                                |  |  |  |

| Status Affected:                                                                | None                                                                                                                                                                                                                                                                                                                                            |  |  |  |