Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | PIC                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | -                                                                      |

| Peripherals                | POR, WDT                                                               |

| Number of I/O              | 32                                                                     |

| Program Memory Size        | 3KB (2K x 12)                                                          |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 134 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                              |

| Data Converters            | -                                                                      |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                               |

| Supplier Device Package    | 40-PDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f59-e-p |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

NOTES:

## 3.4 Option Register

The Option register is a 6-bit wide, write-only register which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the Option register. A Reset sets the Option<5:0> bits.

## **REGISTER 3-2: OPTION REGISTER**

| U-0   | U-0 | W-1  | W-1  | W-1 | W-1 | W-1 | W-1   |

|-------|-----|------|------|-----|-----|-----|-------|

|       | —   | TOCS | T0SE | PSA | PS2 | PS1 | PS0   |

| bit 7 |     |      |      |     |     |     | bit 0 |

bit 7-6 Unimplemented: Read as '0'

| bit 5   | T0CS: Timer0 Clock Source Select bit                                                                                                   |               |                |          |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|----------|--|

|         | 1 = Transition on T0CKI pin                                                                                                            |               |                |          |  |

|         | 0 = Intern                                                                                                                             | nal instructi | on cycle clocł | (CLKOUT) |  |

| bit 4   | TOSE: Tir                                                                                                                              | mer0 Sourc    | e Edge Seleo   | t bit    |  |

|         | <ul> <li>1 = Increment on high-to-low transition on T0CKI pin</li> <li>0 = Increment on low-to-high transition on T0CKI pin</li> </ul> |               |                |          |  |

| bit 3   | PSA: Pre                                                                                                                               | scaler Ass    | ignment bit    |          |  |

|         | 1 = Preso                                                                                                                              | aler assigr   | ned to the WE  | T        |  |

|         | 0 = Presc                                                                                                                              | caler assigr  | ned to Timer0  |          |  |

| bit 2-0 | PS<2:0>: Prescaler rate select bits                                                                                                    |               |                |          |  |

|         |                                                                                                                                        | Bit Value     | Timer0 Rate    | WDT Rate |  |

|         |                                                                                                                                        | 000           | 1:2            | 1:1      |  |

|         | 001 1:4 1:2                                                                                                                            |               |                |          |  |

| 000 | 1:2     | 1:1     |

|-----|---------|---------|

| 001 | 1:4     | 1:2     |

| 010 | 1:8     | 1:4     |

| 011 | 1:16    | 1:8     |

| 100 | 1:32    | 1:16    |

| 101 | 1:64    | 1:32    |

| 110 | 1:128   | 1:64    |

| 111 | 1 : 256 | 1 : 128 |

|     |         |         |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 4.0 OSCILLATOR CONFIGURATIONS

## 4.1 Oscillator Types

The PIC16F5X devices can be operated in four different oscillator modes. The user can program two Configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LP: Low-power Crystal

- XT: Crystal/Resonator

- HS: High-speed Crystal/Resonator

- RC: Resistor/Capacitor

# 4.2 Crystal Oscillator/Ceramic Resonators

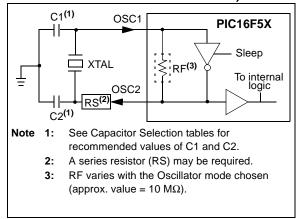

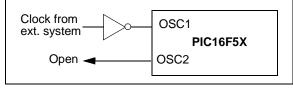

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 4-1). The PIC16F5X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency outside of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source drive the OSC1/CLKIN pin (Figure 4-2).

## FIGURE 4-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

FIGURE 4-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

# TABLE 4-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Osc<br>Type | Resonator<br>Freq. | Cap. Range<br>C1 | Cap. Range<br>C2 |

|-------------|--------------------|------------------|------------------|

| XT          | 455 kHz            | 68-100 pF        | 68-100 pF        |

|             | 2.0 MHz            | 15-33 pF         | 15-33 pF         |

|             | 4.0 MHz            | 10-22 pF         | 10-22 pF         |

| HS          | 8.0 MHz            | 10-22 pF         | 10-22 pF         |

|             | 16.0 MHz           | 10 pF            | 10 pF            |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

## TABLE 4-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Crystal<br>Freq.      | Cap.Range<br>C1                                                                                              | Cap. Range<br>C2                                                                                                                                                                                                                                                                                                         |

|-----------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32 kHz <sup>(1)</sup> | 15 pF                                                                                                        | 15 pF                                                                                                                                                                                                                                                                                                                    |

| 100 kHz               | 15-30 pF                                                                                                     | 200-300 pF                                                                                                                                                                                                                                                                                                               |

| 200 kHz               | 15-30 pF                                                                                                     | 100-200 pF                                                                                                                                                                                                                                                                                                               |

| 455 kHz               | 15-30 pF                                                                                                     | 15-100 pF                                                                                                                                                                                                                                                                                                                |

| 1 MHz                 | 15-30 pF                                                                                                     | 15-30 pF                                                                                                                                                                                                                                                                                                                 |

| 2 MHz                 | 15 pF                                                                                                        | 15 pF                                                                                                                                                                                                                                                                                                                    |

| 4 MHz                 | 15 pF                                                                                                        | 15 pF                                                                                                                                                                                                                                                                                                                    |

| 4 MHz                 | 15 pF                                                                                                        | 15 pF                                                                                                                                                                                                                                                                                                                    |

| 8 MHz                 | 15 pF                                                                                                        | 15 pF                                                                                                                                                                                                                                                                                                                    |

| 20 MHz                | 15 pF                                                                                                        | 15 pF                                                                                                                                                                                                                                                                                                                    |

|                       | Freq.<br>32 kHz <sup>(1)</sup><br>100 kHz<br>200 kHz<br>455 kHz<br>1 MHz<br>2 MHz<br>4 MHz<br>4 MHz<br>8 MHz | Freq.         C1           32 kHz <sup>(1)</sup> 15 pF           100 kHz         15-30 pF           200 kHz         15-30 pF           455 kHz         15-30 pF           1 MHz         15-30 pF           2 MHz         15 pF           4 MHz         15 pF           4 MHz         15 pF           8 MHz         15 pF |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specifications. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

2: The user should verify that the device oscillator starts and performs as expected. Adjusting the loading capacitor values and/or the Oscillator mode may be required.

Note 1: This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.

| TABLE 5-3: | RESET CONDITIONS FOR ALL REGISTERS |

|------------|------------------------------------|

|------------|------------------------------------|

| Register             | Address | Power-on Reset | MCLR or WDT Reset |

|----------------------|---------|----------------|-------------------|

| W                    | N/A     | xxxx xxxx      | սսսս սսսս         |

| TRIS                 | N/A     | 1111 1111      | 1111 1111         |

| OPTION               | N/A     | 11 1111        | 11 1111           |

| INDF                 | 00h     | XXXX XXXX      | uuuu uuuu         |

| TMR0                 | 01h     | XXXX XXXX      | uuuu uuuu         |

| PCL                  | 02h     | 1111 1111      | 1111 1111         |

| STATUS               | 03h     | 0001 1xxx      | 000q quuu         |

| FSR <sup>(1)</sup>   | 04h     | 111x xxxx      | 111u uuuu         |

| FSR <sup>(2)</sup>   | 04h     | 1xxx xxxx      | luuu uuuu         |

| FSR <sup>(3)</sup>   | 04h     | xxxx xxxx      | uuuu uuuu         |

| PORTA                | 05h     | xxxx           | uuuu              |

| PORTB                | 06h     | xxxx xxxx      | uuuu uuuu         |

| PORTC <sup>(4)</sup> | 07h     | xxxx xxxx      | uuuu uuuu         |

| PORTD <sup>(5)</sup> | 08h     | xxxx xxxx      | uuuu uuuu         |

| PORTE <sup>(5)</sup> | 09h     | xxxx           | uuuu              |

**Legend:** u = unchanged, x = unknown, - = unimplemented, read as '0', q = see tables in Table 5-1 for possible values.

Note 1: PIC16F54 only.

2: PIC16F57 only.

3: PIC16F59 only.

4: General purpose register file on PIC16F54.

5: General purpose register file on PIC16F54 and PIC16F57.

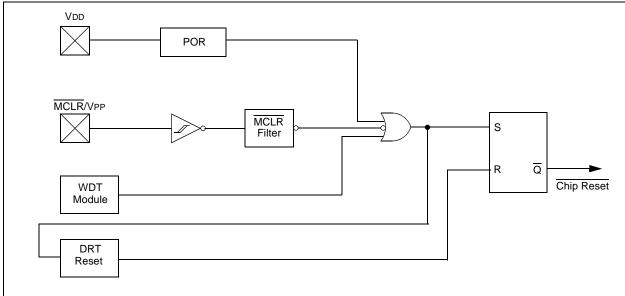

## FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

NOTES:

# PIC16F5X

| Bit Set f                                                                     |                                                                                                                 |                                                                                                                                                                             |                                                                                                                                                                                                |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [label]                                                                       | BSF f, b                                                                                                        | )                                                                                                                                                                           |                                                                                                                                                                                                |

| operands: $0 \le f \le 31$ $0 \le b \le 7$                                    |                                                                                                                 |                                                                                                                                                                             |                                                                                                                                                                                                |

| $1 \rightarrow (f < b >)$                                                     |                                                                                                                 |                                                                                                                                                                             |                                                                                                                                                                                                |

| None                                                                          |                                                                                                                 |                                                                                                                                                                             |                                                                                                                                                                                                |

| 0101                                                                          | bbbf                                                                                                            | ffff                                                                                                                                                                        |                                                                                                                                                                                                |

| Bit 'b' in register 'f' is set.                                               |                                                                                                                 |                                                                                                                                                                             |                                                                                                                                                                                                |

| 1                                                                             |                                                                                                                 |                                                                                                                                                                             |                                                                                                                                                                                                |

| 1                                                                             |                                                                                                                 |                                                                                                                                                                             |                                                                                                                                                                                                |

| BSF                                                                           | FLAG_RE                                                                                                         | G, 7                                                                                                                                                                        |                                                                                                                                                                                                |

| Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG_REG = 0x8A |                                                                                                                 |                                                                                                                                                                             |                                                                                                                                                                                                |

|                                                                               | $[label] I 0 \le f \le 31 0 \le b \le 7 1 \rightarrow (f < b: None 0101 Bit 'b' in r 1 BSF action REG = 0 tion$ | $[label] BSF f, b$ $0 \le f \le 31$ $0 \le b \le 7$ $1 \rightarrow (f < b >)$ None $\boxed{0101 \ bbbf}$ Bit 'b' in register 'f' $1$ $BSF FLAG_RE$ action $REG = 0x0A$ tion | $[label] BSF f, b$ $0 \le f \le 31$ $0 \le b \le 7$ $1 \rightarrow (f < b >)$ None $\boxed{0101 \ bbbf \ ffff}$ Bit 'b' in register 'f' is set. $1$ $1$ BSF FLAG_REG, 7 action REG = 0x0A tion |

| BTFSC                                                 | Bit Test f, Skip if Clear                                                                                                                                                                                                                                                   |  |  |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                               | [label] BTFSC f, b                                                                                                                                                                                                                                                          |  |  |

| Operands:                                             | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                          |  |  |

| Operation:                                            | skip if $(f < b >) = 0$                                                                                                                                                                                                                                                     |  |  |

| Status Affected:                                      | None                                                                                                                                                                                                                                                                        |  |  |

| Encoding:                                             | 0110 bbbf ffff                                                                                                                                                                                                                                                              |  |  |

| Description:                                          | If bit 'b' in register 'f' is '0', then the<br>next instruction is skipped.<br>If bit 'b' is '0', then the next instruc-<br>tion fetched during the current<br>instruction execution is discarded<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |  |  |

| Words:                                                | 1                                                                                                                                                                                                                                                                           |  |  |

| Cycles:                                               | 1(2)                                                                                                                                                                                                                                                                        |  |  |

| <u>Example</u> :                                      | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                                                                                                                                                                                                                 |  |  |

| Before Instru<br>PC<br>After Instruc<br>if FLAG<br>PC | <pre>= address (HERE) tion &lt;1&gt; = 0,                        = address (TRUE);</pre>                                                                                                                                                                                    |  |  |

| if FLAG<br>PC                                         | <1> = 1,<br>= address(FALSE)                                                                                                                                                                                                                                                |  |  |

| BTFSS                                    | Bit Test                                                                                                                                                                                                                                                                    | f, Skip if         | Set                    |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------|

| Syntax:                                  | [ label ]                                                                                                                                                                                                                                                                   | BTFSS f            | , b                    |

| Operands:                                | 0 ≤ f ≤ 31<br>0 ≤ b < 7                                                                                                                                                                                                                                                     | -                  |                        |

| Operation:                               | skip if (f<                                                                                                                                                                                                                                                                 | :b>) = 1           |                        |

| Status Affected:                         | None                                                                                                                                                                                                                                                                        |                    |                        |

| Encoding:                                | 0111                                                                                                                                                                                                                                                                        | bbbf               | ffff                   |

| Description:                             | If bit 'b' in register 'f' is '1', then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next instruc-<br>tion fetched during the current<br>instruction execution is discarded<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |                    |                        |

| Words:                                   | 1                                                                                                                                                                                                                                                                           |                    |                        |

| Cycles:                                  | 1(2)                                                                                                                                                                                                                                                                        |                    |                        |

| <u>Example</u> :                         | HERE<br>FALSE<br>TRUE                                                                                                                                                                                                                                                       | BTFSS<br>GOTO<br>• | FLAG,1<br>PROCESS_CODE |

| Before Inst                              | ruction                                                                                                                                                                                                                                                                     |                    |                        |

| PC                                       | =                                                                                                                                                                                                                                                                           | addres             | SS (HERE)              |

| After Instru<br>If FLAG<br>PC<br>if FLAG | <1> =                                                                                                                                                                                                                                                                       | 0,<br>addres<br>1, | SS (FALSE);            |

| PC                                       | =                                                                                                                                                                                                                                                                           | addres             | SS (TRUE)              |

| CALL                   | Subroutine Call                                                                                                                                                                                                                                                      |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                | [ <i>label</i> ] CALL k                                                                                                                                                                                                                                              |

| Operands:              | $0 \le k \le 255$                                                                                                                                                                                                                                                    |

| Operation:             | $\begin{array}{l} (\text{PC}) + 1 \rightarrow \text{TOS}; \\ k \rightarrow \text{PC}{<}7:0{>}; \\ (\text{Status}{<}6:5{>}) \rightarrow \text{PC}{<}10:9{>}; \\ 0 \rightarrow \text{PC}{<}8{>} \end{array}$                                                           |

| Status Affected:       | None                                                                                                                                                                                                                                                                 |

| Encoding:              | 1001 kkkk kkkk                                                                                                                                                                                                                                                       |

| Description:           | Subroutine call. First, return<br>address (PC + 1) is pushed onto<br>the stack. The eight-bit immediate<br>address is loaded into PC bits<br><7:0>. The upper bits PC<10:9><br>are loaded from STATUS<6:5>,<br>PC<8> is cleared. CALL is a<br>two-cycle instruction. |

| Words:                 | 1                                                                                                                                                                                                                                                                    |

| Cycles:                | 2                                                                                                                                                                                                                                                                    |

| Example:               | HERE CALL THERE                                                                                                                                                                                                                                                      |

| After Instruct<br>PC = | address (HERE)                                                                                                                                                                                                                                                       |

| CLRW             | Clear W                                                              |             |            |          |

|------------------|----------------------------------------------------------------------|-------------|------------|----------|

| Syntax:          | [ label ]                                                            | CLRW        |            |          |

| Operands:        | None                                                                 |             |            |          |

| Operation:       | $\begin{array}{l} 00h \rightarrow (V \\ 1 \rightarrow Z \end{array}$ | V);         |            |          |

| Status Affected: | Z                                                                    |             |            |          |

| Encoding:        | 0000                                                                 | 0100        | 0000       |          |

| Description:     | The W re                                                             | gister is o | cleared. Z | Zero bit |

|                  | (Z) is set                                                           |             |            |          |

| Words:           | 1                                                                    |             |            |          |

| Cycles:          | 1                                                                    |             |            |          |

| Example:         | CLRW                                                                 |             |            |          |

| Before Instru    | ction                                                                |             |            |          |

| W =              | 0x5A                                                                 |             |            |          |

| After Instruct   | ion                                                                  |             |            |          |

| W =              | 0x00                                                                 |             |            |          |

| Z =              | 1                                                                    |             |            |          |

## CLRF Clear f

| -                                                          |                                                                      |                         |                               |

|------------------------------------------------------------|----------------------------------------------------------------------|-------------------------|-------------------------------|

| Syntax:                                                    | [ label ]                                                            | CLRF f                  |                               |

| Operands:                                                  | $0 \le f \le 3^{2}$                                                  | 1                       |                               |

| Operation:                                                 | $\begin{array}{c} 00h \rightarrow (f \\ 1 \rightarrow Z \end{array}$ | );                      |                               |

| Status Affected:                                           | Z                                                                    |                         |                               |

| Encoding:                                                  | 0000                                                                 | 011f                    | ffff                          |

| Description:                                               |                                                                      | ents of re<br>and the Z | gister 'f' are<br>bit is set. |

| Words:                                                     | 1                                                                    |                         |                               |

| Cycles:                                                    | 1                                                                    |                         |                               |

| Example:                                                   | CLRF                                                                 | FLAG_RE                 | IG                            |

| Before Instru<br>FLAG_RI<br>After Instruct<br>FLAG_RI<br>Z | EG =<br>ion                                                          | 0x5A<br>0x00<br>1       |                               |

| CLRWDT                                                                                      | Clear Wa                                                                                                                          | tchdog                                 | Timer                                 |              |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------|--------------|

| Syntax:                                                                                     | [ label ]                                                                                                                         | CLRWD                                  | Γ                                     |              |

| Operands:                                                                                   | None                                                                                                                              |                                        |                                       |              |

| Operation:                                                                                  | $\begin{array}{l} 00h \rightarrow W\\ 0 \rightarrow WDT\\ 1 \rightarrow \overline{TO};\\ 1 \rightarrow \overline{PD} \end{array}$ |                                        | er (if assi                           | gned);       |

| Status Affected:                                                                            | TO, PD                                                                                                                            |                                        |                                       |              |

| Encoding:                                                                                   | 0000                                                                                                                              | 0000                                   | 0100                                  |              |

| Description:                                                                                | The CLR<br>WDT. It a<br>the presc<br>WDT and<br>TO and P                                                                          | lso resets<br>aler is as<br>I not Time | s the pres<br>signed to<br>er0. Statu | caler if the |

| Words:                                                                                      | 1                                                                                                                                 |                                        |                                       |              |

| Cycles:                                                                                     | 1                                                                                                                                 |                                        |                                       |              |

| Example:                                                                                    | CLRWDT                                                                                                                            |                                        |                                       |              |

| Before Instru<br>WDT con<br>After Instruct<br>WDT con<br><u>WD</u> T pre<br><u>TO</u><br>PD | unter =<br>tion                                                                                                                   | ?<br>0x00<br>0<br>1<br>1               |                                       |              |

# PIC16F5X

| COMF                                                 | Complement f                                                                                                                                                                |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                              | [ <i>label</i> ] COMF f, d                                                                                                                                                  |

| Operands:                                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                |

| Operation:                                           | $(\overline{f}) \rightarrow (dest)$                                                                                                                                         |

| Status Affected:                                     | Z                                                                                                                                                                           |

| Encoding:                                            | 0010 01df ffff                                                                                                                                                              |

| Description:                                         | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back in<br>register 'f'. |

| Words:                                               | 1                                                                                                                                                                           |

| Cycles:                                              | 1                                                                                                                                                                           |

| Example:                                             | COMF REG1,0                                                                                                                                                                 |

| Before Instru<br>REG1<br>After Instruct<br>REG1<br>W | = 0x13                                                                                                                                                                      |

| DECF                                        | Decrement f                                                                                                                                       |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                     | [label] DECF f, d                                                                                                                                 |

| Operands:                                   | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                  |

| Operation:                                  | $(f) - 1 \rightarrow (dest)$                                                                                                                      |

| Status Affected:                            | Z                                                                                                                                                 |

| Encoding:                                   | 0000 11df ffff                                                                                                                                    |

| Description:                                | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| Words:                                      | 1                                                                                                                                                 |

| Cycles:                                     | 1                                                                                                                                                 |

| Example:                                    | DECF CNT, 1                                                                                                                                       |

| Before Instru<br>CNT<br>Z<br>After Instruct | = 0x01<br>= 0                                                                                                                                     |

| CNT<br>Z                                    | = 0x00<br>= 1                                                                                                                                     |

| DECFSZ                               | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                              | [label] DECFSZ f, d                                                                                                                                                                                                                                                                                                                        |

| Operands:                            | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                                                  |

| Operation:                           | $(f) - 1 \rightarrow d;$ skip if result = 0                                                                                                                                                                                                                                                                                                |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                            | 0010 11df ffff                                                                                                                                                                                                                                                                                                                             |

| Description:                         | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1'. the result is placed back in<br>register 'f'. If the result is '0', the<br>next instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a<br>two-cycle instruction. |

| Words:                               | 1                                                                                                                                                                                                                                                                                                                                          |

| Cycles:                              | 1(2)                                                                                                                                                                                                                                                                                                                                       |

| Example:                             | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                         |

| Before Instru<br>PC<br>After Instruc | = address (HERE)                                                                                                                                                                                                                                                                                                                           |

| CNT<br>if CNT<br>PC<br>if CNT<br>PC  | <pre>= CNT - 1;<br/>= 0,<br/>= address (CONTINUE);<br/>≠ 0,<br/>= address (HERE+1)</pre>                                                                                                                                                                                                                                                   |

| MOVWF               | Move W to f                                    |

|---------------------|------------------------------------------------|

| Syntax:             | [label] MOVWF f                                |

| Operands:           | $0 \le f \le 31$                               |

| Operation:          | $(W) \rightarrow (f)$                          |

| Status Affected:    | None                                           |

| Encoding:           | 0000 001f ffff                                 |

| Description:        | Move data from the W register to register 'f'. |

| Words:              | 1                                              |

| Cycles:             | 1                                              |

| Example:            | MOVWF TEMP_REG                                 |

| W<br>After Instruct | REG = 0xFF $= 0x4F$                            |

## No Operation

NOP

| Syntax:          | [ label ] | NOP    |      |

|------------------|-----------|--------|------|

| Operands:        | None      |        |      |

| Operation:       | No opera  | ation  |      |

| Status Affected: | None      |        |      |

| Encoding:        | 0000      | 0000   | 0000 |

| Description:     | No opera  | ation. |      |

| Words:           | 1         |        |      |

| Cycles:          | 1         |        |      |

| Example:         | NOP       |        |      |

| OPTION                    | Load OPTION Register                                       |  |

|---------------------------|------------------------------------------------------------|--|

| Syntax:                   | [label] OPTION                                             |  |

| Operands:                 | None                                                       |  |

| Operation:                | $(W) \to OPTION$                                           |  |

| Status Affected:          | None                                                       |  |

| Encoding:                 | 0000 0000 0010                                             |  |

| Description:              | The content of the W registe loaded into the Option regist |  |

| Words:                    | 1                                                          |  |

| Cycles:                   | 1                                                          |  |

| Example:                  | OPTION                                                     |  |

| Before Instru             | ction                                                      |  |

| W                         | = 0x07                                                     |  |

| After Instructi<br>OPTION | on<br>= 0x07                                               |  |

| RETLW                                    | Return with Literal in W                                                                                                                                                            |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                  | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:                                | $0 \le k \le 255$                                                                                                                                                                   |

| Operation:                               | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected:                         | None                                                                                                                                                                                |

| Encoding:                                | 1000 kkkk kkkk                                                                                                                                                                      |

| Description:                             | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address). This<br>is a two-cycle instruction. |

| Words:                                   | 1                                                                                                                                                                                   |

| Cycles:                                  | 2                                                                                                                                                                                   |

| <u>Example</u> :                         | CALL TABLE;W contains<br>;table offset<br>;value.<br>• ;W now has table<br>• ;value.                                                                                                |

| TABLE                                    | •                                                                                                                                                                                   |

|                                          | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•                                                                                                                    |

|                                          |                                                                                                                                                                                     |

| Before Instru<br>W<br>After Instruc<br>W | = 0x07                                                                                                                                                                              |

# PIC16F5X

| XORLW                                         | Exclusive OR literal with W                                                                                       |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:                                       | [ <i>label</i> ] XORLW k                                                                                          |

| Operands:                                     | $0 \le k \le 255$                                                                                                 |

| Operation:                                    | (W) .XOR. $k \rightarrow (W)$                                                                                     |

| Status Affected:                              | Z                                                                                                                 |

| Encoding:                                     | 1111 kkkk kkkk                                                                                                    |

| Description:                                  | The contents of the W register are XOR'ed with the eight-bit literal 'k'. The result is placed in the W register. |

| Words:                                        | 1                                                                                                                 |

| Cycles:                                       | 1                                                                                                                 |

| Example:                                      | XORLW <b>OxAF</b>                                                                                                 |

| Before Instru<br>W =<br>After Instruct<br>W = | 0xB5                                                                                                              |

| XORWF                                                   | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |  |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                 | [label] XORWF f, d                                                                                                                                                              |  |  |  |  |  |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                |  |  |  |  |  |

| Operation:                                              | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                              |  |  |  |  |  |

| Status Affected:                                        | Z                                                                                                                                                                               |  |  |  |  |  |

| Encoding:                                               | 0001 10df ffff                                                                                                                                                                  |  |  |  |  |  |

| Description:                                            | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |

| Words:                                                  | 1                                                                                                                                                                               |  |  |  |  |  |

| Cycles:                                                 | 1                                                                                                                                                                               |  |  |  |  |  |

| Example:                                                | XORWF REG,1                                                                                                                                                                     |  |  |  |  |  |

| Before Instru<br>REG<br>W<br>After Instruct<br>REG<br>W | = 0xAF<br>= 0xB5                                                                                                                                                                |  |  |  |  |  |

# 11.0 ELECTRICAL SPECIFICATIONS FOR PIC16F54/57

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient Temperature under bias                                   | 40°C to +125°C                   |

|------------------------------------------------------------------|----------------------------------|

| Storage Temperature                                              | 65°C to +150°C                   |

| Voltage on VDD with respect to Vss                               | 0V to +6.5V                      |

| Voltage on MCLR with respect to Vss <sup>(1)</sup>               | 0V to +13.5V                     |

| Voltage on all other pins with respect to Vss                    | 0.6V to (VDD + 0.6V)             |

| Total power dissipation <sup>(2)</sup>                           |                                  |

| Max. current out of Vss pin                                      |                                  |

| Max. current into Vod pin                                        | 100 mA                           |

| Max. current into an input pin (T0CKI only)                      | ±500 μA                          |

| Input clamp current, Iıк (Vı < 0 or Vı > Vɒɒ)                    | ±20 mA                           |

| Output clamp current, IOK (VO < 0 or VO > VDD)                   | ±20 mA                           |

| Max. output current sunk by any I/O pin                          | 25 mA                            |

| Max. output current sourced by any I/O pin                       | 25 mA                            |

| Max. output current sourced by a single I/O port (PORTA, B or C) | 50 mA                            |

| Max. output current sunk by a single I/O port (PORTA, B or C)    | 50 mA                            |

| Note 4. Mattern and the balance was the MOLD at a balance and    | standhan 00 m A manual state and |

- **Note 1:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50 to 100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

- 2: Power Dissipation is calculated as follows: Pdis = VDD x {IDD  $\Sigma$  IOH} +  $\Sigma$  {(VDD VOH) x IOH} +  $\Sigma$ (VOL x IOL)

†NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| DC CHARACTERISTICS |      | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |       |      |      |       |                                                                         |

|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|-------------------------------------------------------------------------|

| Param<br>No.       | Sym. | Characteristic/Device                                                                                                                | Min.  | Тур† | Max. | Units | Conditions                                                              |

| D001               | Vdd  | Supply Voltage                                                                                                                       | 2.0   | _    | 5.5  | V     |                                                                         |

| D002               | Vdr  | RAM Data Retention Voltage <sup>(1)</sup>                                                                                            | _     | 1.5* |      | V     | Device in Sleep mode                                                    |

| D003               | Vpor | VDD Start Voltage to ensure<br>Power-on Reset                                                                                        |       | Vss  | —    | V     | See Section 5.1 "Power-on Reset (POR)" for details on Power-on Reset    |

| D004               | Svdd | VDD Rise Rate to ensure<br>Power-on Reset                                                                                            | 0.05* | _    | _    | V/ms  | See Section 5.1 "Power-on Reset<br>(POR)" for details on Power-on Reset |

| D010               | Idd  | Supply Current <sup>(2)</sup>                                                                                                        |       |      |      |       |                                                                         |

|                    |      |                                                                                                                                      |       | 170  | 450  | μA    | FOSC = 4 MHz, VDD = 2.0V, XT or RC mode <sup>(3)</sup>                  |

|                    |      |                                                                                                                                      | —     | 0.4  | 2.0  | mΑ    | Fosc = 10 MHz, VDD = 3.0V, HS mode                                      |

|                    |      |                                                                                                                                      | —     | 1.7  | 7.0  | mA    | Fosc = 20 MHz, VDD = 5.0V, HS mode                                      |

|                    |      |                                                                                                                                      | —     | 15   | 40   | μA    | Fosc = 32 kHz, VDD = 2.0V, LP mode,<br>WDT disabled                     |

| D020               | IPD  | Power-down Current <sup>(2)</sup>                                                                                                    |       |      |      |       |                                                                         |

|                    |      |                                                                                                                                      | _     | 1.0  | 15.0 | μA    | $V_{DD} = 2.0V, WDT$ enabled                                            |

|                    |      |                                                                                                                                      | —     | 0.5  | 8.0  | μA    | VDD = 2.0V, WDT disabled                                                |

# 11.2 DC Characteristics: PIC16F5X (Extended)

\* These parameters are characterized but not tested.

† Data in "Typ" column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature, also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in Sleep mode. The Power-down Current in Sleep mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

| Param<br>No. | Sym.     | Characteristic                                                        | Min.         | Тур† | Max. | Units |

|--------------|----------|-----------------------------------------------------------------------|--------------|------|------|-------|

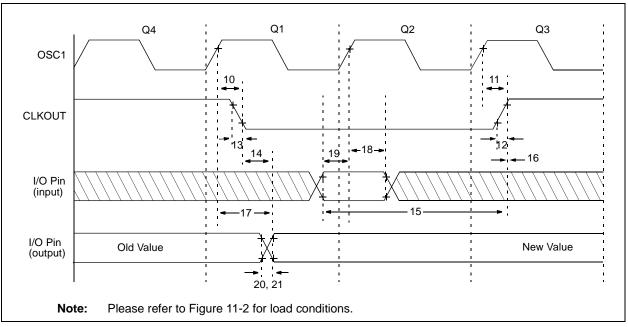

| 10           | TosH2CKL | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                       | —            | 15   | 30** | ns    |

| 11           | TosH2CKH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑(1)</sup>                           | —            | 15   | 30** | ns    |

| 12           | TCKR     | CLKOUT rise time <sup>(1)</sup>                                       | —            | 5.0  | 15** | ns    |

| 13           | ТскF     | CLKOUT fall time <sup>(1)</sup>                                       | —            | 5.0  | 15** | ns    |

| 14           | TCKL2IOV | CLKOUT↓ to Port out valid <sup>(1)</sup>                              | —            | _    | 40** | ns    |

| 15           | ТюV2скН  | Port in valid before CLKOUT <sup>(1)</sup>                            | 0.25 TCY+30* | _    | _    | ns    |

| 16           | TCKH2IOI | Port in hold after CLKOUT <sup>(1)</sup>                              | 0*           | _    |      | ns    |

| 17           | TosH2IoV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2)</sup>         | —            | _    | 100* | ns    |

| 18           | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time) | TBD          | —    | _    | ns    |

| 19           | TIOV20sH | Port input valid to OSC1↑<br>(I/O in setup time)                      | TBD          | —    | _    | ns    |

| 20           | TIOR     | Port output rise time <sup>(2, 3)</sup>                               | —            | 10   | 25** | ns    |

| 20           | TIOR     | Port output rise time <sup>(2, 4)</sup>                               | —            | 10   | 50** | ns    |

| 21           | TIOF     | Port output fall time <sup>(2, 3)</sup>                               | —            | 10   | 25** | ns    |

| 21           | TIOF     | Port output fall time <sup>(2, 4)</sup>                               | —            | 10   | 50** | ns    |

TABLE 11-2: CLKOUT AND I/O TIMING REQUIREMENTS – PIC16F5X

**Legend:** TBD = To Be Determined.