Welcome to E-XFL.COM

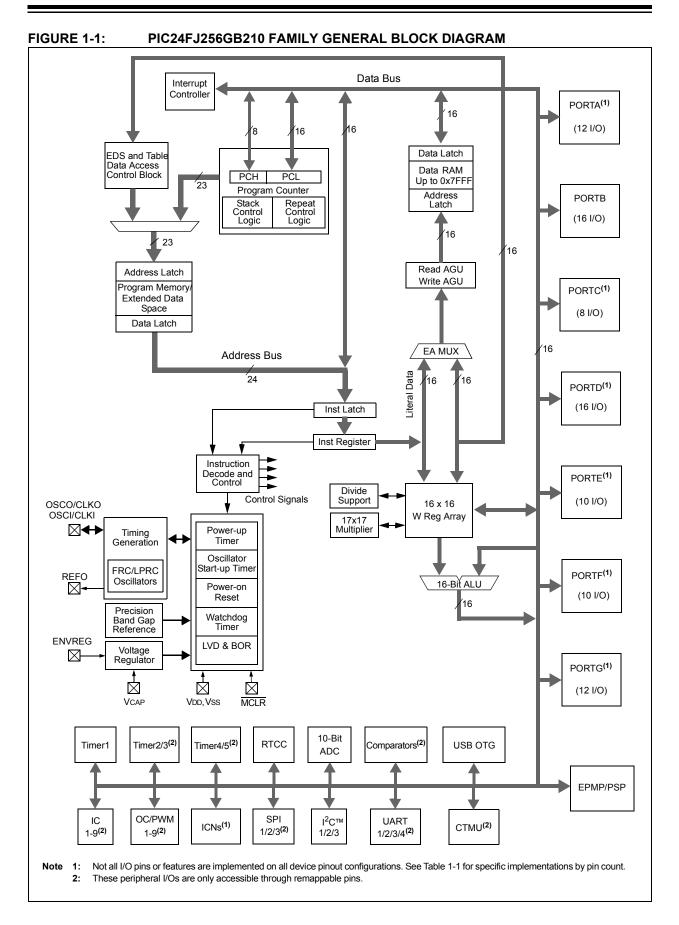

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 52                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 96K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb206t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                               | Pin Number      |                |     | Input  |                                                                       |

|----------|-------------------------------|-----------------|----------------|-----|--------|-----------------------------------------------------------------------|

| Function | 64-Pin<br>TQFP/QFN            | 100-Pin<br>TQFP | 121-Pin<br>BGA | I/O | Buffer | Description                                                           |

| AN0      | 16                            | 25              | K2             | 1   | ANA    |                                                                       |

| AN1      | 15                            | 24              | K1             | I   | ANA    |                                                                       |

| AN2      | 14                            | 23              | J2             | I   | ANA    |                                                                       |

| AN3      | 13                            | 22              | J1             | Ι   | ANA    |                                                                       |

| AN4      | 12                            | 21              | H2             | I   | ANA    |                                                                       |

| AN5      | 11                            | 20              | H1             | I   | ANA    |                                                                       |

| AN6      | 17                            | 26              | L1             | I   | ANA    |                                                                       |

| AN7      | 18                            | 27              | J3             | Ι   | ANA    |                                                                       |

| AN8      | 21                            | 32              | K4             | Ι   | ANA    |                                                                       |

| AN9      | 22                            | 33              | L4             | Ι   | ANA    |                                                                       |

| AN10     | 23                            | 34              | L5             | I   | ANA    |                                                                       |

| AN11     | 24                            | 35              | J5             | I   | ANA    |                                                                       |

| AN12     | 27                            | 41              | J7             | I   | ANA    | A/D Analog Inputs.                                                    |

| AN13     | 28                            | 42              | L7             | I   | ANA    |                                                                       |

| AN14     | 29                            | 43              | K7             | I   | ANA    |                                                                       |

| AN15     | 30                            | 44              | L8             | I   | ANA    |                                                                       |

| AN16     | _                             | 9               | E1             | I   | ANA    |                                                                       |

| AN17     | _                             | 10              | E3             | I   | ANA    |                                                                       |

| AN18     | —                             | 11              | F4             | Ι   | ANA    |                                                                       |

| AN19     | —                             | 12              | F2             | I   | ANA    |                                                                       |

| AN20     | —                             | 14              | F3             | Ι   | ANA    |                                                                       |

| AN21     | —                             | 19              | G2             | I   | ANA    |                                                                       |

| AN22     | —                             | 92              | B5             | Ι   | ANA    |                                                                       |

| AN23     | —                             | 91              | C5             | Ι   | ANA    |                                                                       |

| AVdd     | 19                            | 30              | J4             | Р   | —      | Positive Supply for Analog modules.                                   |

| AVss     | 20                            | 31              | L3             | Р   | _      | Ground Reference for Analog modules.                                  |

| C1INA    | 11                            | 20              | H1             | I   | ANA    | Comparator 1 Input A.                                                 |

| C1INB    | 12                            | 21              | H2             | I   | ANA    | Comparator 1 Input B.                                                 |

| C1INC    | 5                             | 11              | F4             | I   | ANA    | Comparator 1 Input C.                                                 |

| C1IND    | 4                             | 10              | E3             | Ι   | ANA    | Comparator 1 Input D.                                                 |

| C2INA    | 13                            | 22              | J1             | I   | ANA    | Comparator 2 Input A.                                                 |

| C2INB    | 14                            | 23              | J2             | I   | ANA    | Comparator 2 Input B.                                                 |

| C2INC    | 8                             | 14              | F3             | I   | ANA    | Comparator 2 Input C.                                                 |

| C2IND    | 6                             | 12              | F2             | Ι   | ANA    | Comparator 2 Input D.                                                 |

| C3INA    | 55                            | 84              | C7             | I   | ANA    | Comparator 3 Input A.                                                 |

| C3INB    | 54                            | 83              | D7             | I   | ANA    | Comparator 3 Input B.                                                 |

| C3INC    | 48                            | 74              | B11            | I   | ANA    | Comparator 3 Input C.                                                 |

| C3IND    | 47                            | 73              | C10            | I   | ANA    | Comparator 3 Input D.                                                 |

| CLKI     | 39                            | 63              | F9             | I   | ST     | Main Clock Input Connection.                                          |

| CLKO     | 40                            | 64              | F11            | 0   |        | System Clock Output.                                                  |

| -        | TTL = TTL inp<br>ANA = Analog |                 | put            |     |        | Schmitt Trigger input buffer<br>= I <sup>2</sup> C/SMBus input buffer |

#### **TABLE 1-3**: PIC24FJ256GB210 FAMILY PINOUT DESCRIPTIONS

2: The PMSC2 signal will replace the PMA15 signal on the 15-pin PMA when CSF<1:0> = 01 or 10.

3: The PMCS1 signal will replace the PMA14 signal on the 14-pin PMA when CSF<1:0> = 10.

4: The alternate VREF pins selected when the ALTVREF (CW1<5>) bit is programmed to '0'.

### 2.7 Configuration of Analog and Digital Pins During ICSP Operations

If an ICSP compliant emulator is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins. Depending on the particular device, this is done by clearing all bit in the ANSx registers.

All PIC24FJ devices will have several ANSx registers (one for each port). Refer to (**Section 10.0 "I/O Ports**") for more specific information.

The bits in these registers that correspond to the A/D pins that initialized the emulator must not be changed by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must modify the appropriate bits during initialization of the ADC module, as follows:

• Set the bits corresponding to the pin(s) to be configured as analog. Do not change any other bits, particularly those corresponding to the PGECx/PGEDx pair, at any time.

When a Microchip debugger/emulator is used as a programmer, the user application firmware must correctly configure the ANSx registers. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

### 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

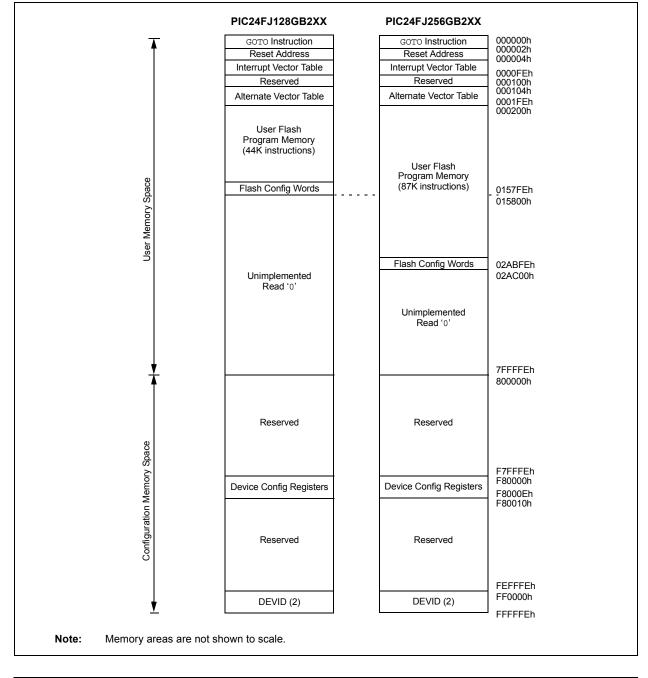

### 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, PIC24F microcontrollers feature separate program and data memory spaces and busses. This architecture also allows direct access of program memory from the data space during code execution.

#### 4.1 **Program Memory Space**

The program address memory space of the PIC24FJ256GB210 family devices is 4M instructions. The space is addressable by a 24-bit value derived

from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24FJ256GB210 family of devices are shown in Figure 4-1.

#### FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24FJ256GB210 FAMILY DEVICES

| TABLE     | 4-6: | INT    | ERRUP   | т солт  | ROLLE   | R REG  | ISTER N  | IAP      |          |        |          |          |          |         |               |               |          |               |

|-----------|------|--------|---------|---------|---------|--------|----------|----------|----------|--------|----------|----------|----------|---------|---------------|---------------|----------|---------------|

| File Name | Addr | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10   | Bit 9    | Bit 8    | Bit 7  | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2         | Bit 1         | Bit 0    | All<br>Resets |

| INTCON1   | 0080 | NSTDIS | _       | _       | _       | _      | _        | _        | -        | _      | _        | _        | MATHERR  | ADDRERR | STKERR        | OSCFAIL       | _        | 0000          |

| INTCON2   | 0082 | ALTIVT | DISI    | _       | —       | _      | _        | _        | _        | _      | _        | —        | INT4EP   | INT3EP  | INT2EP        | INT1EP        | INT0EP   | 0000          |

| IFS0      | 0084 | _      | _       | AD1IF   | U1TXIF  | U1RXIF | SPI1IF   | SPF1IF   | T3IF     | T2IF   | OC2IF    | IC2IF    | _        | T1IF    | OC1IF         | IC1IF         | INTOIF   | 0000          |

| IFS1      | 0086 | U2TXIF | U2RXIF  | INT2IF  | T5IF    | T4IF   | OC4IF    | OC3IF    | _        | IC8IF  | IC7IF    | _        | INT1IF   | CNIF    | CMIF          | MI2C1IF       | SI2C1IF  | 0000          |

| IFS2      | 8800 |        | _       | PMPIF   | OC8IF   | OC7IF  | OC6IF    | OC5IF    | IC6IF    | IC5IF  | IC4IF    | IC3IF    | _        | _       | _             | SPI2IF        | SPF2IF   | 0000          |

| IFS3      | 008A | _      | RTCIF   | _       | —       | _      | _        | _        | _        | _      | INT4IF   | INT3IF   | _        | —       | MI2C2IF       | SI2C2IF       | _        | 0000          |

| IFS4      | 008C | -      | _       | CTMUIF  | _       | _      | _        | _        | LVDIF    | _      | _        | _        | _        | CRCIF   | U2ERIF        | U1ERIF        | _        | 0000          |

| IFS5      | 008E |        | _       | IC9IF   | OC9IF   | SPI3IF | SPF3IF   | U4TXIF   | U4RXIF   | U4ERIF | USB1IF   | MI2C3IF  | SI2C3IF  | U3TXIF  | <b>U3RXIF</b> | <b>U3ERIF</b> | _        | 0000          |

| IEC0      | 0094 | _      |         | AD1IE   | U1TXIE  | U1RXIE | SPI1IE   | SPF1IE   | T3IE     | T2IE   | OC2IE    | IC2IE    | _        | T1IE    | OC1IE         | IC1IE         | INT0IE   | 0000          |

| IEC1      | 0096 | U2TXIE | U2RXIE  | INT2IE  | T5IE    | T4IE   | OC4IE    | OC3IE    | -        | IC8IE  | IC7IE    | —        | INT1IE   | CNIE    | CMIE          | MI2C1IE       | SI2C1IE  | 0000          |

| IEC2      | 0098 |        | _       | PMPIE   | OC8IE   | OC7IE  | OC6IE    | OC5IE    | IC6IE    | IC5IE  | IC4IE    | IC3IE    | _        | _       | _             | SPI2IE        | SPF2IE   | 0000          |

| IEC3      | 009A | _      | RTCIE   | _       | —       |        | _        | -        | _        | _      | INT4IE   | INT3IE   | _        | —       | MI2C2IE       | SI2C2IE       | _        | 0000          |

| IEC4      | 009C | -      | _       | CTMUIE  | _       | -      | _        | _        | LVDIE    | _      | _        | _        | _        | CRCIE   | U2ERIE        | U1ERIE        | _        | 0000          |

| IEC5      | 009E |        | _       | IC9IE   | OC9IE   | SPI3IE | SPF3IE   | U4TXIE   | U4RXIE   | U4ERIE | USB1IE   | MI2C3IE  | SI2C3IE  | U3TXIE  | <b>U3RXIE</b> | <b>U3ERIE</b> | _        | 0000          |

| IPC0      | 00A4 | _      | T1IP2   | T1IP1   | T1IP0   |        | OC1IP2   | OC1IP1   | OC1IP0   | _      | IC1IP2   | IC1IP1   | IC1IP0   | —       | INT0IP2       | INT0IP1       | INT0IP0  | 4444          |

| IPC1      | 00A6 | -      | T2IP2   | T2IP1   | T2IP0   |        | OC2IP2   | OC2IP1   | OC2IP0   | —      | IC2IP2   | IC2IP1   | IC2IP0   | —       | _             | _             | _        | 4440          |

| IPC2      | 00A8 |        | U1RXIP2 | U1RXIP1 | U1RXIP0 | _      | SPI1IP2  | SPI1IP1  | SPI1IP0  | _      | SPF1IP2  | SPF1IP1  | SPF1IP0  | _       | T3IP2         | T3IP1         | T3IP0    | 4444          |

| IPC3      | 00AA | _      |         | _       | —       |        | _        | -        | _        | _      | AD1IP2   | AD1IP1   | AD1IP0   | —       | U1TXIP2       | U1TXIP1       | U1TXIP0  | 0044          |

| IPC4      | 00AC | -      | CNIP2   | CNIP1   | CNIP0   | -      | CMIP2    | CMIP1    | CMIP0    | _      | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | —       | SI2C1IP2      | SI2C1IP1      | SI2C1IP0 | 4444          |

| IPC5      | 00AE |        | IC8IP2  | IC8IP1  | IC8IP0  | -      | IC7IP2   | IC7IP1   | IC7IP0   | —      | —        | —        | —        | —       | INT1IP2       | INT1IP1       | INT1IP0  | 4404          |

| IPC6      | 00B0 | _      | T4IP2   | T4IP1   | T4IP0   |        | OC4IP2   | OC4IP1   | OC4IP0   | —      | OC3IP2   | OC3IP1   | OC3IP0   | —       | —             | —             | —        | 4440          |

| IPC7      | 00B2 | -      | U2TXIP2 | U2TXIP1 | U2TXIP0 |        | U2RXIP2  | U2RXIP1  | U2RXIP0  | —      | INT2IP2  | INT2IP1  | INT2IP0  | —       | T5IP2         | T5IP1         | T5IP0    | 4444          |

| IPC8      | 00B4 |        | -       | —       | —       | -      | -        | -        | -        | —      | SPI2IP2  | SPI2IP1  | SPI2IP0  | —       | SPF2IP2       | SPF2IP1       | SPF2IP0  | 0044          |

| IPC9      | 00B6 | _      | IC5IP2  | IC5IP1  | IC5IP0  |        | IC4IP2   | IC4IP1   | IC4IP0   | _      | IC3IP2   | IC3IP1   | IC3IP0   | —       | _             | _             | _        | 4440          |

| IPC10     | 00B8 | _      | OC7IP2  | OC7IP1  | OC7IP0  |        | OC6IP2   | OC6IP1   | OC6IP0   | _      | OC5IP2   | OC5IP1   | OC5IP0   | _       | IC6IP2        | IC6IP1        | IC6IP0   | 4444          |

| IPC11     | 00BA | _      | _       | —       | —       | _      | _        | _        | _        | —      | PMPIP2   | PMPIP1   | PMPIP0   | _       | OC8IP2        | OC8IP1        | OC8IP0   | 0044          |

| IPC12     | 00BC | _      | _       | _       | _       | _      | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 | _      | SI2C2IP2 | SI2C2IP1 | SI2C2IP0 | _       |               | _             |          | 0440          |

| IPC13     | 00BE | _      | _       | _       | —       | _      | INT4IP2  | INT4IP1  | INT4IP0  | _      | INT3IP2  | INT3IP1  | INT3IP0  | _       | _             | _             | _        | 0440          |

| IPC15     | 00C2 | _      | _       | —       | _       | _      | RTCIP2   | RTCIP1   | RTCIP0   | —      | _        | _        | _        | _       | _             | _             | _        | 0400          |

DS39975A-page 50

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-18: PORTF REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 <sup>(1)</sup> | Bit 12 <sup>(1)</sup> | Bit 11 | Bit 10 | Bit 9 | Bit 8 <sup>(1)</sup> | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2 <sup>(1)</sup> | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|-----------------------|-----------------------|--------|--------|-------|----------------------|--------|-------|--------|--------|--------|----------------------|--------|--------|---------------|

| TRISF        | 02E8 | _      |        | TRISF13               | TRISF12               | _      | _      | _     | TRISF8               | TRISF7 |       | TRISF5 | TRISF4 | TRISF3 | TRISF2               | TRISF1 | TRISF0 | 31BF          |

| PORTF        | 02EA | _      | _      | RF13                  | RF12                  |        | _      | _     | RF8                  | RF7    | _     | RF5    | RF4    | RF3    | RF2                  | RF1    | RF0    | xxxx          |

| LATF         | 02EC | -      |        | LATF13                | LATF12                | -      | -      |       | LATF8                | LATF7  |       | LATF5  | LATF4  | LATF3  | LATF2                | LATF1  | LATF0  | xxxx          |

| ODCF         | 02EE | —      | _      | ODF13                 | ODF12                 | _      | _      | _     | ODF8                 | ODF7   | _     | ODF5   | ODF4   | ODF3   | ODF2                 | ODF1   | ODF0   | 0000          |

Legend:

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Reset values shown are for 100-pin devices.

Note

1:

Bits are unimplemented in 64-pin devices; read as '0'.

#### TABLE 4-19: PORTG REGISTER MAP

| File<br>Name | Addr | Bit 15 <sup>(1)</sup> | Bit 14 <sup>(1)</sup> | Bit 13 <sup>(1)</sup> | Bit 12 <sup>(1)</sup> | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 <sup>(1)</sup> | Bit 0 <sup>(1)</sup> | All<br>Resets |

|--------------|------|-----------------------|-----------------------|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|----------------------|----------------------|---------------|

| TRISG        | 02F0 | TRISG15               | TRISG14               | TRISG13               | TRISG12               | _      | _      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _     | _     | TRISG3 | TRISG2 | TRISG1               | TRISG0               | F3CF          |

| PORTG        | 02F2 | RG15                  | RG14                  | RG13                  | RG12                  | _      | _      | RG9    | RG8    | RG7    | RG6    | _     | _     | RG3    | RG2    | RG1                  | RG0                  | xxxx          |

| LATG         | 02F4 | LATG15                | LATG14                | LATG13                | LATG12                | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | LATG3  | LATG2  | LATG1                | LATG0                | xxxx          |

| ODCG         | 02F6 | ODG15                 | ODG14                 | ODG13                 | ODG12                 |        | _      | ODG9   | ODG8   | ODG7   | ODG6   | _     | _     | ODG3   | ODG2   | ODG1                 | ODG0                 | 0000          |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Reset values shown are for 100-pin devices. Legend:

Bits are unimplemented in 64-pin devices; read as '0'. Note 1:

#### TABLE 4-20: PAD CONFIGURATION REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------|--------|---------------|

| PADCFG       | 02FC | _      | _      |        | _      |        |        |       | _     |       | _     | _     |       |       |       | RTSECSEL | PMPTTL | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|                     | R/W-1                                                                                                          | R/W-0                                                                                                                                                            | R/W-0                                                                                                   | U-0                | R/W-1           | R/W-0           | R/W-0   |

|---------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------|-----------------|-----------------|---------|

| —                   | IC8IP2                                                                                                         | IC8IP1                                                                                                                                                           | IC8IP0                                                                                                  |                    | IC7IP2          | IC7IP1          | IC7IP0  |

| bit 15              | ·                                                                                                              |                                                                                                                                                                  |                                                                                                         | ·                  | ·               | ·               | bit     |

| U-0                 | U-0                                                                                                            | U-0                                                                                                                                                              | U-0                                                                                                     | U-0                | R/W-1           | R/W-0           | R/W-0   |

|                     | _                                                                                                              | _                                                                                                                                                                |                                                                                                         | _                  | INT1IP2         | INT1IP1         | INT1IP0 |

| bit 7               |                                                                                                                |                                                                                                                                                                  | •                                                                                                       |                    |                 |                 | bit     |

| Legend:             |                                                                                                                |                                                                                                                                                                  |                                                                                                         |                    |                 |                 |         |

| R = Readat          | ole bit                                                                                                        | W = Writable                                                                                                                                                     | bit                                                                                                     | U = Unimpler       | mented bit, rea | d as '0'        |         |

| -n = Value a        | at POR                                                                                                         | '1' = Bit is set                                                                                                                                                 |                                                                                                         | '0' = Bit is cle   | ared            | x = Bit is unkr | nown    |

| bit 15              | Unimploment                                                                                                    |                                                                                                                                                                  | o'                                                                                                      |                    |                 |                 |         |

| bit 15              | -                                                                                                              | ited: Read as '                                                                                                                                                  |                                                                                                         |                    |                 |                 |         |

| bit 14-12           |                                                                                                                |                                                                                                                                                                  |                                                                                                         | rrupt Priority bit | S               |                 |         |

|                     |                                                                                                                | pt is priority 7 (                                                                                                                                               | nignest priorit                                                                                         | y interrupt)       |                 |                 |         |

|                     | •                                                                                                              |                                                                                                                                                                  |                                                                                                         |                    |                 |                 |         |

|                     | •                                                                                                              |                                                                                                                                                                  |                                                                                                         |                    |                 |                 |         |

|                     |                                                                                                                | pt is priority 1                                                                                                                                                 | ablad                                                                                                   |                    |                 |                 |         |

|                     | 000 = Interful                                                                                                 | pt source is dis                                                                                                                                                 | aoleo                                                                                                   |                    |                 |                 |         |

| L:1 1 1             |                                                                                                                | -                                                                                                                                                                |                                                                                                         |                    |                 |                 |         |

| bit 11              | -                                                                                                              | ted: Read as '                                                                                                                                                   | 0'                                                                                                      |                    |                 |                 |         |

| bit 11<br>bit 10-8  | IC7IP<2:0>:                                                                                                    | ited: Read as '<br>Input Capture C                                                                                                                               | <sup>0'</sup><br>Channel 7 Inte                                                                         | rrupt Priority bit | S               |                 |         |

|                     | IC7IP<2:0>:                                                                                                    | ted: Read as '                                                                                                                                                   | <sup>0'</sup><br>Channel 7 Inte                                                                         |                    | S               |                 |         |

|                     | IC7IP<2:0>:                                                                                                    | ited: Read as '<br>Input Capture C                                                                                                                               | <sup>0'</sup><br>Channel 7 Inte                                                                         |                    | S               |                 |         |

|                     | IC7IP<2:0>:  <br>111 = Interru                                                                                 | ited: Read as f<br>Input Capture C<br>Ipt is priority 7 (                                                                                                        | <sup>0'</sup><br>Channel 7 Inte                                                                         |                    | S               |                 |         |

|                     | IC7IP<2:0>: 1<br>111 = Interru<br>001 = Interru                                                                | Input Capture C<br>Input Capture C<br>Inpt is priority 7 (<br>Inpt is priority 1                                                                                 | <sup>0'</sup><br>Channel 7 Inte<br>highest priorit                                                      |                    | S               |                 |         |

| bit 10-8            | IC7IP<2:0>: 1<br>111 = Interru                                                                                 | Inted: Read as f<br>Input Capture C<br>Inpt is priority 7 (<br>Inpt is priority 1<br>Inpt source is dis                                                          | <sup>0'</sup><br>Channel 7 Inte<br>highest priorit<br>sabled                                            |                    | S               |                 |         |

| bit 10-8<br>bit 7-3 | IC7IP<2:0>: 1<br>111 = Interru                                                                                 | Input Capture C<br>Input Capture C<br>Inpt is priority 7 (<br>Inpt is priority 1<br>Inpt source is dis<br>Inted: Read as f                                       | <sup>0'</sup><br>Channel 7 Inte<br>highest priorit<br>sabled<br>0'                                      | y interrupt)       | S               |                 |         |

|                     | IC7IP<2:0>: 1<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT1IP<2:0>                  | Input Capture C<br>Input Capture C<br>Input is priority 7 (<br>Input is priority 1<br>Input source is dis<br>Inted: Read as fi<br>External Intern                | <sup>0'</sup><br>Channel 7 Inte<br>highest priorit<br>sabled<br>0'<br>rupt 1 Priority                   | y interrupt)       | S               |                 |         |

| bit 10-8<br>bit 7-3 | IC7IP<2:0>: 1<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT1IP<2:0>                  | Input Capture C<br>Input Capture C<br>Inpt is priority 7 (<br>Inpt is priority 1<br>Inpt source is dis<br>Inted: Read as f                                       | <sup>0'</sup><br>Channel 7 Inte<br>highest priorit<br>sabled<br>0'<br>rupt 1 Priority                   | y interrupt)       | S               |                 |         |

| bit 10-8<br>bit 7-3 | IC7IP<2:0>: 1<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT1IP<2:0>                  | Input Capture C<br>Input Capture C<br>Input is priority 7 (<br>Input is priority 1<br>Input source is dis<br>Inted: Read as fi<br>External Intern                | <sup>0'</sup><br>Channel 7 Inte<br>highest priorit<br>sabled<br>0'<br>rupt 1 Priority                   | y interrupt)       | S               |                 |         |

| bit 10-8<br>bit 7-3 | IC7IP<2:0>: 1<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT1IP<2:0><br>111 = Interru | hted: Read as f<br>Input Capture C<br>opt is priority 7 (<br>opt is priority 1<br>opt source is dis<br>hted: Read as f<br>External Intern<br>opt is priority 7 ( | <sup>0'</sup><br>Channel 7 Inte<br>highest priorit<br>sabled<br>0'<br>rupt 1 Priority                   | y interrupt)       | S               |                 |         |

| bit 10-8<br>bit 7-3 | IC7IP<2:0>: 1<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT1IP<2:0><br>111 = Interru | Input Capture C<br>Input Capture C<br>Input is priority 7 (<br>Input is priority 1<br>Input source is dis<br>Inted: Read as fi<br>External Intern                | <sup>0'</sup><br>Channel 7 Inte<br>highest priorit<br>sabled<br>0'<br>upt 1 Priority<br>highest priorit | y interrupt)       | S               |                 |         |

#### REGISTER 7-22: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

| U-0          | R/W-1                     | R/W-0                                | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |

|--------------|---------------------------|--------------------------------------|------------------|------------------|------------------|-----------------|---------|

| _            | U2TXIP2                   | U2TXIP1                              | U2TXIP0          |                  | U2RXIP2          | U2RXIP1         | U2RXIP0 |

| bit 15       |                           |                                      |                  |                  |                  |                 | bit     |

|              |                           |                                      |                  |                  |                  |                 |         |

| U-0          | R/W-1                     | R/W-0                                | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |

| —            | INT2IP2                   | INT2IP1                              | INT2IP0          | —                | T5IP2            | T5IP1           | T5IP0   |

| bit 7        |                           |                                      |                  |                  |                  |                 | bit     |

| Legend:      |                           |                                      |                  |                  |                  |                 |         |

| R = Readab   | ole bit                   | W = Writable                         | bit              | U = Unimple      | mented bit, read | d as '0'        |         |

| -n = Value a | at POR                    | '1' = Bit is set                     |                  | '0' = Bit is cle | eared            | x = Bit is unkr | nown    |

|              |                           |                                      |                  |                  |                  |                 |         |

| bit 15       | Unimplemen                | ted: Read as '                       | כ'               |                  |                  |                 |         |

| bit 14-12    | U2TXIP<2:0>               | : UART2 Trans                        | smitter Interrup | ot Priority bits |                  |                 |         |

|              | 111 = Interru             | pt is priority 7 (                   | highest priority | / interrupt)     |                  |                 |         |

|              | •                         |                                      |                  |                  |                  |                 |         |

|              | •                         |                                      |                  |                  |                  |                 |         |

|              | 001 = Interru             |                                      |                  |                  |                  |                 |         |

|              |                           | pt source is dis                     |                  |                  |                  |                 |         |

| bit 11       | -                         | ted: Read as '                       |                  |                  |                  |                 |         |

| bit 10-8     |                           | : UART2 Rece                         |                  | -                |                  |                 |         |

|              | 111 = Interru             | pt is priority 7 (                   | nignest priority | / interrupt)     |                  |                 |         |

|              | •                         |                                      |                  |                  |                  |                 |         |

|              | •<br>001 = Interru        | nt in priority 1                     |                  |                  |                  |                 |         |

|              |                           | pt is priority i<br>pt source is dis | abled            |                  |                  |                 |         |

| bit 7        |                           | ted: Read as '                       |                  |                  |                  |                 |         |

| bit 6-4      | -                         | External Interr                      |                  | oits             |                  |                 |         |

|              |                           | pt is priority 7 (                   |                  |                  |                  |                 |         |

|              | •                         |                                      | 0 1 2            |                  |                  |                 |         |

|              | •                         |                                      |                  |                  |                  |                 |         |

|              | 001 = Interru             | pt is priority 1                     |                  |                  |                  |                 |         |

|              | 000 = Interru             | pt source is dis                     | abled            |                  |                  |                 |         |

| bit 3        | Unimplemen                | ted: Read as '                       | כי               |                  |                  |                 |         |

| bit 2-0      | <b>T5IP&lt;2:0&gt;:</b> ⊺ | imer5 Interrupt                      | Priority bits    |                  |                  |                 |         |

|              | 111 = Interru             | pt is priority 7 (                   | highest priority | / interrupt)     |                  |                 |         |

|              | •                         |                                      |                  |                  |                  |                 |         |

|              | •                         |                                      |                  |                  |                  |                 |         |

|              | 001 = Interru             |                                      | م ام ا م         |                  |                  |                 |         |

|              | 000 = Interru             | pt source is dis                     | apled            |                  |                  |                 |         |

#### REGISTER 7-24: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

NOTES:

#### 10.4.5 CONSIDERATIONS FOR PERIPHERAL PIN SELECTION

The ability to control Peripheral Pin Selection introduces several considerations into application design that could be overlooked. This is particularly true for several common peripherals that are available only as remappable peripherals.

The main consideration is that the Peripheral Pin Selects are not available on default pins in the device's default (Reset) state. Since all RPINRx registers reset to '111111' and all RPORx registers reset to '000000', all Peripheral Pin Select inputs are tied to Vss and all Peripheral Pin Select outputs are disconnected.

| Note: | In tying Peripheral Pin Select inputs to  |

|-------|-------------------------------------------|

|       | RP63, RP63 need not exist on a device for |

|       | the registers to be reset to it.          |

This situation requires the user to initialize the device with the proper peripheral configuration before any other application code is executed. Since the IOLOCK bit resets in the unlocked state, it is not necessary to execute the unlock sequence after the device has come out of Reset. For application safety, however, it is best to set IOLOCK and lock the configuration after writing to the control registers.

Because the unlock sequence is timing-critical, it must be executed as an assembly language routine in the same manner as changes to the oscillator configuration. If the bulk of the application is written in 'C', or another high-level language, the unlock sequence should be performed by writing in-line assembly.

Choosing the configuration requires the review of all Peripheral Pin Selects and their pin assignments, especially those that will not be used in the application. In all cases, unused pin-selectable peripherals should be disabled completely. Unused peripherals should have their inputs assigned to an unused RPn/RPIn pin function. I/O pins with unused RPn functions should be configured with the null peripheral output.

The assignment of a peripheral to a particular pin does not automatically perform any other configuration of the pin's I/O circuitry. In theory, this means adding a pin-selectable output to a pin may mean inadvertently driving an existing peripheral input when the output is driven. Users must be familiar with the behavior of other fixed peripherals that share a remappable pin and know when to enable or disable them. To be safe, fixed digital peripherals that share the same pin should be disabled when not in use. Along these lines, configuring a remappable pin for a specific peripheral does not automatically turn that feature on. The peripheral must be specifically configured for operation, and enabled as if it were tied to a fixed pin. Where this happens in the application code (immediately following device Reset and peripheral configuration or inside the main application routine) depends on the peripheral and its use in the application.

A final consideration is that Peripheral Pin Select functions neither override analog inputs nor reconfigure pins with analog functions for digital I/O. If a pin is configured as an analog input on device Reset, it must be explicitly reconfigured as digital I/O when used with a Peripheral Pin Select.

Example 10-3 shows a configuration for bidirectional communication with flow control using UART1. The following input and output functions are used:

- Input Functions: U1RX, U1CTS

- Output Functions: U1TX, U1RTS

#### EXAMPLE 10-3: CONFIGURING UART1 INPUT AND OUTPUT FUNCTIONS

| // Unlock Regis            | sters    |                    |         |

|----------------------------|----------|--------------------|---------|

| asm volatile(              | "MOV     | #OSCCON, w1        | \n"     |

|                            | "MOV     | #0x46, w2          | \n"     |

|                            | "MOV     | #0x57, w3          | \n"     |

|                            | "MOV.b   | w2, [w1]           | \n"     |

|                            | "MOV.b   | w3, [w1]           | \n"     |

|                            | "BCLR (  | ) SCCON , #6 " ) ; |         |

|                            |          |                    |         |

| // or use C30 k            | ouilt-ir | n macro:           |         |

| // _builtin_wri            | ite_OSCO | CONL (OSCCON &     | 0xbf);  |

| // Configure Ir            | nput Fur | nctions (Table     |         |

| Table 10-2))               |          |                    |         |

| // Assign U                | JRX To   | Pin RPO            |         |

| RPINR18bits                | .Ulrxr   | = 0 <i>i</i>       |         |

|                            |          |                    |         |

| // Assign U                |          |                    |         |

| RPINR18bits                | .U1CTSR  | = 1;               |         |

|                            |          |                    |         |

| // Configure Ou            | -        |                    | ≥ 10-4) |

| // Assign U<br>RPOR1bits.R |          |                    |         |

| RPORIDIUS.R                | PZR = 3  | 1                  |         |

| // Assign U                | יוסדפ דה | Din D2             |         |

| RPOR1bits.R                |          |                    |         |

| 111 011101105.11           |          |                    |         |

| // Lock Registe            | ers      |                    |         |

| asm volatile               |          | #OSCCON, w1        | \n"     |

|                            |          | #0x46, w2          | \n"     |

|                            |          |                    | \n"     |

|                            | "MOV.b   | w2, [w1]\          | n"      |

|                            | "MOV.b   | w3, [w1]           | \n"     |

|                            | "BSET    | OSCCON, #6")       | ;       |

| // or use C30 k            | ouilt-ir | n macro:           |         |

| // _builtin_wri            | ite_OSCO | CONL (OSCCON       | 0x40);  |

| 1                          |          |                    |         |

NOTES:

| R/W-0          | U-0                                                                                  | R/W-0                                                                                              | R/W-1, HC                                           | R/W-0                             | R/W-0             | R/W-0                    | R/W-0          |

|----------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------|-------------------|--------------------------|----------------|

| I2CEN          | —                                                                                    | I2CSIDL                                                                                            | SCLREL                                              | IPMIEN                            | A10M              | DISSLW                   | SMEN           |

| bit 15         |                                                                                      |                                                                                                    |                                                     |                                   |                   |                          | bit 8          |

| R/W-0          | R/W-0                                                                                | R/W-0                                                                                              | R/W-0, HC                                           | R/W-0, HC                         | R/W-0, HC         | R/W-0, HC                | R/W-0, HC      |

| GCEN           | STREN                                                                                | ACKDT                                                                                              | ACKEN                                               | RCEN                              | PEN               | RSEN                     | SEN            |

| bit 7          |                                                                                      |                                                                                                    |                                                     |                                   |                   |                          | bit            |

| Legend:        |                                                                                      | HC = Hardwa                                                                                        | are Clearable bit                                   | t                                 |                   |                          |                |

| R = Readab     | le bit                                                                               | W = Writable                                                                                       | bit                                                 | U = Unimplem                      | nented bit, read  | l as '0'                 |                |

| -n = Value a   | t POR                                                                                | '1' = Bit is se                                                                                    | t                                                   | '0' = Bit is clea                 | ared              | x = Bit is unkn          | iown           |

| bit 15         | 12CEN: 12Cx                                                                          | Enable bit                                                                                         |                                                     |                                   |                   |                          |                |

|                | 1 = Enables<br>0 = Disables                                                          | the I2Cx modu                                                                                      | lle and configure<br>ule; all l <sup>2</sup> C™ pin | es the SDAx ar                    | nd SCLx pins a    | s serial port pir<br>ons | IS             |

| bit 14         |                                                                                      | ited: Read as                                                                                      | -                                                   |                                   | a a) por ranea    |                          |                |

| bit 13         | -                                                                                    | p in Idle Mode                                                                                     |                                                     |                                   |                   |                          |                |

|                |                                                                                      |                                                                                                    | peration when d                                     |                                   | n Idle mode       |                          |                |

|                |                                                                                      |                                                                                                    | ation in Idle mo                                    |                                   | <b>_</b>          |                          |                |

| bit 12         |                                                                                      |                                                                                                    | ontrol bit (when                                    | operating as I <sup>2</sup>       | C slave)          |                          |                |

|                | 1 = Releases<br>0 = Holds S0                                                         | SCLX CIOCK                                                                                         | clock stretch)                                      |                                   |                   |                          |                |

|                | If STREN = 1                                                                         |                                                                                                    |                                                     |                                   |                   |                          |                |

|                | •                                                                                    |                                                                                                    | y write '0' to initi                                |                                   |                   | ,                        | dware is clea  |

|                | If STREN = 0                                                                         | -                                                                                                  | nsmission. Hard                                     | iware is clear a                  | at the end of sid | ave reception.           |                |

|                |                                                                                      | ., software may                                                                                    | only write '1' to                                   | release clock)                    | . Hardware is c   | lear at the begi         | inning of slav |

| bit 11         | IPMIEN: Intel                                                                        | lligent Platform                                                                                   | Management Ir                                       | nterface (IPMI)                   | Enable bit        |                          |                |

|                |                                                                                      | oport mode is e<br>de is disabled                                                                  | enabled; all addr                                   | esses are Ack                     | nowledged         |                          |                |

| bit 10         | A10M: 10-Bit                                                                         | Slave Addres                                                                                       | sing bit                                            |                                   |                   |                          |                |

|                |                                                                                      | ) is a 10-bit sla                                                                                  |                                                     |                                   |                   |                          |                |

| 1.11.0         |                                                                                      | ) is a 7-bit slav                                                                                  |                                                     |                                   |                   |                          |                |

| bit 9          |                                                                                      | able Slew Rate<br>e control is disa                                                                |                                                     |                                   |                   |                          |                |

|                |                                                                                      | e control is ena                                                                                   |                                                     |                                   |                   |                          |                |

|                | SMEN: SMB                                                                            | us Input Levels                                                                                    | bit                                                 |                                   |                   |                          |                |

| bit 8          |                                                                                      |                                                                                                    | olds compliant w                                    | ith SMBus spe                     | cifications       |                          |                |

| DIT 8          | 0 = Disables                                                                         | the SMRus in                                                                                       | out thresholds                                      |                                   |                   |                          |                |

|                |                                                                                      | -                                                                                                  |                                                     | ?                                 |                   |                          |                |

| bit 8<br>bit 7 | GCEN: Gene                                                                           | eral Call Enable                                                                                   | bit (when operational colling                       | -                                 |                   | vDSD (modulo             | is eachlad fo  |

|                | GCEN: Gene                                                                           | eral Call Enable<br>interrupt when                                                                 | e bit (when opera<br>a general call a               | -                                 |                   | xRSR (module             | is enabled fo  |

|                | GCEN: Gene<br>1 = Enables<br>receptior                                               | eral Call Enable<br>interrupt when                                                                 | a general call a                                    | -                                 |                   | xRSR (module             | is enabled fo  |

| bit 7          | GCEN: Gene<br>1 = Enables<br>receptior<br>0 = General                                | ral Call Enable<br>interrupt when<br>ו)<br>call address di                                         | a general call a                                    | address is rece                   | ived in the I2C   | xRSR (module             | is enabled fo  |

|                | GCEN: Gene<br>1 = Enables<br>reception<br>0 = General<br>STREN: SCL<br>Used in conju | eral Call Enable<br>interrupt when<br>n)<br>call address di<br>x Clock Stretcl<br>unction with the | a general call a<br>sabled<br>n Enable bit (wh      | address is rece<br>en operating a | ived in the I2C   | xRSR (module             | is enabled f   |

| REGISTER 18           | 8-9: U1AD | DR: USB AD       | DRESS REG | GISTER            |                  |                 |       |

|-----------------------|-----------|------------------|-----------|-------------------|------------------|-----------------|-------|

| U-0                   | U-0       | U-0              | U-0       | U-0               | U-0              | U-0             | U-0   |

| —                     | _         | —                | —         | —                 |                  |                 | _     |

| bit 15                |           |                  |           |                   |                  |                 | bit 8 |

|                       |           |                  |           |                   |                  |                 |       |

| R/W-0                 | R/W-0     | R/W-0            | R/W-0     | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| LSPDEN <sup>(1)</sup> | ADDR6     | ADDR5            | ADDR4     | ADDR3             | ADDR2            | ADDR1           | ADDR0 |

| bit 7                 |           |                  |           |                   |                  |                 | bit   |

|                       |           |                  |           |                   |                  |                 |       |

| Legend:               |           |                  |           |                   |                  |                 |       |

| R = Readable          | bit       | W = Writable     | bit       | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P       | OR        | '1' = Bit is set |           | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

| bit 15-8 | Unimplemented: Read as '0'                                                                           |

|----------|------------------------------------------------------------------------------------------------------|

| bit 7    | LSPDEN: Low-Speed Enable Indicator bit <sup>(1)</sup>                                                |

|          | <ul><li>1 = USB module operates at low speed</li><li>0 = USB module operates at full speed</li></ul> |

| bit 6-0  | ADDR<6:0>: USB Device Address bits                                                                   |

Note 1: Host mode only. In Device mode, this bit is unimplemented and read as '0'.

### REGISTER 18-10: U1TOK: USB TOKEN REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | —   | —   | _   | _   | _   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PID3  | PID2  | PID1  | PID0  | EP3   | EP2   | EP1   | EP0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-4PID<3:0>: Token Type Identifier bits1101 = SETUP (TX) token type transaction<sup>(1)</sup>1001 = IN (RX) token type transaction<sup>(1)</sup>0001 = OUT (TX) token type transaction<sup>(1)</sup>bit 3-0EP<3:0>: Token Command Endpoint Address bits

This value must specify a valid endpoint on the attached device.

Note 1: All other combinations are reserved and are not to be used.

### REGISTER 18-16: U1IR: USB INTERRUPT STATUS REGISTER (DEVICE MODE ONLY)

| U-0          | U-0                     | U-0                                      | U-0              | U-0                    | U-0                 | U-0                    | U-0              |

|--------------|-------------------------|------------------------------------------|------------------|------------------------|---------------------|------------------------|------------------|

| _            | _                       | —                                        | _                | —                      | _                   | —                      | _                |

| bit 15       |                         |                                          |                  |                        |                     |                        | bit 8            |

|              |                         |                                          |                  |                        |                     |                        |                  |

| R/K-0, HS    | U-0                     | R/K-0, HS                                | R/K-0, HS        | R/K-0, HS              | R/K-0, HS           | R-0                    | R/K-0, HS        |

| STALLIF      |                         | RESUMEIF                                 | IDLEIF           | TRNIF                  | SOFIF               | UERRIF                 | URSTIF           |

| bit 7        |                         |                                          |                  |                        |                     |                        | bit 0            |

|              |                         |                                          |                  |                        |                     |                        |                  |

| Legend:      |                         | U = Unimplem                             |                  |                        | 0 11 1 1 1          |                        |                  |

| R = Readab   |                         | K = Write '1' to                         | o clear bit      |                        | re Settable bit     | <b>D</b> <sup>11</sup> |                  |

| -n = Value a | t POR                   | '1' = Bit is set                         |                  | '0' = Bit is clea      | ared                | x = Bit is unkr        | iown             |

| bit 15-8     | Unimplome               | ented: Read as '0                        | ,'               |                        |                     |                        |                  |

| bit 7        | -                       | TALL Handshake                           |                  |                        |                     |                        |                  |

|              |                         | L handshake wa                           | •                | eripheral durin        | g the handshak      | e phase of the         | transaction in   |

|              | Device                  | mode                                     |                  | -                      | 0                   | ·                      |                  |

|              |                         | L handshake has                          |                  | t                      |                     |                        |                  |

| bit 6        | -                       | ented: Read as '0                        |                  |                        |                     |                        |                  |

| bit 5        |                         | : Resume Interru                         |                  |                        |                     |                        | · · · · · ·      |

|              | 1 = A K-sta<br>full spe | ite is observed on<br>ed)                | the D+ or D- p   | bin for 2.5 $\mu$ s (d | ifferential '1' foi | r low speed, dif       | terential '0' to |

|              |                         | tate is observed                         |                  |                        |                     |                        |                  |

| bit 4        | IDLEIF: Idle            | e Detect Interrupt                       | bit              |                        |                     |                        |                  |

|              |                         | ndition is detected                      | •                | e state of 3 ms        | or more)            |                        |                  |

|              |                         | condition is dete                        |                  |                        |                     |                        |                  |

| bit 3        |                         | en Processing Co                         | •                | •                      |                     |                        |                  |

|              |                         | sing of the curren<br>sing of the curren |                  |                        |                     |                        |                  |

|              |                         | TAT (clearing this                       |                  |                        |                     | egister of load        |                  |

| bit 2        | SOFIF: Star             | rt-of-Frame Toker                        | n Interrupt bit  |                        | -                   |                        |                  |

|              | 1 = A Start-            | -of-Frame token is                       | s received by t  | he peripheral o        | r the Start-of-F    | rame threshold         | l is reached by  |

|              | the hos                 | •                                        |                  | 0                      |                     |                        |                  |

| L:1 4        |                         | rt-of-Frame token                        |                  |                        | ned                 |                        |                  |

| bit 1        |                         | SB Error Conditio                        | •                |                        | atataa anablad      | in the LI1EIE r        | ogiator oon oo   |

|              | this bit                | nasked error cond                        | IIIIOII HAS OCCU | freu, only error       | states enabled      |                        | egister can se   |

|              |                         | nasked error cond                        | dition has occu  | irred                  |                     |                        |                  |

| bit 0        | URSTIF: US              | SB Reset Interrup                        | ot bit           |                        |                     |                        |                  |

|              |                         | SB Reset has oc                          | curred for at le | east 2.5 μs; Re        | set state must l    | be cleared before      | ore this bit car |

|              | be reas                 | sserted<br>B Reset has occu              | rrod Individua   | hite can only          | be cleared by       | writing a '1' to t     | he hit position  |

|              |                         | of a word write of                       |                  |                        |                     |                        |                  |