Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 84                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 96K × 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                    |

| Data Converters            | A/D 24x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

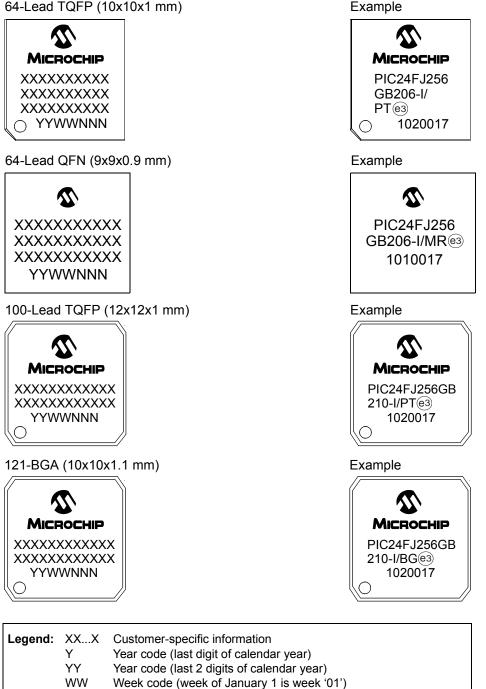

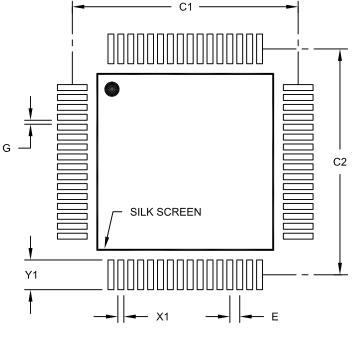

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb210-i-bg |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.2.6 SOFTWARE STACK

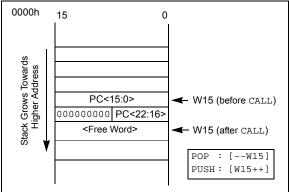

Apart from its use as a working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer (SSP). The pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-7. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL register to the |

|       | MSB of the PC prior to the push.         |

The Stack Pointer Limit Value register (SPLIM), associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 2000h in RAM, initialize the SPLIM with the value, 1FFEh.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the SFR space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

# 4.3 Interfacing Program and Data Memory Spaces

The PIC24F architecture uses a 24-bit wide program space and 16-bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the PIC24F architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (program space visibility)

Table instructions allow an application to read or write to small areas of the program memory. This makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. It can only access the least significant word of the program word.

### 4.3.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Memory Page Address register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the MSBs of TBLPAG are used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 10-bit Extended Data Space Read register (DSRPAG) is used to define a 16K word page in the program space. When the Most Significant bit (MSb) of the EA is '1', and the MSb (bit 9) of DSRPAG is '1', the lower 8 bits of DSRPAG are concatenated with the lower 15 bits of the EA to form a 23-bit program space address. The DSRPAG<8> bit decides whether the lower word (when bit is '0') or the higher word (when bit is '1') of program memory is mapped. Unlike table operations, this strictly limits remapping operations to the user memory area.

Table 4-35 and Figure 4-8 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

#### EXAMPLE 4-3: EDS READ CODE FROM PROGRAM MEMORY IN ASSEMBLY

```

; Set the EDS page from where the data to be read

#0x0202 , w0

mov

w0 , DSRPAG

;page 0x202, consisting lower words, is selected for read

mov

;select the location (0x0A) to be read

mov

#0x000A , w1

bset w1 , #15

;set the MSB of the base address, enable EDS mode

;Read a byte from the selected location

mov.b [w1++] , w2

mov.b [w1++] , w3

;read Low byte

;read High byte

;Read a word from the selected location

mov

[w1] , w2

;

;Read Double - word from the selected location

;two word read, stored in w2 and w3

mov.d [w1] , w2

```

# 6.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 7. "Reset" (DS39712). The information in this data sheet supersedes the information in the FRM.

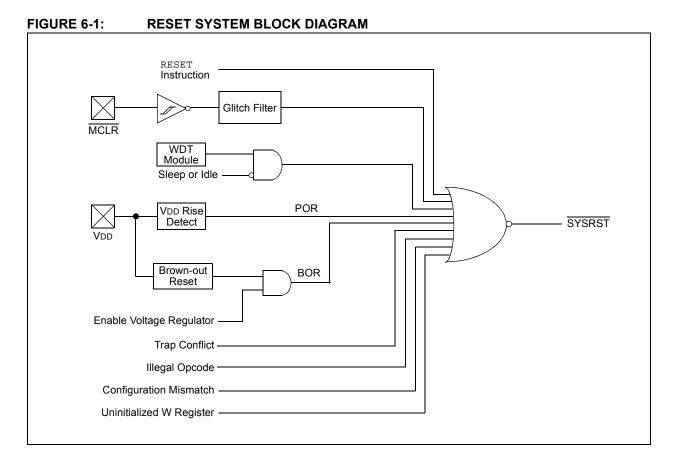

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Note: Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1). A POR will clear all bits, except for the BOR and POR (RCON<1:0>) bits, which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| U-0    | U-0 | R/W-0, HS |

|--------|-----|-----------|-----------|-----------|-----------|-----------|-----------|

| —      | —   | AD1IF     | U1TXIF    | U1RXIF    | SPI1IF    | SPF1IF    | T3IF      |

| bit 15 |     |           |           |           |           |           | bit 8     |

| R/W-0, HS | R/W-0, HS | R/W-0, HS | U-0 | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0, HS |

|-----------|-----------|-----------|-----|-----------|-----------|-----------|-----------|

| T2IF      | OC2IF     | IC2IF     | —   | T1IF      | OC1IF     | IC1IF     | INTOIF    |

| bit 7     |           |           |     |           |           |           | bit 0     |

| Legend:          |             | HS = Hardware Settabl                                            | e bit                    |                    |

|------------------|-------------|------------------------------------------------------------------|--------------------------|--------------------|

| R = Readable bit |             | W = Writable bit                                                 | U = Unimplemented bit,   | read as '0'        |

| -n = Value a     | at POR      | '1' = Bit is set                                                 | '0' = Bit is cleared     | x = Bit is unknown |

| bit 15-14        | Unimplem    | ented: Read as '0'                                               |                          |                    |

| bit 13           | •           | Conversion Complete Inte                                         | errupt Flag Status bit   |                    |

|                  |             | pt request has occurred                                          |                          |                    |

|                  | 0 = Interru | ipt request has not occurred                                     | b                        |                    |

| bit 12           | U1TXIF: U   | ART1 Transmitter Interrupt                                       | Flag Status bit          |                    |

|                  |             | pt request has occurred                                          |                          |                    |

|                  |             | pt request has not occurred                                      |                          |                    |

| bit 11           | U1RXIF: U   | IART1 Receiver Interrupt FI                                      | ag Status bit            |                    |

|                  |             | pt request has occurred                                          | 4                        |                    |

| L:1 4 0          |             | pt request has not occurred                                      |                          |                    |

| bit 10           |             | PI1 Event Interrupt Flag Stat                                    | tus dit                  |                    |

|                  |             | <pre>ipt request has occurred ipt request has not occurred</pre> | 4                        |                    |

| bit 9            |             | PI1 Fault Interrupt Flag Stat                                    |                          |                    |

|                  |             | pt request has occurred                                          |                          |                    |

|                  |             | pt request has not occurred                                      | b                        |                    |

| bit 8            | T3IF: Time  | r3 Interrupt Flag Status bit                                     |                          |                    |

|                  |             | pt request has occurred                                          |                          |                    |

|                  | 0 = Interru | pt request has not occurred                                      |                          |                    |

| bit 7            | T2IF: Time  | r2 Interrupt Flag Status bit                                     |                          |                    |

|                  |             | pt request has occurred                                          |                          |                    |

|                  |             | pt request has not occurred                                      |                          |                    |

| bit 6            |             | Itput Compare Channel 2 In                                       | iterrupt Flag Status bit |                    |

|                  |             | pt request has occurred<br>pt request has not occurred           |                          |                    |

| bit 5            |             | ut Capture Channel 2 Interru                                     |                          |                    |

|                  | •           | pt request has occurred                                          |                          |                    |

|                  |             | pt request has not occurred                                      | b                        |                    |

| bit 4            | Unimplem    | ented: Read as '0'                                               |                          |                    |

| bit 3            | T1IF: Time  | r1 Interrupt Flag Status bit                                     |                          |                    |

|                  |             | pt request has occurred                                          |                          |                    |

|                  | 0 = Interru | pt request has not occurred                                      | d                        |                    |

| bit 2            |             | Itput Compare Channel 1 In                                       | terrupt Flag Status bit  |                    |

|                  |             | pt request has occurred                                          | 4                        |                    |

|                  | v = interru | pt request has not occurred                                      | L                        |                    |

### REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | R/W-0, HS | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----------|-----|-----|-----|-----|-----|-------|

| —      | RTCIF     | —   | —   | _   | —   | —   | —     |

| bit 15 |           |     |     |     |     |     | bit 8 |

| U-0   | R/W-0, HS | R/W-0, HS | U-0 | U-0 | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----------|-----------|-----|-----|-----------|-----------|-------|

| —     | INT4IF    | INT3IF    | —   | —   | MI2C2IF   | SI2C2IF   | —     |

| bit 7 |           |           |     |     |           |           | bit 0 |

| Legend:           | HS = Hardware Settable | e bit                  |                    |

|-------------------|------------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit       | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15   | Unimplemented: Read as '0'                                |

|----------|-----------------------------------------------------------|

| bit 14   | RTCIF: Real-Time Clock/Calendar Interrupt Flag Status bit |

|          | 1 = Interrupt request has occurred                        |

|          | 0 = Interrupt request has not occurred                    |

| bit 13-7 | Unimplemented: Read as '0'                                |

| bit 6    | INT4IF: External Interrupt 4 Flag Status bit              |

|          | 1 = Interrupt request has occurred                        |

|          | 0 = Interrupt request has not occurred                    |

| bit 5    | INT3IF: External Interrupt 3 Flag Status bit              |

|          | 1 = Interrupt request has occurred                        |

|          | 0 = Interrupt request has not occurred                    |

| bit 4-3  | Unimplemented: Read as '0'                                |

| bit 2    | MI2C2IF: Master I2C2 Event Interrupt Flag Status bit      |

|          | 1 = Interrupt request has occurred                        |

|          | 0 = Interrupt request has not occurred                    |

| bit 1    | SI2C2IF: Slave I2C2 Event Interrupt Flag Status bit       |

|          | 1 = Interrupt request has occurred                        |

|          | 0 = Interrupt request has not occurred                    |

| bit 0    | Unimplemented: Read as '0'                                |

## 9.2.2 IDLE MODE

Idle mode has these features:

- The CPU will stop executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 9.4 "Selective Peripheral Module Control").

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The device will wake from Idle mode on any of these events:

- Any interrupt that is individually enabled.

- · Any device Reset.

- A WDT time-out.

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

#### 9.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

### 9.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default.

It is also possible to use Doze mode to selectively reduce power consumption in event driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

### 9.4 Selective Peripheral Module Control

Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what these modes do not provide: the allocation of power resources to CPU processing with minimal power consumption from the peripherals.

PIC24F devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- The Peripheral Enable bit, generically named, "XXXEN", located in the module's main control SFR.

- The Peripheral Module Disable (PMD) bit, generically named, "XXXMD", located in one of the PMD Control registers.

Both bits have similar functions in enabling or disabling its associated module. Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral will also be disabled, so writes to those registers will have no effect and read values will be invalid. Many peripheral modules have a corresponding PMD bit.

In contrast, disabling a module by clearing its XXXEN bit disables its functionality, but leaves its registers available to be read and written to. This reduces power consumption, but not by as much as setting the PMD bit does. Most peripheral modules have an enable bit; exceptions include input capture, output compare and RTCC.

To achieve more selective power savings, peripheral modules can also be selectively disabled when the device enters Idle mode. This is done through the control bit of the generic name format, "XXXIDL". By default, all modules that can operate during Idle mode will do so. Using the disable on Idle feature allows further reduction of power consumption during Idle mode, enhancing power savings for extremely critical power applications.

## 10.1.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

### 10.1.2 OPEN-DRAIN CONFIGURATION

In addition to the PORT, LAT and TRIS registers for data control, each port pin can also be individually configured for either a digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired digital only pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

#### 10.1.3 CONFIGURING D+ AND D- PINS (RG2 AND RG3)

The input buffers of the RG2 and RG3 pins are, by default, tri-stated. To use these pins as input pins, the UTRDIS bit (U1CNFG2<0>) should be set, which enables the input buffers on these pins.

# 10.2 Configuring Analog Port Pins (ANSEL)

The ANSx and TRISx registers control the operation of the pins with analog function. Each port pin with analog function is associated with one of the ANS bits (see Register 10-1 through Register 10-7), which decides if the pin function should be analog or digital. Refer to Table 10-1 for detailed behavior of the pin for different ANSx and TRISx bit settings.

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

#### 10.2.1 ANALOG INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Pins that are used as digital only inputs are able to handle DC voltages of up to 5.5V, a level typical for digital logic circuits. In contrast, pins that also have analog input functions of any kind can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins should always be avoided. Table 10-2 summarizes the input capabilities. Refer to **Section 29.1 "DC Characteristics"** for more details.

| Pin Function   | ANSx Setting | TRISx Setting | Comments                                                                                                                                   |

|----------------|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Analog Input   | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Analog Output  | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Digital Input  | 0            | 1             | Firmware must wait at least one instruction cycle<br>after configuring a pin as a digital input before a valid<br>input value can be read. |

| Digital Output | 0            | 0             | Make sure to disable the analog output function on the pin if any is present.                                                              |

TABLE 10-1: CONFIGURING ANALOG/DIGITAL FUNCTION OF AN I/O PIN

## TABLE 10-2: INPUT VOLTAGE LEVELS FOR PORT OR PIN TOLERATED DESCRIPTION INPUT

| Port or Pin                            | Tolerated Input | Description                              |  |  |

|----------------------------------------|-----------------|------------------------------------------|--|--|

| PORTA <sup>(1)</sup> <10:9, 7:6>       |                 |                                          |  |  |

| PORTB<15:0>                            |                 |                                          |  |  |

| PORTC <sup>(1)</sup> <15:12, 4>        |                 |                                          |  |  |

| PORTD<7:6>                             | VDD             | Only VDD input levels are tolerated.     |  |  |

| PORTE <sup>(1)</sup> <9>               |                 |                                          |  |  |

| PORTF<0>                               |                 |                                          |  |  |

| PORTG<9:6, 3:2>                        |                 |                                          |  |  |

| PORTA <sup>(1)</sup> <15:14, 5:0>      |                 |                                          |  |  |

| PORTC <sup>(1)</sup> <3:1>             | 5.57            |                                          |  |  |

| PORTD <sup>(1)</sup> <15:8, 5:0>       |                 | Tolerates input levels above VDD, useful |  |  |

| PORTE <sup>(1)</sup> <8:0>             | 5.5V            | for most standard logic.                 |  |  |

| PORTF <sup>(1)</sup> <13:12, 8:7, 5:1> |                 |                                          |  |  |

| PORTG <sup>(1)</sup> <15:12, 1:0>      |                 |                                          |  |  |

**Note 1:** Not all of the pins of these PORTS are implemented in 64-pin devices (PIC24FJXXXGB206); refer to the device pinout diagrams for the details.

# 10.3 Input Change Notification

The input change notification function of the I/O ports allows the PIC24FJ256GB210 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 84 external inputs that may be selected (enabled) for generating an interrupt request on a Change-of-State.

Registers, CNEN1 through CNEN6, contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin has a both a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source that is connected to the pin, while the pull-downs act as a current sink that is connected to the pin. These eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups and pull-downs are separately enabled using the CNPU1 through CNPU6 registers (for pull-ups), and the CNPD1 through CNPD6 registers (for pull-downs). Each CN pin has individual control bits for its pull-up and pull-down. Setting a control bit enables the weak pull-up or pull-down for the corresponding pin.

When the internal pull-up is selected, the pin pulls up to VDD - 1.1V (typical). When the internal pull-down is selected, the pin pulls down to Vss.

Note: Pull-ups on change notification pins should always be disabled whenever the port pin is configured as a digital output.

Note: To use CN83 and CN84, which are on the D+ and D- pins, the UTRDIS bit (U1CNFG2<0>) should be set.

# EXAMPLE 10-1: PORT WRITE/READ IN ASSEMBLY

| MOV 0xFF00, W0  | ; Configure PORTB<15:8> as inputs |

|-----------------|-----------------------------------|

| MOV W0, TRISB   | ; and PORTB<7:0> as outputs       |

| NOP             | ; Delay 1 cycle                   |

| BTSS PORTB, #13 | ; Next Instruction                |

|               | PORT WRITE/READ IN 'C' |

|---------------|------------------------|

| EXAMPLE 10-2: |                        |

| TRISB = 0xFF00;                     | //Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs |

|-------------------------------------|-------------------------------------------------------------|

| Nop();                              | //Delay 1 cycle                                             |

| <pre>If (PORTBbits.RB13) { };</pre> | //Next Instruction                                          |

# REGISTER 12-2: TyCON: TIMER3 AND TIMER5 CONTROL REGISTER<sup>(3)</sup>

| R/W-0              | U-0 | R/W-0                | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|----------------------|-----|-----|-----|-----|-------|

| TON <sup>(1)</sup> | —   | TSIDL <sup>(1)</sup> | —   | —   |     | _   | —     |

| bit 15             |     |                      |     |     |     |     | bit 8 |

| U-0   | R/W-0                | R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0                | U-0   |

|-------|----------------------|-----------------------|-----------------------|-----|-----|----------------------|-------|

| —     | TGATE <sup>(1)</sup> | TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> |     | —   | TCS <sup>(1,2)</sup> | —     |

| bit 7 |                      |                       |                       |     |     |                      | bit 0 |

| Legend:   |                                                |                                                              |                                  |                                 |  |  |  |

|-----------|------------------------------------------------|--------------------------------------------------------------|----------------------------------|---------------------------------|--|--|--|

| R = Read  | able bit                                       | W = Writable bit                                             | U = Unimplemented bit,           | read as '0'                     |  |  |  |

| n = Value | e at POR                                       | '1' = Bit is set                                             | '0' = Bit is cleared             | x = Bit is unknown              |  |  |  |

| it 15     | TON: Tim                                       | ery On bit <sup>(1)</sup>                                    |                                  |                                 |  |  |  |

|           |                                                | s 16-bit Timery<br>s 16-bit Timery                           |                                  |                                 |  |  |  |

| it 14     | Unimpler                                       | mented: Read as '0'                                          |                                  |                                 |  |  |  |

| it 13     | TSIDL: S                                       | top in Idle Mode bit <sup>(1)</sup>                          |                                  |                                 |  |  |  |

|           |                                                | ontinue module operation wh<br>inue module operation in Idle |                                  |                                 |  |  |  |

| it 12-7   | Unimpler                                       | Unimplemented: Read as '0'                                   |                                  |                                 |  |  |  |

| it 6      | TGATE:                                         | Timery Gated Time Accumula                                   | ation Enable bit <sup>(1)</sup>  |                                 |  |  |  |

|           |                                                | ignored.                                                     |                                  |                                 |  |  |  |

| it 5-4    | TCKPS<                                         | 1:0>: Timery Input Clock Pre                                 | scale Select bits <sup>(1)</sup> |                                 |  |  |  |

|           | 11 = 1:25<br>10 = 1:64<br>01 = 1:8<br>00 = 1:1 | •                                                            |                                  |                                 |  |  |  |

| it 3-2    | Unimpler                                       | mented: Read as '0'                                          |                                  |                                 |  |  |  |

| it 1      | TCS: Tim                                       | ery Clock Source Select bit <sup>(1</sup>                    | l,2)                             |                                 |  |  |  |

|           |                                                | nal clock from pin, TyCK (on<br>nal clock (Fosc/2)           | the rising edge)                 |                                 |  |  |  |

| it 0      | Unimpler                                       | mented: Read as '0'                                          |                                  |                                 |  |  |  |

| lote 1:   |                                                | operation is enabled (T2CON timer functions are set through  |                                  | e bits have no effect on Timery |  |  |  |

| 2:        | •                                              |                                                              |                                  | pin. See Section 10.4 "Periphe  |  |  |  |

Pin Select (PPS)" for more information.

**3:** Changing the value of TyCON while the timer is running (TON = 1) causes the timer prescale counter to reset and is not recommended.

For 32-bit cascaded operation, these steps are also necessary:

- Set the OC32 bits for both registers (OCyCON2<8> and OCxCON2<8>). Enable the even numbered module first to ensure the modules will start functioning in unison.

- Clear the OCTRIG bit of the even module (OCyCON2) so the module will run in Synchronous mode.

- 3. Configure the desired output and Fault settings for OCy.

- 4. Force the output pin for OCx to the output state by clearing the OCTRIS bit.

- If Trigger mode operation is required, configure the trigger options in OCx by using the OCTRIG (OCxCON2<7>), TRIGMODE (OCxCON1<3>) and SYNCSEL (OCxCON2<4:0>) bits.

- Configure the desired Compare or PWM mode of operation (OCM<2:0>) for OCy first, then for OCx.

Depending on the output mode selected, the module holds the OCx pin in its default state and forces a transition to the opposite state when OCxR matches the timer. In Double Compare modes, OCx is forced back to its default state when a match with OCxRS occurs. The OCxIF interrupt flag is set after an OCxR match in Single Compare modes and after each OCxRS match in Double Compare modes.

Single-shot pulse events only occur once, but may be repeated by simply rewriting the value of the OCxCON1 register. Continuous pulse events continue indefinitely until terminated.

### 14.3 Pulse-Width Modulation (PWM) Mode

In PWM mode, the output compare module can be configured for edge-aligned or center-aligned pulse waveform generation. All PWM operations are double-buffered (buffer registers are internal to the module and are not mapped into SFR space).

To configure the output compare module for PWM operation:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins.

- 2. Calculate the desired duty cycles and load them into the OCxR register.

- 3. Calculate the desired period and load it into the OCxRS register.

- Select the current OCx as the synchronization source by writing 0x1F to the SYNCSEL<4:0> bits (OCxCON2<4:0>) and '0' to the OCTRIG bit (OCxCON2<7>).

- 5. Select a clock source by writing to the OCTSEL<2:0> bits (OCxCON<12:10>).

- 6. Enable interrupts, if required, for the timer and output compare modules. The output compare interrupt is required for PWM Fault pin utilization.

- 7. Select the desired PWM mode in the OCM<2:0> bits (OCxCON1<2:0>).

- Appropriate Fault inputs may be enabled by using the ENFLT<2:0> bits as described in Register 14-1.

- 9. If a timer is selected as a clock source, set the selected timer prescale value. The selected timer's prescaler output is used as the clock input for the OCx timer, and not the selected timer output.

Note: This peripheral contains input and output functions that may need to be configured by the Peripheral Pin Select. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

#### **REGISTER 14-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is only cleared by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits<sup>(1)</sup>

- 111 = Center-Aligned PWM mode on OCx<sup>(2)</sup>

- 110 = Edge-Aligned PWM Mode on  $OCx^{(2)}$

- 101 = Double Compare Continuous Pulse mode: Initialize the OCx pin low, the toggle OCx state is continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initialize the OCx pin low, toggle the OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare Continuous Pulse mode: Compare events continuously toggle the OCx pin

- 010 = Single Compare Single-Shot mode: Initialize OCx pin high, compare event forces the OCx pin low

- 001 = Single Compare Single-Shot mode: Initialize OCx pin low, compare event forces the OCx pin high

- 000 = Output compare channel is disabled

- Note 1: The OCx output must also be configured to an available RPn pin. For more information, see Section 10.4 "Peripheral Pin Select (PPS)".

- 2: The Fault input enable and Fault status bits are valid when OCM<2:0> = 111 or 110.

- **3:** The Comparator 1 output controls the OC1-OC3 channels; Comparator 2 output controls the OC4-OC6 channels. Comparator 3 output controls the OC7-OC9 channels.

- 4: The OCFA/OCFB Fault input must also be configured to an available RPn/RPIn pin. For more information, see Section 10.4 "Peripheral Pin Select (PPS)".

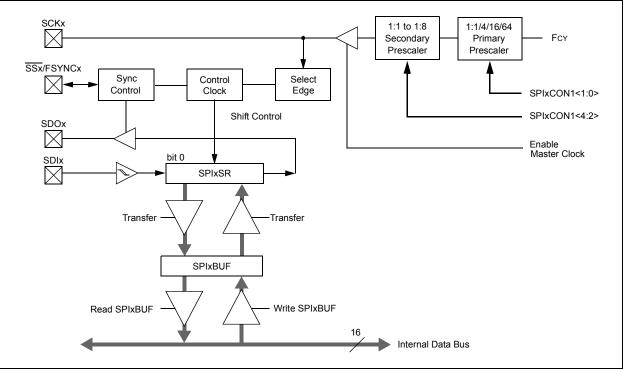

To set up the SPI module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

- 5. Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPI module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit.

- If the CKE bit (SPIxCON1<8>) is set, then the SSEN bit (SPIxCON1<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

# FIGURE 15-1: SPIX MODULE BLOCK DIAGRAM (STANDARD MODE)

| U-0                 | U-0                                             | U-0                                | R/W-0                 | R/W-0                     | R/W-0                 | R/W-0              | R/W-0              |

|---------------------|-------------------------------------------------|------------------------------------|-----------------------|---------------------------|-----------------------|--------------------|--------------------|

| _                   | —                                               | —                                  | DISSCK <sup>(1)</sup> | DISSDO <sup>(2)</sup>     | MODE16                | SMP                | CKE <sup>(3)</sup> |

| bit 15              |                                                 |                                    |                       |                           |                       |                    | bit 8              |

|                     |                                                 |                                    |                       |                           |                       |                    |                    |

| R/W-0               | R/W-0                                           | R/W-0                              | R/W-0                 | R/W-0                     | R/W-0                 | R/W-0              | R/W-0              |

| SSEN <sup>(4)</sup> | CKP                                             | MSTEN                              | SPRE2                 | SPRE1                     | SPRE0                 | PPRE1              | PPRE0              |

| bit 7               |                                                 |                                    |                       |                           |                       |                    | bit 0              |

| Legend:             |                                                 |                                    |                       |                           |                       |                    |                    |

| R = Readat          | ole hit                                         | W = Writable                       | bit                   | U = Unimplem              | nented bit, read      | as '0'             |                    |

| -n = Value a        |                                                 | '1' = Bit is set                   |                       | '0' = Bit is clea         |                       | x = Bit is unkr    | own                |

|                     |                                                 | 1 - Dit 13 301                     |                       |                           |                       |                    | IOWIT              |

| bit 15-13           | Unimplement                                     | ted: Read as '                     | 0'                    |                           |                       |                    |                    |

| bit 12              | -                                               |                                    | bit (SPI Master       | modes only) <sup>(1</sup> | )                     |                    |                    |

|                     |                                                 |                                    | abled; pin funct      | • /                       |                       |                    |                    |

|                     |                                                 | SPI clock is ena                   |                       |                           |                       |                    |                    |

| bit 11              |                                                 | able SDOx Pin                      |                       |                           |                       |                    |                    |

|                     |                                                 |                                    | the module; p         | in functions as           | I/O                   |                    |                    |

| bit 10              | -                                               | is controlled t                    | iunication Select     | at hit                    |                       |                    |                    |

|                     |                                                 | ication is word                    |                       |                           |                       |                    |                    |

|                     |                                                 | ication is byte-                   |                       |                           |                       |                    |                    |

| bit 9               | SMP: SPIx Da                                    | ata Input Samp                     | le Phase bit          |                           |                       |                    |                    |

|                     | Master mode:                                    |                                    |                       |                           |                       |                    |                    |

|                     |                                                 |                                    | t the end of data     |                           | 2                     |                    |                    |

|                     | Slave mode:                                     | a is sampled a                     | t the middle of o     |                           | e                     |                    |                    |

|                     |                                                 | cleared when                       | SPIx is used in       | Slave mode.               |                       |                    |                    |

| bit 8               | CKE: SPIx CI                                    | ock Edge Sele                      | ct bit <sup>(3)</sup> |                           |                       |                    |                    |

|                     |                                                 |                                    |                       |                           | lock state to Idl     |                    |                    |

|                     |                                                 | -                                  | -                     |                           | ck state to activ     | e clock state (s   | see bit 6)         |

| bit 7               |                                                 |                                    | (Slave mode) b        | Dit <sup>(4)</sup>        |                       |                    |                    |

|                     |                                                 | s used for Slav<br>s not used by t |                       | is controlled by          | y the port functi     | on                 |                    |

| bit 6               | CKP: Clock P                                    | olarity Select b                   | bit                   |                           | · · ·                 |                    |                    |

|                     | 1 = Idle state                                  | for the clock is                   | s a high level; a     | ctive state is a          | low level             |                    |                    |

|                     |                                                 |                                    | s a low level; ac     | tive state is a h         | nigh level            |                    |                    |

| bit 5               |                                                 | ter Mode Enab                      | le bit                |                           |                       |                    |                    |

|                     | 1 = Master m<br>0 = Slave mo                    |                                    |                       |                           |                       |                    |                    |

| Note 1:             | f DISSCK = 0, SO                                | CKy must be a                      | onfigurad to an       | available PPn             | nin Soo <b>Socti</b>  | on 10 4 "Porin     | boral Din          |

|                     | Select (PPS)" for                               |                                    |                       |                           | pin. See Section      | ul lu.4 relip      |                    |

| <b>2</b> :          | f DISSDO = 0, SI<br>Select (PPS)" for           | DOx must be c                      | onfigured to an       | available RPn             | pin. See <b>Secti</b> | on 10.4 "Perij     | oheral Pin         |

| 3:                  | The CKE bit is no<br>SPI modes (FRMI            | t used in the F                    |                       | les. The user s           | hould program         | this bit to '0' fo | or the Framed      |

| 4:                  | f SSEN = 1, <del>SSx</del><br>Select (PPS)" for | must be config                     |                       | ilable RPn/PRI            | n pin. See <b>Sec</b> | tion 10.4 "Per     | ipheral Pin        |

# REGISTER 15-2: SPIxCON1: SPIx CONTROL REGISTER 1

#### 18.1 **Hardware Configuration**

#### 18.1.1 DEVICE MODE

#### 18.1.1.1 D+ Pull-up Resistor

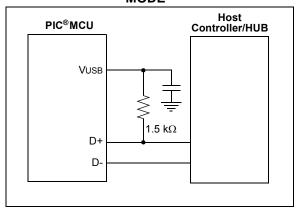

PIC24FJ256GB210 family devices have a built-in 1.5 k $\Omega$  resistor on the D+ line that is available when the microcontroller is operating in Device mode. This is used to signal an external Host that the device is operating in Full-Speed Device mode. It is engaged by setting the USBEN bit (U1CON<0>). If the OTGEN bit (U1OTGCON<2>) is set, then the D+ pull-up is enabled through the DPPULUP bit (U1OTGCON<7>).

Alternatively, an external resistor may be used on D+, as shown in Figure 18-2.

#### **FIGURE 18-2: EXTERNAL PULL-UP FOR** FULL-SPEED DEVICE MODE

#### 18.1.1.2 Power Modes

Many USB applications will likely have several different sets of power requirements and configuration. The most common power modes encountered are:

- · Bus Power Only mode

- Self-Power Only mode

- Dual Power with Self-Power Dominance

Bus Power Only mode (Figure 18-3) is effectively the simplest method. All power for the application is drawn from the USB.

To meet the inrush current requirements of the "USB 2.0 OTG Specification", the total effective capacitance appearing across VBUS and ground must be no more than 10 µF.

In the USB Suspend mode, devices must consume no more than 2.5 mA from the 5V VBUS line of the USB cable. During the USB Suspend mode, the D+ or Dpull-up resistor must remain active, which will consume some of the allowed suspend current.

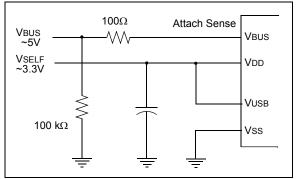

In Self-Power Only mode (Figure 18-4), the USB application provides its own power, with very little power being pulled from the USB. Note that an attach indication is added to indicate when the USB has been connected and the host is actively powering VBUS.

To meet compliance specifications, the USB module (and the D+ or D- pull-up resistor) should not be enabled until the host actively drives VBUS high. One of the 5.5V tolerant I/O pins may be used for this purpose.

The application should never source any current onto the 5V VBUS pin of the USB cable.

The Dual Power mode with Self-Power Dominance (Figure 18-5) allows the application to use internal power primarily, but switch to power from the USB when no internal power is available. Dual power devices must also meet all of the special requirements for inrush current and Suspend mode current previously described, and must not enable the USB module until VBUS is driven high.

**FIGURE 18-4:**

SELF-POWER ONLY

| R/W-0         | U-0                                                    | R/W-0                                | R/W-0               | R/W-0             | R/W-0            | R/W-0           | R/W-0      |  |  |

|---------------|--------------------------------------------------------|--------------------------------------|---------------------|-------------------|------------------|-----------------|------------|--|--|

| CTMUEN        | —                                                      | CTMUSIDL                             | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN         | IDISSEN         | CTTRIG     |  |  |

| bit 15        |                                                        |                                      |                     | •                 |                  |                 | bit        |  |  |

|               |                                                        |                                      |                     |                   |                  |                 |            |  |  |

| R/W-0         | R/W-0                                                  | R/W-0                                | R/W-0               | R/W-0             | R/W-0            | R/W-0, HSC      | R/W-0, HSC |  |  |

| EDG2POL       | EDG2SEL1                                               | EDG2SEL0                             | EDG1POL             | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT   |  |  |

| bit 7         |                                                        |                                      |                     |                   |                  |                 | bit        |  |  |

| Legend:       |                                                        | HSC = Hardw                          | are Settable/C      | learable bit      |                  |                 |            |  |  |

| R = Readable  | e bit                                                  | W = Writable I                       | oit                 | U = Unimplen      | nented bit, read | l as '0'        |            |  |  |

| -n = Value at | POR                                                    | '1' = Bit is set                     |                     | '0' = Bit is clea |                  | x = Bit is unkr | iown       |  |  |

| bit 15        | CTMUEN: CT                                             | MU Enable bit                        |                     |                   |                  |                 |            |  |  |

|               | 1 = Module is<br>0 = Module is                         |                                      |                     |                   |                  |                 |            |  |  |

| bit 14        | Unimplement                                            | ted: Read as '0                      | )'                  |                   |                  |                 |            |  |  |

| bit 13        |                                                        | Stop in Idle Moo                     |                     |                   |                  |                 |            |  |  |

|               |                                                        | ue module ope<br>module operat       |                     |                   | s Idle mode      |                 |            |  |  |

| bit 12        | TGEN: Time Generation Enable bit <sup>(1)</sup>        |                                      |                     |                   |                  |                 |            |  |  |

|               | 0 = Disables                                           | edge delay gen<br>edge delay ger     |                     |                   |                  |                 |            |  |  |

| bit 10        | EDGEN: Edge Enable bit                                 |                                      |                     |                   |                  |                 |            |  |  |

|               | 1 = Edges are<br>0 = Edges are                         |                                      |                     |                   |                  |                 |            |  |  |

| bit 10        |                                                        | Edge Sequence                        |                     |                   |                  |                 |            |  |  |

|               |                                                        | vent must occu<br>sequence is ne     |                     | 2 event can oc    | cur              |                 |            |  |  |

| bit 9         | IDISSEN: Ana                                           | alog Current Sc                      | urce Control b      | oit               |                  |                 |            |  |  |

|               |                                                        | urrent source o<br>urrent source o   |                     |                   |                  |                 |            |  |  |

| bit 8         | CTTRIG: Trigg                                          | ger Control bit                      |                     |                   |                  |                 |            |  |  |

|               |                                                        | utput is enabled<br>utput is disable |                     |                   |                  |                 |            |  |  |

| bit 7         | EDG2POL: E                                             | dge 2 Polarity S                     | Select bit          |                   |                  |                 |            |  |  |

|               |                                                        | programmed f<br>programmed f         |                     |                   |                  |                 |            |  |  |

| bit 6-5       | EDG2SEL<1:                                             | 0>: Edge 2 So                        | urce Select bits    | s                 |                  |                 |            |  |  |

|               | 11 = CTEDG<br>10 = CTEDG<br>01 = OC1 mo<br>00 = Timer1 | 2 pin<br>odule                       |                     |                   |                  |                 |            |  |  |

| bit 4         |                                                        | dge 1 Polarity S                     | Select bit          |                   |                  |                 |            |  |  |

|               | 1 = Edge 1 is                                          | programmed f                         | or a positive e     |                   |                  |                 |            |  |  |

### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER

Note 1: If TGEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

| U-0    | U-0           | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |  |  |

|--------|---------------|-----|-----|-----|-----|-----|-----|--|--|--|

| _      | —             | —   | —   | —   | —   | —   | —   |  |  |  |

| bit 23 | bit 23 bit 16 |     |     |     |     |     |     |  |  |  |

| r-x          | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | r-1      | R/PO-1 | R/PO-1 |  |

|--------------|--------|--------|--------|--------|----------|--------|--------|--|

| reserved     | JTAGEN | GCP    | GWRP   | DEBUG  | reserved | ICS1   | ICS0   |  |

| bit 15 bit 8 |        |        |        |        |          |        |        |  |

| R/PO-1 | R/PO-1 | R/PO-1                 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |

|--------|--------|------------------------|--------|--------|--------|--------|--------|

| FWDTEN | WINDIS | ALTVREF <sup>(1)</sup> | FWPSA  | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 |

| bit 7  |        |                        |        |        |        |        | bit 0  |

| Legend:           | r = Reserved bit |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

| bit 23-16 | Unimplemented: Read as '1'                                                                                                                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | Reserved: The value is unknown; program as '0'                                                                                                                                                                                       |

| bit 14    | JTAGEN: JTAG Port Enable bit                                                                                                                                                                                                         |

|           | <ul><li>1 = JTAG port is enabled</li><li>0 = JTAG port is disabled</li></ul>                                                                                                                                                         |

| bit 13    | GCP: General Segment Program Memory Code Protection bit                                                                                                                                                                              |

|           | <ul> <li>1 = Code protection is disabled</li> <li>0 = Code protection is enabled for the entire program memory space</li> </ul>                                                                                                      |

| bit 12    | GWRP: General Segment Code Flash Write Protection bit                                                                                                                                                                                |

|           | <ul><li>1 = Writes to program memory are allowed</li><li>0 = Writes to program memory are not allowed</li></ul>                                                                                                                      |

| bit 11    | DEBUG: Background Debugger Enable bit                                                                                                                                                                                                |

|           | <ul><li>1 = Device resets into Operational mode</li><li>0 = Device resets into Debug mode</li></ul>                                                                                                                                  |

| bit 10    | Reserved: Always maintain as '1'                                                                                                                                                                                                     |

| bit 9-8   | ICS<1:0>: Emulator Pin Placement Select bits                                                                                                                                                                                         |

|           | <ul> <li>11 = Emulator functions are shared with PGEC1/PGED1</li> <li>10 = Emulator functions are shared with PGEC2/PGED2</li> <li>01 = Emulator functions are shared with PGEC3/PGED3</li> <li>00 = Reserved; do not use</li> </ul> |

| bit 7     | FWDTEN: Watchdog Timer Enable bit                                                                                                                                                                                                    |

|           | <ul><li>1 = Watchdog Timer is enabled</li><li>0 = Watchdog Timer is disabled</li></ul>                                                                                                                                               |

| bit 6     | WINDIS: Windowed Watchdog Timer Disable bit                                                                                                                                                                                          |

|           | <ul> <li>1 = Standard Watchdog Timer is enabled</li> <li>0 = Windowed Watchdog Timer is enabled; FWDTEN must be '1'</li> </ul>                                                                                                       |

| bit 5     | ALTVREF: Alternate VREF Pin Selection bit <sup>(1)</sup>                                                                                                                                                                             |

|           | <ul> <li>1 = VREF is on a default pin (VREF+ on RA10 and VREF- on RA9)</li> <li>0 = VREF is on an alternate pin (VREF+ on RB0 and VREF- on RB1)</li> </ul>                                                                           |

|           |                                                                                                                                                                                                                                      |

Note 1: Unimplemented in 64-pin devices, maintain at '1' (VREF+ on RB0 and VREF- on RB1).

# 27.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows<sup>®</sup> programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

## 27.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

## 27.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

| DC CHARACTERISTICS                  |                        |     | Standard Operating Conditions: 2.2V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |                     |               |  |  |  |  |  |

|-------------------------------------|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------|---------------|--|--|--|--|--|

| Parameter<br>No.                    | Typical <sup>(1)</sup> | Max | Units                                                                                                                                            | Conditions |                     |               |  |  |  |  |  |

| Idle Current (IIDLE) <sup>(2)</sup> |                        |     |                                                                                                                                                  |            |                     |               |  |  |  |  |  |

| DC40D                               | 170                    | 320 | μA                                                                                                                                               | -40°C      |                     |               |  |  |  |  |  |

| DC40E                               | 170                    | 320 | μA                                                                                                                                               | +25°C      | 3.3∨ <sup>(3)</sup> | 1 MIPS        |  |  |  |  |  |

| DC40F                               | 220                    | 380 | μA                                                                                                                                               | +85°C      |                     |               |  |  |  |  |  |

| DC43D                               | 0.6                    | 1.2 | mA                                                                                                                                               | -40°C      |                     |               |  |  |  |  |  |

| DC43E                               | 0.6                    | 1.2 | mA                                                                                                                                               | +25°C      | 3.3∨ <sup>(3)</sup> | 4 MIPS        |  |  |  |  |  |

| DC43F                               | 0.7                    | 1.2 | mA                                                                                                                                               | +85°C      |                     |               |  |  |  |  |  |

| DC47D                               | 2.3                    | 4.8 | mA                                                                                                                                               | -40°C      |                     |               |  |  |  |  |  |

| DC47E                               | 2.3                    | 4.8 | mA                                                                                                                                               | +25°C      | 3.3∨ <sup>(3)</sup> | 16 MIPS       |  |  |  |  |  |

| DC47F                               | 2.4                    | 4.8 | mA                                                                                                                                               | +85°C      |                     |               |  |  |  |  |  |

| DC50D                               | 0.8                    | 1.8 | mA                                                                                                                                               | -40°C      |                     | FRC (4 MIPS)  |  |  |  |  |  |

| DC50E                               | 0.8                    | 1.8 | mA                                                                                                                                               | +25°C      | 3.3∨ <sup>(3)</sup> |               |  |  |  |  |  |

| DC50F                               | 1.0                    | 1.8 | mA                                                                                                                                               | +85°C      | 7                   |               |  |  |  |  |  |

| DC51D                               | 40.0                   | 85  | μA                                                                                                                                               | -40°C      |                     | LPRC (31 kHz) |  |  |  |  |  |

| DC51E                               | 40.0                   | 85  | μA                                                                                                                                               | +25°C      | 3.3∨ <sup>(3)</sup> |               |  |  |  |  |  |

| DC51F                               | 120.0                  | 210 | μA                                                                                                                                               | +85°C      | 7                   |               |  |  |  |  |  |

#### TABLE 29-5: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.