Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 84                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 96K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                     |

| Data Converters            | A/D 24x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 121-TFBGA                                                                       |

| Supplier Device Package    | 121-TFBGA (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb210t-i-bg |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                                | Pin Number      | in Number      |       |                           |                                                                       |

|----------|--------------------------------|-----------------|----------------|-------|---------------------------|-----------------------------------------------------------------------|

| Function | 64-Pin<br>TQFP/QFN             | 100-Pin<br>TQFP | 121-Pin<br>BGA | I/O   | Input<br>Buffer           | Description                                                           |

| PMD0     | 60                             | 93              | A4             | I/O   | ST/TTL                    |                                                                       |

| PMD1     | 61                             | 94              | B4             | I/O   | ST/TTL                    |                                                                       |

| PMD2     | 62                             | 98              | B3             | I/O   | ST/TTL                    |                                                                       |

| PMD3     | 63                             | 99              | A2             | I/O   | ST/TTL                    |                                                                       |

| PMD4     | 64                             | 100             | A1             | I/O   | ST/TTL                    |                                                                       |

| PMD5     | 1                              | 3               | D3             | I/O   | ST/TTL                    |                                                                       |

| PMD6     | 2                              | 4               | C1             | I/O   | ST/TTL                    |                                                                       |

| PMD7     | 3                              | 5               | D2             | I/O   | ST/TTL                    | Devellet Menter Devt Dete kite (45:0)                                 |

| PMD8     | _                              | 90              | A5             | I/O   | ST/TTL                    | Parallel Master Port Data bits<15:0>.                                 |

| PMD9     |                                | 89              | E6             | I/O   | ST/TTL                    |                                                                       |

| PMD10    | _                              | 88              | A6             | I/O   | ST/TTL                    |                                                                       |

| PMD11    |                                | 87              | B6             | I/O   | ST/TTL                    |                                                                       |

| PMD12    |                                | 79              | A9             | I/O   | ST/TTL                    |                                                                       |

| PMD13    | —                              | 80              | D8             | I/O   | ST/TTL                    |                                                                       |

| PMD14    | —                              | 83              | D7             | I/O   | ST/TTL                    |                                                                       |

| PMD15    | —                              | 84              | C7             | I/O   | ST/TTL                    |                                                                       |

| PMRD     | 53                             | 82              | B8             | I/O   | ST/TTL                    | Parallel Master Port Read Strobe.                                     |

| PMWR     | 52                             | 81              | C8             | I/O   | ST/TTL                    | Parallel Master Port Write Strobe.                                    |

| RA0      | —                              | 17              | G3             | I/O   | ST                        |                                                                       |

| RA1      | —                              | 38              | J6             | I/O   | ST                        |                                                                       |

| RA2      | —                              | 58              | H11            | I/O   | ST                        |                                                                       |

| RA3      | —                              | 59              | G10            | I/O   | ST                        |                                                                       |

| RA4      | —                              | 60              | G11            | I/O   | ST                        |                                                                       |

| RA5      | —                              | 61              | G9             | I/O   | ST                        | PORTA Digital I/O.                                                    |

| RA6      | _                              | 91              | C5             | I/O   | ST                        |                                                                       |

| RA7      | —                              | 92              | B5             | I/O   | ST                        |                                                                       |

| RA9      | —                              | 28              | L2             | I/O   | ST                        |                                                                       |

| RA10     | —                              | 29              | K3             | I/O   | ST                        |                                                                       |

| RA14     | —                              | 66              | E11            | I/O   | ST                        |                                                                       |

| RA15     | —                              | 67              | E8             | I/O   | ST                        |                                                                       |

|          | TTL = TTL inpu<br>ANA = Analog |                 | put            | <br>- | ST =<br>I <sup>2</sup> C™ | Schmitt Trigger input buffer<br>= I <sup>2</sup> C/SMBus input buffer |

#### TABLE 1-3: PIC24FJ256GB210 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

**Note 1:** The alternate EPMP pins are selected when the ALTPMP (CW3<12>) bit is programmed to '0'.

2: The PMSC2 signal will replace the PMA15 signal on the 15-pin PMA when CSF<1:0> = 01 or 10.

3: The PMCS1 signal will replace the PMA14 signal on the 14-pin PMA when CSF<1:0> = 10.

4: The alternate VREF pins selected when the ALTVREF (CW1<5>) bit is programmed to '0'.

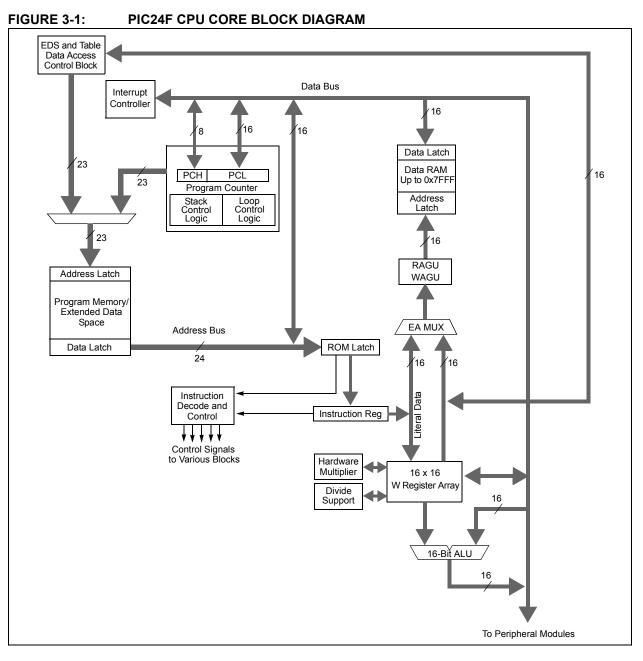

| TABLE 3-1:CPU CORE REGISTERS |

|------------------------------|

|------------------------------|

| Register(s) Name | Description                        |  |

|------------------|------------------------------------|--|

| W0 through W15   | Working Register Array             |  |

| PC               | 23-Bit Program Counter             |  |

| SR               | ALU STATUS Register                |  |

| SPLIM            | Stack Pointer Limit Value Register |  |

| TBLPAG           | Table Memory Page Address Register |  |

| RCOUNT           | Repeat Loop Counter Register       |  |

| CORCON           | CPU Control Register               |  |

| DISICNT          | Disable Interrupt Count Register   |  |

| DSRPAG           | Data Space Read Page Register      |  |

| DSWPAG           | Data Space Write Page Register     |  |

#### TABLE 4-31: SYSTEM REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|--------|--------|-------|-------|--------|--------|-------|---------------|

| RCON         | 0740 | TRAPR  | IOPUWR | _      | _      | _      | _      | CM     | VREGS  | EXTR    | SWR    | SWDTEN | WDTO  | SLEEP | IDLE   | BOR    | POR   | Note 1        |

| OSCCON       | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | IOLOCK | LOCK   | _     | CF    | POSCEN | SOSCEN | OSWEN | Note 2        |

| CLKDIV       | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | CPDIV1  | CPDIV0 | PLLEN  | r     | _     | —      | _      | -     | 0100          |

| OSCTUN       | 0748 |        | _      | _      | _      | _      | _      | _      | _      | _       | _      | TUN5   | TUN4  | TUN3  | TUN2   | TUN1   | TUN0  | 0000          |

| REFOCON      | 074E | ROEN   | —      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | —      | _      | —     | -     | —      | _      | -     | 0000          |

- = unimplemented, read as '0', r = Reserved. Reset values are shown in hexadecimal. Legend:

Note 1:

The Reset value of the RCON register is dependent on the type of Reset event. See Section 6.0 "Resets" for more information. The Reset value of the OSCCON register is dependent on both the type of Reset event and the device configuration. See Section 8.0 "Oscillator Configuration" for more information. 2:

#### TABLE 4-32: NVM REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets   |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|----------------------|-------|-------|-------|--------|--------|--------|--------|-----------------|

| NVMCON       | 0760 | WR     | WREN   | WRERR  | _      | _      | _      | _     | _     | -                    | ERASE | _     | _     | NVMOP3 | NVMOP2 | NVMOP1 | NVMOP0 | 0000 <b>(1)</b> |

| NVMKEY       | 0766 | _      |        | -      |        | —      |        |       | _     | NVMKEY Register<7:0> |       |       |       |        | 0000   |        |        |                 |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-33: PMD REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|--------|-------|--------|--------|--------|--------|--------|---------------|

| PMD1         | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | -      | —      | _     | I2C1MD | U2MD   | U1MD  | SPI2MD | SPI1MD | —      | _      | ADC1MD | 0000          |

| PMD2         | 0772 | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD | OC8MD  | OC7MD  | OC6MD | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3         | 0774 | -      | _      | _      | _      | _      | CMPMD  | RTCCMD | PMPMD | CRCMD  | _      | _     | _      | U3MD   | I2C3MD | I2C2MD | _      | 0000          |

| PMD4         | 0776 |        | _      | _      | _      | _      | _      | _      | _     | _      | UPWMMD | U4MD  | _      | REFOMD | CTMUMD | LVDMD  | USB1MD | 0000          |

| PMD5         | 0778 |        | _      | _      | _      | _      | _      | _      | IC9MD | _      | _      | _     | _      | _      | _      | _      | OC9MD  | 0000          |

| PMD6         | 077A |        |        | _      | _      | _      |        | _      | _     |        | _      |       | _      | _      | _      | _      | SPI3MD | 0000          |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

#### EXAMPLE 5-2: ERASING A PROGRAM MEMORY BLOCK ('C' LANGUAGE CODE)

| <pre>// C example using MPLAB C30     unsigned long progAddr = 0xXXXXXX;     unsigned int offset;</pre> | // Address of row to write                             |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| //Set up pointer to the first memory location t                                                         | o be written                                           |

| TBLPAG = progAddr>>16;                                                                                  | // Initialize PM Page Boundary SFR                     |

| offset = progAddr & 0xFFFF;                                                                             | <pre>// Initialize lower word of address</pre>         |

| <pre>builtin_tblwtl(offset, 0x0000);</pre>                                                              | // Set base address of erase block                     |

|                                                                                                         | // with dummy latch write                              |

| NVMCON = $0 \times 4042$ ;                                                                              | // Initialize NVMCON                                   |

| asm("DISI #5");                                                                                         | <pre>// Block all interrupts with priority &lt;7</pre> |

|                                                                                                         | // for next 5 instructions                             |

| builtin_write_NVM();                                                                                    | // check function to perform unlock                    |

|                                                                                                         | // sequence and set WR                                 |

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS

| ; Set up NVMCON for row programming operation | 22                                          |

|-----------------------------------------------|---------------------------------------------|

| MOV #0x4001, W0                               | ;                                           |

| MOV W0, NVMCON                                | ,<br>; Initialize NVMCON                    |

| ; Set up a pointer to the first program memo  |                                             |

| ; program memory selected, and writes enable  |                                             |

| MOV #0x0000, W0                               | ;                                           |

| MOV W0, TBLPAG                                | ,<br>; Initialize PM Page Boundary SFR      |

| MOV #0x6000, W0                               | ; An example program memory address         |

| ; Perform the TBLWT instructions to write th  |                                             |

| ; Oth program word                            |                                             |

| MOV #LOW_WORD_0, W2                           | i                                           |

| MOV #HIGH_BYTE_0, W3                          | ;                                           |

| TBLWTL W2, [W0]                               | ,<br>; Write PM low word into program latch |

| TBLWTH W3, [W0++]                             | ; Write PM high byte into program latch     |

| ; lst_program_word                            | , write in high byte into program faton     |

| MOV #LOW_WORD_1, W2                           | i                                           |

| MOV #HIGH BYTE 1, W3                          | ;                                           |

| TBLWTL W2, [W0]                               | ; Write PM low word into program latch      |

| TBLWTH W3, [W0++]                             | ; Write PM high byte into program latch     |

| ; 2nd program word                            |                                             |

| MOV #LOW_WORD_2, W2                           | i                                           |

| MOV #HIGH_BYTE_2, W3                          | i                                           |

| TBLWTL W2, [W0]                               | ; Write PM low word into program latch      |

| TBLWTH W3, [W0++]                             | ; Write PM high byte into program latch     |

| •                                             |                                             |

| •                                             |                                             |

| •                                             |                                             |

| ; 63rd_program_word                           |                                             |

| MOV #LOW_WORD_63, W2                          | ;                                           |

| MOV #HIGH_BYTE_63, W3                         | ;                                           |

| TBLWTL W2, [W0]                               | ; Write PM low word into program latch      |

| TBLWTH W3, [W0]                               | ; Write PM high byte into program latch     |

|                                               |                                             |

#### EXAMPLE 5-4: INITIATING A PROGRAMMING SEQUENCE

| DISI  | #5          | ; Block all interrupts with priority <7 |

|-------|-------------|-----------------------------------------|

|       |             | ; for next 5 instructions               |

| MOV.B | #0x55, W0   |                                         |

| MOV   | W0, NVMKEY  | ; Write the 0x55 key                    |

| MOV.B | #0xAA, W1   | ;                                       |

| MOV   | W1, NVMKEY  | ; Write the OxAA key                    |

| BSET  | NVMCON, #WR | ; Start the programming sequence        |

| NOP   |             | ; Required delays                       |

| NOP   |             |                                         |

| BTSC  | NVMCON, #15 | ; and wait for it to be                 |

| BRA   | \$-2        | ; completed                             |

| R/W-0         | R-0, HSC                                                                  | U-0               | U-0                                                                                          | U-0               | U-0    | U-0                | U-0    |  |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------|-------------------|--------|--------------------|--------|--|--|--|--|--|--|

| ALTIVT        | DISI                                                                      |                   | _                                                                                            | —                 | —      | —                  | —      |  |  |  |  |  |  |

| bit 15        |                                                                           |                   |                                                                                              |                   |        |                    | bit 8  |  |  |  |  |  |  |

|               |                                                                           |                   |                                                                                              |                   |        |                    |        |  |  |  |  |  |  |

| U-0           | U-0                                                                       | U-0               | R/W-0                                                                                        | R/W-0             | R/W-0  | R/W-0              | R/W-0  |  |  |  |  |  |  |

|               |                                                                           | —                 | INT4EP                                                                                       | INT3EP            | INT2EP | INT1EP             | INT0EP |  |  |  |  |  |  |

| bit 7         |                                                                           |                   |                                                                                              |                   |        |                    | bit 0  |  |  |  |  |  |  |

|               |                                                                           |                   |                                                                                              |                   |        |                    |        |  |  |  |  |  |  |

| Legend:       |                                                                           | HSC = Hardw       | ISC = Hardware Settable/Clearable bit<br>V = Writable bit U = Unimplemented bit, read as '0' |                   |        |                    |        |  |  |  |  |  |  |

| R = Readable  |                                                                           | W = Writable      | l as '0'                                                                                     |                   |        |                    |        |  |  |  |  |  |  |

| -n = Value at | POR                                                                       | '1' = Bit is set  |                                                                                              | '0' = Bit is clea | ared   | x = Bit is unknown |        |  |  |  |  |  |  |

|               |                                                                           |                   |                                                                                              |                   |        |                    |        |  |  |  |  |  |  |

| bit 15        |                                                                           |                   | terrupt Vector 7                                                                             | lable bit         |        |                    |        |  |  |  |  |  |  |

|               | 1 = Use Alternate Interrupt Vector Table                                  |                   |                                                                                              |                   |        |                    |        |  |  |  |  |  |  |

| bit 14        | 0 = Use standard (default) vector table DISI: DISI Instruction Status bit |                   |                                                                                              |                   |        |                    |        |  |  |  |  |  |  |

| DIL 14        |                                                                           | truction is activ |                                                                                              |                   |        |                    |        |  |  |  |  |  |  |

|               |                                                                           | truction is not a | -                                                                                            |                   |        |                    |        |  |  |  |  |  |  |

| bit 13-5      | Unimplemen                                                                | ted: Read as '    | 0'                                                                                           |                   |        |                    |        |  |  |  |  |  |  |

| bit 4         | INT4EP: Exte                                                              | ernal Interrupt 4 | Edge Detect F                                                                                | Polarity Select b | pit    |                    |        |  |  |  |  |  |  |

|               |                                                                           | on negative ed    |                                                                                              |                   |        |                    |        |  |  |  |  |  |  |

|               | 0 = Interrupt                                                             | on positive edg   | ge                                                                                           |                   |        |                    |        |  |  |  |  |  |  |

| bit 3         |                                                                           |                   | •                                                                                            | Polarity Select b | bit    |                    |        |  |  |  |  |  |  |

|               |                                                                           | on negative ed    |                                                                                              |                   |        |                    |        |  |  |  |  |  |  |

| bit 2         | •                                                                         | on positive edg   |                                                                                              | Palarity Calaat k | .:+    |                    |        |  |  |  |  |  |  |

| DIL Z         |                                                                           | on negative ed    | •                                                                                            | Polarity Select b | JIL    |                    |        |  |  |  |  |  |  |

|               |                                                                           | on positive ed    |                                                                                              |                   |        |                    |        |  |  |  |  |  |  |

| bit 1         | •                                                                         |                   |                                                                                              | Polarity Select b | oit    |                    |        |  |  |  |  |  |  |

|               | 1 = Interrupt on negative edge                                            |                   |                                                                                              |                   |        |                    |        |  |  |  |  |  |  |

|               | 0 = Interrupt                                                             | on positive edg   | ge                                                                                           |                   |        |                    |        |  |  |  |  |  |  |

| bit 0         |                                                                           | •                 | •                                                                                            | Polarity Select b | pit    |                    |        |  |  |  |  |  |  |

|               |                                                                           | on negative ed    |                                                                                              |                   |        |                    |        |  |  |  |  |  |  |

|               | 0 = Interrupt                                                             | on positive edo   | je                                                                                           |                   |        |                    |        |  |  |  |  |  |  |

|               |                                                                           |                   |                                                                                              |                   |        |                    |        |  |  |  |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

#### REGISTER 7-12: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 9 | OC3IE: Output Compare Channel 3 Interrupt Enable bit   |

|-------|--------------------------------------------------------|

|       | 1 = Interrupt request is enabled                       |

|       | 0 = Interrupt request is not enabled                   |

| bit 8 | Unimplemented: Read as '0'                             |

| bit 7 | IC8IE: Input Capture Channel 8 Interrupt Enable bit    |

|       | 1 = Interrupt request is enabled                       |

|       | 0 = Interrupt request is not enabled                   |

| bit 6 | IC7IE: Input Capture Channel 7 Interrupt Enable bit    |

|       | 1 = Interrupt request is enabled                       |

|       | 0 = Interrupt request is not enabled                   |

| bit 5 | Unimplemented: Read as '0'                             |

| bit 4 | INT1IE: External Interrupt 1 Enable bit <sup>(1)</sup> |

|       | 1 = Interrupt request is enabled                       |

|       | 0 = Interrupt request is not enabled                   |

| bit 3 | CNIE: Input Change Notification Interrupt Enable bit   |

|       | 1 = Interrupt request is enabled                       |

|       | 0 = Interrupt request is not enabled                   |

| bit 2 | CMIE: Comparator Interrupt Enable bit                  |

|       | 1 = Interrupt request is enabled                       |

|       | 0 = Interrupt request is not enabled                   |

| bit 1 | MI2C1IE: Master I2C1 Event Interrupt Enable bit        |

|       | 1 = Interrupt request is enabled                       |

|       | 0 = Interrupt request is not enabled                   |

| bit 0 | SI2C1IE: Slave I2C1 Event Interrupt Enable bit         |

|       | 1 = Interrupt request is enabled                       |

|       | 0 = Interrupt request is not enabled                   |

**Note 1:** If an external interrupt is enabled, the interrupt input must also be configured to an available RPx or RPIx pin. See **Section 10.4 "Peripheral Pin Select (PPS)**" for more information.

#### REGISTER 7-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5 (CONTINUED)

- **U3ERIE:** UART3 Error Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 0 Unimplemented: Read as '0'

bit 1

#### REGISTER 7-17: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0    | R/W-1 | R/W-0 | R/W-0 | U-0 | R/W-1  | R/W-0  | R/W-0  |

|--------|-------|-------|-------|-----|--------|--------|--------|

| —      | T1IP2 | T1IP1 | T1IP0 | —   | OC1IP2 | OC1IP1 | OC1IP0 |

| bit 15 |       |       |       |     |        |        | bit 8  |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|--------|--------|--------|-----|---------|---------|---------|

| _     | IC1IP2 | IC1IP1 | IC1IP0 | —   | INT0IP2 | INT0IP1 | INT0IP0 |

| bit 7 |        |        |        |     |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15           | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12        | T1IP<2:0>: Timer1 Interrupt Priority bits                                                                                                                                                                                                                                                                                                       |

|                  | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                      |

|                  | •                                                                                                                                                                                                                                                                                                                                               |

|                  | •                                                                                                                                                                                                                                                                                                                                               |

|                  | 001 = Interrupt is priority 1                                                                                                                                                                                                                                                                                                                   |

|                  | 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                              |

| bit 11           | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| bit 10-8         | OC1IP<2:0>: Output Compare Channel 1 Interrupt Priority bits                                                                                                                                                                                                                                                                                    |

|                  | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                      |

|                  | •                                                                                                                                                                                                                                                                                                                                               |

|                  |                                                                                                                                                                                                                                                                                                                                                 |

|                  | 001 = Interrupt is priority 1                                                                                                                                                                                                                                                                                                                   |

|                  | 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                              |

|                  |                                                                                                                                                                                                                                                                                                                                                 |

| bit 7            | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| bit 7<br>bit 6-4 | Unimplemented: Read as '0'<br>IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits                                                                                                                                                                                                                                                       |

|                  | -                                                                                                                                                                                                                                                                                                                                               |

|                  | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits                                                                                                                                                                                                                                                                                     |

|                  | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                       |

|                  | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1                                                                                                                                                                                      |

| bit 6-4          | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                                                                                                |

|                  | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled<br>Unimplemented: Read as '0'                                                                                                                  |

| bit 6-4          | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                                                                                                |

| bit 6-4<br>bit 3 | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled<br>Unimplemented: Read as '0'                                                                                                                  |

| bit 6-4<br>bit 3 | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled<br>Unimplemented: Read as '0'<br>INTOIP<2:0>: External Interrupt 0 Priority bits                                                               |

| bit 6-4<br>bit 3 | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled<br>Unimplemented: Read as '0'<br>INTOIP<2:0>: External Interrupt 0 Priority bits                                                               |

| bit 6-4<br>bit 3 | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled<br>Unimplemented: Read as '0'<br>INTOIP<2:0>: External Interrupt 0 Priority bits                                                               |

| bit 6-4<br>bit 3 | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled<br>Unimplemented: Read as '0'<br>INTOIP<2:0>: External Interrupt 0 Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |

#### 7.4 Interrupt Setup Procedures

#### 7.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS (INTCON1<15>) control bit if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|

|       | initialized, such that all user interrupt |  |  |  |  |

|       | sources are assigned to Priority Level 4. |  |  |  |  |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

### 7.4.2 INTERRUPT SERVICE ROUTINE (ISR)

The method that is used to declare an Interrupt Service Routine (ISR) and initialize the IVT with the correct vector address will depend on the programming language (i.e., 'C' or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.4.3 TRAP SERVICE ROUTINE (TSR)

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value 0Eh with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Levels 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels, 1-6, for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7   | CLKLOCK: Clock Selection Lock Enabled bit                                                |

|---------|------------------------------------------------------------------------------------------|

|         | If FSCM is enabled (FCKSM1 = 1):                                                         |

|         | 1 = Clock and PLL selections are locked                                                  |

|         | 0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit |

|         | If FSCM is disabled (FCKSM1 = 0):                                                        |

|         | Clock and PLL selections are never locked and may be modified by setting the OSWEN bit.  |

| bit 6   | IOLOCK: I/O Lock Enable bit <sup>(2)</sup>                                               |

|         | 1 = I/O lock is active                                                                   |

|         | 0 = I/O lock is not active                                                               |

| bit 5   | LOCK: PLL Lock Status bit <sup>(3)</sup>                                                 |

|         | 1 = PLL module is in lock or PLL module start-up timer is satisfied                      |

|         | 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled          |

| bit 4   | Unimplemented: Read as '0'                                                               |

| bit 3   | CF: Clock Fail Detect bit                                                                |

|         | 1 = FSCM has detected a clock failure                                                    |

|         | 0 = No clock failure has been detected                                                   |

| bit 2   | POSCEN: Primary Oscillator Sleep Enable bit                                              |

|         | 1 = Primary Oscillator continues to operate during Sleep mode                            |

|         | 0 = Primary Oscillator is disabled during Sleep mode                                     |

| bit 1   | SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit                                    |

|         | 1 = Enable the Secondary Oscillator                                                      |

|         | 0 = Disable the Secondary Oscillator                                                     |

| bit 0   | OSWEN: Oscillator Switch Enable bit                                                      |

|         | 1 = Initiate an oscillator switch to the clock source specified by the NOSC<2:0> bits    |

|         | 0 = Oscillator switch is complete                                                        |

| Note 1: | Reset values for these bits are determined by the FNOSC Configuration bits.              |

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1', once the IOLOCK bit is set, it cannot be cleared.

- 3: Also resets to '0' during any valid clock switch or whenever a non PLL Clock mode is selected.

#### 10.4.5 CONSIDERATIONS FOR PERIPHERAL PIN SELECTION

The ability to control Peripheral Pin Selection introduces several considerations into application design that could be overlooked. This is particularly true for several common peripherals that are available only as remappable peripherals.

The main consideration is that the Peripheral Pin Selects are not available on default pins in the device's default (Reset) state. Since all RPINRx registers reset to '111111' and all RPORx registers reset to '000000', all Peripheral Pin Select inputs are tied to Vss and all Peripheral Pin Select outputs are disconnected.

| Note: | In tying Peripheral Pin Select inputs to  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|

|       | RP63, RP63 need not exist on a device for |  |  |  |  |

|       | the registers to be reset to it.          |  |  |  |  |

This situation requires the user to initialize the device with the proper peripheral configuration before any other application code is executed. Since the IOLOCK bit resets in the unlocked state, it is not necessary to execute the unlock sequence after the device has come out of Reset. For application safety, however, it is best to set IOLOCK and lock the configuration after writing to the control registers.

Because the unlock sequence is timing-critical, it must be executed as an assembly language routine in the same manner as changes to the oscillator configuration. If the bulk of the application is written in 'C', or another high-level language, the unlock sequence should be performed by writing in-line assembly.

Choosing the configuration requires the review of all Peripheral Pin Selects and their pin assignments, especially those that will not be used in the application. In all cases, unused pin-selectable peripherals should be disabled completely. Unused peripherals should have their inputs assigned to an unused RPn/RPIn pin function. I/O pins with unused RPn functions should be configured with the null peripheral output.

The assignment of a peripheral to a particular pin does not automatically perform any other configuration of the pin's I/O circuitry. In theory, this means adding a pin-selectable output to a pin may mean inadvertently driving an existing peripheral input when the output is driven. Users must be familiar with the behavior of other fixed peripherals that share a remappable pin and know when to enable or disable them. To be safe, fixed digital peripherals that share the same pin should be disabled when not in use. Along these lines, configuring a remappable pin for a specific peripheral does not automatically turn that feature on. The peripheral must be specifically configured for operation, and enabled as if it were tied to a fixed pin. Where this happens in the application code (immediately following device Reset and peripheral configuration or inside the main application routine) depends on the peripheral and its use in the application.

A final consideration is that Peripheral Pin Select functions neither override analog inputs nor reconfigure pins with analog functions for digital I/O. If a pin is configured as an analog input on device Reset, it must be explicitly reconfigured as digital I/O when used with a Peripheral Pin Select.

Example 10-3 shows a configuration for bidirectional communication with flow control using UART1. The following input and output functions are used:

- Input Functions: U1RX, U1CTS

- Output Functions: U1TX, U1RTS

#### EXAMPLE 10-3: CONFIGURING UART1 INPUT AND OUTPUT FUNCTIONS

| // Unlock Regis            | sters    |                    |         |

|----------------------------|----------|--------------------|---------|

| asm volatile(              | "MOV     | #OSCCON, w1        | \n"     |

|                            | "MOV     | #0x46, w2          | \n"     |

|                            | "MOV     | #0x57, w3          | \n"     |

|                            | "MOV.b   | w2, [w1]           | \n"     |

|                            | "MOV.b   | w3, [w1]           | \n"     |

|                            | "BCLR (  | ) SCCON , #6 " ) ; |         |

|                            |          |                    |         |

| // or use C30 k            | ouilt-ir | n macro:           |         |

| // _builtin_wri            | ite_OSCO | CONL (OSCCON &     | 0xbf);  |

| // Configure Ir            | nput Fur | nctions (Table     |         |

| Table 10-2))               |          |                    |         |

| // Assign U                | JRX To   | Pin RPO            |         |

| RPINR18bits                | .Ulrxr   | = 0 <i>i</i>       |         |

|                            |          |                    |         |

| // Assign U                |          |                    |         |

| RPINR18bits                | .U1CTSR  | = 1;               |         |

|                            |          |                    |         |

| // Configure Ou            | -        |                    | ≥ 10-4) |

| // Assign U<br>RPOR1bits.R |          |                    |         |

| RPORIDIUS.R                | PZR = 3  | 1                  |         |

| // Assign U                | יוסדפ דה | Din D2             |         |

| RPOR1bits.R                |          |                    |         |

| 111 011101105.11           |          |                    |         |

| // Lock Registe            | ers      |                    |         |

| asm volatile               |          | #OSCCON, w1        | \n"     |

|                            |          | #0x46, w2          | \n"     |

|                            |          |                    | \n"     |

|                            | "MOV.b   | w2, [w1]\          | n"      |

|                            | "MOV.b   | w3, [w1]           | \n"     |

|                            | "BSET    | OSCCON, #6")       | ;       |

| // or use C30 k            | ouilt-ir | n macro:           |         |

| // _builtin_wri            | ite_OSCO | CONL (OSCCON       | 0x40);  |

| 1                          |          |                    |         |

'1' = Bit is set

#### REGISTER 10-29: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| bit 15<br>U-0 U-<br>bit 7<br>Legend: |          |       |       |       |       |       |

|--------------------------------------|----------|-------|-------|-------|-------|-------|

| U-0 U-                               |          |       |       |       |       |       |

| U-0 U-                               |          |       |       |       |       | bit 0 |

|                                      |          |       |       |       |       |       |

|                                      | – RP0R5  | RP0R4 | RP0R3 | RP0R2 | RP0R1 | RP0R0 |

| bit 15                               | -0 R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| bit 15                               |          |       |       |       |       |       |

|                                      |          |       |       |       |       | bit 8 |

|                                      |          |       |       |       |       |       |

| U-0 U-                               | – RP1R5  | RP1R4 | RP1R3 | RP1R2 | RP1R1 | RP1R0 |

bit 15-14 Unimplemented: Read as '0'

-n = Value at POR

bit 13-8

RP1R<5:0>: RP1 Output Pin Mapping bits

Peripheral output number n is assigned to pin, RP1 (see Table 10-4 for peripheral function numbers).

bit 7-6

Unimplemented: Read as '0'

bit 5.0

RP2D (5:0) = RP0 Output Pin Mapping bits

'0' = Bit is cleared

x = Bit is unknown

bit 5-0 **RP0R<5:0>:** RP0 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP0 (see Table 10-4 for peripheral function numbers).

#### REGISTER 10-30: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | RP3R5 | RP3R4 | RP3R3 | RP3R2 | RP3R1 | RP3R0 |

| bit 15 |     | •     |       |       |       |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | RP2R5 | RP2R4 | RP2R3 | RP2R2 | RP2R1 | RP2R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP3R<5:0>:** RP3 Output Pin Mapping bits

Peripheral output number n is assigned to pin, RP3 (see Table 10-4 for peripheral function numbers).

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP2R<5:0>:** RP2 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP2 (see Table 10-4 for peripheral function numbers).

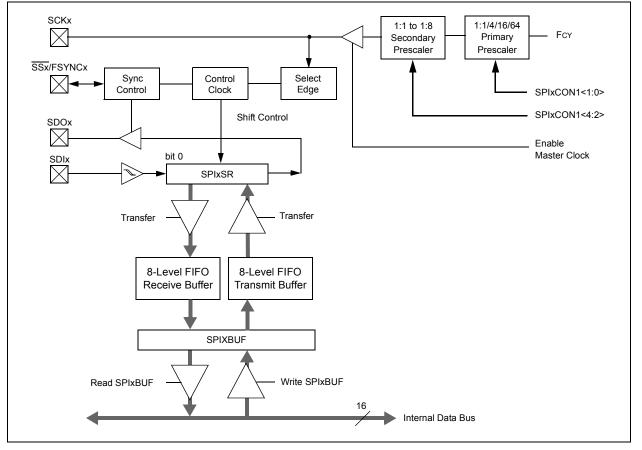

To set up the SPI module for the Enhanced Buffer Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Select Enhanced Buffer mode by setting the SPIBEN bit (SPIxCON2<0>).

- Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

- 6. Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPI module for the Enhanced Buffer Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Select Enhanced Buffer mode by setting the SPIBEN bit (SPIxCON2<0>).

- 8. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

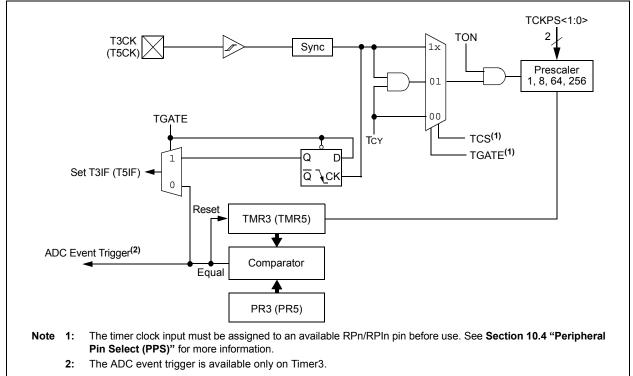

#### FIGURE 15-2: SPIX MODULE BLOCK DIAGRAM (ENHANCED MODE)

#### REGISTER 17-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

- bit 4 **RXINV:** Receive Polarity Inversion bit

- 1 = UxRX Idle state is '0'

- 0 = UxRX Idle state is '1'

- bit 3 BRGH: High Baud Rate Enable bit

- 1 = High-Speed mode (4 BRG clock cycles per bit)

- 0 = Standard-Speed mode (16 BRG clock cycles per bit)

- bit 2-1 **PDSEL<1:0>:** Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Bit Selection bit

- 1 = Two Stop bits

- 0 = One Stop bit

- Note 1: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

#### EQUATION 18-1: ESTIMATING USB TRANSCEIVER CURRENT CONSUMPTION

$\mathsf{IXCVR} = \frac{40 \text{ mA} \cdot \mathsf{VUSB} \cdot \mathsf{PZERO} \cdot \mathsf{PIN} \cdot \mathsf{LCABLE}}{3.3 \text{ V} \cdot 5 \text{ m}} + \mathsf{IPULLUP}$

**Legend:** VUSB – Voltage applied to the VUSB pin in volts (3.0V to 3.6V).

PZERO – Percentage (in decimal) of the IN traffic bits sent by the PIC<sup>®</sup> microcontroller that are a value of '0'.

PIN – Percentage (in decimal) of total bus bandwidth that is used for IN traffic.

LCABLE – Length (in meters) of the USB cable. The *"USB 2.0 OTG Specification"* requires that full-speed applications use cables no longer than 5m.

$\mbox{IPULLUP}$  – Current which the nominal, 1.5 k $\Omega$  pull-up resistor (when enabled) must supply to the USB cable.

#### ALWDHR: ALARM WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup> REGISTER 20-9:

| U-0                               | U-0 | U-0    | U-0    | U-0          | R/W-x           | R/W-x    | R/W-x  |

|-----------------------------------|-----|--------|--------|--------------|-----------------|----------|--------|

| —                                 | _   | —      | —      | —            | WDAY2           | WDAY1    | WDAY0  |

| bit 15 bit 8                      |     |        |        |              |                 |          |        |

|                                   |     |        |        |              |                 |          |        |

| U-0                               | U-0 | R/W-x  | R/W-x  | R/W-x        | R/W-x           | R/W-x    | R/W-x  |

| —                                 | _   | HRTEN1 | HRTEN0 | HRONE3       | HRONE2          | HRONE1   | HRONE0 |

| bit 7                             |     |        |        |              |                 |          | bit 0  |

|                                   |     |        |        |              |                 |          |        |

| Legend:                           |     |        |        |              |                 |          |        |

| R = Readable bit W = Writable bit |     |        | bit    | U = Unimplen | nented hit read | l as '0' |        |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-11 | Unimplemented: Read as '0'                                       |

|-----------|------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits      |

|           | Contains a value from 0 to 6.                                    |

| bit 7-6   | Unimplemented: Read as '0'                                       |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits |

|           | Contains a value from 0 to 2.                                    |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits |

|           | Contains a value from 0 to 9.                                    |

|           |                                                                  |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### REGISTER 20-10: ALMINSEC: ALARM MINUTES AND SECONDS VALUE REGISTER

| U-0    | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| _      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

|        |         |         |         |         |         |         |         |

| U-0    | R/W-x   |

| —      | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7  |         |         |         |         |         |         | bit 0   |

Legend: R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit '0' = Bit is cleared -n = Value at POR '1' = Bit is set x = Bit is unknown

| bit 15    | Unimplemented: Read as '0'                                          |

|-----------|---------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

| bit 7     | Unimplemented: Read as '0'                                          |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

| U-0                             | U-0 | R/W-0            | R/W-0                                                                                                                                          | R/W-0                                                                                                                                                   | R/W-0                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                         |  |

|---------------------------------|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| _                               | —   | DWIDTH4          | DWIDTH3                                                                                                                                        | DWIDTH2                                                                                                                                                 | DWIDTH1                                                                                                                                                                                                | DWIDTH0                                                                                                                                                                                                                                       |  |

|                                 |     | ·                |                                                                                                                                                | •                                                                                                                                                       |                                                                                                                                                                                                        | bit 8                                                                                                                                                                                                                                         |  |

|                                 |     |                  |                                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                                        |                                                                                                                                                                                                                                               |  |

| U-0                             | U-0 | R/W-0            | R/W-0                                                                                                                                          | R/W-0                                                                                                                                                   | R/W-0                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                         |  |

|                                 | —   | PLEN4            | PLEN3                                                                                                                                          | PLEN2                                                                                                                                                   | PLEN1                                                                                                                                                                                                  | PLEN0                                                                                                                                                                                                                                         |  |

|                                 |     |                  |                                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                                        | bit 0                                                                                                                                                                                                                                         |  |

|                                 |     |                  |                                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                                        |                                                                                                                                                                                                                                               |  |

|                                 |     |                  |                                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                                        |                                                                                                                                                                                                                                               |  |

| R = Readable bit W = Writable b |     | bit              | U = Unimplemented bit, read as '0'                                                                                                             |                                                                                                                                                         |                                                                                                                                                                                                        |                                                                                                                                                                                                                                               |  |