Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 84                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 96K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                     |

| Data Converters            | A/D 24x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb210t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **High-Performance CPU**

- Modified Harvard Architecture

- · Up to 16 MIPS Operation at 32 MHz

- 8 MHz Internal Oscillator

- 17-Bit x 17-Bit Single-Cycle Hardware Multiplier

- 32-Bit by 16-Bit Hardware Divider

- 16 x 16-Bit Working Register Array

- C Compiler Optimized Instruction Set Architecture with Flexible Addressing modes

- Linear Program Memory Addressing, up to 12 Mbytes

- Data Memory Addressing, up to 16 Mbytes:

- 2K SFR space

- 30K linear data memory

- 66K extended data memory

- Remaining (from 16 Mbytes) memory (external) can be accessed using extended data Memory (EDS) and EPMP (EDS is divided into 32-Kbyte pages)

- Two Address Generation Units for Separate Read and Write Addressing of Data Memory

### **Power Management:**

- On-Chip Voltage Regulator of 1.8V

- · Switch between Clock Sources in Real Time

- Idle, Sleep and Doze modes with Fast Wake-up and Two-Speed Start-up

- Run Mode: 800 μA/MIPS, 3.3V Typical

- + Sleep mode Current Down to 20  $\mu\text{A},$  3.3V Typical

- Standby Current with 32 kHz Oscillator: 22  $\mu\text{A},$  3.3V Typical

### **Analog Features:**

- 10-Bit, up to 24-Channel Analog-to-Digital (A/D) Converter at 500 ksps:

- Operation is possible in Sleep mode

- Band gap reference input feature

- Three Analog Comparators with Programmable

Input/Output Configuration

- Charge Time Measurement Unit (CTMU):

- Supports capacitive touch sensing for touch screens and capacitive switches

- Minimum time measurement setting at 100 ps

- Available LVD Interrupt VLVD Level

### **Special Microcontroller Features:**

- Operating Voltage Range of 2.2V to 3.6V

- 5.5V Tolerant Input (digital pins only)

- Configurable Open-Drain Outputs on Digital I/O Ports

- High-Current Sink/Source (18 mA/18 mA) on all I/O Ports

- Selectable Power Management modes:

- Sleep, Idle and Doze modes with fast wake-up

- Fail-Safe Clock Monitor (FSCM) Operation:

- Detects clock failure and switches to on-chip, FRC oscillator

- On-Chip LDO Regulator

- Power-on Reset (POR) and Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Flexible Watchdog Timer (WDT) with On-Chip Low-Power RC Oscillator for Reliable Operation

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and In-Circuit Debug (ICD) via 2 Pins

- JTAG Boundary Scan Support

- Flash Program Memory:

- 10,000 erase/write cycle endurance (minimum)

- 20-year data retention minimum

- Selectable write protection boundary

- Self-reprogrammable under software control

- Write protection option for Configuration Words

### 4.2.6 SOFTWARE STACK

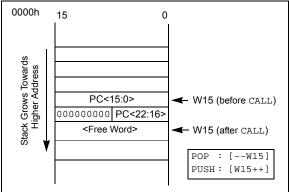

Apart from its use as a working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer (SSP). The pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-7. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL register to the |

|       | MSB of the PC prior to the push.         |

The Stack Pointer Limit Value register (SPLIM), associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 2000h in RAM, initialize the SPLIM with the value, 1FFEh.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the SFR space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### 4.3 Interfacing Program and Data Memory Spaces

The PIC24F architecture uses a 24-bit wide program space and 16-bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the PIC24F architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (program space visibility)

Table instructions allow an application to read or write to small areas of the program memory. This makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. It can only access the least significant word of the program word.

### 4.3.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Memory Page Address register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the MSBs of TBLPAG are used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 10-bit Extended Data Space Read register (DSRPAG) is used to define a 16K word page in the program space. When the Most Significant bit (MSb) of the EA is '1', and the MSb (bit 9) of DSRPAG is '1', the lower 8 bits of DSRPAG are concatenated with the lower 15 bits of the EA to form a 23-bit program space address. The DSRPAG<8> bit decides whether the lower word (when bit is '0') or the higher word (when bit is '1') of program memory is mapped. Unlike table operations, this strictly limits remapping operations to the user memory area.

Table 4-35 and Figure 4-8 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 2 **IDLE:** Wake-up From Idle Flag bit

- 1 = Device has been in Idle mode

- 0 = Device has not been in Idle mode

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

Note that BOR is also set after a Power-on Reset.

0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

- **3:** Re-enabling the regulator after it enters Standby mode will add a delay, TVREG, when waking up from Sleep. Applications that do not use the voltage regulator should set this bit to prevent this delay from occurring.

| Flag Bit          | Setting Event                                     | Clearing Event                     |

|-------------------|---------------------------------------------------|------------------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                                |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                                |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                                |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                                |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                                |

| WDTO (RCON<4>)    | WDT Time-out                                      | CLRWDT, PWRSAV<br>Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #0 Instruction                             | POR                                |

| IDLE (RCON<2>)    | PWRSAV #1 Instruction                             | POR                                |

| BOR (RCON<1>)     | POR, BOR                                          |                                    |

| POR (RCON<0>)     | POR                                               | —                                  |

TABLE 6-1: RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

#### REGISTER 7-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5 (CONTINUED)

- **U3ERIE:** UART3 Error Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 0 Unimplemented: Read as '0'

bit 1

### REGISTER 7-17: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0    | R/W-1 | R/W-0 | R/W-0 | U-0 | R/W-1  | R/W-0  | R/W-0  |

|--------|-------|-------|-------|-----|--------|--------|--------|

| —      | T1IP2 | T1IP1 | T1IP0 | —   | OC1IP2 | OC1IP1 | OC1IP0 |

| bit 15 |       |       |       |     |        |        | bit 8  |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|--------|--------|--------|-----|---------|---------|---------|

| _     | IC1IP2 | IC1IP1 | IC1IP0 | —   | INT0IP2 | INT0IP1 | INT0IP0 |

| bit 7 |        |        |        |     |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15           | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12        | T1IP<2:0>: Timer1 Interrupt Priority bits                                                                                                                                                                                                                                                                                                       |

|                  | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                      |

|                  | •                                                                                                                                                                                                                                                                                                                                               |

|                  | •                                                                                                                                                                                                                                                                                                                                               |

|                  | 001 = Interrupt is priority 1                                                                                                                                                                                                                                                                                                                   |

|                  | 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                              |

| bit 11           | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| bit 10-8         | OC1IP<2:0>: Output Compare Channel 1 Interrupt Priority bits                                                                                                                                                                                                                                                                                    |

|                  | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                      |

|                  | •                                                                                                                                                                                                                                                                                                                                               |

|                  |                                                                                                                                                                                                                                                                                                                                                 |

|                  | 001 = Interrupt is priority 1                                                                                                                                                                                                                                                                                                                   |

|                  | 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                              |

|                  |                                                                                                                                                                                                                                                                                                                                                 |

| bit 7            | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| bit 7<br>bit 6-4 | Unimplemented: Read as '0'<br>IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits                                                                                                                                                                                                                                                       |

|                  | -                                                                                                                                                                                                                                                                                                                                               |

|                  | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits                                                                                                                                                                                                                                                                                     |

|                  | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                       |

|                  | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1                                                                                                                                                                                      |

| bit 6-4          | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                                                                                                |

|                  | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled<br>Unimplemented: Read as '0'                                                                                                                  |

| bit 6-4          | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                                                                                                |

| bit 6-4<br>bit 3 | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled<br>Unimplemented: Read as '0'                                                                                                                  |

| bit 6-4<br>bit 3 | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled<br>Unimplemented: Read as '0'<br>INTOIP<2:0>: External Interrupt 0 Priority bits                                                               |

| bit 6-4<br>bit 3 | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled<br>Unimplemented: Read as '0'<br>INTOIP<2:0>: External Interrupt 0 Priority bits                                                               |

| bit 6-4<br>bit 3 | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled<br>Unimplemented: Read as '0'<br>INTOIP<2:0>: External Interrupt 0 Priority bits                                                               |

| bit 6-4<br>bit 3 | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled<br>Unimplemented: Read as '0'<br>INTOIP<2:0>: External Interrupt 0 Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |

### REGISTER 10-39: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      |     | RP21R5 | RP21R4 | RP21R3 | RP21R2 | RP21R1 | RP21R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP20R5 | RP20R4 | RP20R3 | RP20R2 | RP20R1 | RP20R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                        |                    |  |  |

|-------------------|------------------|----------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                   | x = Bit is unknown |  |  |

- bit 13-8**RP21R<5:0>:** RP21 Output Pin Mapping bits<br/>Peripheral output number n is assigned to pin, RP21 (see Table 10-4 for peripheral function numbers).bit 7-6**Unimplemented:** Read as '0'

- bit 5-0 **RP20R<5:0>:** RP20 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP20 (see Table 10-4 for peripheral function numbers).

#### REGISTER 10-40: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP23R5 | RP23R4 | RP23R3 | RP23R2 | RP23R1 | RP23R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP22R5 | RP22R4 | RP22R3 | RP22R2 | RP22R1 | RP22R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                                                                |                      |                    |  |  |

|-------------------|----------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | adable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP23R<5:0>:** RP23 Output Pin Mapping bits

Peripheral output number n is assigned to pin, RP23 (see Table 10-4 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP22R<5:0>:** RP22 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP22 (see Table 10-4 for peripheral function numbers).

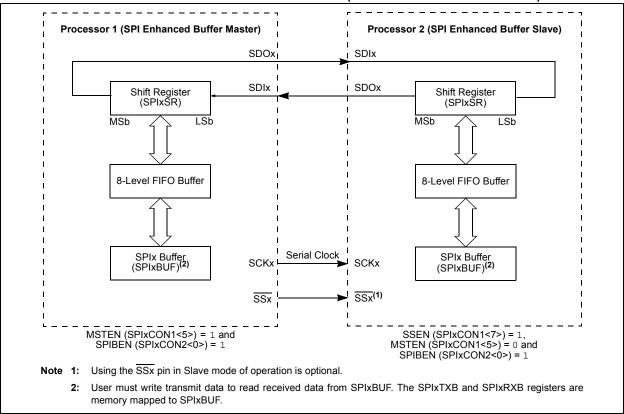

#### FIGURE 15-4: SPI MASTER/SLAVE CONNECTION (ENHANCED BUFFER MODES)

NOTES:

### 16.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 24. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS39702). The information in this data sheet supersedes the information in the FRM.

The Inter-Integrated Circuit<sup>TM</sup> (I<sup>2</sup>C<sup>TM</sup>) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, display drivers, A/D Converters, etc.

The I<sup>2</sup>C module supports these features:

- Independent master and slave logic

- · 7-bit and 10-bit device addresses

- General call address, as defined in the I<sup>2</sup>C protocol

- Clock stretching to provide delays for the processor to respond to a slave data request

- Both 100 kHz and 400 kHz bus specifications

- · Configurable address masking

- Multi-Master modes to prevent loss of messages in arbitration

- Bus Repeater mode, allowing the acceptance of all messages as a slave regardless of the address

- Automatic SCL

- A block diagram of the module is shown in Figure 16-1.

# 16.1 Communicating as a Master in a Single Master Environment

The details of sending a message in Master mode depends on the communications protocol for the device being communicated with. Typically, the sequence of events is as follows:

- 1. Assert a Start condition on SDAx and SCLx.

- 2. Send the I<sup>2</sup>C device address byte to the slave with a write indication.

- 3. Wait for and verify an Acknowledge from the slave.

- 4. Send the first data byte (sometimes known as the command) to the slave.

- 5. Wait for and verify an Acknowledge from the slave.

- 6. Send the serial memory address low byte to the slave.

- 7. Repeat steps 4 and 5 until all data bytes are sent.

- 8. Assert a Repeated Start condition on SDAx and SCLx.

- 9. Send the device address byte to the slave with a read indication.

- 10. Wait for and verify an Acknowledge from the slave.

- 11. Enable master reception to receive serial memory data.

- 12. Generate an ACK or NACK condition at the end of a received byte of data.

- 13. Generate a Stop condition on SDAx and SCLx.

| U-0           | U-0       | U-0                                      | U-0                     | U-0                   | U-0                  | U-0                    | U-0                   |

|---------------|-----------|------------------------------------------|-------------------------|-----------------------|----------------------|------------------------|-----------------------|

| —             | —         | —                                        |                         | —                     | _                    | —                      | —                     |

| bit 15        |           |                                          |                         |                       |                      |                        | bit                   |

|               |           |                                          |                         |                       |                      |                        |                       |

| R/W-0         | R/W-0     | R/W-0                                    | R/W-0                   | R/W-0                 | R/W-0                | R/W-0                  | R/W-0                 |

| DPPULUP       | DMPULUP   | DPPULDWN <sup>(1)</sup>                  | DMPULDWN <sup>(1)</sup> | VBUSON <sup>(1)</sup> | OTGEN <sup>(1)</sup> | VBUSCHG <sup>(1)</sup> | VBUSDIS <sup>(1</sup> |

| bit 7         |           |                                          |                         |                       |                      |                        | bit                   |

| Legend:       |           |                                          |                         |                       |                      |                        |                       |

| R = Readabl   | le bit    | W = Writable bit                         |                         | U = Unimplen          | nented bit re        | ad as '0'              |                       |

| -n = Value at |           | '1' = Bit is set                         |                         | '0' = Bit is cle      |                      | x = Bit is unkn        | own                   |

|               |           |                                          |                         |                       |                      |                        |                       |

| bit 15-8      | Unimpleme | nted: Read as '0                         |                         |                       |                      |                        |                       |

| bit 7         | DPPULUP:  | D+ Pull-up Enable                        | e bit                   |                       |                      |                        |                       |

|               |           | line pull-up resis                       |                         |                       |                      |                        |                       |

| 1.1.0         |           | line pull-up resis                       |                         |                       |                      |                        |                       |

| bit 6         |           | D- Pull-up Enable<br>line pull-up resist |                         |                       |                      |                        |                       |

|               |           | line pull-up resist                      |                         |                       |                      |                        |                       |

| bit 5         |           | I: D+ Pull-Down I                        |                         |                       |                      |                        |                       |

|               |           | line pull-down re                        |                         |                       |                      |                        |                       |

|               |           | line pull-down re                        |                         |                       |                      |                        |                       |

| bit 4         |           | 1: D- Pull-Down E                        |                         |                       |                      |                        |                       |

|               |           | line pull-down res<br>line pull-down res |                         |                       |                      |                        |                       |

| bit 3         |           | BUS Power-on bit                         |                         |                       |                      |                        |                       |

|               |           | e is powered                             |                         |                       |                      |                        |                       |

|               |           | e is not powered                         |                         |                       |                      |                        |                       |

| bit 2         |           | G Features Enab                          |                         |                       |                      |                        |                       |

|               |           | G is enabled; all                        |                         |                       |                      |                        |                       |

|               |           | G is disabled; D-<br>OSTEN and USE       |                         |                       | are controlled       | a in naroware b        | y the setting         |

| bit 1         |           | VBUS Charge Se                           |                         | ,                     |                      |                        |                       |

|               |           | e is set to charge                       |                         |                       |                      |                        |                       |

|               |           | e is set to charge                       |                         |                       |                      |                        |                       |

| bit 0         |           | ′BUS Discharge E                         |                         |                       |                      |                        |                       |

|               |           | e is discharged the                      |                         |                       |                      |                        |                       |

|               |           | e is not discharge                       | 54                      |                       |                      |                        |                       |

| REGISTER 18-13: | U1CNFG2: USB | <b>CONFIGURATION REGISTER 2</b> |

|-----------------|--------------|---------------------------------|

|-----------------|--------------|---------------------------------|

| U-0          | U-0                                                                                                                                             | U-0                                                                                          | U-0             | U-0              | U-0                     | U-0                     | U-0                   |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------|------------------|-------------------------|-------------------------|-----------------------|--|--|--|--|

| _            | —                                                                                                                                               | —                                                                                            | _               | _                | —                       | —                       | _                     |  |  |  |  |

| bit 15       |                                                                                                                                                 |                                                                                              |                 |                  |                         |                         | bit 8                 |  |  |  |  |

|              |                                                                                                                                                 |                                                                                              |                 |                  |                         |                         |                       |  |  |  |  |

| U-0          | U-0                                                                                                                                             | R/W-0                                                                                        | R/W-0           | R/W-0            | R/W-0                   | R/W-0                   | R/W-0                 |  |  |  |  |

|              | —                                                                                                                                               | UVCMPSEL                                                                                     | PUVBUS          | EXTI2CEN         | UVBUSDIS <sup>(1)</sup> | UVCMPDIS <sup>(1)</sup> | UTRDIS <sup>(1)</sup> |  |  |  |  |

| bit 7        |                                                                                                                                                 |                                                                                              |                 |                  |                         |                         | bit                   |  |  |  |  |

|              |                                                                                                                                                 |                                                                                              |                 |                  |                         |                         |                       |  |  |  |  |

| Legend:      |                                                                                                                                                 |                                                                                              |                 |                  |                         |                         |                       |  |  |  |  |

| R = Readal   |                                                                                                                                                 | W = Writable b                                                                               | bit             | •                | nented bit, read        |                         |                       |  |  |  |  |

| -n = Value a | at POR                                                                                                                                          | '1' = Bit is set                                                                             |                 | '0' = Bit is cle | ared                    | x = Bit is unkno        | own                   |  |  |  |  |

|              |                                                                                                                                                 |                                                                                              |                 |                  |                         |                         |                       |  |  |  |  |

| bit 15-6     | •                                                                                                                                               | nted: Read as '0                                                                             |                 |                  |                         |                         |                       |  |  |  |  |

| bit 5        |                                                                                                                                                 | UVCMPSEL: VBUS Comparator External Interface Selection bit                                   |                 |                  |                         |                         |                       |  |  |  |  |

|              | <ol> <li>Use VBUSVLD, SESSVLD and SESSEND as comparator interface pins</li> <li>Use VCMPST1 and VCMPST2 as comparator interface pins</li> </ol> |                                                                                              |                 |                  |                         |                         |                       |  |  |  |  |

| bit 4        |                                                                                                                                                 |                                                                                              | •               |                  | pins                    |                         |                       |  |  |  |  |

| DIL 4        | <b>PUVBUS:</b> VBUS Pull-Up Enable bit<br>1 = Pull-up on VBUS pin is enabled                                                                    |                                                                                              |                 |                  |                         |                         |                       |  |  |  |  |

|              |                                                                                                                                                 | on VBUS pin is di                                                                            |                 |                  |                         |                         |                       |  |  |  |  |

| bit 3        |                                                                                                                                                 | EXTI2CEN: I <sup>2</sup> C <sup>™</sup> Interface For External Module Control Enable bit     |                 |                  |                         |                         |                       |  |  |  |  |

|              | 1 = External module(s) is controlled via the $I^2C^{TM}$ interface                                                                              |                                                                                              |                 |                  |                         |                         |                       |  |  |  |  |

|              | 0 = External module(s) controlled via the dedicated pins                                                                                        |                                                                                              |                 |                  |                         |                         |                       |  |  |  |  |

| bit 2        | UVBUSDIS:                                                                                                                                       | On-Chip 5V Boo                                                                               | ost Regulator I | Builder Disable  | bit <sup>(1)</sup>      |                         |                       |  |  |  |  |

|              |                                                                                                                                                 | 1 = On-chip boost regulator builder is disabled; digital output control interface is enabled |                 |                  |                         |                         |                       |  |  |  |  |

|              |                                                                                                                                                 | boost regulator                                                                              |                 |                  |                         |                         |                       |  |  |  |  |

| bit 1        |                                                                                                                                                 | UVCMPDIS: On-Chip VBUS Comparator Disable bit <sup>(1)</sup>                                 |                 |                  |                         |                         |                       |  |  |  |  |

|              |                                                                                                                                                 | 1 = On-chip charge VBUS comparator is disabled; digital input status interface is enabled    |                 |                  |                         |                         |                       |  |  |  |  |

|              | •                                                                                                                                               | charge VBUS co                                                                               | •               |                  |                         |                         |                       |  |  |  |  |

|              | UTRDIS: On-Chip Transceiver Disable bit <sup>(1)</sup>                                                                                          |                                                                                              |                 |                  |                         |                         |                       |  |  |  |  |

| bit 0        |                                                                                                                                                 | •                                                                                            |                 |                  |                         |                         |                       |  |  |  |  |

| bit 0        | 1 = On-chip                                                                                                                                     | transceiver is di                                                                            | sabled; digital |                  | erface is enable        | ed                      |                       |  |  |  |  |

**Note 1:** Never change these bits while the USBPWR bit is set (U1PWRC<0> = 1).

### REGISTER 18-16: U1IR: USB INTERRUPT STATUS REGISTER (DEVICE MODE ONLY)

| U-0          | U-0                                                                      | U-0                                                                                                                       | U-0              | U-0               | U-0               | U-0                | U-0              |  |  |  |

|--------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-------------------|--------------------|------------------|--|--|--|

| _            |                                                                          |                                                                                                                           | _                |                   |                   |                    |                  |  |  |  |

| bit 15       |                                                                          |                                                                                                                           |                  |                   | •                 |                    | bit 8            |  |  |  |

|              |                                                                          |                                                                                                                           |                  |                   |                   |                    |                  |  |  |  |

| R/K-0, HS    | U-0                                                                      | R/K-0, HS                                                                                                                 | R/K-0, HS        | R/K-0, HS         | R/K-0, HS         | R-0                | R/K-0, HS        |  |  |  |

| STALLIF      | —                                                                        | RESUMEIF                                                                                                                  | IDLEIF           | TRNIF             | SOFIF             | UERRIF             | URSTIF           |  |  |  |

| bit 7        |                                                                          |                                                                                                                           |                  |                   |                   |                    | bit C            |  |  |  |

|              |                                                                          |                                                                                                                           |                  |                   |                   |                    |                  |  |  |  |

| Legend:      |                                                                          | U = Unimplem                                                                                                              | ented bit, read  | 1 as '0'          |                   |                    |                  |  |  |  |

| R = Readab   | le bit                                                                   | K = Write '1' to                                                                                                          | o clear bit      | HS = Hardwa       | re Settable bit   |                    |                  |  |  |  |

| -n = Value a | It POR                                                                   | '1' = Bit is set                                                                                                          |                  | '0' = Bit is clea | ared              | x = Bit is unkr    | nown             |  |  |  |

|              |                                                                          |                                                                                                                           |                  |                   |                   |                    |                  |  |  |  |

| bit 15-8     | Unimpleme                                                                | ented: Read as '0                                                                                                         | ,                |                   |                   |                    |                  |  |  |  |

| bit 7        |                                                                          | TALL Handshake                                                                                                            | •                |                   |                   |                    |                  |  |  |  |

|              | 1 = A STAL<br>Device                                                     | L handshake wa                                                                                                            | s sent by the p  | eripheral durin   | g the handshal    | e phase of the     | transaction in   |  |  |  |

|              |                                                                          | L handshake has                                                                                                           | s not been sen   | t                 |                   |                    |                  |  |  |  |

| bit 6        | Unimpleme                                                                | ented: Read as '0                                                                                                         | ,                |                   |                   |                    |                  |  |  |  |

| bit 5        | -                                                                        | RESUMEIF: Resume Interrupt bit                                                                                            |                  |                   |                   |                    |                  |  |  |  |

|              | 1 = AK-sta                                                               | $1 = A K$ -state is observed on the D+ or D- pin for 2.5 $\mu$ s (differential '1' for low speed, differential '0' fo     |                  |                   |                   |                    |                  |  |  |  |

|              | •                                                                        | full speed)<br>0 = No K-state is observed                                                                                 |                  |                   |                   |                    |                  |  |  |  |

| L:1 4        |                                                                          |                                                                                                                           | L 14             |                   |                   |                    |                  |  |  |  |

| bit 4        |                                                                          | <b>IDLEIF:</b> Idle Detect Interrupt bit<br>1 = Idle condition is detected (constant Idle state of 3 ms or more)          |                  |                   |                   |                    |                  |  |  |  |

|              |                                                                          | condition is dete                                                                                                         | •                |                   | or more)          |                    |                  |  |  |  |

| bit 3        |                                                                          | TRNIF: Token Processing Complete Interrupt bit                                                                            |                  |                   |                   |                    |                  |  |  |  |

|              |                                                                          | sing of the curren                                                                                                        | -                | -                 | U1STAT regist     | er for endpoint    | information      |  |  |  |

|              |                                                                          | sing of the curren                                                                                                        |                  |                   |                   | egister or load    | the next token   |  |  |  |

| bit 2        | SOFIF: Star                                                              | SOFIF: Start-of-Frame Token Interrupt bit                                                                                 |                  |                   |                   |                    |                  |  |  |  |

|              |                                                                          | 1 = A Start-of-Frame token is received by the peripheral or the Start-of-Frame threshold is reached by                    |                  |                   |                   |                    |                  |  |  |  |

|              | the host<br>0 = No Start-of-Frame token is received or threshold reached |                                                                                                                           |                  |                   |                   |                    |                  |  |  |  |

| bit 1        | UERRIF: USB Error Condition Interrupt bit (read-only)                    |                                                                                                                           |                  |                   |                   |                    |                  |  |  |  |

|              |                                                                          | <ul> <li>1 = An unmasked error condition has occurred; only error states enabled in the U1EIE register can set</li> </ul> |                  |                   |                   |                    |                  |  |  |  |

|              | this bit                                                                 |                                                                                                                           |                  |                   |                   |                    |                  |  |  |  |

|              | 0 = No unmasked error condition has occurred                             |                                                                                                                           |                  |                   |                   |                    |                  |  |  |  |

| bit 0        |                                                                          | URSTIF: USB Reset Interrupt bit                                                                                           |                  |                   |                   |                    |                  |  |  |  |

|              |                                                                          | 1 = Valid USB Reset has occurred for at least 2.5 $\mu$ s; Reset state must be cleared before this bit can                |                  |                   |                   |                    |                  |  |  |  |

|              | be reas<br>0 = No USF                                                    | B Reset has occu                                                                                                          | rred. Individua  | al bits can only  | be cleared by y   | writing a '1' to t | the bit position |  |  |  |

|              |                                                                          | of a word write o                                                                                                         |                  |                   |                   |                    |                  |  |  |  |

|              |                                                                          | o write to a singl                                                                                                        | e bit position v | vill cause all se | et bits at the mo | oment of the w     | rite to become   |  |  |  |

|              | cleared                                                                  |                                                                                                                           |                  |                   |                   |                    |                  |  |  |  |

| Note: II     | ndividual bits c                                                         | an only be cleare                                                                                                         | d by writing a ' | 1' to the bit pos | ition as part of  | a word write or    | peration on the  |  |  |  |

| e            | entire register.                                                         | Using Boolean in                                                                                                          | structions or b  | itwise operatio   |                   |                    |                  |  |  |  |

| a            | all set bits at the                                                      | e moment of the v                                                                                                         | write to becom   | e cleared.        |                   |                    |                  |  |  |  |

| <b>NEGISTEN</b>    | LOISTER 13-0. FINCEADS. CHIF SELECT & DASE ADDRESS REGISTER |                    |                    |                                         |                    |                    |                    |  |  |  |

|--------------------|-------------------------------------------------------------|--------------------|--------------------|-----------------------------------------|--------------------|--------------------|--------------------|--|--|--|

| R/W <sup>(1)</sup> | R/W <sup>(1)</sup>                                          | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> | R/W <sup>(1)</sup>                      | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> |  |  |  |

| BASE23             | BASE22                                                      | BASE21             | BASE20             | BASE19                                  | BASE18             | BASE17             | BASE16             |  |  |  |

| bit 15             |                                                             |                    |                    |                                         |                    |                    | bit 8              |  |  |  |

|                    |                                                             |                    |                    |                                         |                    |                    |                    |  |  |  |

| R/W <sup>(1)</sup> | U-0                                                         | U-0                | U-0                | R/W <sup>(1)</sup>                      | U-0                | U-0                | U-0                |  |  |  |

| BASE15             |                                                             | _                  | _                  | BASE11                                  | —                  | —                  | —                  |  |  |  |

| bit 7              |                                                             |                    |                    |                                         |                    |                    | bit 0              |  |  |  |

|                    |                                                             |                    |                    |                                         |                    |                    |                    |  |  |  |

| Legend:            |                                                             |                    |                    |                                         |                    |                    |                    |  |  |  |

| R = Readabl        | e bit                                                       | W = Writable       | bit                | U = Unimplemented bit, read as '0'      |                    |                    |                    |  |  |  |

| -n = Value at      | POR                                                         | '1' = Bit is se    | t                  | '0' = Bit is cleared x = Bit is unknown |                    |                    | wn                 |  |  |  |

bit 15-7 BASE<23:15>: Chip Select x Base Address bits<sup>(2)</sup>

bit 6-4 Unimplemented: Read as '0'

bit 3 BASE<11>: Chip Select x Base Address bits<sup>(2)</sup>

bit 2-0 Unimplemented: Read as '0'

**Note 1:** Value at POR is 0x0200 for PMCS1BS and 0x0600 for PMCS2BS.

2: If the whole PMCS2BS register is written together as 0x0000, then the last EDS address for the Chip Select 1 will be 0xFFFFFF. In this case, the Chip Select 2 should not be used. PMCS1BS has no such feature.

#### ALWDHR: ALARM WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup> REGISTER 20-9:

| U-0          | U-0 | U-0          | U-0    | U-0          | R/W-x           | R/W-x    | R/W-x  |

|--------------|-----|--------------|--------|--------------|-----------------|----------|--------|

| —            | _   | —            | —      | —            | WDAY2           | WDAY1    | WDAY0  |

| bit 15       |     |              |        |              |                 |          | bit 8  |

|              |     |              |        |              |                 |          |        |

| U-0          | U-0 | R/W-x        | R/W-x  | R/W-x        | R/W-x           | R/W-x    | R/W-x  |

| —            | _   | HRTEN1       | HRTEN0 | HRONE3       | HRONE2          | HRONE1   | HRONE0 |

| bit 7        |     |              |        |              |                 |          | bit 0  |

|              |     |              |        |              |                 |          |        |

| Legend:      |     |              |        |              |                 |          |        |

| R = Readable | bit | W = Writable | bit    | U = Unimplen | nented hit read | l as '0' |        |

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15-11 | Unimplemented: Read as '0'                                       |

|-----------|------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits      |

|           | Contains a value from 0 to 6.                                    |

| bit 7-6   | Unimplemented: Read as '0'                                       |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits |

|           | Contains a value from 0 to 2.                                    |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits |

|           | Contains a value from 0 to 9.                                    |

|           |                                                                  |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 20-10: ALMINSEC: ALARM MINUTES AND SECONDS VALUE REGISTER

| U-0    | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| _      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

|        |         |         |         |         |         |         |         |

| U-0    | R/W-x   |

| —      | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7  |         |         |         |         |         |         | bit 0   |

Legend: R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit '0' = Bit is cleared -n = Value at POR '1' = Bit is set x = Bit is unknown

| bit 15    | Unimplemented: Read as '0'                                          |

|-----------|---------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

| bit 7     | Unimplemented: Read as '0'                                          |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

### 20.2 Calibration

The real-time crystal input can be calibrated using the periodic auto-adjust feature. When properly calibrated, the RTCC can provide an error of less than 3 seconds per month. This is accomplished by finding the number of error clock pulses for one minute and storing the value into the lower half of the RCFGCAL register. The 8-bit signed value loaded into the lower half of RCFGCAL is multiplied by four and will either be added or subtracted from the RTCC timer, once every minute. Refer to the following steps for RTCC calibration:

- 1. Using another timer resource on the device, the user must find the error of the 32.768 kHz crystal.

- 2. Once the error is known, it must be converted to the number of error clock pulses per minute and loaded into the RCFGCAL register.

#### EQUATION 20-1: RTCC CALIBRATION

Error (clocks per minute) = (Ideal Frequency $\dagger$  – Measured Frequency) x 60

†Ideal Frequency = 32,768H

3. a) If the oscillator is faster then ideal (negative result form Step 2), the RCFGCAL register value needs to be negative. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

b) If the oscillator is slower then ideal (positive result from Step 2), the RCFGCAL register value needs to be positive. This causes the specified number of clock pulses to be added to the timer counter, once every minute.

Divide the number of error clocks per minute by 4 to get the correct CAL value and load the RCFGCAL register with the correct value.

(Each 1-bit increment in CAL adds or subtracts 4 pulses).

Writes to the lower half of the RCFGCAL register should only occur when the timer is turned off or immediately after the rising edge of the seconds pulse.

Note: It is up to the user to include in the error value the initial error of the crystal, drift due to temperature and drift due to crystal aging.

### 20.3 Alarm

- Configurable from half second to one year

- Enabled using the ALRMEN bit (ALCFGRPT<15>, Register 20-3)

- One-time alarm and repeat alarm options available

#### 20.3.1 CONFIGURING THE ALARM

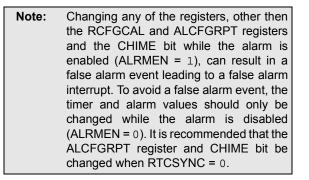

The alarm feature is enabled using the ALRMEN bit. This bit is cleared when an alarm is issued. Writes to ALRMVAL should only take place when ALRMEN = 0.

As shown in Figure 20-2, the interval selection of the alarm is configured through the AMASK bits (ALCFGRPT<13:10>). These bits determine which and how many digits of the alarm must match the clock value for the alarm to occur.

The alarm can also be configured to repeat based on a preconfigured interval. The amount of times this occurs, once the alarm is enabled, is stored in the ARPT bits, ARPT<7:0> (ALCFGRPT<7:0>). When the value of the ARPT bits equals 00h and the CHIME bit (ALCFGRPT<14>) is cleared, the repeat function is disabled and only a single alarm will occur. The alarm can be repeated up to 255 times by loading ARPT<7:0> with FFh.

After each alarm is issued, the value of the ARPT bits is decremented by one. Once the value has reached 00h, the alarm will be issued one last time, after which the ALRMEN bit will be cleared automatically and the alarm will turn off.

Indefinite repetition of the alarm can occur if the CHIME bit = 1. Instead of the alarm being disabled when the value of the ARPT bits reaches 00h, it rolls over to FFh and continues counting indefinitely while CHIME is set.

#### 20.3.2 ALARM INTERRUPT

At every alarm event, an interrupt is generated. In addition, an alarm pulse output is provided that operates at half the frequency of the alarm. This output is completely synchronous to the RTCC clock and can be used as a trigger clock to other peripherals.

### 25.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the associated "PIC24F Family Reference Manual", Section 11. "Charge Time Measurement Unit (CTMU)" (DS39724). The information in this data sheet supersedes the information in the FRM.

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- · Four edge input trigger sources

- Polarity control for each edge source

- Control of edge sequence

- · Control of response to edges

- Time measurement resolution of 1 nanosecond

- Accurate current source suitable for capacitive measurement

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock. The CTMU module is ideal for interfacing with capacitive-based sensors.

The CTMU is controlled through two registers: CTMUCON and CTMUICON. CTMUCON enables the module, and controls edge source selection, edge

source polarity selection, and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

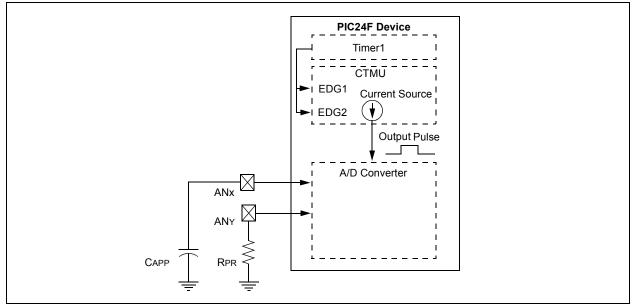

### 25.1 Measuring Capacitance

The CTMU module measures capacitance by generating an output pulse with a width equal to the time between edge events on two separate input channels. The pulse edge events to both input channels can be selected from four sources: two internal peripheral modules (OC1 and Timer1) and two external pins (CTEDG1 and CTEDG2). This pulse is used with the module's precision current source to calculate capacitance according to the relationship:

$$C = I \cdot \frac{dV}{dT}$$

For capacitance measurements, the A/D Converter samples an external capacitor (CAPP) on one of its input channels after the CTMU output's pulse. A precision resistor (RPR) provides current source calibration on a second A/D channel. After the pulse ends, the converter determines the voltage on the capacitor. The actual calculation of capacitance is performed in software by the application.

Figure 25-1 shows the external connections used for capacitance measurements, and how the CTMU and A/D modules are related in this application. This example also shows the edge events coming from Timer1, but other configurations using external edge sources are possible. A detailed discussion on measuring capacitance and time with the CTMU module is provided in the "*PIC24F Family Reference Manual*".

# FIGURE 25-1: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR CAPACITANCE MEASUREMENT

#### REGISTER 26-5: DEVID: DEVICE ID REGISTER

| U-0    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| —      | _      | _      | -      | —      |        |        | —      |