Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 52                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 96K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256gb206t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Pin Diagram – Top View (121-Pin BGA)<sup>(1)</sup>

|   | 1                  | 2                  | 3              | 4         | 5         | 6                | 7         | 8             | 9                  | 10            | 11                 |

|---|--------------------|--------------------|----------------|-----------|-----------|------------------|-----------|---------------|--------------------|---------------|--------------------|

| A | ORE4               | RE3                | RG13           | O<br>RE0  | ORG0      | RF1              |           | O<br>N/C      | RD12               | RD2           | ORD1               |

| в | O<br>N/C           | RG15               | RE2            | O<br>RE1  | O<br>RA7  | O<br>RF0         | O<br>Vcap | RD5           | RD3                | O<br>Vss      | O<br>RC14          |

| с | e<br>RE6           | O<br>Vdd           | RG12           | O<br>RG14 | O<br>RA6  | O<br>N/C         | O<br>RD7  | RD4           | O<br>VDD           | O<br>RC13     | RD11               |

| D | RC1                | RE7                | RE5            | O<br>Vss  | O<br>Vss  | O<br>N/C         | O<br>RD6  | RD13          | RD0                | O<br>n/c      | RD10               |

| Е | O<br>RC4           | RC3                | O<br>RG6       | RC2       | O<br>Vdd  | ORG1             | O<br>N/C  | ORA15         | RD8                | RD9           | RA14               |

| F |                    | O<br>RG8           | O<br>RG9       | O<br>RG7  | O<br>Vss  | O<br>n/c         | O<br>N/C  | O<br>Vdd      | O<br>OSCI/<br>RC12 | O<br>Vss      | O<br>OSCO/<br>RC15 |

| G | RE8                | O<br>RE9           | RA0            | O<br>N/C  | O<br>Vdd  | O<br>Vss         | O<br>Vss  | O<br>N/C      | RA5                | RA3           | O<br>RA4           |

| н | O<br>PGEC3/<br>RB5 | O<br>PGED3/<br>RB4 | O<br>Vss       | O<br>Vdd  | O<br>N/C  | O<br>Vdd         | O<br>n/c  | O<br>VBUS/RF7 | O<br>Vusb          | O<br>D+/RG2   | RA2                |

| J | O<br>RB3           | O<br>RB2           | O<br>PGED2/RB7 | O<br>AVDD | O<br>RB11 | RA1              | O<br>RB12 | O<br>N/C      | O<br>N/C           | RF8           | O<br>D-/RG3        |

| к | O<br>PGEC1/<br>RB1 | O<br>PGED1/<br>RB0 | O<br>RA10      | O<br>RB8  | O<br>N/C  | RF12             | O<br>RB14 | O<br>Vdd      | RD15               | USBID/<br>RF3 | RF2                |

| L | O<br>PGEC2/<br>RB6 | O<br>RA9           | O<br>AVss      | O<br>RB9  | O<br>RB10 | <b>O</b><br>RF13 | O<br>RB13 | O<br>RB15     | <b>R</b> D14       | RF4           | RF5                |

**Note 1:** See Table 3 for complete functional pinout descriptions.

**Legend: RPn** and **RPIn** represent remappable pins for Peripheral Pin Select functions. Shaded pins indicate pins tolerant to up to +5.5V.

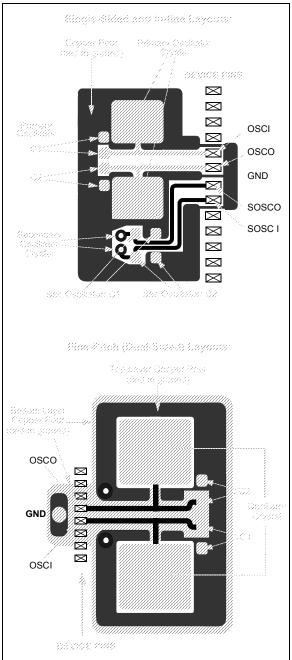

#### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-4. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals in close proximity to the oscillator are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

#### FIGURE 2-4: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| CTBUF         0144         Input Capture 1         Input Capture 2         Input Capture 3         Input Capture 3 <t< th=""><th>ABLE 4</th><th>4-8:</th><th>INPU</th><th>I CAPI</th><th>URE R</th><th>EGISTE</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></t<>                                            | ABLE 4   | 4-8:  | INPU       | I CAPI      | URE R        | EGISTE       |             |          |       |              |               |               |       |          |          |          |          |          |               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|------------|-------------|--------------|--------------|-------------|----------|-------|--------------|---------------|---------------|-------|----------|----------|----------|----------|----------|---------------|

| CICON2       0142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ile Name | Addr  | Bit 15     | Bit 14      | Bit 13       | Bit 12       | Bit 11      | Bit 10   | Bit 9 | Bit 8        | Bit 7         | Bit 6         | Bit 5 | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| C1BUF         0144         Input Capture 1         Input Capture 2         Input Capture 3         Input Capture 3 <t< td=""><td>1CON1</td><td>0140</td><td>_</td><td>_</td><td>ICSIDL</td><td>ICTSEL2</td><td>ICTSEL1</td><td>ICTSEL0</td><td>_</td><td>—</td><td>_</td><td>ICI1</td><td>ICI0</td><td>ICOV</td><td>ICBNE</td><td>ICM2</td><td>ICM1</td><td>ICM0</td><td>0000</td></t<> | 1CON1    | 0140  | _          | _           | ICSIDL       | ICTSEL2      | ICTSEL1     | ICTSEL0  | _     | —            | _             | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| GTMR       0146       input Capture 1 Timer Value Register         GCTMR       0146       —       —       —       ICTSEL2       ICTSEL2       ICTSEL0       —       —       ICT       ICT0       ICOV       ICON       ICON <t< td=""><td>1CON2</td><td>0142</td><td>_</td><td>_</td><td>_</td><td>—</td><td>_</td><td>_</td><td>_</td><td>IC32</td><td>ICTRIG</td><td>TRIGSTAT</td><td>—</td><td>SYNCSEL4</td><td>SYNCSEL3</td><td>SYNCSEL2</td><td>SYNCSEL1</td><td>SYNCSEL0</td><td>000D</td></t<>                                                                                                                                                                                                                                                                                                                                                                   | 1CON2    | 0142  | _          | _           | _            | —            | _           | _        | _     | IC32         | ICTRIG        | TRIGSTAT      | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| C2CON1         0148         —         —         ICSIDL         ICTSEL2         ICTSEL1         ICTSEL0         —         —         ICT         ICD         ICOV         ICBNE         ICAL         ICM         ICAL         ICAL <thi< td=""><td>1BUF</td><td>0144</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>Input Cap</td><td>oture 1 Buffe</td><td>er Register</td><td></td><td></td><td></td><td></td><td></td><td></td><td>0000</td></thi<>                                                                                                                                                                                                                                                                                                          | 1BUF     | 0144  |            |             |              |              |             |          |       | Input Cap    | oture 1 Buffe | er Register   |       |          |          |          |          |          | 0000          |

| C2CON2         014A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1TMR     | 0146  |            |             |              |              |             |          |       | Input Captur | e 1 Timer Va  | alue Register |       |          |          |          |          |          | xxxx          |

| C2BUF         014C         Input Capture 2 Buffer Register           IC2TMR         014E         Input Capture 2 Timer Value Register           IC3CON1         0152         —         —         —         —         —         —         —         —         —         SYNCSEL3                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2CON1    | 0148  | _          | _           | ICSIDL       | ICTSEL2      | ICTSEL1     | ICTSEL0  | _     | _            | _             | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| C2TMR         014E         input Capture 2 Timer Value Register           IC3CON1         0150         -         -         ICSID         ICTSL2         ICTSL1         ICTSL0         -         -         ICI1         ICO         ICON         ICBNE         ICM2         ICM1         ICM2         ICM2         ICM1         ICM2         ICM2         ICM1         ICI3           IC3DCN2         0154         -         -         -         -         -         ICI1         ICI0         ICOV         ICBNE         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL4         SYNCSEL4         SYNCSEL4         SYNCSEL4         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL4         SYNCSEL4         SYNCSEL4         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL4         SYNCSEL4         SYNCSEL4         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL4         SYNCSEL4         SYNCSEL4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2CON2    | 014A  | _          | _           | _            | _            | _           |          | _     | IC32         | ICTRIG        | TRIGSTAT      | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| C3CONT         0150         —         —         ICTSL         ICTSL         ICTSL         ICTSL         ICTSL         ICTSL         ICM2         ICM2         ICM2         ICM2         ICM2         ICM1         ICM2         ICM2         ICM2         ICM2         ICM2         ICM1         ICM2         ICM1         ICM2         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2BUF     | 014C  |            |             |              | •            |             |          |       | Input Cap    | oture 2 Buffe | er Register   |       | •        | •        | •        | •        | •        | 0000          |

| C3CON2       0152          IC32       ICTRIG       TRIGSTAT        SYNCSEL3       SYNCSEL4 <td>2TMR</td> <td>014E</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>Input Captur</td> <td>e 2 Timer Va</td> <td>alue Register</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>xxxx</td>                                                                                                                                                                                                                                                                          | 2TMR     | 014E  |            |             |              |              |             |          |       | Input Captur | e 2 Timer Va  | alue Register |       |          |          |          |          |          | xxxx          |

| C3BUF         0154         Input Capture 3 Buffer Register           IC3TMR         0156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3CON1    | 0150  | _          | _           | ICSIDL       | ICTSEL2      | ICTSEL1     | ICTSEL0  | _     | _            | _             | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| ICSTMR         0156         Input Capture 3 Timer Value Register           IC4CON1         0158         -         -         ICSDL         ICTSEL2         ICTSEL1         ICTSEL0         -         -         IC11         ICO         ICOV         ICBNE         ICM2         ICM1         ICIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3CON2    | 0152  | _          | _           | _            | —            | _           | _        |       | IC32         | ICTRIG        | TRIGSTAT      |       | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC4CON1         0158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3BUF     | 0154  |            |             |              | •            |             |          |       | Input Cap    | oture 3 Buffe | er Register   |       | •        | •        | •        | •        | •        | 0000          |

| IC4CON2       015A       —       —       —       —       —       IC32       ICTRIG       TRIGSTAT       —       SYNCSEL3       SYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3TMR     | 0156  |            |             |              |              |             |          |       | Input Captur | e 3 Timer Va  | alue Register |       |          |          |          |          |          | xxxx          |

| IC4BUF         015C         Input Capture 4 Buffer Register           IC4TMR         015E         Input Capture 4 Timer Value Register           IC5C0N1         0160         —         —         ICSIDL         ICTSEL2         ICTSEL1         ICTSEL0         —         —         IC1         IC10         ICOV         ICBNE         ICM1         ICSON2           IC5C0N2         0162         —         —         —         —         —         IC11         IC10         ICOV         ICBNE         ICM1         ICSCON2           IC5C0N2         0164         —         —         —         —         Input Capture 5 Buffer Register           IC6C0N1         0168         —         —         ICSIDL         ICTSEL2         ICTSEL1         ICTSEL0         —         —         IC11         IC10         ICOV         ICBNE         SYNCSEL2         SYNCSEL3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4CON1    | 0158  | _          | _           | ICSIDL       | ICTSEL2      | ICTSEL1     | ICTSEL0  | _     | _            | _             | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC4TMR       016E       Input Capture 4 Timer Value Register         IC5CON1       0160       -       -       ICSIDL       ICTSEL2       ICTSEL1       ICTSEL0       -       -       IC11       IC10       ICOV       ICBNE       ICM2       ICM1       IC         IC5CON1       0160       -       -       -       -       -       -       SYNCSEL3       SYNCSEL4       SYNCSEL3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4CON2    | 015A  | _          | _           | _            | —            | _           | _        | _     | IC32         | ICTRIG        | TRIGSTAT      | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| ICSCON1       0160       -       -       ICSID       ICTSEL2       ICTSEL1       ICTSEL1       ICTSEL0       -       -       ICI       ICI0       ICOV       ICBNE       ICM2       ICM1       ICM1         ICSCON2       0162       -       -       -       -       -       ICTSEL1       ICTSEL1       ICTSEL1       ICTSEL1       ICTSEL2       ICTSEL2       ICTSEL2       SYNCSEL3       SYNCSEL3 <td< td=""><td>4BUF</td><td>015C</td><td></td><td></td><td></td><td>•</td><td></td><td></td><td></td><td>Input Cap</td><td>oture 4 Buffe</td><td>er Register</td><td></td><td>•</td><td>•</td><td>•</td><td>•</td><td>•</td><td>0000</td></td<>                                                                                                                                                                                                                                                                                        | 4BUF     | 015C  |            |             |              | •            |             |          |       | Input Cap    | oture 4 Buffe | er Register   |       | •        | •        | •        | •        | •        | 0000          |

| ICSCON2       0162       —       —       —       —       —       IC32       ICTRIG       TRIGSTAT       —       SYNCSEL3       SYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4TMR     | 015E  |            |             |              |              |             |          |       | Input Captur | e 4 Timer Va  | alue Register |       |          |          |          |          |          | xxxx          |

| ICSBUF       0164       Input Capture 5 Buffer Register         ICSTMR       0166       Input Capture 5 Timer Value Register         ICSCON1       0168         ICSIDL       ICTSEL2       ICTSEL2       ICTSEL1       ICTSEL0         IC11       IC0       ICOV       ICBNE       ICM2       ICM1       ICM2       ICM1       IC         IC6BUF       0166            IC32       ICTRIG       TRIGSTAT        SYNCSEL3       SYNCSEL2       SYNCSEL2       SYNCSEL3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5CON1    | 0160  | _          | _           | ICSIDL       | ICTSEL2      | ICTSEL1     | ICTSEL0  | _     | _            | _             | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| ICSTMR       0166       Input Capture 5 Timer Value Register         IC6CON1       0168       -       -       ICSIDL       ICTSEL2       ICTSEL1       ICTSEL0       -       -       IC11       ICI0       ICOV       ICBNE       ICM2       ICM1       IC         IC6CON2       016A       -       -       -       -       -       IC11       ICI0       ICOV       ICBNE       ICM2       ICM1       IC         IC6BUF       016C       -       -       -       -       Input Capture 6 Buffer Register       Input Capture 6 Timer Value Register       ICOV       ICBNE       ICM2       ICM1       IC         IC7CON1       0170       -       -       ICSIDL       ICTSEL2       ICTSEL1       ICTSEL0       -       -       IC11       ICI0       ICOV       ICBNE       ICM2       ICM1       ICM2       ICM1       ICCV       ICM2       ICM1       ICM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5CON2    | 0162  |            | _           |              | _            |             |          | _     | IC32         | ICTRIG        | TRIGSTAT      |       | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC6CON1         0168         -         -         IC3DL         ICTSEL2         ICTSEL1         ICTSEL0         -         -         IC11         IC10         ICOV         ICBNE         ICM2         ICM1           IC6C0N2         016A         -         -         -         -         ICTRIG         TRIGSTAT         -         SYNCSEL3         SYNCSEL2         SYNCSEL3         SY                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5BUF     | 0164  |            |             |              | •            |             |          |       | Input Cap    | oture 5 Buffe | er Register   |       | •        | •        | •        | •        | •        | 0000          |

| IC6CON2       016A       —       —       —       —       —       IC32       ICTRIG       TRIGSTAT       —       SYNCSEL3       SYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5TMR     | 0166  |            |             |              |              |             |          |       | Input Captur | e 5 Timer Va  | alue Register |       |          |          |          |          |          | xxxx          |

| IC6BUF       016C       Input Capture 6 Buffer Register         IC6TMR       016E       Input Capture 6 Timer Value Register         IC7CON1       0170       -       -       ICTSEL2       ICTSEL2       ICTSEL1       ICTSEL0       -       -       IC11       IC10       ICOV       ICBNE       ICM2       ICM1       I         IC7CON1       0170       -       -       -       -       -       -       IC12       ICI1       ICI0       ICOV       ICBNE       ICM2       ICM1       I         IC7CON2       0172       -       -       -       -       -       -       -       IC32       ICTRIG       TRIGSTAT       -       SYNCSEL3       SYN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6CON1    | 0168  | _          | _           | ICSIDL       | ICTSEL2      | ICTSEL1     | ICTSEL0  | _     | _            | _             | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| ICGTMR         016E         Input Capture 6 Timer Value Register           ICGTON1         0170         -         -         ICSIDL         ICTSEL2         ICTSEL1         ICTSEL0         -         -         IC11         ICI0         ICOV         ICBNE         ICM2         ICM1         ICM1           IC7CON1         0170         -         -         -         -         IC11         ICI0         ICOV         ICBNE         ICM2         ICM1         ICM1           IC7CON2         0172         -         -         -         -         IC32         ICTRIG         TRIGSTAT         -         SYNCSEL3         SYNCSEL2         SYNCSEL2         SYNCSEL3         SYNCSEL2         SYNCSEL2         SYNCSEL1         SYNCSEL3         SYNCSEL2         SYNCSEL3         SYNCSEL2         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL2         SYNCSEL3         SYNCSEL2         SYNCSEL4         SYNCSEL4         SYNCSEL3         SYNCSEL2         SYNCSEL3         SYNCSEL3         SYNCSEL2         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL3         SYNCSEL2         SYNCSEL3         SYNCSEL3         SYNCSEL2         SYNCSEL3         SYNCSEL3         SYNCSEL2         SYNCSEL3         SYNCSEL3         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6CON2    | 016A  | _          | _           | _            | _            | _           | _        | _     | IC32         | ICTRIG        | TRIGSTAT      | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| ICTCON1         0170         —         ICSIDL         ICTSEL2         ICTSEL1         ICTSEL0         —         —         IC11         IC10         ICOV         ICBNE         ICM2         ICM1         ICM1           IC7CON2         0172         —         —         —         —         —         —         ICTSEL1         ICTSEL2         ICTSEL1         ICTSEL0         —         —         IC11         IC10         ICOV         ICBNE         ICM2         ICM1         ICM1           IC7C0N2         0172         —         —         —         —         —         —         IC32         ICTRIG         TRIGSTAT         —         SYNCSEL3         SYNCSEL2         SYNCSEL1         SYNCSEL3         SYNCSEL2         SYNCSEL1         ICTSUN         ICTSUN         ICTSUN         ICTSEL2         ICTSEL1         ICTSEL0         —         —         —         IC11         IC10         ICOV         ICBNE         ICM2         ICM1         ICM1         ICM2         ICM1         ICM2         ICM1         ICM1         ICM2         ICM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6BUF     | 016C  |            |             |              | •            |             |          |       | Input Cap    | oture 6 Buffe | er Register   |       | •        | •        | •        | •        | •        | 0000          |

| IC7CON2       0172       -       -       -       -       IC32       ICTRIG       TRIGSTAT       -       SYNCSEL3       SYNCSEL2       SYNCSEL2       SYNCSEL3       SYNCSEL2       SYNCSEL3       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6TMR     | 016E  |            |             |              |              |             |          |       | Input Captur | e 6 Timer Va  | alue Register |       |          |          |          |          |          | xxxx          |

| IC7BUF       0174       Input Capture 7 Buffer Register         IC7TMR       0176       Input Capture 7 Timer Value Register         IC8CON1       0178       —       —       ICTSEL2       ICTSEL3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7CON1    | 0170  | _          | _           | ICSIDL       | ICTSEL2      | ICTSEL1     | ICTSEL0  | _     | —            | _             | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC7TMR       0176       Input Capture 7 Timer Value Register         IC8CON1       0178       -       -       ICSIDL       ICTSEL2       ICTSEL1       ICTSEL0       -       -       -       ICI1       ICI0       ICOV       ICBNE       ICM2       ICM1       ICM1         IC8CON1       0178       -       -       ICSIDL       ICTSEL2       ICTSEL1       ICTSEL0       -       -       -       ICI1       ICI0       ICOV       ICBNE       ICM2       ICM1       ICM1         IC8CON2       017A       -       -       -       -       -       -       -       -       SYNCSEL3       SYNCSEL4       SYNCSEL4       SYNCSEL4       SYNCSEL4       SYNCSEL4       SYNCSEL3       SYNCSEL4       SYNCSEL4       SYNCSEL3       SYNCSEL4       SYNCSEL3       SYNCSEL3       SYNCSEL4       SYNCSEL4       SYNCSEL4       SYNCSEL4       SYNCSEL3       SYNCSEL4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7CON2    | 0172  | _          | _           | _            | _            | _           | _        | _     | IC32         | ICTRIG        | TRIGSTAT      | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC8CON1       0178       -       -       ICSIDL       ICTSEL2       ICTSEL1       ICTSEL0       -       -       -       ICI1       ICI0       ICOV       ICBNE       ICM2       ICM1       ICM1         IC8CON2       017A       -       -       -       -       IC32       ICTRIG       TRIGSTAT       -       SYNCSEL3       SYNCSEL2       SYNCSEL3       SYNCSEL4       SYNCSEL4       SYNCSEL4       SYNCSEL4       SYNCSE13       SYNCSEL4       SYNCSE13       SYNCSE14       SYNCSE12       SYNCSE14       SY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7BUF     | 0174  |            |             |              |              |             |          |       | Input Cap    | oture 7 Buffe | er Register   |       |          |          |          |          |          | 0000          |

| IC8CON2       017A       —       —       —       —       —       IC32       ICTRIG       TRIGSTAT       —       SYNCSEL3       SYNCSEL2       SYNCSEL3       SYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7TMR     | 0176  |            |             |              |              |             |          |       | Input Captur | e 7 Timer Va  | alue Register |       |          |          |          |          |          | xxxx          |

| IC8BUF       017C       Input Capture 8 Buffer Register         IC8TMR       017E       Input Capture 8 Buffer Register         IC9CON1       0180       —       —       ICSIDL       ICTSEL2       ICTSEL2       ICTSEL1       ICTSEL0       —       —       —       ICI1       ICI0       ICOV       ICBNE       ICM2       ICM1       ICM1         IC9CON2       0182       —       —       —       —       —       —       IC32       ICTRIG       TRIGSTAT       —       SYNCSEL3       SYNCSEL2       SYNCSEL1       S         IC9BUF       0184                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8CON1    | 0178  | _          | _           | ICSIDL       | ICTSEL2      | ICTSEL1     | ICTSEL0  | _     | _            | _             | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC8TMR       017E       Input Capture 8 Timer Value Register         IC9CON1       0180       —       —       ICSIDL       ICTSEL2       ICTSEL2       ICTSEL1       ICTSEL0       —       —       ICI1       ICI0       ICOV       ICBNE       ICM2       ICM1       ICM1         IC9CON2       0182       —       —       —       —       —       IC32       ICTRIG       TRIGSTAT       —       SYNCSEL3       SYNCSEL2       SYNCSEL1       SYNCSEL1       SYNCSEL4       SYNCSEL3       SYNCSEL2       SYNCSEL1       SYNCSEL3       SYNCSEL4       SYNCSEL4       SYNCSEL3       SYNCSEL2       SYNCSEL1       SYNCSEL4       SYNCSEL5 <t< td=""><td>8CON2</td><td>017A</td><td>—</td><td>_</td><td>—</td><td>_</td><td></td><td></td><td>_</td><td>IC32</td><td>ICTRIG</td><td>TRIGSTAT</td><td></td><td>SYNCSEL4</td><td>SYNCSEL3</td><td>SYNCSEL2</td><td>SYNCSEL1</td><td>SYNCSEL0</td><td>000D</td></t<>                                                                                                                                                                                                                                                                           | 8CON2    | 017A  | —          | _           | —            | _            |             |          | _     | IC32         | ICTRIG        | TRIGSTAT      |       | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC9CON1       0180         ICSIDL       ICTSEL2       ICTSEL1       ICTSEL0         ICI1       ICI0       ICOV       ICBNE       ICM2       ICM1         IC9CON2       0182          IC32       ICTRIG       TRIGSTAT        SYNCSEL4       SYNCSEL3       SYNCSEL2       SYNCSEL1       SYNCSEL4       SYNCSEL3       SYNCSEL4       SYNCSEL3       SYNCSEL1       SYNCSEL4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8BUF     | 017C  |            |             |              |              |             |          |       | Input Cap    | oture 8 Buffe | er Register   |       |          |          |          |          |          | 0000          |

| IC9CON2       0182       —       —       —       —       IC32       ICTRIG       TRIGSTAT       —       SYNCSEL3       SYNCSEL2       SYNCSEL1       SYNCSEL3         IC9BUF       0184                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8TMR     | 017E  |            |             |              |              |             |          |       | Input Captur | e 8 Timer Va  | alue Register |       |          |          |          |          |          | xxxx          |

| IC9BUF     0184     Input Capture 9 Buffer Register       IC9TMR     0186     Input Capture 9 Timer Value Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9CON1    | 0180  | _          | —           | ICSIDL       | ICTSEL2      | ICTSEL1     | ICTSEL0  | _     | _            | —             | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC9TMR 0186 Input Capture 9 Timer Value Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9CON2    | 0182  | _          | _           | —            | —            | —           | _        | _     | IC32         | ICTRIG        | TRIGSTAT      | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9BUF     | 0184  |            |             |              |              |             |          |       | Input Cap    | oture 9 Buffe | er Register   |       |          | •        |          |          | •        | 0000          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9TMR     | 0186  |            |             |              |              |             |          |       | Input Captur | e 9 Timer Va  | alue Register |       |          |          |          |          |          | xxxx          |

| Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | egend:   | — = u | nimplement | ed, read as | '0'. Reset v | alues are sh | own in hexa | decimal. |       |              |               |               |       |          |          |          |          |          | <u> </u>      |

#### **TABLE 4-8:** INPUT CAPTURE REGISTER MAP

#### TABLE 4-21: ADC REGISTER MAP (CONTINUED)

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7                 | Bit 6                 | Bit 5                 | Bit 4                 | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0                 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------------|

| AD1CON1      | 0320 | ADON   | _      | ADSIDL | _      | _      | _      | FORM1  | FORM0  | SSRC2                 | SSRC1                 | SSRC0                 | _                     | _                     | ASAM                  | SAMP                  | DONE                  | 0000          |

| AD1CON2      | 0322 | VCFG2  | VCFG1  | VCFG0  | r      | _      | CSCNA  |        |        | BUFS                  | SMPI4                 | SMPI3                 | SMPI2                 | SMPI1                 | SMPI0                 | BUFM                  | ALTS                  | 0000          |

| AD1CON3      | 0324 | ADRC   | r      | r      | SAMC4  | SAMC3  | SAMC2  | SAMC1  | SAMC0  | ADCS7                 | ADCS6                 | ADCS5                 | ADCS4                 | ADCS3                 | ADCS2                 | ADCS1                 | ADCS0                 | 0000          |

| AD1CHS       | 0328 | CH0NB  | _      | _      | CH0SB4 | CH0SB3 | CH0SB2 | CH0SB1 | CH0SB0 | CH0NA                 | —                     |                       | CH0SA4                | CH0SA3                | CH0SA2                | CH0SA1                | CH0SA0                | 0000          |

| AD1CSSH      | 032E | _      |        |        | _      | CSSL27 | CSSL26 | CSSL25 | CSSL24 | CSSL23 <sup>(1)</sup> | CSSL22 <sup>(1)</sup> | CSSL21 <sup>(1)</sup> | CSSL20 <sup>(1)</sup> | CSSL19 <sup>(1)</sup> | CSSL18 <sup>(1)</sup> | CSSL17 <sup>(1)</sup> | CSSL16 <sup>(1)</sup> | 0000          |

| AD1CSSL      | 0330 | CSSL15 | CSSL14 | CSSL13 | CSSL12 | CSSL11 | CSSL10 | CSSL9  | CSSL8  | CSSL7                 | CSSL6                 | CSSL5                 | CSSL4                 | CSSL3                 | CSSL2                 | CSSL1                 | CSSL0                 | 0000          |

Legend: — = unimplemented, read as '0', r = Reserved, maintain as '0'. Reset values are shown in hexadecimal. Note 1: Unimplemented in 64-pin devices, read as '0'

#### TABLE 4-22: CTMU REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10   | Bit 9   | Bit 8  | Bit 7   | Bit 6    | Bit 5    | Bit 4   | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|------|--------|--------|----------|--------|--------|----------|---------|--------|---------|----------|----------|---------|----------|----------|----------|----------|---------------|

| CTMUCON      | 033C | CTMUEN |        | CTMUSIDL | TGEN   | EDGEN  | EDGSEQEN | IDISSEN | CTTRIG | EDG2POL | EDG2SEL1 | EDG2SEL0 | EDG1POL | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | 0000          |

| CTMUICON     | 033E | ITRIM5 | ITRIM4 | ITRIM3   | ITRIM2 | ITRIM1 | ITRIM0   | IRNG1   | IRNG0  | _       | _        | _        | _       | _        | _        | _        | _        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase blocks of eight rows (512 instructions) at a time and to program one row at a time. It is also possible to program single words.

The 8-row erase blocks and single row write blocks are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using table writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 64 TBLWT instructions are required to write the full row of memory.

To ensure that no data is corrupted during a write, any unused address should be programmed with FFFFFFh. This is because the holding latches reset to an unknown state, so if the addresses are left in the Reset state, they may overwrite the locations on rows which were not rewritten.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing is *not* recommended.

All of the table write operations are single-word writes (2 instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

#### 5.3 JTAG Operation

The PIC24F family supports JTAG boundary scan. Boundary scan can improve the manufacturing process by verifying pin to PCB connectivity.

#### 5.4 Enhanced In-Circuit Serial Programming

Enhanced In-Circuit Serial Programming uses an on-board bootloader, known as the program executive, to manage the programming process. Using an SPI data frame format, the program executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

#### 5.5 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.6 "Programming Operations"** for further details.

#### 5.6 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 6.1 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSC bits in Flash Configuration Word 2 (CW2) (see Table 6-2). The RCFGCAL and NVMCON registers are only affected by a POR.

#### 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. Note that the system Reset signal, SYSRST, is released after the POR delay time expires.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The Fail-Safe Clock Monitor (FSCM) delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

### 6.3 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 8.0 "Oscillator Configuration"** for further details.

| TABLE 6-2: | OSCILLATOR SELECTION vs. |

|------------|--------------------------|

|            | TYPE OF RESET (CLOCK     |

|            | SWITCHING ENABLED)       |

| Reset Type | Clock Source Determinant             |  |  |  |  |

|------------|--------------------------------------|--|--|--|--|

| POR        | FNOSC Configuration bits (CW2<10:8>) |  |  |  |  |

| BOR        |                                      |  |  |  |  |

| MCLR       |                                      |  |  |  |  |

| WDTO       | COSC Control bits<br>(OSCCON<14:12>) |  |  |  |  |

| SWR        | (000001(11.12))                      |  |  |  |  |

| U-0          | R/W-0                 | U-0                                 | U-0              | U-0              | U-0              | U-0              | U-0        |

|--------------|-----------------------|-------------------------------------|------------------|------------------|------------------|------------------|------------|

| _            | RTCIE                 |                                     | _                | _                | _                | _                |            |

| bit 15       |                       | •                                   |                  |                  |                  |                  | bit        |

|              |                       |                                     |                  |                  |                  |                  |            |

| U-0          | R/W-0                 | R/W-0                               | U-0              | U-0              | R/W-0            | R/W-0            | U-0        |

| —            | INT4IE <sup>(1)</sup> | INT3IE <sup>(1)</sup>               |                  | —                | MI2C2IE          | SI2C2IE          | —          |

| bit 7        |                       |                                     |                  |                  |                  |                  | bit        |

|              |                       |                                     |                  |                  |                  |                  |            |

| Legend:      |                       |                                     |                  |                  |                  |                  |            |

| R = Readal   |                       | W = Writable                        | bit              | •                | mented bit, read |                  |            |

| -n = Value a | at POR                | '1' = Bit is set                    |                  | '0' = Bit is cle | ared             | x = Bit is unkno | own        |

|              |                       |                                     |                  |                  |                  |                  |            |

| bit 15       | -                     | ted: Read as 'o                     |                  |                  |                  |                  |            |

| bit 14       |                       | Time Clock/Ca                       | •                | t Enable bit     |                  |                  |            |

|              |                       | request is enat                     |                  |                  |                  |                  |            |

|              | •                     | request is not e                    |                  |                  |                  |                  |            |

| bit 13-7     | -                     | ted: Read as '                      |                  |                  |                  |                  |            |

| bit 6        |                       | nal Interrupt 4                     |                  |                  |                  |                  |            |

|              |                       | request is enat<br>request is not e |                  |                  |                  |                  |            |

| bit 5        | •                     | nal Interrupt 3                     |                  |                  |                  |                  |            |

|              |                       | request is enat                     |                  |                  |                  |                  |            |

|              |                       | request is not e                    |                  |                  |                  |                  |            |

| bit 4-3      | Unimplemen            | ted: Read as '                      | )'               |                  |                  |                  |            |

| bit 2        | MI2C2IE: Mas          | ster I2C2 Even                      | t Interrupt Enal | ble bit          |                  |                  |            |

|              | 1 = Interrupt         | request is enat                     | led              |                  |                  |                  |            |

|              | 0 = Interrupt         | request is not e                    | enabled          |                  |                  |                  |            |

| bit 1        | SI2C2IE: Slav         | ve I2C2 Event I                     | nterrupt Enabl   | e bit            |                  |                  |            |

|              |                       | request is enat                     |                  |                  |                  |                  |            |

|              | •                     | request is not e                    |                  |                  |                  |                  |            |