Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 84                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 96K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                     |

| Data Converters            | A/D 24x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 121-TFBGA                                                                       |

| Supplier Device Package    | 121-TFBGA (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256gb210t-i-bg |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | Pin Number         |                 |                | Immut |                 |                                               |  |

|----------|--------------------|-----------------|----------------|-------|-----------------|-----------------------------------------------|--|

| Function | 64-Pin<br>TQFP/QFN | 100-Pin<br>TQFP | 121-Pin<br>BGA | I/O   | Input<br>Buffer | Description                                   |  |

| RG0      | —                  | 90              | A5             | I/O   | ST              |                                               |  |

| RG1      |                    | 89              | E6             | I/O   | ST              |                                               |  |

| RG2      | 37                 | 57              | H10            | I/O   | ST              |                                               |  |

| RG3      | 36                 | 56              | J11            | I/O   | ST              |                                               |  |

| RG6      | 4                  | 10              | E3             | I/O   | ST              |                                               |  |

| RG7      | 5                  | 11              | F4             | I/O   | ST              |                                               |  |

| RG8      | 6                  | 12              | F2             | I/O   | ST              | PORTG Digital I/O.                            |  |

| RG9      | 8                  | 14              | F3             | I/O   | ST              |                                               |  |

| RG12     | _                  | 96              | C3             | I/O   | ST              |                                               |  |

| RG13     | _                  | 97              | A3             | I/O   | ST              |                                               |  |

| RG14     | _                  | 95              | C4             | I/O   | ST              |                                               |  |

| RG15     | _                  | 1               | B2             | I/O   | ST              |                                               |  |

| RP0      | 16                 | 25              | K2             | I/O   | ST              |                                               |  |

| RP1      | 15                 | 24              | K1             | I/O   | ST              |                                               |  |

| RP2      | 42                 | 68              | E9             | I/O   | ST              |                                               |  |

| RP3      | 44                 | 70              | D11            | I/O   | ST              |                                               |  |

| RP4      | 43                 | 69              | E10            | I/O   | ST              |                                               |  |

| RP5      | _                  | 48              | K9             | I/O   | ST              |                                               |  |

| RP6      | 17                 | 26              | L1             | I/O   | ST              |                                               |  |

| RP7      | 18                 | 27              | J3             | I/O   | ST              |                                               |  |

| RP8      | 21                 | 32              | K4             | I/O   | ST              |                                               |  |

| RP9      | 22                 | 33              | L4             | I/O   | ST              | Demonstration Device and (manufacture events) |  |

| RP10     | 31                 | 49              | L10            | I/O   | ST              | Remappable Peripheral (input or output).      |  |

| RP11     | 46                 | 72              | D9             | I/O   | ST              |                                               |  |

| RP12     | 45                 | 71              | C11            | I/O   | ST              |                                               |  |

| RP13     | 14                 | 23              | J2             | I/O   | ST              |                                               |  |

| RP14     | 29                 | 43              | K7             | I/O   | ST              |                                               |  |

| RP15     | —                  | 53              | J10            | I/O   | ST              |                                               |  |

| RP16     | 33                 | 51              | K10            | I/O   | ST              |                                               |  |

| RP17     | 32                 | 50              | L11            | I/O   | ST              |                                               |  |

| RP18     | 11                 | 20              | H1             | I/O   | ST              |                                               |  |

| RP19     | 6                  | 12              | F2             | I/O   | ST              |                                               |  |

| Legend:  | TTL = TTL inpu     | ut buffer       |                |       | ST =            | Schmitt Trigger input buffer                  |  |

### TABLE 1-3: PIC24FJ256GB210 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

ANA = Analog level input/output

ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

**Note 1:** The alternate EPMP pins are selected when the ALTPMP (CW3<12>) bit is programmed to '0'.

2: The PMSC2 signal will replace the PMA15 signal on the 15-pin PMA when CSF<1:0> = 01 or 10.

3: The PMCS1 signal will replace the PMA14 signal on the 14-pin PMA when CSF<1:0> = 10.

4: The alternate VREF pins selected when the ALTVREF (CW1<5>) bit is programmed to '0'.

The CORCON register contains the IPL3 bit, which, together with IPL<2:0>, indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

The interrupt controller has the Interrupt Controller Test register, INTTREG, which displays the status of the interrupt controller. When an interrupt request occurs, it's associated vector number and the new interrupt priority level are latched into INTTREG. This information can be used to determine a specific interrupt source if a generic ISR is used for multiple vectors (such as when ISR remapping is used in bootloader applications) or to check if another interrupt is pending while in an ISR.

All interrupt registers are described in Register 7-1 through Register 7-38 in the succeeding pages.

### REGISTER 7-1: SR: ALU STATUS REGISTER (IN CPU)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC          |

|--------|-----|-----|-----|-----|-----|-----|-------------------|

| —      | —   | —   | _   | —   | —   | —   | DC <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8             |

| R/W-0, HSC            | R/W-0, HSC            | R/W-0, HSC            | R-0, HSC          | R/W-0, HSC       | R/W-0, HSC        | R/W-0, HSC       | R/W-0, HSC       |

|-----------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|------------------|

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | 0V <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                 |                       |                       |                   |                  |                   |                  | bit 0            |

| Legend:           | HSC = Hardware Settal | HSC = Hardware Settable/Clearable bit |                                    |  |  |  |

|-------------------|-----------------------|---------------------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit                 | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                  | x = Bit is unknown                 |  |  |  |

### bit 15-9 Unimplemented: Read as '0'

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>                   |

|---------|---------------------------------------------------------------------------------------|

|         | 111 = CPU interrupt priority level is 7 (15); user interrupts are disabled            |

|         | 110 = CPU interrupt priority level is 6 (14)                                          |

|         | 101 = CPU interrupt priority level is 5 (13)                                          |

|         | 100 = CPU interrupt priority level is 4 (12)                                          |

|         | 011 = CPU interrupt priority level is 3 (11)                                          |

|         | 010 = CPU interrupt priority level is 2 (10)                                          |

|         | 001 = CPU interrupt priority level is 1 (9)                                           |

|         | 000 = CPU interrupt priority level is 0 (8)                                           |

| Note 1: | See Register 3-1 for the description of the remaining bits (bits 8, 4, 3, 2, 1 and 0) |

- **Note 1:** See Register 3-1 for the description of the remaining bits (bits 8, 4, 3, 2, 1 and 0) that are not dedicated to interrupt control functions.

- **2:** The IPL bits are concatenated with the IPL3 (CORCON<3>) bit to form the CPU interrupt priority level. The value in parentheses indicates the interrupt priority level if IPL3 = 1.

- **3:** The IPL Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

### REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | R/W-0, HS | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----------|-----|-----|-----|-----|-----|-------|

| —      | RTCIF     | —   | —   | _   | —   | —   | —     |

| bit 15 |           |     |     |     |     |     | bit 8 |

| U-0   | R/W-0, HS | R/W-0, HS | U-0 | U-0 | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----------|-----------|-----|-----|-----------|-----------|-------|

| —     | INT4IF    | INT3IF    | —   | —   | MI2C2IF   | SI2C2IF   | —     |

| bit 7 |           |           |     |     |           |           | bit 0 |

| Legend:           | HS = Hardware Settable | HS = Hardware Settable bit                          |                    |  |  |  |

|-------------------|------------------------|-----------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit       | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |

| bit 15   | Unimplemented: Read as '0'                                |

|----------|-----------------------------------------------------------|

| bit 14   | RTCIF: Real-Time Clock/Calendar Interrupt Flag Status bit |

|          | 1 = Interrupt request has occurred                        |

|          | 0 = Interrupt request has not occurred                    |

| bit 13-7 | Unimplemented: Read as '0'                                |

| bit 6    | INT4IF: External Interrupt 4 Flag Status bit              |

|          | 1 = Interrupt request has occurred                        |

|          | 0 = Interrupt request has not occurred                    |

| bit 5    | INT3IF: External Interrupt 3 Flag Status bit              |

|          | 1 = Interrupt request has occurred                        |

|          | 0 = Interrupt request has not occurred                    |

| bit 4-3  | Unimplemented: Read as '0'                                |

| bit 2    | MI2C2IF: Master I2C2 Event Interrupt Flag Status bit      |

|          | 1 = Interrupt request has occurred                        |

|          | 0 = Interrupt request has not occurred                    |

| bit 1    | SI2C2IF: Slave I2C2 Event Interrupt Flag Status bit       |

|          | 1 = Interrupt request has occurred                        |

|          | 0 = Interrupt request has not occurred                    |

| bit 0    | Unimplemented: Read as '0'                                |

### REGISTER 7-29: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

| U-0          | U-0                                                        | U-0                | U-0              | U-0              | R/W-1            | R/W-0           | R/W-0    |

|--------------|------------------------------------------------------------|--------------------|------------------|------------------|------------------|-----------------|----------|

|              |                                                            | —                  |                  | _                | MI2C2IP2         | MI2C2IP1        | MI2C2IP0 |

| bit 15       |                                                            |                    |                  |                  |                  |                 | bit 8    |

|              |                                                            |                    |                  |                  |                  |                 |          |

| U-0          | R/W-1                                                      | R/W-0              | R/W-0            | U-0              | U-0              | U-0             | U-0      |

|              | SI2C2IP2                                                   | SI2C2IP1           | SI2C2IP0         | —                | _                | _               | _        |

| bit 7        |                                                            |                    |                  |                  |                  |                 | bit 0    |

|              |                                                            |                    |                  |                  |                  |                 |          |

| Legend:      |                                                            |                    |                  |                  |                  |                 |          |

| R = Readab   | le bit                                                     | W = Writable       | bit              | U = Unimplen     | nented bit, read | d as '0'        |          |

| -n = Value a | t POR                                                      | '1' = Bit is set   |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown     |

| L: 4 C 44    |                                                            |                    | o'               |                  |                  |                 |          |

| bit 15-11    | -                                                          | ted: Read as '     |                  |                  |                  |                 |          |

| bit 10-8     |                                                            | >: Master I2C2     | •                | •                |                  |                 |          |

|              | 111 = Interru                                              | pt is priority 7 ( | highest priority | interrupt)       |                  |                 |          |

|              | •                                                          |                    |                  |                  |                  |                 |          |

|              | •                                                          |                    |                  |                  |                  |                 |          |

|              |                                                            | pt is priority 1   |                  |                  |                  |                 |          |

|              |                                                            | ipt source is dis  |                  |                  |                  |                 |          |

| bit 7        | -                                                          | ted: Read as '     |                  |                  |                  |                 |          |

| bit 6-4      | SI2C2IP<2:0                                                | >: Slave I2C2 E    | Event Interrupt  | Priority bits    |                  |                 |          |

|              | 111 = Interrupt is priority 7 (highest priority interrupt) |                    |                  |                  |                  |                 |          |

| •            |                                                            |                    |                  |                  |                  |                 |          |

|              | •                                                          |                    |                  |                  |                  |                 |          |

|              |                                                            | pt is priority 1   |                  |                  |                  |                 |          |

|              | 000 = Interru                                              | ipt source is dis  | abled            |                  |                  |                 |          |

| bit 3-0      | Unimplemen                                                 | ted: Read as '     | 0'               |                  |                  |                 |          |

|              |                                                            |                    |                  |                  |                  |                 |          |

### 7.4 Interrupt Setup Procedures

### 7.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS (INTCON1<15>) control bit if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |

|-------|-------------------------------------------|

|       | initialized, such that all user interrupt |

|       | sources are assigned to Priority Level 4. |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

## 7.4.2 INTERRUPT SERVICE ROUTINE (ISR)

The method that is used to declare an Interrupt Service Routine (ISR) and initialize the IVT with the correct vector address will depend on the programming language (i.e., 'C' or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

### 7.4.3 TRAP SERVICE ROUTINE (TSR)

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value 0Eh with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Levels 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels, 1-6, for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

### REGISTER 8-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| R/W-0         | U-0                                                                                                                  | R/W-0                                                                                                                                                                            | R/W-0                                                                                                                 | R/W-0             | R/W-0            | R/W-0            | R/W-0     |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|-----------|--|--|

| ROEN          |                                                                                                                      | ROSSLP                                                                                                                                                                           | ROSEL <sup>(1)</sup>                                                                                                  | RODIV3            | RODIV2           | RODIV1           | RODIV0    |  |  |

| bit 15        |                                                                                                                      |                                                                                                                                                                                  |                                                                                                                       |                   |                  |                  | bit 8     |  |  |

| U-0           | U-0                                                                                                                  | U-0                                                                                                                                                                              | U-0                                                                                                                   | U-0               | U-0              | U-0              | U-0       |  |  |

| _             | _                                                                                                                    | _                                                                                                                                                                                | _                                                                                                                     | —                 | _                | _                | _         |  |  |

| bit 7         |                                                                                                                      |                                                                                                                                                                                  |                                                                                                                       |                   |                  |                  | bit (     |  |  |

| Legend:       |                                                                                                                      |                                                                                                                                                                                  |                                                                                                                       |                   |                  |                  |           |  |  |

| R = Readable  | e bit                                                                                                                | W = Writable                                                                                                                                                                     | bit                                                                                                                   | U = Unimplem      | nented bit, read | 1 as '0'         |           |  |  |

| -n = Value at | POR                                                                                                                  | '1' = Bit is set                                                                                                                                                                 |                                                                                                                       | '0' = Bit is clea | ared             | x = Bit is unkr  | iown      |  |  |

| bit 15        | ROEN: Refer                                                                                                          | ence Oscillator                                                                                                                                                                  | Output Enable                                                                                                         | bit               |                  |                  |           |  |  |

|               |                                                                                                                      | e oscillator is e<br>coscillator is d                                                                                                                                            |                                                                                                                       | O pin             |                  |                  |           |  |  |

| bit 14        | Unimplemen                                                                                                           | ted: Read as '                                                                                                                                                                   | )'                                                                                                                    |                   |                  |                  |           |  |  |

| bit 13        | <b>ROSSLP:</b> Reference Oscillator Output Stop in Sleep bit                                                         |                                                                                                                                                                                  |                                                                                                                       |                   |                  |                  |           |  |  |

|               | 1 = Reference oscillator continues to run in Sleep                                                                   |                                                                                                                                                                                  |                                                                                                                       |                   |                  |                  |           |  |  |

|               | 0 = Reference oscillator is disabled in Sleep                                                                        |                                                                                                                                                                                  |                                                                                                                       |                   |                  |                  |           |  |  |

| bit 12        | <b>ROSEL:</b> Reference Oscillator Source Select bit <sup>(1)</sup>                                                  |                                                                                                                                                                                  |                                                                                                                       |                   |                  |                  |           |  |  |

|               |                                                                                                                      | oscillator is use<br>clock is used as                                                                                                                                            |                                                                                                                       |                   | eflects any cloc | k switching of t | he device |  |  |

| bit 11-8      |                                                                                                                      |                                                                                                                                                                                  |                                                                                                                       |                   | 5                | 0                |           |  |  |

|               | <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divisor Select bits<br>1111 = Base clock value divided by 32,768       |                                                                                                                                                                                  |                                                                                                                       |                   |                  |                  |           |  |  |

|               | 1110 = Base                                                                                                          | e clock value di                                                                                                                                                                 | vided by 16,38                                                                                                        | 4                 |                  |                  |           |  |  |

|               |                                                                                                                      | e clock value di                                                                                                                                                                 |                                                                                                                       |                   |                  |                  |           |  |  |

|               | 1100 = Base clock value divided by 4,096                                                                             |                                                                                                                                                                                  |                                                                                                                       |                   |                  |                  |           |  |  |

|               | 1011 = Base clock value divided by 2,048<br>1010 = Base clock value divided by 1,024                                 |                                                                                                                                                                                  |                                                                                                                       |                   |                  |                  |           |  |  |

|               | 1001 = Base clock value divided by 512                                                                               |                                                                                                                                                                                  |                                                                                                                       |                   |                  |                  |           |  |  |

|               |                                                                                                                      |                                                                                                                                                                                  |                                                                                                                       |                   |                  |                  |           |  |  |

|               | 1001 = Base                                                                                                          |                                                                                                                                                                                  | vided by 512                                                                                                          |                   |                  |                  |           |  |  |

|               | 1001 = Base<br>1000 = Base<br>0111 = Base                                                                            | e clock value di<br>e clock value di<br>e clock value di                                                                                                                         | vided by 512<br>vided by 256<br>vided by 128                                                                          |                   |                  |                  |           |  |  |

|               | 1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base                                                             | e clock value di<br>e clock value di<br>e clock value di<br>e clock value di                                                                                                     | vided by 512<br>vided by 256<br>vided by 128<br>vided by 64                                                           |                   |                  |                  |           |  |  |

|               | 1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base                                              | e clock value di<br>e clock value di                                                             | vided by 512<br>vided by 256<br>vided by 128<br>vided by 64<br>vided by 32                                            |                   |                  |                  |           |  |  |

|               | 1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base<br>0100 = Base                               | e clock value di<br>e clock value di                                         | vided by 512<br>vided by 256<br>vided by 128<br>vided by 64<br>vided by 32<br>vided by 16                             |                   |                  |                  |           |  |  |

|               | 1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base<br>0100 = Base<br>0011 = Base                | e clock value di<br>e clock value di                                         | vided by 512<br>vided by 256<br>vided by 128<br>vided by 64<br>vided by 32<br>vided by 16<br>vided by 8               |                   |                  |                  |           |  |  |

|               | 1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base<br>0100 = Base<br>0011 = Base<br>0010 = Base | e clock value di<br>e clock value di                     | vided by 512<br>vided by 256<br>vided by 128<br>vided by 64<br>vided by 32<br>vided by 16<br>vided by 8<br>vided by 4 |                   |                  |                  |           |  |  |

|               | 1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base<br>0100 = Base<br>0011 = Base<br>0010 = Base | e clock value di<br>e clock value di | vided by 512<br>vided by 256<br>vided by 128<br>vided by 64<br>vided by 32<br>vided by 16<br>vided by 8<br>vided by 4 |                   |                  |                  |           |  |  |

**Note 1:** Note that the crystal oscillator must be enabled using the FOSC<2:0> bits; the crystal maintains the operation in Sleep mode.

### 10.4.3.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains two 6-bit fields, with each field being associated with one RPn pin (see Register 10-29 through Register 10-44). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-4).

Because of the mapping technique, the list of peripherals for output mapping also includes a null value of '000000'. This permits any given pin to remain disconnected from the output of any of the pin-selectable peripherals.

| <b>TABLE 10-4</b> : | SELECTABLE OUTPUT SOURCES ( | (MAPS FUNCTION TO OUTPUT) |

|---------------------|-----------------------------|---------------------------|

|                     |                             |                           |

| Output Function Number <sup>(1)</sup> | Function             | Output Name              |

|---------------------------------------|----------------------|--------------------------|

| 0                                     | NULL <sup>(2)</sup>  | Null                     |

| 1                                     | C1OUT                | Comparator 1 Output      |

| 2                                     | C2OUT                | Comparator 2 Output      |

| 3                                     | U1TX                 | UART1 Transmit           |

| 4                                     | U1RTS <sup>(3)</sup> | UART1 Request To Send    |

| 5                                     | U2TX                 | UART2 Transmit           |

| 6                                     | U2RTS <sup>(3)</sup> | UART2 Request To Send    |

| 7                                     | SDO1                 | SPI1 Data Output         |

| 8                                     | SCK10UT              | SPI1 Clock Output        |

| 9                                     | SS1OUT               | SPI1 Slave Select Output |

| 10                                    | SDO2                 | SPI2 Data Output         |

| 11                                    | SCK2OUT              | SPI2 Clock Output        |

| 12                                    | SS2OUT               | SPI2 Slave Select Output |

| 18                                    | OC1                  | Output Compare 1         |

| 19                                    | OC2                  | Output Compare 2         |

| 20                                    | OC3                  | Output Compare 3         |

| 21                                    | OC4                  | Output Compare 4         |

| 22                                    | OC5                  | Output Compare 5         |

| 23                                    | OC6                  | Output Compare 6         |

| 24                                    | OC7                  | Output Compare 7         |

| 25                                    | OC8                  | Output Compare 8         |

| 28                                    | U3TX                 | UART3 Transmit           |

| 29                                    | U3RTS <sup>(3)</sup> | UART3 Request To Send    |

| 30                                    | U4TX                 | UART4 Transmit           |

| 31                                    | U4RTS <sup>(3)</sup> | UART4 Request To Send    |

| 32                                    | SDO3                 | SPI3 Data Output         |

| 33                                    | SCK3OUT              | SPI3 Clock Output        |

| 34                                    | SS3OUT               | SPI3 Slave Select Output |

| 35                                    | OC9                  | Output Compare 9         |

| 36                                    | C3OUT                | Comparator 3 Output      |

| 37-63                                 | (unused)             | NC                       |

**Note 1:** Setting the RPORx register with the listed value assigns that output function to the associated RPn pin.

2: The NULL function is assigned to all RPn outputs at device Reset and disables the RPn output function.

3: IrDA<sup>®</sup> BCLK functionality uses this output.

NOTES:

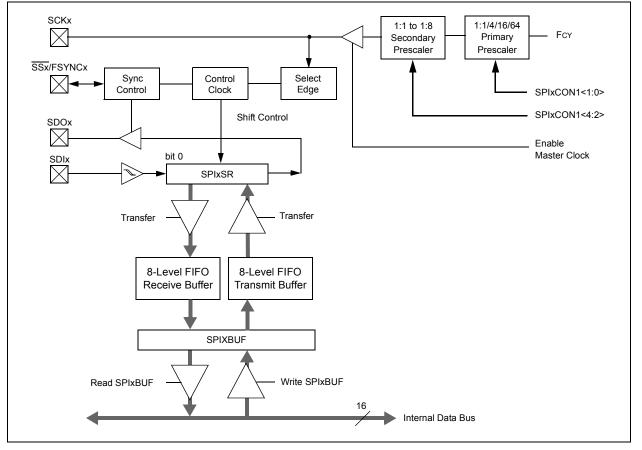

To set up the SPI module for the Enhanced Buffer Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Select Enhanced Buffer mode by setting the SPIBEN bit (SPIxCON2<0>).

- Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

- 6. Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPI module for the Enhanced Buffer Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Select Enhanced Buffer mode by setting the SPIBEN bit (SPIxCON2<0>).

- 8. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

### FIGURE 15-2: SPIX MODULE BLOCK DIAGRAM (ENHANCED MODE)

| R/W-0         | R/W-0        | R/W-0                                  | U-0            | U-0                          | U-0             | U-0             | U-0    |

|---------------|--------------|----------------------------------------|----------------|------------------------------|-----------------|-----------------|--------|

| FRMEN         | SPIFSD       | SPIFPOL                                | _              | —                            | _               | _               | —      |

| bit 15        | ÷            |                                        |                |                              |                 | Ŀ               | bit 8  |

|               |              |                                        |                |                              |                 |                 |        |

| U-0           | U-0          | U-0                                    | U-0            | U-0                          | U-0             | R/W-0           | R/W-0  |

| _             |              |                                        | _              | <u> </u>                     | —               | SPIFE           | SPIBEN |

| bit 7         |              |                                        |                |                              |                 |                 | bit C  |

|               |              |                                        |                |                              |                 |                 |        |

| Legend:       |              |                                        |                |                              |                 |                 |        |

| R = Readabl   | le bit       | W = Writable b                         | it             | U = Unimplen                 | nented bit, rea | ıd as '0'       |        |

| -n = Value at | POR          | '1' = Bit is set                       |                | '0' = Bit is clea            | ared            | x = Bit is unki | nown   |

|               |              |                                        |                |                              |                 |                 |        |

| bit 15        |              | med SPIx Suppo                         |                |                              |                 |                 |        |

|               |              | SPIx support is e<br>SPIx support is c |                |                              |                 |                 |        |

| bit 14        |              | me Sync Pulse [                        |                | trol on $\overline{SSx}$ Pin | bit             |                 |        |

|               |              | ync pulse input (                      |                |                              | 2.1             |                 |        |

|               |              | nc pulse output                        |                |                              |                 |                 |        |

| bit 13        | SPIFPOL: Fr  | ame Sync Pulse                         | Polarity bit ( | Frame mode or                | ıly)            |                 |        |

|               |              | ync pulse is activ                     |                |                              |                 |                 |        |

|               | 0 = Frame sy | ync pulse is activ                     | ve-low         |                              |                 |                 |        |

| bit 12-2      | Unimplemen   | ted: Read as '0                        | ,              |                              |                 |                 |        |

| bit 1         | SPIFE: Fram  | e Sync Pulse Ed                        | lge Select bit |                              |                 |                 |        |

|               | -            | ync pulse coincio                      |                |                              |                 |                 |        |

|               | -            | /nc pulse preced                       |                | it clock                     |                 |                 |        |

| bit 0         |              | nanced Buffer Er                       |                |                              |                 |                 |        |

|               |              | d buffer is enabl                      |                | modo)                        |                 |                 |        |

|               | 0 = Enhance  | d buffer is disab                      | led (Legacy r  | mode)                        |                 |                 |        |

### REGISTER 15-3: SPIxCON2: SPIx CONTROL REGISTER 2

DS39975A-page 218

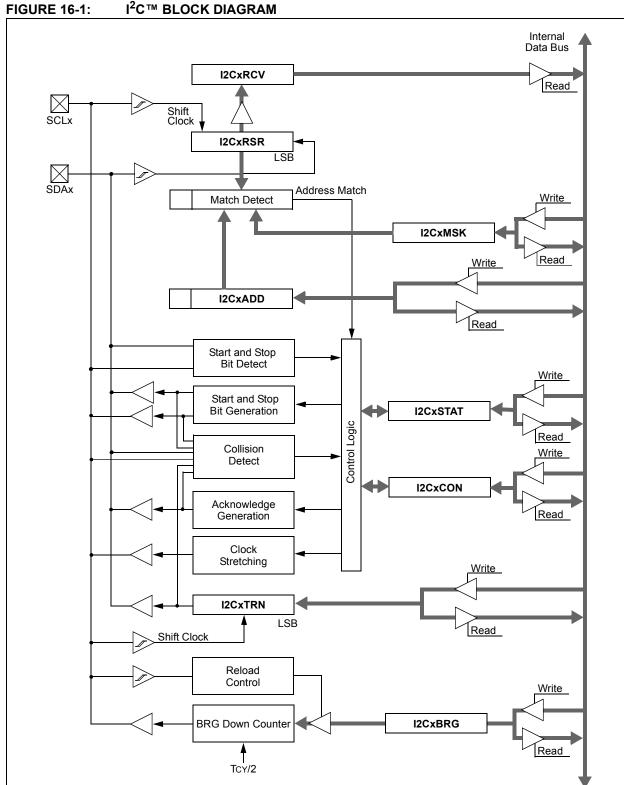

### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 4 | P: Stop bit                                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Stop bit has been detected last                                                                                       |

|       | 0 = Stop bit was not detected last                                                                                                         |

|       | Hardware is set or clear when Start, Repeated Start or Stop is detected.                                                                   |

| bit 3 | S: Start bit                                                                                                                               |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul> |

|       | Hardware is set or clear when Start, Repeated Start or Stop is detected.                                                                   |

| bit 2 | <b>R/W</b> : Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                         |

|       | 1 = Read – indicates data transfer is output from the slave                                                                                |

|       | 0 = Write – indicates data transfer is input to the slave                                                                                  |

|       | Hardware is set or clear after the reception of an I <sup>2</sup> C device address byte.                                                   |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                        |

|       | 1 = Receive is complete, I2CxRCV is full                                                                                                   |

|       | 0 = Receive not complete, I2CxRCV is empty                                                                                                 |

|       | Hardware is set when I2CxRCV is written with the received byte; hardware is clear when the software<br>reads I2CxRCV.                      |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                       |

|       | 1 = Transmit is in progress, I2CxTRN is full                                                                                               |

|       |                                                                                                                                            |

0 = Transmit is complete, I2CxTRN is empty

Hardware is set when software writes to I2CxTRN; hardware is clear at the completion of data transmission.

| R/W-0                 | U-0               | R/W-0                                                                                                                  | R/W-0               | R/W-0             | U-0              | R/W-0              | R/W-0             |  |

|-----------------------|-------------------|------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|------------------|--------------------|-------------------|--|

| UARTEN <sup>(1)</sup> | _                 | USIDL                                                                                                                  | IREN <sup>(2)</sup> | RTSMD             | _                | UEN1               | UEN0              |  |

| bit 15                |                   | 1                                                                                                                      |                     |                   |                  |                    | bit 8             |  |

|                       |                   |                                                                                                                        |                     |                   |                  |                    |                   |  |

| R/W-0, HC             | R/W-0             | R/W-0, HC                                                                                                              | R/W-0               | R/W-0             | R/W-0            | R/W-0              | R/W-0             |  |

| WAKE                  | LPBACK            | ABAUD                                                                                                                  | RXINV               | BRGH              | PDSEL1           | PDSEL0             | STSEL             |  |

| bit 7                 |                   |                                                                                                                        |                     |                   |                  |                    | bit 0             |  |

|                       |                   |                                                                                                                        |                     |                   |                  |                    |                   |  |

| Legend:               |                   | HC = Hardwar                                                                                                           |                     |                   |                  |                    |                   |  |

| R = Readab            |                   | W = Writable b                                                                                                         | it                  | •                 | nented bit, read |                    |                   |  |

| -n = Value a          | t POR             | '1' = Bit is set                                                                                                       |                     | '0' = Bit is clea | ared             | x = Bit is unkn    | own               |  |

|                       |                   | RTx Enable bit <sup>(</sup>                                                                                            | 1)                  |                   |                  |                    |                   |  |

| bit 15                |                   | s enabled; all UA                                                                                                      |                     | controlled by U   | APTy as define   | ad by LIEN < 1.05  |                   |  |

|                       |                   | disabled; all UA                                                                                                       |                     |                   |                  |                    |                   |  |

| bit 14                | Unimplemen        | ted: Read as '0                                                                                                        |                     |                   |                  |                    |                   |  |

| bit 13                | USIDL: Stop       | in Idle Mode bit                                                                                                       |                     |                   |                  |                    |                   |  |

|                       |                   | ue module oper                                                                                                         |                     |                   | e mode           |                    |                   |  |

|                       |                   | module operation                                                                                                       |                     |                   |                  |                    |                   |  |

| bit 12                |                   | Encoder and De                                                                                                         |                     |                   |                  |                    |                   |  |

|                       |                   | oder and decode                                                                                                        |                     |                   |                  |                    |                   |  |

| bit 11                |                   | le Selection for $\overline{I}$                                                                                        |                     |                   |                  |                    |                   |  |

|                       |                   | in is in Simplex                                                                                                       |                     |                   |                  |                    |                   |  |

|                       |                   | in is in Flow Cor                                                                                                      |                     |                   |                  |                    |                   |  |

| bit 10                | Unimplemen        | ted: Read as '0                                                                                                        |                     |                   |                  |                    |                   |  |

| bit 9-8               |                   | ARTx Enable bi                                                                                                         |                     |                   |                  |                    |                   |  |

|                       |                   | UxRX and BCLM<br>UxRX, UxCTS a                                                                                         |                     |                   |                  | controlled by po   | ort latches       |  |

|                       |                   | UxRX and UxRT                                                                                                          |                     |                   |                  | controlled by po   | ort latches       |  |

|                       |                   | ind UxRX pins a                                                                                                        |                     |                   |                  |                    |                   |  |

|                       | latches           |                                                                                                                        |                     | <u> </u>          |                  |                    |                   |  |

| bit 7                 |                   | -up on Start Bit                                                                                                       | •                   | •                 |                  | the folling edge   | hit is alcored    |  |

|                       |                   | vill continue to sa<br>are on the follow                                                                               |                     |                   | is generated or  | i the railing edge | e, dit is cleared |  |

|                       |                   | -up is enabled                                                                                                         |                     | -                 |                  |                    |                   |  |

| bit 6                 | LPBACK: UA        | RTx Loopback                                                                                                           | Mode Select b       | bit               |                  |                    |                   |  |

|                       |                   | oopback mode                                                                                                           |                     |                   |                  |                    |                   |  |

|                       |                   | k mode is disabl                                                                                                       |                     |                   |                  |                    |                   |  |

| bit 5                 |                   | p-Baud Enable b                                                                                                        |                     | o novt characte   | r roquiroo ro    | contion of a av    | na fiold (EEb):   |  |

|                       |                   | aud rate measun<br>hardware upor                                                                                       |                     |                   | er – requires re | ception of a sy    |                   |  |

|                       |                   | e measurement                                                                                                          |                     | completed         |                  |                    |                   |  |

| Note 1: If            | UARTEN = 1        | the peripheral in                                                                                                      | puts and outp       | uts must be cor   | nfigured to an a | vailable RPn/RI    | PIn pin. See      |  |

|                       |                   |                                                                                                                        |                     |                   |                  |                    |                   |  |

| <b>2:</b> T           | his feature is or | n 10.4 "Peripheral Pin Select (PPS)" for more information.<br>ature is only available for the 16x BRG mode (BRGH = 0). |                     |                   |                  |                    |                   |  |

### REGISTER 17-1: UxMODE: UARTx MODE REGISTER

### 18.7.4 USB VBUS POWER CONTROL REGISTER

### REGISTER 18-22: U1PWMCON: USB VBUS PWM GENERATOR CONTROL REGISTER

| R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0 |

|--------|-----|-----|-----|-----|-----|--------|-------|

| PWMEN  | _   |     | _   |     |     | PWMPOL | CNTEN |

| bit 15 | •   |     |     |     |     |        | bit 8 |

|        |     |     |     |     |     |        |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    | U-0   |

| —      | —   |     | —   | _   | _   | _      | _     |

| bit 7  |     |     |     |     |     |        | bit 0 |

|        |     |     |     |     |     |        |       |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15    | PWMEN: PWM Enable bit                                                                                                                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>1 = PWM generator is enabled</li> <li>0 = PWM generator is disabled; output is held in the Reset state specified by PWMPOL</li> </ul> |

| bit 14-10 | Unimplemented: Read as '0'                                                                                                                     |

| bit 9     | PWMPOL: PWM Polarity bit                                                                                                                       |

|           | <ul> <li>1 = PWM output is active-low and resets high</li> <li>0 = PWM output is active-high and resets low</li> </ul>                         |

| bit 8     | CNTEN: PWM Counter Enable bit                                                                                                                  |

|           | <ul><li>1 = Counter is enabled</li><li>0 = Counter is disabled</li></ul>                                                                       |

| bit 7-0   | Unimplemented: Read as '0'                                                                                                                     |

| Pin Name                     | Туре | Description                                                                                    |  |  |

|------------------------------|------|------------------------------------------------------------------------------------------------|--|--|

| PMA<22:16> <sup>(1)</sup>    | 0    | Address Bus Bits<22-16>                                                                        |  |  |

|                              | 0    | Address Bus Bit<15>                                                                            |  |  |

| PMA<15>, PMCS2               | 0    | Chip Select 2 (alternate location)                                                             |  |  |

| T MAX102, T MOOZ             | I/O  | Data Bus Bit<15> when port size is 16 bits and address is<br>multiplexed                       |  |  |

|                              | 0    | Address Bus Bit<14>                                                                            |  |  |

| PMA<14>, PMCS1               | 0    | Chip Select 1 (alternate location)                                                             |  |  |

|                              | I/O  | Data Bus Bit<14> when port size is 16-bit and address is multiplexed                           |  |  |

|                              | 0    | Address Bus Bits<13-8>                                                                         |  |  |

| PMA<13:8>                    | I/O  | Data Bus Bits<13-8> when port size is 16 bits and addres is multiplexed                        |  |  |

| PMA<7:3>                     | 0    | Address Bus Bits<7-3>                                                                          |  |  |

| PMA<2>, PMALU <sup>(1)</sup> | 0    | Address Bus Bit<2>                                                                             |  |  |

|                              | 0    | Address latch upper strobe for multiplexed address                                             |  |  |

|                              | I/O  | Address Bus Bit<1>                                                                             |  |  |

| PMA<1>, PMALH                | 0    | Address latch high strobe for multiplexed address                                              |  |  |

|                              | I/O  | Address Bus Bit<0>                                                                             |  |  |

| PMA<0>, PMALL                | 0    | Address latch low strobe for multiplexed address                                               |  |  |

| PMD<15:8>                    | I/O  | Data Bus Bits<15-8> when address is not multiplexed                                            |  |  |

|                              | I/O  | Data Bus Bits<7-4>                                                                             |  |  |

| PMD<7:4>                     | 0    | Address Bus Bits<7-4> when port size is 4 bits and address is multiplexed with 1 address phase |  |  |

| PMD<3:0>                     | I/O  | Data Bus Bits<3-0>                                                                             |  |  |

| PMCS1                        | I/O  | Chip Select 1                                                                                  |  |  |

| PMCS2                        | 0    | Chip Select 2                                                                                  |  |  |

| PMWR, PMENB                  | I/O  | Write strobe or enable signal depending on Strobe mode                                         |  |  |

| PMRD, PMRD/PMWR              | I/O  | Read strobe or Read/Write signal depending on Strobe mode                                      |  |  |

| PMBE1 <sup>(1)</sup>         | 0    | Byte indicator                                                                                 |  |  |

| PMBE0                        | 0    | Nibble or byte indicator                                                                       |  |  |

| PMACK1                       | Ι    | Acknowledgment 1                                                                               |  |  |

| PMACK2                       | I    | Acknowledgment 2                                                                               |  |  |

### TABLE 19-2: PARALLEL MASTER PORT PIN DESCRIPTION

**Note 1:** Available only in 100-pin devices (PIC24FJXXXGB210).

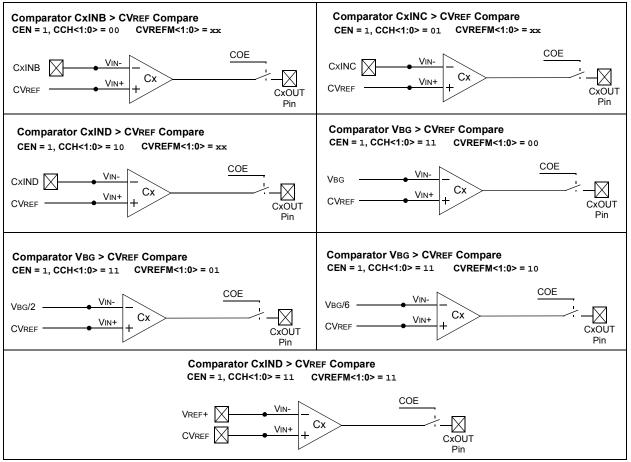

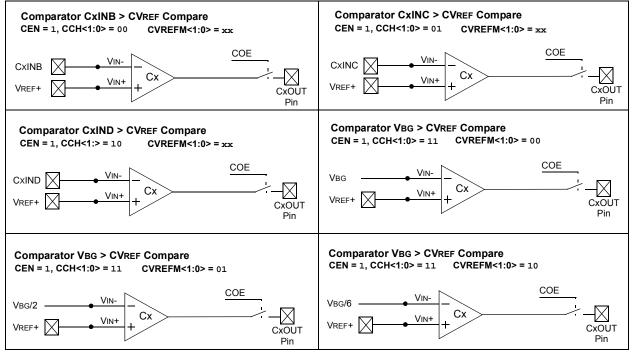

### FIGURE 23-3: INDIVIDUAL COMPARATOR CONFIGURATIONS WHEN CREF = 1 AND CVREFP = 0

### 26.2 On-Chip Voltage Regulator

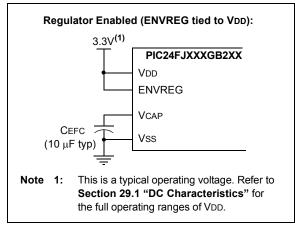

All PIC24FJ256GB210 family devices power their core digital logic at a nominal 1.8V. This may create an issue for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the PIC24FJ256GB210 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator is controlled by the ENVREG pin. Tying VDD to the pin enables the regulator, which in turn, provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR capacitor (such as ceramic) must be connected to the VCAP pin (Figure 26-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor (CEFC) is provided in **Section 29.1 "DC Characteristics"**.

### 26.2.1 VOLTAGE REGULATOR LOW-VOLTAGE DETECTION

When the on-chip regulator is enabled, it provides a constant voltage of 1.8V nominal to the digital core logic.

The regulator can provide this level from a VDD of about 2.1V, all the way up to the device's VDDMAX. It does not have the capability to boost VDD levels. In order to prevent "brown-out" conditions when the voltage drops too low for the regulator, the Brown-out Reset occurs. Then the regulator output follows VDD with a typical voltage drop of 300 mV.

To provide information about when the regulator voltage starts reducing, the on-chip regulator includes a simple Low-Voltage Detect circuit, which sets the Low-Voltage Detect Interrupt Flag, LVDIF (IFS4<8>). This can be used to generate an interrupt to trigger an orderly shutdown.

## FIGURE 26-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

### 26.2.2 ON-CHIP REGULATOR AND POR

When the voltage regulator is enabled, it takes approximately 10  $\mu$ s for it to generate output. During this time, designated as TVREG, code execution is disabled. TVREG is applied every time the device resumes operation after any power-down, including Sleep mode. TVREG is determined by the status of the VREGS bit (RCON<8>) and the WUTSEL Configuration bits (CW3<11:10>). Refer to **Section 29.0 "Electrical Characteristics"** for more information on TVREG.

### 26.2.3 ON-CHIP REGULATOR AND BOR

When the on-chip regulator is enabled, PIC24FJ256GB210 family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain the output level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR (RCON<1>) flag bit. The brown-out voltage specifications are provided in **Section 7.** "**Reset**" (DS39712) in the "*PIC24F Family Reference Manual*".

| Note: | For more information, see Section 29.0                           |

|-------|------------------------------------------------------------------|

|       | "Electrical Characteristics". The infor-                         |

|       | mation in this data sheet supersedes the information in the FRM. |

### 26.2.4 VOLTAGE REGULATOR STANDBY MODE

When enabled, the on-chip regulator always consumes a small incremental amount of current over IDD/IPD, including when the device is in Sleep mode, even though the core digital logic does not require power. To provide additional savings in applications where power resources are critical, the regulator can be made to enter Standby mode on its own whenever the device goes into Sleep mode. This feature is controlled by the VREGS bit (RCON<8>). Clearing the VREGS bit enables the Standby mode. When waking up from Standby mode, the regulator needs to wait for TVREG to expire before wake-up.

The regulator wake-up time required for Standby mode is controlled by the WUTSEL<1:0> (CW3<11:10>) Configuration bits. The regulator wake-up time is lower when WUTSEL<1:0> = 01, and higher when WUTSEL<1:0> = 11. Refer to the TVREG specification in Table 29-10 for regulator wake-up time.

When the regulator's Standby mode is turned off (VREGS = 1), the device wakes up without waiting for TVREG. However, with the VREGS bit set, the power consumption while in Sleep mode will be approximately 40  $\mu$ A higher than what it would be if the regulator was allowed to enter Standby mode.

| Assembly<br>Mnemonic |        | Assembly Syntax | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|-----------------|------------------------------|---------------|----------------|--------------------------|