### NXP USA Inc. - S9S12HY32J0CLH Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HCS12                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 32MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SCI, SPI              |

| Peripherals                | LCD, Motor control PWM, POR, PWM, WDT                                  |

| Number of I/O              | 50                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 4K x 8                                                                 |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                            |

| Data Converters            | A/D 6x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12hy32j0clh |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

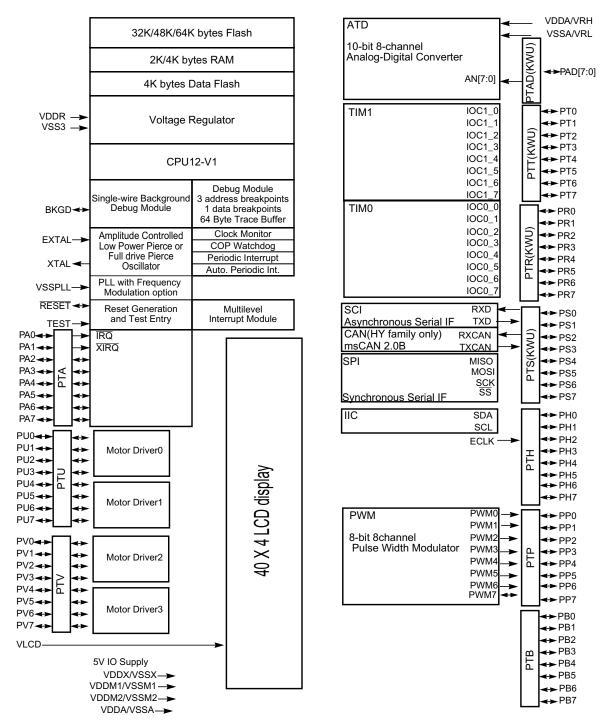

# 1.4 Block Diagram

Figure 1-1 shows a block diagram of the MC9S12HY/HA-Family devices

MC9S12HY/HA-Family Reference Manual, Rev. 1.05

Consult the ATD section for information about the analog-to-digital converter module. References to freeze mode are equivalent to active BDM mode.

# 1.14 S12CPMU Configuration

The bandgap reference voltage  $V_{BG}$  and the output voltage of the temperature sensor  $V_{HT}$  can be connected to the ATD channel SPECIAL17 (see Table 8-15) using the VSEL (Voltage Access Select Bit) in CPMUHTCTL register (see Table 7-13)

# 1.15 Documentation Note

The terms S12P, S12X and S12S which appear in some of the following chapters refer to the original architecture which those modules were designed to work with. Please do not confuse them with the S12HY/S12HA product families.

S12HY/S12HA will support only 10-bit ATD resolution, although in ATD12B8C block it still has the 12-bit descriptions.

Interrupt Module (S12SINTV1)

If the interrupt source is unknown (for example, in the case where an interrupt request becomes inactive after the interrupt has been recognized, but prior to the CPU vector request), the vector address supplied to the CPU will default to that of the spurious interrupt vector.

### NOTE

Care must be taken to ensure that all interrupt requests remain active until the system begins execution of the applicable service routine; otherwise, the exception request may not get processed at all or the result may be a spurious interrupt request (vector at address (vector base + 0x0080)).

# 4.4.3 Reset Exception Requests

The INT module supports three system reset exception request types (please refer to the Clock and Reset generator module for details):

- 1. Pin reset, power-on reset or illegal address reset, low voltage reset (if applicable)

- 2. Clock monitor reset request

- 3. COP watchdog reset request

# 4.4.4 Exception Priority

The priority (from highest to lowest) and address of all exception vectors issued by the INT module upon request by the CPU is shown in Table 4-4.

| Vector Address <sup>1</sup>   | Source                                                                                                                            |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0xFFFE                        | Pin reset, power-on reset, illegal address reset, low voltage reset (if applicable)                                               |

| 0xFFFC                        | Clock monitor reset                                                                                                               |

| 0xFFFA                        | COP watchdog reset                                                                                                                |

| (Vector base + 0x00F8)        | Unimplemented opcode trap                                                                                                         |

| (Vector base + 0x00F6)        | Software interrupt instruction (SWI) or BDM vector request                                                                        |

| (Vector base + 0x00F4)        | X bit maskable interrupt request (XIRQ or D2D error interrupt) <sup>2</sup>                                                       |

| (Vector base + 0x00F2)        | IRQ or D2D interrupt request <sup>3</sup>                                                                                         |

| (Vector base + 0x00F0-0x0082) | Device specific I bit maskable interrupt sources (priority determined by the low byte of the vector address, in descending order) |

| (Vector base + 0x0080)        | Spurious interrupt                                                                                                                |

Table 4-4. Exception Vector Map and Priority

<sup>1</sup> 16 bits vector address based

$^2\,$  D2D error interrupt on MCUs featuring a D2D initiator module, otherwise  $\overline{XIRQ}$  pin interrupt

<sup>3</sup> D2D interrupt on MCUs featuring a D2D initiator module, otherwise IRQ pin interrupt

S12S Debug Module (S12SDBGV2)

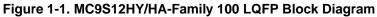

### 6.3.2.7.2 Debug State Control Register 2 (DBGSCR2)

Address: 0x0027

Figure 6-10. Debug State Control Register 2 (DBGSCR2)

Read: If COMRV[1:0] = 01

Write: If COMRV[1:0] = 01 and DBG is not armed.

This register is visible at 0x0027 only with COMRV[1:0] = 01. The state control register 2 selects the targeted next state whilst in State2. The matches refer to the match channels of the comparator match control logic as depicted in Figure 6-1 and described in 6.3.2.8.1, "Debug Comparator Control Register (DBGXCTL)". Comparators must be enabled by setting the comparator enable bit in the associated DBGXCTL control register.

| Field          | Description                                                                             |

|----------------|-----------------------------------------------------------------------------------------|

| 3–0<br>SC[3:0] | These bits select the targeted next state whilst in State2, based upon the match event. |

| Ta | able 6-18. 3 | State2 — S | Sequencer l | Next Stat | e Selecti | on |

|----|--------------|------------|-------------|-----------|-----------|----|

|    |              |            |             |           |           |    |

| SC[3:0] | Description (Unspecified matches have no effect)       |  |  |  |

|---------|--------------------------------------------------------|--|--|--|

| 0000    | Match0 to State1 Match2 to State3.                     |  |  |  |

| 0001    | Match1 to State3                                       |  |  |  |

| 0010    | Match2 to State3                                       |  |  |  |

| 0011    | Match1 to State3 Match0 Final State                    |  |  |  |

| 0100    | Match1 to State1 Match2 to State3.                     |  |  |  |

| 0101    | Match2 to Final State                                  |  |  |  |

| 0110    | Match2 to State1 Match0 to Final State                 |  |  |  |

| 0111    | Either Match0 or Match1 to Final State                 |  |  |  |

| 1000    | Reserved                                               |  |  |  |

| 1001    | Reserved                                               |  |  |  |

| 1010    | Reserved                                               |  |  |  |

| 1011    | Reserved                                               |  |  |  |

| 1100    | Either Match0 or Match1 to Final StateMatch2 to State3 |  |  |  |

| 1101    | Reserved                                               |  |  |  |

| 1110    | Reserved                                               |  |  |  |

| 1111    | Either Match0 or Match1 to Final StateMatch2 to State1 |  |  |  |

The priorities described in Table 6-36 dictate that in the case of simultaneous matches, a match leading to final state has priority followed by the match on the lower channel number (0,1,2).

S12S Debug Module (S12SDBGV2)

# Chapter 8 Analog-to-Digital Converter (ADC12B8CV1) Block Description Revision History

| Version<br>Number | Revision<br>Date | Effective<br>Date | Author | Description of Changes                                                                       |

|-------------------|------------------|-------------------|--------|----------------------------------------------------------------------------------------------|

| V01.00            | 25 July 2007     | 25 July 2007      |        | Initial version                                                                              |

| V01.01            | 14 Sept 2007     | 14 Sept 2007      |        | Added reserved registers at the end the memory map.                                          |

| V01.02            | 1 Oct 2007       | 1 Oct 2007        |        | Added following mention where applies:<br>(n conversion number, NOT channel number!)         |

| V01.03            | 9 Oct 2007       | 9 Oct 2007        |        | Modified table "Analog Input Channel Select Coding" due to new customer feature (SPECIAL17). |

| V01.04            | 30 Apr 2008      | 30 Apr 2008       |        | Updated document for 8 channels.                                                             |

# 8.1 Introduction

The ADC12B8C is a 8-channel, 12-bit, multiplexed input successive approximation analog-to-digital converter. Refer to device electrical specifications for ATD accuracy.

### 8.1.1 Features

- 8-, 10-, or 12-bit resolution.

- Conversion in Stop Mode using internally generated clock

- Automatic return to low power after conversion sequence

- Automatic compare with interrupt for higher than or less/equal than programmable value

- Programmable sample time.

- Left/right justified result data.

- External trigger control.

- Sequence complete interrupt.

- Analog input multiplexer for 8 analog input channels.

- Special conversions for  $V_{RH}$ ,  $V_{RL}$ ,  $(V_{RL}+V_{RH})/2$ .

- 1-to-8 conversion sequence lengths.

#### MC9S12HY/HA-Family Reference Manual, Rev. 1.05

```

Pulse-Width Modulator (S12PWM8B8CV1)

```

Write: Anytime (any value written causes PWM counter to be reset to \$00).

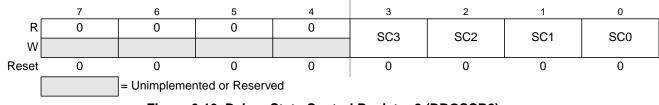

# 11.3.2.13 PWM Channel Period Registers (PWMPERx)

There is a dedicated period register for each channel. The value in this register determines the period of the associated PWM channel.

The period registers for each channel are double buffered so that if they change while the channel is enabled, the change will NOT take effect until one of the following occurs:

- The effective period ends

- The counter is written (counter resets to \$00)

- The channel is disabled

In this way, the output of the PWM will always be either the old waveform or the new waveform, not some variation in between. If the channel is not enabled, then writes to the period register will go directly to the latches as well as the buffer.

### NOTE

Reads of this register return the most recent value written. Reads do not necessarily return the value of the currently active period due to the double buffering scheme.

See Section 11.4.2.3, "PWM Period and Duty" for more information.

To calculate the output period, take the selected clock source period for the channel of interest (A, B, SA, or SB) and multiply it by the value in the period register for that channel:

- Left aligned output (CAEx = 0)

- PWMx Period=Channel Clock Period \* PWMPERx Center Aligned Output (CAEx=1) PWMx Period = Channel Clock Period \* (2 \* PWMPERx)

For boundary case programming values, please refer to Section 11.4.2.8, "PWM Boundary Cases".

Module Base + 0x0014 = PWMPER0, 0x0015 = PWMPER1, 0x0016 = PWMPER2, 0x0017 = PWMPER3 Module Base + 0x0018 = PWMPER4, 0x0019 = PWMPER5, 0x001A = PWMPER6, 0x001B = PWMPER7

Read: Anytime

Write: Anytime

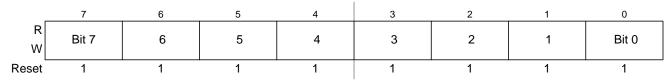

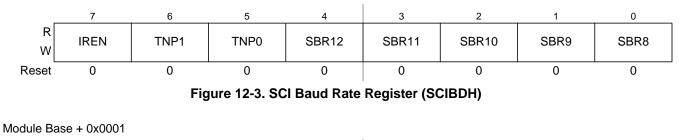

## 12.3.2.1 SCI Baud Rate Registers (SCIBDH, SCIBDL)

Module Base + 0x0000

|        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|------|------|------|------|------|------|------|------|

| R<br>W | SBR7 | SBR6 | SBR5 | SBR4 | SBR3 | SBR2 | SBR1 | SBR0 |

| Reset  | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    |

|        |      |      |      |      |      |      |      |      |

Figure 12-4. SCI Baud Rate Register (SCIBDL)

Read: Anytime, if AMAP = 0. If only SCIBDH is written to, a read will not return the correct data until SCIBDL is written to as well, following a write to SCIBDH.

Write: Anytime, if AMAP = 0.

#### NOTE

Those two registers are only visible in the memory map if AMAP = 0 (reset condition).

The SCI baud rate register is used by to determine the baud rate of the SCI, and to control the infrared modulation/demodulation submodule.

| Table 12-2. SCIBDH and SCIBDL F | Field Descriptions |

|---------------------------------|--------------------|

|---------------------------------|--------------------|

| Field                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IREN               | Infrared Enable Bit — This bit enables/disables the infrared modulation/demodulation submodule.<br>0 IR disabled<br>1 IR enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6:5<br>TNP[1:0]         | <b>Transmitter Narrow Pulse Bits</b> — These bits enable whether the SCI transmits a 1/16, 3/16, 1/32 or 1/4 narrow pulse. See Table 12-3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4:0<br>7:0<br>SBR[12:0] | <ul> <li>SCI Baud Rate Bits — The baud rate for the SCI is determined by the bits in this register. The baud rate is calculated two different ways depending on the state of the IREN bit.</li> <li>The formulas for calculating the baud rate are:<br/>When IREN = 0 then,<br/>SCI baud rate = SCI bus clock / (16 x SBR[12:0])</li> <li>When IREN = 1 then,<br/>SCI baud rate = SCI bus clock / (32 x SBR[12:1])</li> <li>Note: The baud rate generator is disabled after reset and not started until the TE bit or the RE bit is set for the first time. The baud rate generator is disabled when (SBR[12:0] = 0 and IREN = 0) or (SBR[12:1] = 0 and IREN = 1).</li> <li>Note: Writing to SCIBDH has no effect without writing to SCIBDL, because writing to SCIBDH puts the data in a temporary location until SCIBDL is written to.</li> </ul> |

Figure 15-20. Flash Reserveds Register (FRS

All bits in the FRSV3 register read 0 and are not writable.

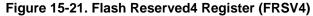

### 15.3.2.15 Flash Reserved4 Register (FRSV4)

This Flash register is reserved for factory testing.

Offset Module Base + 0x000E

All bits in the FRSV4 register read 0 and are not writable.

# 15.3.2.16 Flash Option Register (FOPT)

The FOPT register is the Flash option register.

All bits in the FOPT register are readable but are not writable.

During the reset sequence, the FOPT register is loaded from the Flash nonvolatile byte in the Flash configuration field at global address 0x3\_FF0E located in P-Flash memory (see Table 15-3) as indicated by reset condition F in Figure 15-22. If a double bit fault is detected while reading the P-Flash phrase containing the Flash nonvolatile byte during the reset sequence, all bits in the FOPT register will be set.

| Register | Error Bit | Error Condition                                                                                  |  |

|----------|-----------|--------------------------------------------------------------------------------------------------|--|

| ACCERR   |           | Set if CCOBIX[2:0] != 000 at command launch                                                      |  |

|          | ACCERR    | Set if command not available in current mode (see Table 15-27)                                   |  |

| FSTAT    | FPVIOL    | Set if any area of the P-Flash or D-Flash memory is protected                                    |  |

| _        | MGSTAT1   | Set if any errors have been encountered during the verify operation <sup>1</sup>                 |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation <sup>1</sup> |  |

Table 15-50. Unsecure Flash Command Error Handling

<sup>1</sup> As found in the memory map for FTMRC64K1.

### 15.4.5.11 Verify Backdoor Access Key Command

The Verify Backdoor Access Key command will only execute if it is enabled by the KEYEN bits in the FSEC register (see Table 15-9). The Verify Backdoor Access Key command releases security if user-supplied keys match those stored in the Flash security bytes of the Flash configuration field (see Table 15-3). The Verify Backdoor Access Key command must not be executed from the Flash block containing the backdoor comparison key to avoid code runaway.

Table 15-51. Verify Backdoor Access Key Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters  |  |  |

|-------------|-------------------|--|--|

| 000         | 0x0C Not required |  |  |

| 001         | Key 0             |  |  |

| 010         | Key 1             |  |  |

| 011         | Key 2             |  |  |

| 100         | Key 3             |  |  |

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash configuration field with Key 0 compared to 0x3\_FF00, etc. If the backdoor keys match, security will be released. If the backdoor keys do not match, security is not released and all future attempts to execute the Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is set after the Verify Backdoor Access Key operation has completed.

### 16.1.2.2 D-Flash Features

- 4 Kbytes of D-Flash memory composed of one 4 Kbyte Flash block divided into 16 sectors of 256 bytes

- Single bit fault correction and double bit fault detection within a word during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and word program operation

- Protection scheme to prevent accidental program or erase of D-Flash memory

- Ability to program up to four words in a burst sequence

### 16.1.2.3 Other Flash Module Features

- No external high-voltage power supply required for Flash memory program and erase operations

- Interrupt generation on Flash command completion and Flash error detection

- Security mechanism to prevent unauthorized access to the Flash memory

### 16.1.3 Block Diagram

The block diagram of the Flash module is shown in Figure 16-1.

#### 48 KByte Flash Module (S12FTMRC48K1V1)

#### Table 16-4. Program IFR Fields

| Global Address      | Size<br>(Bytes) | Field Description                                                       |

|---------------------|-----------------|-------------------------------------------------------------------------|

| 0x0_4000 - 0x0_4007 | 8               | Reserved                                                                |

| 0x0_4008 - 0x0_40B5 | 174             | Reserved                                                                |

| 0x0_40B6 - 0x0_40B7 | 2               | Version ID <sup>1</sup>                                                 |

| 0x0_40B8 - 0x0_40BF | 8               | Reserved                                                                |

| 0x0_40C0 - 0x0_40FF | 64              | Program Once Field<br>Refer to Section 16.4.5.6, "Program Once Command" |

<sup>1</sup> Used to track firmware patch versions, see Section 16.4.2

| Global Address      | Size<br>(Bytes) | Description                                            |

|---------------------|-----------------|--------------------------------------------------------|

| 0x0_4000 - 0x0_43FF | 1,024           | Reserved                                               |

| 0x0_4400 - 0x0_53FF | 4,096           | D-Flash Memory                                         |

| 0x0_5400 - 0x0_57FF | 1,024           | Reserved                                               |

| 0x0_5800 - 0x0_5AFF | 768             | Memory Controller Scratch RAM (RAMON <sup>1</sup> = 1) |

| 0x0_5B00 - 0x0_5FFF | 1,280           | Reserved                                               |

| 0x0_6000 - 0x0_67FF | 2,048           | Reserved                                               |

| 0x0_6800 - 0x0_7FFF | 6,144           | Reserved                                               |

#### Table 16-5. D-Flash and Memory Controller Resource Fields

<sup>1</sup> MMCCTL1 register bit

| Field              | Description                                                                                                                                                                                                                                                                                     |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 3<br>MGBUSY        | <ul> <li>Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.</li> <li>0 Memory Controller is idle</li> <li>1 Memory Controller is busy executing a Flash command (CCIF = 0)</li> </ul>                                                            |  |  |  |  |

| 2<br>RSVD          | Reserved Bit — This bit is reserved and always reads 0.                                                                                                                                                                                                                                         |  |  |  |  |

| 1–0<br>MGSTAT[1:0] | <b>Memory Controller Command Completion Status Flag</b> — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. See Section 16.4.5, "Flash Command Description," and Section 16.6, "Initialization" for details. |  |  |  |  |

#### Table 16-14. FSTAT Field Descriptions (continued)

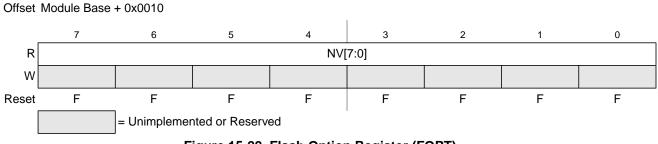

### 16.3.2.8 Flash Error Status Register (FERSTAT)

The FERSTAT register reflects the error status of internal Flash operations.

#### Figure 16-12. Flash Error Status Register (FERSTAT)

All flags in the FERSTAT register are readable and only writable to clear the flag.

#### Table 16-15. FERSTAT Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1<br>DFDIF | <ul> <li>Double Bit Fault Detect Interrupt Flag — The setting of the DFDIF flag indicates that a double bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The DFDIF flag is cleared by writing a 1 to DFDIF. Writing a 0 to DFDIF has no effect on DFDIF.</li> <li>0 No double bit fault detected</li> <li>1 Double bit fault detected or an invalid Flash array read operation attempted</li> </ul>                                                |  |  |  |  |

| 0<br>SFDIF | <ul> <li>Single Bit Fault Detect Interrupt Flag — With the IGNSF bit in the FCNFG register clear, the SFDIF flag indicates that a single bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The SFDIF flag is cleared by writing a 1 to SFDIF. Writing a 0 to SFDIF has no effect on SFDIF.</li> <li>0 No single bit fault detected</li> <li>1 Single bit fault detected and corrected or an invalid Flash array read operation attempted</li> </ul> |  |  |  |  |

<sup>1</sup> The single bit fault and double bit fault flags are mutually exclusive for parity errors (an ECC fault occurrence can be either single fault or double fault but never both). A simultaneous access collision (read attempted while command running) is indicated when both SFDIF and DFDIF flags are high.

### 16.3.2.9 P-Flash Protection Register (FPROT)

The FPROT register defines which P-Flash sectors are protected against program and erase operations.

#### MC9S12HY/HA-Family Reference Manual, Rev. 1.05

Motor Controller (MC10B8CV1)

| Offset | Register                                                   | Access |

|--------|------------------------------------------------------------|--------|

| 0x0016 | Motor Controller Channel Control Register 6 (MCCC6)        | RW     |

| 0x0017 | Motor Controller Channel Control Register 7 (MCCC7)        | RW     |

| 0x0018 | Reserved                                                   | —      |

| 0x0019 | Reserved                                                   |        |

| 0x001A | Reserved                                                   |        |

| 0x001B | Reserved                                                   | —      |

| 0x001C | Reserved                                                   |        |

| 0x001D | Reserved                                                   | —      |

| 0x001E | Reserved                                                   |        |

| 0x001F | Reserved                                                   | —      |

| 0x0020 | Motor Controller Duty Cycle Register 0 (MCDC0) — High Byte | RW     |

| 0x0021 | Motor Controller Duty Cycle Register 0 (MCDC0) — Low Byte  | RW     |

| 0x0022 | Motor Controller Duty Cycle Register 1 (MCDC1) — High Byte | RW     |

| 0x0023 | Motor Controller Duty Cycle Register 1 (MCDC1) — Low Byte  | RW     |

| 0x0024 | Motor Controller Duty Cycle Register 2 (MCDC2) — High Byte | RW     |

| 0x0025 | Motor Controller Duty Cycle Register 2 (MCDC2) — Low Byte  | RW     |

| 0x0026 | Motor Controller Duty Cycle Register 3 (MCDC3) — High Byte | RW     |

| 0x0027 | Motor Controller Duty Cycle Register 3 (MCDC3) — Low Byte  | RW     |

| 0x0028 | Motor Controller Duty Cycle Register 4 (MCDC4) — High Byte | RW     |

| 0x0029 | Motor Controller Duty Cycle Register 4 (MCDC4) — Low Byte  | RW     |

| 0x002A | Motor Controller Duty Cycle Register 5 (MCDC5) — High Byte | RW     |

| 0x002B | Motor Controller Duty Cycle Register 5 (MCDC5) — Low Byte  | RW     |

| 0x002C | Motor Controller Duty Cycle Register 6 (MCDC6) — High Byte | RW     |

| 0x002D | Motor Controller Duty Cycle Register 6 (MCDC6) — Low Byte  | RW     |

| 0x002E | Motor Controller Duty Cycle Register 7 (MCDC7) — High Byte | RW     |

| 0x002F | Motor Controller Duty Cycle Register 7 (MCDC7) — Low Byte  | RW     |

| 0x0030 | Reserved                                                   | _      |

| 0x0031 | Reserved                                                   |        |

| 0x0032 | Reserved                                                   |        |

| 0x0033 | Reserved                                                   |        |

| 0x0034 | Reserved                                                   | — —    |

| 0x0035 | Reserved                                                   |        |

| 0x0036 | Reserved                                                   |        |

| 0x0037 | Reserved                                                   | _      |

| 0x0038 | Reserved                                                   | —      |

| 0x0039 | Reserved                                                   | _      |

| 0x003A | Reserved                                                   | _      |

| 0x003B | Reserved                                                   | _      |

| 0x003C | Reserved                                                   | _      |

| 0x003D | Reserved                                                   | _      |

| Figure 19-2. MC10B8C Memor | у Мар | (continued) |

|----------------------------|-------|-------------|

|----------------------------|-------|-------------|

VDDR supplies the internal voltage regulator.

All VDDM pins are internally connected by metal.

All VSSM pins are internally connected by metal.

VDDA, VDDX, VDDM and VSSA, VSSX, VSSM are connected by diodes for ESD protection.

### NOTE

In the following context  $V_{DD35}$  is used for either VDDA, VDDR, VDDM and VDDX;  $V_{SS35}$  is used for either VSSA, VSSM and VSSX unless otherwise noted.

$I_{DD35}$  denotes the sum of the currents flowing into the VDDA and VDDR pins. The run mode current in VDDM and VDDX is external load dependent

### A.1.3 Pins

There are four groups of functional pins.

### A.1.3.1 I/O Pins

The I/O pins have a level in the range of 4.5V to 5.5V. This class of pins is comprised of all port I/O pins, the analog inputs, BKGD and the RESET pins. Some functionality may be disabled.

### A.1.3.2 Analog Reference

This group is made up by the VDDA and VSSA pins.

### A.1.3.3 Oscillator

The pins EXTAL, XTAL dedicated to the oscillator have a nominal 1.8V level.

### A.1.3.4 TEST

This pin is used for production testing only. The TEST pin must be tied to ground in all applications.

## A.1.4 Current Injection

Power supply must maintain regulation within operating  $V_{DD35}$  or  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{in} > V_{DD35}$ ) is greater than  $I_{DD35}$ , the injection current may flow out of  $V_{DD35}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD35}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power; e.g., if no system clock is present, or if clock rate is very low which would reduce overall power consumption.

#### Table A-6. 5-V I/O Characteristics

| 18 | D | Port T, S, R, AD interrupt input pulse passed (STOP) | t <sub>PULSE</sub> | 4 | — | — | tcyc |

|----|---|------------------------------------------------------|--------------------|---|---|---|------|

| 19 |   | IRQ pulse width, edge-sensitive mode (STOP)          | PWIRQ              | 1 | _ | _ | tcyc |

1. Maximum leakage current occurs at maximum operating temperature. Current decreases by approximately one-half for each 8 C to 12°C in the temperature range from 50°C to 125°C.

2. Refer to Section A.1.4, "Current Injection" for more details

3. Parameter only applies in stop or pseudo stop mode.

# A.1.10 Supply Currents

This section describes the current consumption characteristics of the device as well as the conditions for the measurements.

### A.1.10.1 Measurement Conditions

IDD value is measured on VDDR pin. It does not include the current to drive external loads. Unless otherwise noted the currents are measured in special single chip mode and the CPU code is executed from RAM. For Run and Wait current measurements PLL is on and the reference clock is the IRC trimmed to 1 MHz. The bus frequency is 32 MHz and the CPU frequency is 64 MHz. Table A-7, Table A-8 and Table A-9 show the configuration of the CPMU module and the peripherals for Run, Wait and Stop current measurement.

| CPMU REGISTER | Bit settings/Conditions                                                                             |

|---------------|-----------------------------------------------------------------------------------------------------|

| CPMUCLKS      | PLLSEL=0, PSTP=1,<br>PRE=PCE=RTIOSCSEL=COPOSCSEL=1                                                  |

| CPMUOSC       | OSCE=1, External Square wave on EXTAL $\rm f_{EXTAL}$ =16MHz, $\rm V_{IH}$ = 1.8V, $\rm V_{IL}$ =0V |

| CPMURTI       | RTDEC=0, RTR[6:4]=111, RTR[3:0]=1111;                                                               |

| CPMUCOP       | WCOP=1, CR[2:0]=111                                                                                 |

#### Table A-7. CPMU Configuration for Pseudo Stop Current Measurement

| CPMU REGISTER | Bit settings/Conditions                                                                    |  |  |

|---------------|--------------------------------------------------------------------------------------------|--|--|

| CPMUSYNR      | VCOFRQ[1:0]=01,SYNDIV[5:0] = 32                                                            |  |  |

| CPMUPOSTDIV   | POSTDIV[4:0]=0,                                                                            |  |  |

| CPMUCLKS      | PLLSEL=1                                                                                   |  |  |

| CPMUOSC       | OSCE=0,<br>Reference clock for PLL is f <sub>ref</sub> =f <sub>irc1m</sub> trimmed to 1MHz |  |  |

# A.2 ATD Characteristics

This section describes the characteristics of the analog-to-digital converter.

# A.2.1 ATD Operating Characteristics

The Table A-12 and Table A-13 show conditions under which the ATD operates.

The following constraints exist to obtain full-scale, full range results:

$V_{SSA} (V_{RL}) \le V_{IN} \le V_{DDA} (V_{RH}).$

This constraint exists since the sample buffer amplifier can not drive beyond the power supply levels that it ties to. If the input level goes outside of this range it will effectively be clipped.

| Condit | tions | s are shown in Table A-4 unless otherwise noted, supply v                                           | oltage 3.13 V                             | < V <sub>DDA</sub> < 5 | 5.5 V |          |                        |

|--------|-------|-----------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------|-------|----------|------------------------|

| Num    | С     | Rating                                                                                              | Symbol                                    | Min                    | Тур   | Max      | Unit                   |

| 1      | D     | Voltage difference V <sub>DDX</sub> /V <sub>DDM</sub> to V <sub>DDA</sub>                           | $\Delta_{VDDX}$                           | -0.1                   | 0     | 0.1      | V                      |

| 2      | D     | Voltage difference $V_{SSX}/V_{SSM}$ to $V_{SSA}$                                                   | $\Delta_{VSSX}$                           | -0.1                   | 0     | 0.1      | V                      |

| 3      | С     | Differential reference voltage <sup>(1)</sup>                                                       | V <sub>RH</sub> -V <sub>RL</sub>          | 3.13                   | 5.0   | 5.5      | V                      |

| 4      | С     | ATD Clock Frequency (derived from bus clock via the prescaler bus)                                  | f <sub>ATDCLk</sub>                       | 0.25                   |       | 8.0      | MHz                    |

| 5      | Ρ     | ATD Clock Frequency in Stop mode (internal generated temperature and voltage dependent clock, ICLK) |                                           | 0.6                    | 1     | 1.7      | MHz                    |

| 6      | D     | ADC conversion in stop, recovery time <sup>(2)</sup>                                                | t <sub>ATDSTPRC</sub><br>V                |                        | —     | 1.5      | us                     |

| 7      | D     | ATD Conversion Period <sup>(3)</sup><br>10 bit resolution:<br>8 bit resolution:                     | N <sub>CONV10</sub><br>N <sub>CONV8</sub> | 19<br>17               |       | 41<br>39 | ATD<br>clock<br>Cycles |

| Table | A-12. | ATD ( | Operating   | Characteristics  |

|-------|-------|-------|-------------|------------------|

|       |       |       | o por a mig | •••••••••••••••• |

1. Full accuracy is not guaranteed when differential voltage is less than 4.50 V

2. When converting in Stop Mode (ICLKSTP=1) an ATD Stop Recovery time tATDSTPRCV is required to switch back to bus clock based ATDCLK when leaving Stop Mode. Do not access ATD registers during this time.

3. The minimum time assumes a sample time of 4 ATD clock cycles. The maximum time assumes a sample time of 24 ATD clock cycles and the discharge feature (SMP\_DIS) enabled, which adds 2 ATD clock cycles.

# A.2.2 Factors Influencing Accuracy

Source resistance, source capacitance and current injection have an influence on the accuracy of the ATD. A further factor is that PortAD pins that are configured as output drivers switching.

# A.2.2.1 Port AD Output Drivers Switching

PortAD output drivers switching can adversely affect the ATD accuracy whilst converting the analog voltage on other PortAD pins because the output drivers are supplied from the VDDA/VSSA ATD supply pins. Although internal design measures are implemented to minimize the affect of output driver noise, it

### A.3.1.8 Erase P-Flash Block (FCMD=0x09)

The time required to erase the P-Flash block is given by:

for 64 KB P-Flash

$t_{pmass} \approx 100100 \cdot \frac{1}{f_{\rm NVMOP}} + 35000 \cdot \frac{1}{f_{\rm NVMBUS}}$

### A.3.1.9 Erase P-Flash Sector (FCMD=0x0A)

The typical time to erase a 512-byte P-Flash sector is given by:

$$t_{pera} \approx 20020 \cdot \frac{1}{f_{\rm NVMOP}} + 700 \cdot \frac{1}{f_{\rm NVMBUS}}$$

The maximum time to erase a 512-byte P-Flash sector is given by:

$$t_{pera} \approx 20020 \cdot \frac{1}{f_{\rm NVMOP}} + 1400 \cdot \frac{1}{f_{\rm NVMBUS}}$$

### A.3.1.10 Unsecure Flash (FCMD=0x0B)

The maximum time required to erase and unsecure the Flash is given by:

for 64 KB P-Flash and 4 KB D-Flash

$$t_{uns} \approx 100100 \cdot \frac{1}{f_{NVMOP}} + 38000 \cdot \frac{1}{f_{NVMBUS}}$$

## A.3.1.11 Verify Backdoor Access Key (FCMD=0x0C)

The maximum verify backdoor access key time is given by:

$$t = 400 \cdot \frac{1}{f_{\text{NVMBUS}}}$$

### A.3.1.12 Set User Margin Level (FCMD=0x0D)

The maximum set user margin level time is given by:

$$t = 350 \cdot \frac{1}{f_{\rm NVMBUS}}$$

# A.4 Reset, Oscillator, IRC, IVREG, IPLL

# A.5 Phase Locked Loop

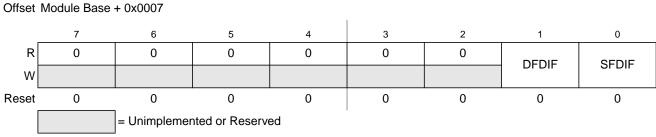

# A.5.1 Jitter Definitions

With each transition of the feedback clock, the deviation from the reference clock is measured and input voltage to the VCO is adjusted accordingly. The adjustment is done continuously with no abrupt changes in the VCOCLK frequency. Noise, voltage, temperature and other factors cause slight variations in the control loop resulting in a clock jitter. This jitter affects the real minimum and maximum clock periods as illustrated in Figure A-2.

Figure A-2. Jitter Definitions

The relative deviation of  $t_{nom}$  is at its maximum for one clock period, and decreases towards zero for larger number of clock periods (N).

Defining the jitter as:

$$J(N) = max\left(\left|1 - \frac{t_{max}(N)}{N \cdot t_{nom}}\right|, \left|1 - \frac{t_{min}(N)}{N \cdot t_{nom}}\right|\right)$$

For N < 100, the following equation is a good fit for the maximum jitter:

$$J(N) = \frac{j_1}{\sqrt{N}}$$

#### **Detailed Register Address Map**

| Address           | Name     |        | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

|-------------------|----------|--------|--------|--------|--------|--------|--------|--------|-------|-------|

| 0x010A            | FCCOBHI  | R<br>W | CCOB15 | CCOB14 | CCOB13 | CCOB12 | CCOB11 | CCOB10 | CCOB9 | CCOB8 |

| 0x010B            | FCCOBLO  | R<br>W | CCOB7  | CCOB6  | CCOB5  | CCOB4  | CCOB3  | CCOB2  | CCOB1 | CCOB0 |

| 0x010C-<br>0x010F | Reserved | R      | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

|                   |          | W      |        |        |        |        |        |        |       |       |

| 0x0110            | FOPT     | R      | NV7    | NV6    | NV5    | NV4    | NV3    | NV2    | NV1   | NV0   |

|                   |          | W      |        |        |        |        |        |        |       |       |

| 0x0111-<br>0x0113 | Reserved | R      | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

|                   |          | W      |        |        |        |        |        |        |       |       |

### 0x0114–0x011F Reserved

| Address           | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0114-<br>0x011F | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|                   |          | W |       |       |       |       |       |       |       |       |

### 0x0120 Interrupt Module(INT) Map

| Address | Name | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2 | Bit 1 | Bit 0 |

|---------|------|--------|-------|-------|--------|---------|-------|-------|-------|

| 0x0120  | IVBR | R<br>W |       |       | IVB_AD | DR[7:0] |       |       |       |

### 0x0121-0x013F Reserved

| Address           | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0121-<br>0x013F | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|                   | Reserveu | W |       |       |       |       |       |       |       |       |

### 0x140-0x017F MSCAN(CAN) Map

| Address | Name    |           | Bit 7 | Bit 6          | Bit 5  | Bit 4          | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|---------|---------|-----------|-------|----------------|--------|----------------|--------|--------|--------|--------|

| 0x0140  | CANCTL0 | R         | RXFRM | RXACT          | CSWAI  | SYNCH          | ТІМЕ   | WUPE   | SLPRQ  | INITRQ |

| 0,0110  | 0/      | W         |       |                |        |                |        |        |        |        |

| 0x0141  | CANCTL1 | R         | CANE  | CLKSRC         | LOOPB  | OOPB LISTEN    | BORM   | WUPM   | SLPAK  | INITAK |

|         | CANCILI | W         | CANE  | CLASICO        | LOOFB  | LISTEN         | BORIN  |        |        |        |

| 0,0140  |         | R         |       | SJW0           | BRP5   | BRP4           | BRP3   | BRP2   | BRP1   | BRP0   |

| 0x0142  | CANBTR0 | CANDIRU W | SJW1  | 53000          | DKPO   | DKP4           | DRPS   | DKPZ   | DRPI   | DRPU   |

| 0.0440  |         | R         |       | <b>TOF 000</b> | TOFOOL | <b>TOF 000</b> | T05040 | T05040 | TOFOIL | T05040 |

| 0x0143  | CANBTR1 | w         | SAMP  | TSEG22         | TSEG21 | TSEG20         | TSEG13 | TSEG12 | TSEG11 | TSEG10 |

| 0x0144  | CANRFLG | R         | R     |                | RSTAT1 | RSTAT0         | TSTAT1 | TSTAT0 |        |        |

|         |         | W         | WUPIF | CSCIF          |        |                |        |        | OVRIF  | RXF    |

MC9S12HY/HA-Family Reference Manual, Rev. 1.05