Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc202-e-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

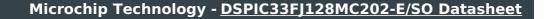

### Pin Diagrams

### Pin Diagrams (Continued)

### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33F/PIC24H Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

- Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33FJ64MC804 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory" (DS70202)

- Section 4. "Program Memory" (DS70202)

- Section 5. "Flash Programming" (DS70191)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer and Power-saving Modes" (DS70196)

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

- Section 14. "Motor Control PWM" (DS70187)

- Section 15. "Quadrature Encoder Interface (QEI)" (DS70208)

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Section 17. "UART" (DS70188)

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- Section 20. "Data Converter Interface (DCI)" (DS70288)

- Section 23. "CodeGuard™ Security" (DS70199)

- Section 24. "Programming and Diagnostics" (DS70207)

- Section 25. "Device Configuration" (DS70194)

- Section 30. "I/O Ports with Peripheral Pin Select (PPS)" (DS70190)

- Section 32. "Interrupts (Part III)" (DS70214)

- Section 33. "Audio Digital-to-Analog Converter (DAC)" (DS70211)

- Section 34. "Comparator" (DS70212)

- Section 35. "Parallel Master Port (PMP)" (DS70299)

- Section 36. "Programmable Cyclic Redundancy Check (CRC)" (DS70298)

- Section 37. "Real-Time Clock and Calendar (RTCC)" (DS70301)

- Section 38. "Direct Memory Access" (DS70215)

- · Section 39. "Oscillator (Part III)" (DS70216)

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit                                           |

|-------|-----------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit                                            |

|       | <ol> <li>Interrupt request has occurred</li> </ol>                                                  |

|       | 0 = Interrupt request has not occurred                                                              |

| bit 0 | INT0IF: External Interrupt 0 Flag Status bit                                                        |

|       | 1 = Interrupt request has occurred                                                                  |

0 = Interrupt request has not occurred

### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 2 | CMIE: Comparator Interrupt Enable bit                                                     |

|-------|-------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| bit 1 | MI2C1IE: I2C1 Master Events Interrupt Enable bit                                          |

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| bit 0 | SI2C1IE: I2C1 Slave Events Interrupt Enable bit                                           |

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

#### **I/O PORTS** 11.0

- This data sheet summarizes the features Note 1: the dsPIC33FJ32MC302/304. of dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 of family devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet, refer to Section 10. "I/O Ports" (DS70193) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, Vss, MCLR and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

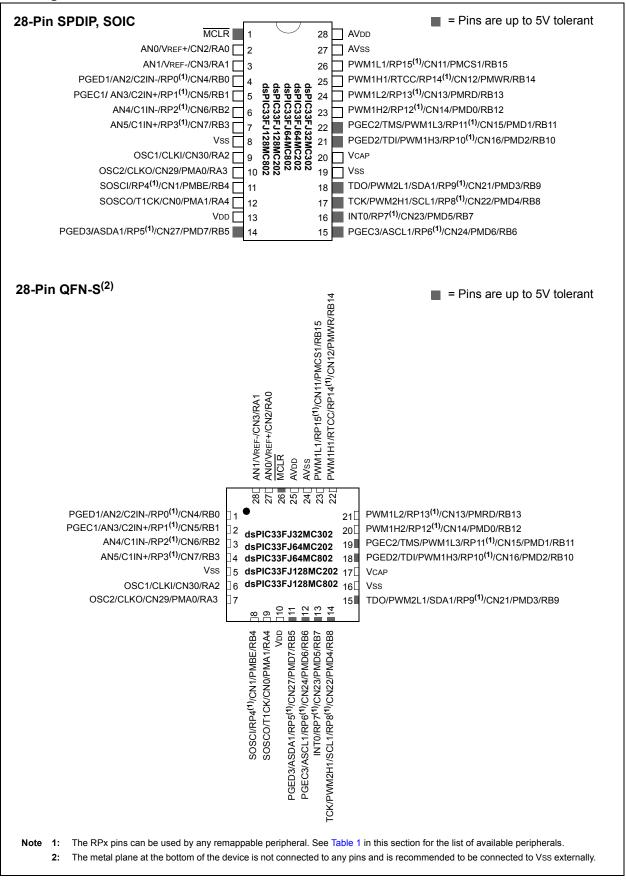

### Parallel I/O (PIO) Ports 11.1

Generally, a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents loop through, in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

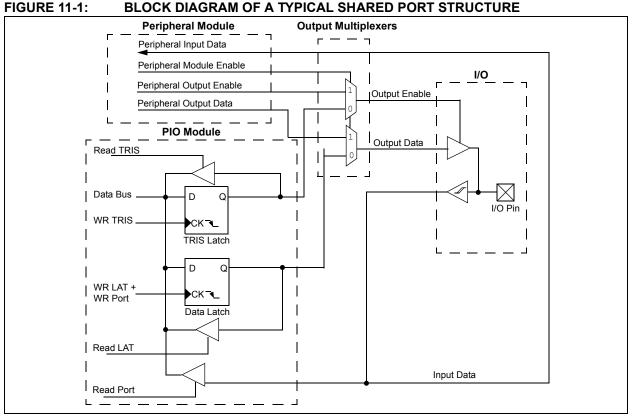

### 11.6.2.2 Output Mapping

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 5-bit fields, with each set associated with one RPn pin (see Register 11-21 through Register 11-33). The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

The list of peripherals for output mapping also includes a null value of '00000' because of the mapping technique. This permits any given pin to remain unconnected from the output of any of the pin selectable peripherals.

### TABLE 11-2: OUTPUT SELECTION FOR REMAPPABLE PIN (RPn)

| Function | RPnR<4:0> | Output Name                              |

|----------|-----------|------------------------------------------|

| NULL     | 00000     | RPn tied to default port pin             |

| C1OUT    | 00001     | RPn tied to Comparator1 Output           |

| C2OUT    | 00010     | RPn tied to Comparator2 Output           |

| U1TX     | 00011     | RPn tied to UART1 Transmit               |

| U1RTS    | 00100     | RPn tied to UART1 Ready To Send          |

| U2TX     | 00101     | RPn tied to UART2 Transmit               |

| U2RTS    | 00110     | RPn tied to UART2 Ready To Send          |

| SDO1     | 00111     | RPn tied to SPI1 Data Output             |

| SCK1     | 01000     | RPn tied to SPI1 Clock Output            |

| SS1      | 01001     | RPn tied to SPI1 Slave Select Output     |

| SDO2     | 01010     | RPn tied to SPI2 Data Output             |

| SCK2     | 01011     | RPn tied to SPI2 Clock Output            |

| SS2      | 01100     | RPn tied to SPI2 Slave Select Output     |

| C1TX     | 10000     | RPn tied to ECAN1 Transmit               |

| OC1      | 10010     | RPn tied to Output Compare 1             |

| OC2      | 10011     | RPn tied to Output Compare 2             |

| OC3      | 10100     | RPn tied to Output Compare 3             |

| OC4      | 10101     | RPn tied to Output Compare 4             |

| UPDN1    | 11010     | RPn tied to QEI1 direction (UPDN) status |

| UPDN2    | 11011     | RPn tied to QEI2 direction (UPDN) status |

© 2007-2012 Microchip Technology Inc.

### 13.0 TIMER2/3 AND TIMER4/5

- This data sheet summarizes the features Note 1: dsPIC33FJ32MC302/304. of the dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 of family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

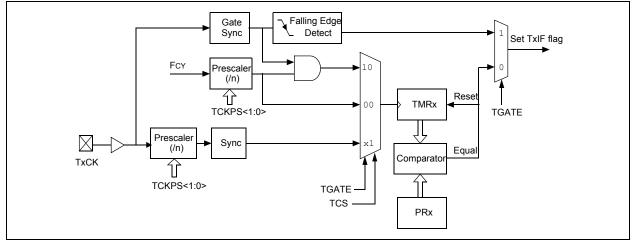

Timer2 and Timer4 are Type B timers with the following specific features:

- A Type B timer can be concatenated with a Type C timer to form a 32-bit timer

- The external clock input (TxCK) is always synchronized to the internal device clock and the clock synchronization is performed after the prescaler

A block diagram of the Type B timer is shown in Figure 13-1.

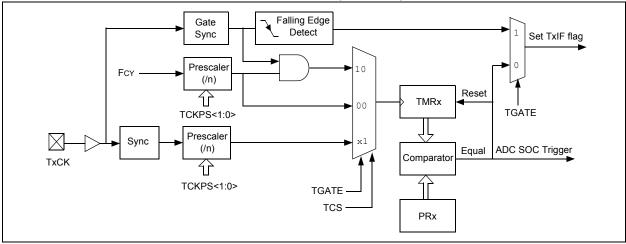

Timer3 and Timer5 are Type C timers with the following specific features:

- A Type C timer can be concatenated with a Type B timer to form a 32-bit timer

- At least one Type C timer has the ability to trigger an analog-to-digital conversion

- The external clock input (TxCK) is always synchronized to the internal device clock and the clock synchronization is performed before the prescaler

A block diagram of the Type C timer is shown in Figure 13-2.

### FIGURE 13-1: TYPE B TIMER BLOCK DIAGRAM (x = 2 or 4)

### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                                                                                     |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                                                       |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                                                                                                               |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                |

|       | <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ul> |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                              |

|       | 1 = Receive complete, I2CxRCV is full                                                                                                                                                                                            |

|       | 0 = Receive not complete, I2CxRCV is empty                                                                                                                                                                                       |

|       | Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.                                                                                                                             |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                             |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                                                                                                                                        |

|       | 0 = Transmit complete, I2CxTRN is empty                                                                                                                                                                                          |

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

## dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| REGISTER     | 21-20: CiRXN<br>REGIS                                                                                                                                                                                                                                                                              | InSID: ECAN<br>TER n (n = 0                                 |             | ANCE FILTE                              | R MASK STA | NDARD IDEI | NTIFIER |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------|-----------------------------------------|------------|------------|---------|--|

| R/W-x        | R/W-x                                                                                                                                                                                                                                                                                              | R/W-x                                                       | R/W-x       | R/W-x                                   | R/W-x      | R/W-x      | R/W-x   |  |

| SID10        | SID9                                                                                                                                                                                                                                                                                               | SID8                                                        | SID7        | SID6                                    | SID5       | SID4       | SID3    |  |

| bit 15       |                                                                                                                                                                                                                                                                                                    |                                                             |             |                                         |            |            | bit 8   |  |

| R/W-x        | R/W-x                                                                                                                                                                                                                                                                                              | R/W-x                                                       | U-0         | R/W-x                                   | U-0        | R/W-x      | R/W-x   |  |

| SID2         | SID1                                                                                                                                                                                                                                                                                               | SID0                                                        | _           | MIDE                                    |            | EID17      | EID16   |  |

| bit 7        |                                                                                                                                                                                                                                                                                                    |                                                             |             |                                         |            |            | bit 0   |  |

| Legend:      |                                                                                                                                                                                                                                                                                                    |                                                             |             |                                         |            |            |         |  |

| R = Readab   | le bit                                                                                                                                                                                                                                                                                             | W = Writable                                                | bit         | U = Unimplemented bit, read as '0'      |            |            |         |  |

| -n = Value a | It POR                                                                                                                                                                                                                                                                                             | '1' = Bit is set                                            |             | '0' = Bit is cleared x = Bit is unknown |            |            |         |  |

| bit 15-5     | 1 = Include bi                                                                                                                                                                                                                                                                                     | tandard Identifi<br>t SIDx in filter o<br>s don't care in f | comparison  | son                                     |            |            |         |  |

| bit 4        | Unimplemen                                                                                                                                                                                                                                                                                         | ted: Read as '                                              | כי          |                                         |            |            |         |  |

| bit 3        | MIDE: Identifi                                                                                                                                                                                                                                                                                     | er Receive Mo                                               | de bit      |                                         |            |            |         |  |

|              | <ul> <li>1 = Match only message types (standard or extended address) that correspond to EXIDE bit in filter</li> <li>0 = Match either standard or extended address message if filters match</li> <li>(i.e., if (Filter SID) = (Message SID) or if (Filter SID/EID) = (Message SID/EID))</li> </ul> |                                                             |             |                                         |            |            |         |  |

| bit 2        | Unimplemen                                                                                                                                                                                                                                                                                         | ted: Read as '                                              | כי          |                                         |            |            |         |  |

| bit 1-0      | EID<17:16>:                                                                                                                                                                                                                                                                                        | Extended Iden                                               | tifier bits |                                         |            |            |         |  |

|              |                                                                                                                                                                                                                                                                                                    | t EIDx in filter o<br>s don't care in f                     | •           | son                                     |            |            |         |  |

# REGISTER 21-21: CIRXMnEID: ECAN<sup>™</sup> ACCEPTANCE FILTER MASK EXTENDED IDENTIFIER REGISTER n (n = 0-2)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| EID7   | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7  |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Include bit EIDx in filter comparison

0 = Bit EIDx is don't care in filter comparison

| R/W-0              | R/W-0                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                   | R/W-0                                                             | R/W-0                                                | R/W-0            | R/W-0              | R/W-0         |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------|------------------|--------------------|---------------|--|

| ALRMEN             | CHIME                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                         | AMA                                                               | SK<3:0>                                              |                  | ALRMP              | TR<1:0>       |  |

| bit 15             |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                         |                                                                   |                                                      |                  |                    | bit 8         |  |

| R/W-0              | R/W-0                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                   | R/W-0                                                             | R/W-0                                                | R/W-0            | R/W-0              | R/W-0         |  |

|                    |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                         | ARP                                                               | T<7:0>                                               |                  |                    |               |  |

| bit 7              |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                         |                                                                   |                                                      |                  |                    | bit (         |  |

| Legend:            |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                         |                                                                   |                                                      |                  |                    |               |  |

| R = Readabl        |                                                                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                                                                            |                                                                   | •                                                    | nented bit, read |                    |               |  |

| -n = Value at      | t POR                                                                                                                                                                                                                                                  | '1' = Bit is set                                                                                                                                                                                                                                                                        | i                                                                 | '0' = Bit is cle                                     | ared             | x = Bit is unkn    | iown          |  |

| bit 15             |                                                                                                                                                                                                                                                        | Alarm Enable bit                                                                                                                                                                                                                                                                        |                                                                   |                                                      |                  |                    |               |  |

| bit 10             | 1 = Alarm i<br>CHIME                                                                                                                                                                                                                                   | s enabled (clear<br>= 0)                                                                                                                                                                                                                                                                |                                                                   | ally after an ala                                    | rm event when    | ever ARPT<7:0      | )> = 0x00 and |  |

|                    | 0 = Alarm i                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                         |                                                                   |                                                      |                  |                    |               |  |

| bit 14             | -                                                                                                                                                                                                                                                      | ime Enable bit                                                                                                                                                                                                                                                                          |                                                                   |                                                      | II avar fram Ov  |                    |               |  |

|                    |                                                                                                                                                                                                                                                        | is enabled; ARP<br>is disabled; ARF                                                                                                                                                                                                                                                     |                                                                   |                                                      |                  |                    |               |  |

| bit 13-10          |                                                                                                                                                                                                                                                        | 0>: Alarm Mask                                                                                                                                                                                                                                                                          |                                                                   |                                                      |                  |                    |               |  |

|                    |                                                                                                                                                                                                                                                        | erved – do not u                                                                                                                                                                                                                                                                        | •                                                                 | bito                                                 |                  |                    |               |  |

|                    | 101x = Reserved – do not use                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                         |                                                                   |                                                      |                  |                    |               |  |

|                    | 1001 <b>= Onc</b>                                                                                                                                                                                                                                      | e a year (excep                                                                                                                                                                                                                                                                         | t when config                                                     | ured for Februa                                      | ry 29th, once e  | very 4 years)      |               |  |

|                    | 1000 <b>= Onc</b>                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                         |                                                                   |                                                      |                  |                    |               |  |

|                    | 0111 <b>= Onc</b>                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                         |                                                                   |                                                      |                  |                    |               |  |

|                    | 0110 <b>= Onc</b><br>0101 <b>= Eve</b>                                                                                                                                                                                                                 | •                                                                                                                                                                                                                                                                                       |                                                                   |                                                      |                  |                    |               |  |

|                    |                                                                                                                                                                                                                                                        | ry 10 minutes                                                                                                                                                                                                                                                                           |                                                                   |                                                      |                  |                    |               |  |

|                    |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                         |                                                                   |                                                      |                  |                    |               |  |

|                    | 0011 <b>= Eve</b>                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                         |                                                                   |                                                      |                  |                    |               |  |

|                    | 0011 <b>= Eve</b><br>0010 <b>= Eve</b>                                                                                                                                                                                                                 | ry minute<br>ry 10 seconds                                                                                                                                                                                                                                                              |                                                                   |                                                      |                  |                    |               |  |

|                    | 0011 <b>= Eve</b><br>0010 <b>= Eve</b><br>0001 <b>= Eve</b>                                                                                                                                                                                            | ry minute<br>ry 10 seconds<br>ry second                                                                                                                                                                                                                                                 |                                                                   |                                                      |                  |                    |               |  |

|                    | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br>0000 = Eve                                                                                                                                                                                                   | ry minute<br>ry 10 seconds<br>ry second<br>ry half second                                                                                                                                                                                                                               |                                                                   |                                                      |                  |                    |               |  |

| bit 9-8            | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br>0000 = Eve<br>ALRMPTR<                                                                                                                                                                                       | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br>< <b>1:0&gt;:</b> Alarm Va                                                                                                                                                                                                 | -                                                                 |                                                      |                  |                    |               |  |

| bit 9-8            | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br>0000 = Eve<br>ALRMPTR<br>Points to the                                                                                                                                                                       | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br>< <b>1:0&gt;:</b> Alarm Val<br>corresponding <i>J</i>                                                                                                                                                                      | Alarm Value re                                                    | gisters when re                                      | ading ALRMVA     |                    |               |  |

| bit 9-8            | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br>0000 = Eve<br>ALRMPTR<<br>Points to the<br>the ALRMP                                                                                                                                                         | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br>< <b>1:0&gt;:</b> Alarm Val<br>corresponding <i>J</i><br>TR<1:0> value d                                                                                                                                                   | Alarm Value re                                                    | gisters when re                                      | ading ALRMVA     |                    |               |  |

| bit 9-8            | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br>0000 = Eve<br>ALRMPTR<<br>Points to the<br>the ALRMP                                                                                                                                                         | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br>< <b>1:0&gt;:</b> Alarm Val<br>e corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u>                                                                                                                             | Alarm Value re                                                    | gisters when re                                      | ading ALRMVA     |                    |               |  |

| bit 9-8            | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br>0000 = Eve<br>ALRMPTR<<br>Points to the<br>the ALRMP                                                                                                                                                         | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br>< <b>1:0&gt;:</b> Alarm Val<br>corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u><br>lemented                                                                                                                   | Alarm Value re                                                    | gisters when re                                      | ading ALRMVA     |                    |               |  |

| bit 9-8            | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br>ALRMPTR<<br>Points to the<br>the ALRMP<br><u>ALRMVAL&lt;</u><br>11 = Unimp<br>10 = ALRM<br>01 = ALRM                                                                                                         | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br>< <b>1:0&gt;:</b> Alarm Val<br>e corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u><br>lemented<br>MNTH<br>WD                                                                                                   | Alarm Value re                                                    | gisters when re                                      | ading ALRMVA     |                    |               |  |

| bit 9-8            | 0011 = Eve<br>0010 = Eve<br>0000 = Eve<br><b>ALRMPTR</b><br><b>Points to the</b><br><b>the ALRMP</b><br><u>ALRMVAL&lt;</u><br>11 = Unimp<br>10 = ALRM<br>01 = ALRM<br>00 = ALRM                                                                        | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br>< <b>1:0&gt;:</b> Alarm Val<br>e corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u><br>lemented<br>MNTH<br>WD<br>MIN                                                                                            | Alarm Value re                                                    | gisters when re                                      | ading ALRMVA     |                    |               |  |

| bit 9-8            | 0011 = Eve<br>0010 = Eve<br>0000 = Eve<br><b>ALRMPTR</b><br><b>Points to the</b><br><b>the ALRMP</b><br><b>ALRMVAL</b><br>11 = Unimp<br>10 = ALRM<br>01 = ALRM<br>00 = ALRM                                                                            | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br>< <b>1:0&gt;:</b> Alarm Val<br>e corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u><br>lemented<br>MNTH<br>WD<br>MIN<br><u>7:0&gt;:</u>                                                                         | Alarm Value re                                                    | gisters when re                                      | ading ALRMVA     |                    |               |  |

| bit 9-8            | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br><b>ALRMPTR</b><br><b>Points to the</b><br><b>the ALRMP</b><br><b>ALRMVAL</b><br>11 = Unimp<br>10 = ALRM<br>01 = ALRM<br>00 = ALRM<br>ALRMVAL<br>11 = Unimp                                                   | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br>< <b>1:0&gt;:</b> Alarm Val<br>e corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u><br>lemented<br>MNTH<br>WD<br>MIN<br><u>7:0&gt;:</u><br>lemented                                                             | Alarm Value re                                                    | gisters when re                                      | ading ALRMVA     |                    |               |  |

| bit 9-8            | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br><b>ALRMPTR</b><br><b>Points to the</b><br><b>the ALRMP</b><br><b>ALRMVAL</b><br>11 = Unimp<br>10 = ALRM<br>00 = ALRM<br><u>ALRMVAL</u><br>11 = Unimp<br>10 = ALRM                                            | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br><b>&lt;1:0&gt;:</b> Alarm Val<br>e corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u><br>lemented<br>MNTH<br>WD<br>MIN<br><u>7:0&gt;:</u><br>lemented<br>DAY                                                    | Alarm Value re                                                    | gisters when re                                      | ading ALRMVA     |                    |               |  |

| bit 9-8            | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br><b>ALRMPTR</b><br><b>Points to the</b><br><b>the ALRMP</b><br><b>ALRMVAL</b><br>11 = Unimp<br>10 = ALRM<br>01 = ALRM<br>00 = ALRM<br>ALRMVAL<br>11 = Unimp                                                   | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br><b>&lt;1:0&gt;:</b> Alarm Val<br>e corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u><br>lemented<br>MNTH<br>WD<br>MIN<br><u>7:0&gt;:</u><br>lemented<br>DAY<br>HR                                              | Alarm Value re                                                    | gisters when re                                      | ading ALRMVA     |                    |               |  |

|                    | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br><b>ALRMPTR</b><br>Points to the<br>the ALRMP<br><u>ALRMVAL</u><br>11 = Unimp<br>10 = ALRM<br>01 = ALRM<br>00 = ALRM<br>11 = Unimp<br>10 = ALRM<br>01 = ALRM<br>01 = ALRM                                     | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br><b>&lt;1:0&gt;:</b> Alarm Val<br>e corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u><br>lemented<br>MNTH<br>WD<br>MIN<br><u>7:0&gt;:</u><br>lemented<br>DAY<br>HR<br>SEC                                       | Alarm Value re<br>ecrements on                                    | gisters when re<br>every read or w                   | ading ALRMVA     |                    |               |  |

|                    | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br><b>ALRMPTR</b><br><b>Points to the</b><br><b>the ALRMP</b><br><b>ALRMVAL</b><br>11 = Unimp<br>10 = ALRM<br>00 = ALRM<br>11 = Unimp<br>10 = ALRM<br>00 = ALRM<br>01 = ALRM<br>01 = ALRM                       | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br><b>&lt;1:0&gt;:</b> Alarm Val<br>e corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u><br>lemented<br>MNTH<br>WD<br>MIN<br><u>7:0&gt;:</u><br>lemented<br>DAY<br>HR                                              | Alarm Value re<br>ecrements on<br>Counter Value                   | gisters when re<br>every read or w                   | ading ALRMVA     |                    |               |  |

|                    | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br><b>ALRMPTR</b><br><b>Points to the</b><br><b>the ALRMP</b><br><b>ALRMVAL</b><br>11 = Unimp<br>10 = ALRM<br>00 = ALRM<br>11 = Unimp<br>10 = ALRM<br>00 = ALRM<br>01 = ALRM<br>01 = ALRM                       | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br>< <b>1:0&gt;:</b> Alarm Val<br>e corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u><br>lemented<br>MNTH<br>WD<br>MIN<br><u>7:0&gt;:</u><br>lemented<br>DAY<br>HR<br>SEC<br>:: Alarm Repeat                      | Alarm Value re<br>ecrements on<br>Counter Value                   | gisters when re<br>every read or w                   | ading ALRMVA     |                    |               |  |

|                    | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br><b>ALRMPTR</b><br><b>Points to the</b><br><b>the ALRMP</b><br><b>ALRMVAL</b><br>11 = Unimp<br>10 = ALRM<br>00 = ALRM<br>11 = Unimp<br>10 = ALRM<br>00 = ALRM<br>01 = ALRM<br>01 = ALRM                       | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br>< <b>1:0&gt;:</b> Alarm Val<br>e corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u><br>lemented<br>MNTH<br>WD<br>MIN<br><u>7:0&gt;:</u><br>lemented<br>DAY<br>HR<br>SEC<br>:: Alarm Repeat                      | Alarm Value re<br>ecrements on<br>Counter Value                   | gisters when re<br>every read or w                   | ading ALRMVA     |                    |               |  |

| bit 9-8<br>bit 7-0 | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br>0000 = Eve<br>ALRMPTR<br>Points to the<br>the ALRMP<br><u>ALRMVAL&lt;</u><br>11 = Unimp<br>10 = ALRM<br>00 = ALRM<br>01 = ALRM<br>01 = ALRM<br>01 = ALRM<br>01 = ALRM<br>01 = ALRM<br>01 = ALRM              | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br>< <b>1:0&gt;:</b> Alarm Val<br>e corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u><br>lemented<br>MNTH<br>WD<br>MIN<br><u>7:0&gt;:</u><br>lemented<br>DAY<br>HR<br>SEC<br>:: Alarm Repeat<br>= Alarm will repe | Alarm Value re<br>ecrements on<br>Counter Value<br>eat 255 more   | gisters when re<br>every read or w                   | ading ALRMVA     |                    |               |  |

|                    | 0011 = Eve<br>0010 = Eve<br>0001 = Eve<br>0000 = Eve<br>ALRMPTR<br>Points to the<br>the ALRMP<br><u>ALRMVAL&lt;</u><br>11 = Unimp<br>10 = ALRM<br>00 = ALRM<br>01 = ALRM | ry minute<br>ry 10 seconds<br>ry second<br>ry half second<br>< <b>1:0&gt;:</b> Alarm Val<br>e corresponding <i>J</i><br>TR<1:0> value d<br><u>15:8&gt;:</u><br>lemented<br>MNTH<br>WD<br>MIN<br><u>7:0&gt;:</u><br>lemented<br>DAY<br>HR<br>SEC<br>:: Alarm Repeat                      | Alarm Value re<br>ecrements on<br>Counter Value<br>eat 255 more f | gisters when re<br>every read or w<br>e bits<br>imes | eading ALRMVA    | ALH until it reach | nes '00'.     |  |

### REGISTER 25-3: ALCFGRPT: ALARM CONFIGURATION REGISTER

# **REGISTER 25-8:** ALRMVAL (WHEN ALRMPTR<1:0> = 10): ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0       | U-0 | U-0     | R/W-x | R/W-x | R/W-x   | R/W-x | R/W-x |

|-----------|-----|---------|-------|-------|---------|-------|-------|

| — — MTHTE |     | MTHTEN0 |       | MTHON | IE<3:0> |       |       |

| bit 15    |     |         |       |       |         |       | bit 8 |

|           |     |         |       |       |         |       |       |

| U-0       | U-0 | R/W-x   | R/W-x | R/W-x | R/W-x   | R/W-x | R/W-x |

| U-0   | 0-0 | R/W-X | R/W-X  | R/W-X | R/W-X | R/W-X  | R/W-X |

|-------|-----|-------|--------|-------|-------|--------|-------|

| —     | —   | DAYTE | N<1:0> |       | DAYON | E<3:0> |       |

| bit 7 | :7  |       |        |       |       |        | bit 0 |

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| bit 15-13 | Unimplemented: Read as '0'                                                                  |

|-----------|---------------------------------------------------------------------------------------------|

| bit 12    | MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit; contains a value of 0 or 1       |

| bit 11-8  | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit; contains a value from 0 to 9 |

| bit 7-6   | Unimplemented: Read as '0'                                                                  |

| bit 5-4   | DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit; contains a value from 0 to 3   |

| bit 3-0   | DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit; contains a value from 0 to 9   |

|           |                                                                                             |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

# **REGISTER 25-9:** ALRMVAL (WHEN ALRMPTR<1:0> = 01): ALARM WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-----|-------|-------|-------|

| —      |     | —   |     | —   | WDAY2 | WDAY1 | WDAY0 |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | U-0 | R/W-x | R/W-x  | R/W-x | R/W-x | R/W-x  | R/W-x |

|-------|-----|-------|--------|-------|-------|--------|-------|

| —     | —   | HRTEN | N<1:0> |       | HRON  | E<3:0> |       |

| bit 7 |     |       |        |       |       |        | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

bit 10-8 WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit; contains a value from 0 to 6

bit 7-6 Unimplemented: Read as '0'

bit 5-4 HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit; contains a value from 0 to 2

bit 3-0 HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit; contains a value from 0 to 9

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### 28.0 SPECIAL FEATURES

- Note 1: This data sheet summarizes the features dsPIC33FJ32MC302/304. of the dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 devices include the following features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components:

- Flexible configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- · JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

#### Address Bit 7 Bit 6 Bit 1 Bit 0 Name Bit 5 Bit 4 Bit 3 Bit 2 0xF80000 FBS RBS<1:0> BSS<2:0> BWRP FSS<sup>(1)</sup> 0xF80002 RSS<1:0> SSS<2:0> SWRP 0xF80004 GWRP FGS \_\_\_\_ \_\_\_\_ GSS<1:0> \_\_\_\_ \_\_\_\_ \_\_\_\_ 0xF80006 FOSCSEL FNOSC<2:0> IESO OSCIOFNC POSCMD<1:0> 0xF80008 FOSC FCKSM<1:0> **IOL1WAY** 0xF8000A FWDT FWDTEN WINDIS \_ WDTPRE WDTPOST<3:0> PWMPIN 0xF8000C FPOR HPOL LPOL ALTI2C FPWRT<2:0> Reserved<sup>(2)</sup> 0xF8000E FICD **JTAGEN** ICS<1:0> 0xF80010 FUID0 User Unit ID Byte 0 0xF80012 FUID1 User Unit ID Byte 1 0xF80014 FUID2 User Unit ID Byte 2 0xF80016 FUID3 User Unit ID Byte 3

### TABLE 28-1: DEVICE CONFIGURATION REGISTER MAP

**Legend:** — = unimplemented bit, read as '0'.

Note 1: This Configuration register is not available and reads as 0xFF on dsPIC33FJ32MC302/304 devices.

2: These bits are reserved for use by development tools and must be programmed as '1'.

### 28.1 Configuration Bits

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 devices provide nonvolatile memory implementations for device Configuration bits. Refer to **Section 25.** "**Device Configuration**" (DS70194) in the "*dsPIC33F/PIC24H Family Reference Manual*" for more information on this implementation.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The individual Configuration bit descriptions for the Configuration registers are shown in Table 28-2.

Note that address 0xF80000 is beyond the user program memory space. It belongs to the configuration memory space (0x800000-0xFFFFFF), which can only be accessed using table reads and table writes.

The Device Configuration register map is shown in Table 28-1.

### 31.1 DC Characteristics

### TABLE 31-1: OPERATING MIPS VS. VOLTAGE

|                |                         |                       | Max MIPS                                                                   |

|----------------|-------------------------|-----------------------|----------------------------------------------------------------------------|

| Characteristic | VDD Range<br>(in Volts) | Temp Range<br>(in °C) | dsPIC33FJ32MC302/304,<br>dsPIC33FJ64MCX02/X04 and<br>dsPIC33FJ128MCX02/X04 |

| _              | 3.0-3.6V <sup>(1)</sup> | -40°C to +85°C        | 40                                                                         |

|                | 3.0-3.6V <sup>(1)</sup> | -40°C to +125°C       | 40                                                                         |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 31-11 for the minimum and maximum BOR values.

### TABLE 31-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                    | Symbol | Min           | Тур         | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------|--------|---------------|-------------|------|------|

| Industrial Temperature Devices                                                                                            |        |               |             |      |      |

| Operating Junction Temperature Range                                                                                      | TJ     | -40           | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                                                       | TA     | -40           | —           | +85  | °C   |

| Extended Temperature Devices                                                                                              |        |               |             |      |      |

| Operating Junction Temperature Range                                                                                      | TJ     | -40           | —           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                       | TA     | -40           | —           | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation: | PD     | D PINT + PI/O |             |      | w    |

| $I/O = \Sigma (\{VDD - VOH\} \times IOH\} + \Sigma (VOL \times IOL)$                                                      |        |               |             |      |      |

| Maximum Allowed Power Dissipation                                                                                         | PDMAX  | (             | TJ – TA)/θJ | IA   | W    |

### TABLE 31-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур | Мах | Unit | Notes |

|------------------------------------------|--------|-----|-----|------|-------|

| Package Thermal Resistance, 44-pin QFN   | θja    | 30  | _   | °C/W | 1     |

| Package Thermal Resistance, 44-pin TFQP  | θја    | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SPDIP | θја    | 45  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SOIC  | θја    | 50  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin QFN-S | θја    | 30  | —   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

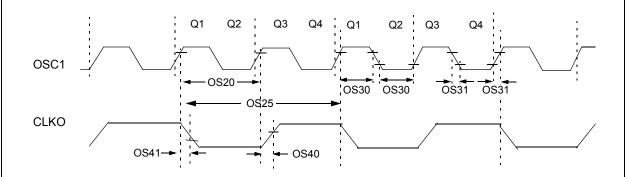

### FIGURE 31-2: EXTERNAL CLOCK TIMING

### TABLE 31-16: EXTERNAL CLOCK TIMING REQUIREMENTS

| АС СНА       | PACTER        |                                                                                    | (unless otherw                                                                                                                                                                               | vise state         |              | to 3.6V |                          |  |

|--------------|---------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|---------|--------------------------|--|

|              |               |                                                                                    | $\begin{array}{ll} \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |              |         |                          |  |

| Param<br>No. | Symb          | Characteristic                                                                     | Min                                                                                                                                                                                          | Typ <sup>(1)</sup> | Мах          | Units   | Conditions               |  |

| OS10         | FIN           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                                                                                                                                                           | —                  | 40           | MHz     | EC                       |  |

|              |               | Oscillator Crystal Frequency                                                       | 3.5                                                                                                                                                                                          | _                  | 10           | MHz     | XT                       |  |

|              |               |                                                                                    | 10                                                                                                                                                                                           | —                  | 40           | MHz     | HS                       |  |

|              |               |                                                                                    | — —                                                                                                                                                                                          | —                  | 33           | kHz     | Sosc                     |  |

|              |               |                                                                                    | 3.5                                                                                                                                                                                          | —                  | 10           | MHz     | AUX_OSC_FIN              |  |

| OS20         | Tosc          | Tosc = 1/Fosc                                                                      | 12.5                                                                                                                                                                                         | _                  | DC           | ns      | _                        |  |

| OS25         | TCY           | Instruction Cycle Time <sup>(2)</sup>                                              | 25                                                                                                                                                                                           | _                  | DC           | ns      | —                        |  |

| OS30         | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time                                       | 0.375 x Tosc                                                                                                                                                                                 | —                  | 0.625 x Tosc | ns      | EC                       |  |

| OS31         | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time                                      | -                                                                                                                                                                                            | —                  | 20           | ns      | EC                       |  |

| OS40         | TckR          | CLKO Rise Time <sup>(3)</sup>                                                      | —                                                                                                                                                                                            | 5.2                |              | ns      | —                        |  |

| OS41         | TckF          | CLKO Fall Time <sup>(3)</sup>                                                      | _                                                                                                                                                                                            | 5.2                |              | ns      | —                        |  |

| OS42         | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                             | 14                                                                                                                                                                                           | 16                 | 18           | mA/V    | VDD = 3.3V<br>TA = +25°C |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Instruction cycle period (Tcr) equals two times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: Data for this parameter is Preliminary. This parameter is characterized, but not tested in manufacturing.

| АС СНА       | RACTERIST             | TICS                                         | Standard Operating Conditions: 3.0V<br>(unless otherwise stated)Operating temperature-40°C ≤TA ≤+<br>-40°C ≤TA ≤+ |                    |     |       |                               |

|--------------|-----------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-------------------------------|