Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

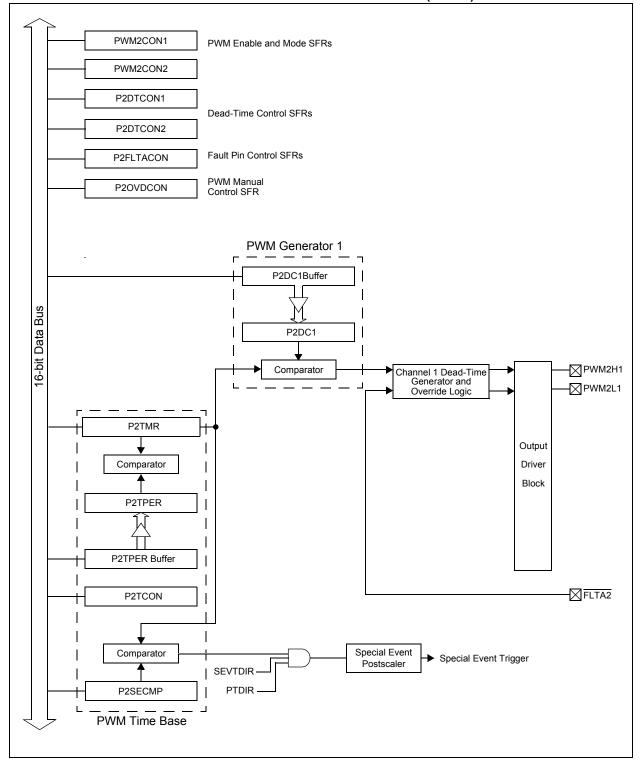

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

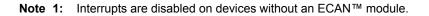

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc202-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

- **Note 1:** This data sheet summarizes the features the dsPIC33FJ32MC302/304, of dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device specific information for the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 Digital Signal Controller (DSC) devices. The dsPIC33F devices contain extensive Digital Signal Processor (DSP) functionality with a high performance 16-bit Microcontroller (MCU) architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules in the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 families of devices. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

| Pin Name         Pin Buffer Type         PPS         Description |     |        |     | Description                                                                                                |

|------------------------------------------------------------------|-----|--------|-----|------------------------------------------------------------------------------------------------------------|

| TMS                                                              | Ι   | ST     | No  | JTAG Test mode select pin.                                                                                 |

| ТСК                                                              | Ι   | ST     | No  | JTAG test clock input pin.                                                                                 |

| TDI                                                              | Ι   | ST     | No  | JTAG test data input pin.                                                                                  |

| TDO                                                              | 0   | —      | No  | JTAG test data output pin.                                                                                 |

| INDX1                                                            | Ι   | ST     | Yes | Quadrature Encoder Index1 Pulse input.                                                                     |

| QEA1                                                             | I   | ST     | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary Timer External Clock/Gate input in Timer mode.    |

| QEB1                                                             | Ι   | ST     | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary Timer External Clock/Gate input in Timer mode.    |

| UPDN1                                                            | 0   | CMOS   | Yes | Position Up/Down Counter Direction State.                                                                  |

| INDX2                                                            | Ι   | ST     | Yes | Quadrature Encoder Index2 Pulse input.                                                                     |

| QEA2                                                             | Ι   | ST     | Yes | Quadrature Encoder Phase A input in QEI2 mode. Auxiliary Timer<br>External Clock/Gate input in Timer mode. |

| QEB2                                                             | Ι   | ST     | Yes | Quadrature Encoder Phase A input in QEI2 mode. Auxiliary Timer External Clock/Gate input in Timer mode.    |

| UPDN2                                                            | 0   | CMOS   | Yes | Position Up/Down Counter Direction State.                                                                  |

| C1RX                                                             | I   | ST     | Yes | ECAN1 bus receive pin.                                                                                     |

| C1TX                                                             | 0   | —      | Yes | ECAN1 bus transmit pin.                                                                                    |

| RTCC                                                             | 0   | _      | No  | Real-Time Clock Alarm Output.                                                                              |

| CVREF                                                            | 0   | ANA    | No  | Comparator Voltage Reference Output.                                                                       |

| C1IN-                                                            | Ι   | ANA    | No  | Comparator 1 Negative Input.                                                                               |

| C1IN+                                                            | I   | ANA    | No  | Comparator 1 Positive Input.                                                                               |

| C1OUT                                                            | 0   | _      | Yes | Comparator 1 Output.                                                                                       |

| C2IN-                                                            | Ι   | ANA    | No  | Comparator 2 Negative Input.                                                                               |

| C2IN+                                                            | Ι   | ANA    | No  | Comparator 2 Positive Input.                                                                               |

| C2OUT                                                            | 0   |        | Yes | Comparator 2 Output.                                                                                       |

| PMA0                                                             | I/O | TTL/ST | No  | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes).                 |

| PMA1                                                             | I/O | TTL/ST | No  | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes).                 |

| PMA2 -PMPA10                                                     | 0   | _      | No  | Parallel Master Port Address (Demultiplexed Master modes).                                                 |

| PMBE                                                             | Ō   |        | No  | Parallel Master Port Byte Enable Strobe.                                                                   |

| PMCS1                                                            | 0   | _      | No  | Parallel Master Port Chip Select 1 Strobe.                                                                 |

| PMD0-PMPD7                                                       | I/O | TTL/ST | No  | Parallel Master Port Data (Demultiplexed Master mode) or Address/<br>Data (Multiplexed Master modes).      |

| PMRD                                                             | 0   | _      | No  | Parallel Master Port Read Strobe.                                                                          |

| PMWR                                                             | Ō   | —      | No  | Parallel Master Port Write Strobe.                                                                         |

| DAC1RN                                                           | 0   | _      | No  | DAC1 Negative Output.                                                                                      |

| DAC1RP                                                           | 0   | —      | No  | DAC1 Positive Output.                                                                                      |

| DAC1RM                                                           | 0   |        | No  | DAC1 Output indicating middle point value (typically 1.65V).                                               |

| DAC2RN                                                           | 0   |        | No  | DAC2 Negative Output.                                                                                      |

| DAC2RP                                                           | 0   | —      | No  | DAC2 Positive Output.                                                                                      |

| DAC2RM                                                           | 0   | 1      | No  | DAC2 Output indicating middle point value (typically 1.65V).                                               |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog inputP = PoweO = OutputI = InputTTL = TTL input buffer

#### 6.9 Configuration Mismatch Reset

To maintain the integrity of the peripheral pin select control registers, they are constantly monitored with shadow registers in hardware. If an unexpected change in any of the registers occur (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset occurs.

The Configuration Mismatch Flag bit (CM) in the Reset Control register (RCON<9>) is set to indicate the configuration mismatch Reset. Refer to **Section 11.0 "I/O Ports"** for more information on the configuration mismatch Reset.

Note: The configuration mismatch feature and associated reset flag is not available on all devices.

### 6.10 Illegal Condition Device Reset

An illegal condition device Reset occurs due to the following sources:

- Illegal Opcode Reset

- Uninitialized W Register Reset

- · Security Reset

**TABLE 6-3**:

The Illegal Opcode or Uninitialized W Access Reset Flag bit (IOPUWR) in the Reset Control register (RCON<14>) is set to indicate the illegal condition device Reset.

#### 6.10.0.1 ILLEGAL OPCODE RESET

A device Reset is generated if the device attempts to execute an illegal opcode value that is fetched from program memory.

The illegal opcode Reset function can prevent the device from executing program memory sections that are used to store constant data. To take advantage of the illegal opcode Reset, use only the lower 16 bits of

**RESET FLAG BIT OPERATION**<sup>(1)</sup>

each program memory section to store the data values. The upper 8 bits should be programmed with 3Fh, which is an illegal opcode value.

#### 6.10.0.2 UNINITIALIZED W REGISTER RESET

Any attempts to use the uninitialized W register as an address pointer will Reset the device. The W register array (with the exception of W15) is cleared during all resets and is considered uninitialized until written to.

#### 6.10.0.3 SECURITY RESET

If a Program Flow Change (PFC) or Vector Flow Change (VFC) targets a restricted location in a protected segment (Boot and Secure Segment), that operation will cause a security Reset.

The PFC occurs when the Program Counter is reloaded as a result of a Call, Jump, Computed Jump, Return, Return from Subroutine, or other form of branch instruction.

The VFC occurs when the Program Counter is reloaded with an Interrupt or Trap vector.

Refer to Section 28.8 "Code Protection and CodeGuard Security" for more information on Security Reset.

## 6.11 Using the RCON Status Bits

The user application can read the Reset Control register (RCON) after any device Reset to determine the cause of the reset.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

Table 6-3 provides a summary of the Reset flag bit operation.

| Flag Bit         | Set by:                                                             | Cleared by:                                      |

|------------------|---------------------------------------------------------------------|--------------------------------------------------|

| TRAPR (RCON<15>) | Trap conflict event                                                 | POR, BOR                                         |

| IOPWR (RCON<14>) | Illegal opcode or uninitialized W register access or Security Reset | POR, BOR                                         |

| CM (RCON<9>)     | Configuration Mismatch                                              | POR, BOR                                         |

| EXTR (RCON<7>)   | MCLR Reset                                                          | POR                                              |

| SWR (RCON<6>)    | RESET instruction                                                   | POR, BOR                                         |

| WDTO (RCON<4>)   | WDT time-out                                                        | PWRSAV instruction, CLRWDT instruction, POR, BOR |

| SLEEP (RCON<3>)  | PWRSAV #SLEEP instruction                                           | POR, BOR                                         |

| IDLE (RCON<2>)   | PWRSAV #IDLE instruction                                            | POR, BOR                                         |

| BOR (RCON<1>)    | POR, BOR                                                            | -                                                |

| POR (RCON<0>)    | POR                                                                 | _                                                |

Note 1: All Reset flag bits can be set or cleared by user software.

### FIGURE 7-1: dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/ X04 INTERRUPT VECTOR TABLE

|                                   | Reset – GOTO Instruction          | 0x000000          |                                                        |

|-----------------------------------|-----------------------------------|-------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Address              | 0x000002          |                                                        |

|                                   | Reserved                          | 0x000004          |                                                        |

|                                   | Oscillator Fail Trap Vector       |                   |                                                        |

|                                   | Address Error Trap Vector         |                   |                                                        |

|                                   | Stack Error Trap Vector           |                   |                                                        |

|                                   | Math Error Trap Vector            |                   |                                                        |

|                                   | DMA Error Trap Vector             |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Interrupt Vector 0                | 0x000014          |                                                        |

|                                   | Interrupt Vector 1                |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | Interrupt Vector 52               | 0x00007C          | Interview Vector Table (IVT)(1)                        |

|                                   | Interrupt Vector 53               | 0x00007E          | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| ity                               | Interrupt Vector 54               | 0x000080          |                                                        |

| jo                                | ~                                 |                   |                                                        |

| Ē                                 | ~                                 |                   |                                                        |

| de                                | ~                                 |                   |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 116              | 0x0000FC          |                                                        |

| Iral                              | Interrupt Vector 117              | 0x0000FE          |                                                        |

| atr                               | Reserved                          | 0x000100          |                                                        |

| Z                                 | Reserved                          | 0x000102          |                                                        |

| sinç                              | Reserved                          |                   |                                                        |

| eas                               | Oscillator Fail Trap Vector       |                   |                                                        |

| ů –                               | Address Error Trap Vector         |                   |                                                        |

| ă                                 | Stack Error Trap Vector           |                   |                                                        |

|                                   | Math Error Trap Vector            |                   |                                                        |

|                                   | DMA Error Trap Vector             |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Interrupt Vector 0                | 0x000114          |                                                        |

|                                   | Interrupt Vector 1                |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 |                   | (4)                                                    |

|                                   | ~                                 |                   | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52               | 0x00017C          |                                                        |

|                                   | Interrupt Vector 53               | 0x00017E          |                                                        |

|                                   | Interrupt Vector 54               | 0x000180          |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 | _                 |                                                        |

|                                   |                                   |                   | 1                                                      |

|                                   | Interrupt Vector 116              |                   |                                                        |

| ₩                                 | Interrupt Vector 117              | 0x0001FE          |                                                        |

| ۲                                 | Start of Code                     | 0x000200          |                                                        |

|                                   |                                   |                   |                                                        |

|                                   |                                   |                   |                                                        |

| Note 1: See                       | Table 7-1 for the list of impleme | ented interrupt v | rectors                                                |

|                                   |                                   |                   |                                                        |

|                                   |                                   |                   |                                                        |

#### 7.5 Interrupt Registers

| R-0    | R-0 | R/C-0 | R/C-0 | R-0 | R/C-0 | R -0 | R/W-0 |

|--------|-----|-------|-------|-----|-------|------|-------|

| OA     | OB  | SA    | SB    | OAB | SAB   | DA   | DC    |

| bit 15 |     |       |       |     |       |      | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | Ν     | OV    | Z     | C     |

| bit 7                |                      |                      |     |       |       |       | bit 0 |

## Legend:

| C = Clear only bit | R = Readable bit     | U = Unimplemented bit, read as '0' |  |

|--------------------|----------------------|------------------------------------|--|

| S = Set only bit   | W = Writable bit     | -n = Value at POR                  |  |

| '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |  |

bit 7-5

IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup>

111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

Note 1: For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

#### CORCON: CORE CONTROL REGISTER<sup>(1)</sup> **REGISTER 7-2:**

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R-0 | R-0     | R-0   |

|--------|-----|-----|-------|-------|-----|---------|-------|

| —      | —   | —   | US    | EDT   |     | DL<2:0> |       |

| bit 15 |     |     |       |       |     |         | bit 8 |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-------|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | PSV   | RND   | IF    |

| bit 7 |       |       |        |                     |       |       | bit 0 |

| Legend:             | C = Clear only bit  |                             |                  |

|---------------------|---------------------|-----------------------------|------------------|

| R = Readable bit    | W = Writable bit    | -n = Value at POR           | '1' = Bit is set |

| 0' = Bit is cleared | 'x = Bit is unknown | U = Unimplemented bit, read | l as '0'         |

**IPL3:** CPU Interrupt Priority Level Status bit 3<sup>(2)</sup> bit 3

- 1 = CPU interrupt priority level is greater than 7

- 0 = CPU interrupt priority level is 7 or less

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| <b>REGISTER 7</b> | -3: INTCC                                                  | N1: INTERR                                                                                                                 | UPT CONTR        | ROL REGISTE                        | ER 1             |                 |           |  |  |  |  |

|-------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------|------------------|-----------------|-----------|--|--|--|--|

| R/W-0             | R/W-0                                                      | R/W-0                                                                                                                      | R/W-0            | R/W-0                              | R/W-0            | R/W-0           | R/W-0     |  |  |  |  |

| NSTDIS            | OVAERR                                                     | OVBERR                                                                                                                     | COVAERR          | COVBERR                            | OVATE            | OVBTE           | COVTE     |  |  |  |  |

| bit 15            |                                                            |                                                                                                                            |                  |                                    |                  |                 | bit 8     |  |  |  |  |

| R/W-0             | R/W-0                                                      | R/W-0                                                                                                                      | R/W-0            | R/W-0                              | R/W-0            | R/W-0           | U-0       |  |  |  |  |

| SFTACERR          |                                                            | DMACERR                                                                                                                    |                  | ADDRERR                            |                  | OSCFAIL         | 0-0       |  |  |  |  |

| bit 7             | DIV0ERR                                                    | DIVIACERR                                                                                                                  | MATHERR          | ADDRERR                            | STKERR           | USCFAIL         | <br>bit 0 |  |  |  |  |

|                   |                                                            |                                                                                                                            |                  |                                    |                  |                 |           |  |  |  |  |

| Legend:           |                                                            |                                                                                                                            |                  |                                    |                  |                 |           |  |  |  |  |

| R = Readable      | bit                                                        | W = Writable                                                                                                               | bit              | U = Unimplem                       | nented bit, read | d as '0'        |           |  |  |  |  |

| -n = Value at F   | POR                                                        | '1' = Bit is set                                                                                                           |                  | '0' = Bit is clea                  | ared             | x = Bit is unkn | own       |  |  |  |  |

| bit 15            | NSTDIS: Inte                                               | rrupt Nesting E                                                                                                            | )isable bit      |                                    |                  |                 |           |  |  |  |  |

|                   |                                                            | nesting is disat                                                                                                           |                  |                                    |                  |                 |           |  |  |  |  |

|                   |                                                            | nesting is enab                                                                                                            |                  |                                    |                  |                 |           |  |  |  |  |

| bit 14            | OVAERR: Ac                                                 | cumulator A O                                                                                                              | verflow Trap F   | lag bit                            |                  |                 |           |  |  |  |  |

|                   |                                                            | caused by ove                                                                                                              |                  |                                    |                  |                 |           |  |  |  |  |

|                   | -                                                          | 0 = Trap was not caused by overflow of Accumulator A                                                                       |                  |                                    |                  |                 |           |  |  |  |  |

| bit 13            | OVBERR: Accumulator B Overflow Trap Flag bit               |                                                                                                                            |                  |                                    |                  |                 |           |  |  |  |  |

|                   |                                                            | <ul> <li>Trap was caused by overflow of Accumulator B</li> <li>Trap was not caused by overflow of Accumulator B</li> </ul> |                  |                                    |                  |                 |           |  |  |  |  |

| bit 12            | COVAERR: Accumulator A Catastrophic Overflow Trap Flag bit |                                                                                                                            |                  |                                    |                  |                 |           |  |  |  |  |

|                   |                                                            | p was caused by catastrophic overflow of Accumulator A                                                                     |                  |                                    |                  |                 |           |  |  |  |  |

| bit 11            | COVBERR: Accumulator B Catastrophic Overflow Trap Flag bit |                                                                                                                            |                  |                                    |                  |                 |           |  |  |  |  |

|                   |                                                            |                                                                                                                            |                  | flow of Accumu                     |                  |                 |           |  |  |  |  |

| bit 10            | OVATE: Accu                                                | <b>OVATE:</b> Accumulator A Overflow Trap Enable bit                                                                       |                  |                                    |                  |                 |           |  |  |  |  |

|                   | 1 = Trap over<br>0 = Trap disa                             | flow of Accum<br>bled                                                                                                      | ulator A         |                                    |                  |                 |           |  |  |  |  |

| bit 9             | OVBTE: Accumulator B Overflow Trap Enable bit              |                                                                                                                            |                  |                                    |                  |                 |           |  |  |  |  |

|                   | 1 = Trap over<br>0 = Trap disa                             | flow of Accum<br>bled                                                                                                      | ulator B         |                                    |                  |                 |           |  |  |  |  |

| bit 8             | COVTE: Cata                                                | astrophic Overf                                                                                                            | low Trap Enat    | ole bit                            |                  |                 |           |  |  |  |  |

|                   | 1 = Trap on c<br>0 = Trap disa                             | -                                                                                                                          | erflow of Accur  | mulator A or B e                   | enabled          |                 |           |  |  |  |  |

| bit 7             | SFTACERR:                                                  | Shift Accumula                                                                                                             | ator Error Statu | us bit                             |                  |                 |           |  |  |  |  |

|                   |                                                            |                                                                                                                            |                  | ilid accumulator<br>invalid accumu |                  |                 |           |  |  |  |  |

| bit 6             | DIV0ERR: Ar                                                | ithmetic Error \$                                                                                                          | Status bit       |                                    |                  |                 |           |  |  |  |  |

|                   |                                                            | r trap was cau<br>r trap was not                                                                                           |                  |                                    |                  |                 |           |  |  |  |  |

| bit 5             |                                                            | DMA Controlle                                                                                                              | -                | -                                  |                  |                 |           |  |  |  |  |

|                   |                                                            | troller error trap<br>troller error trap                                                                                   |                  |                                    |                  |                 |           |  |  |  |  |

| bit 4             | MATHERR: A                                                 | Arithmetic Error                                                                                                           | Status bit       |                                    |                  |                 |           |  |  |  |  |

|                   |                                                            | r trap has occu                                                                                                            |                  |                                    |                  |                 |           |  |  |  |  |

| REGISTER 7-3: | INTCON1: | INTERRUPT | CONTROL | <b>REGISTER 1</b> |

|---------------|----------|-----------|---------|-------------------|

|               |          |           |         |                   |

0 = Math error trap has not occurred

| R/W-0                             | R/W-0                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0          | U-0              | R/W-0           | R/W-0            | U-0                                                                          |  |  |  |  |  |  |  |  |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|-----------------|------------------|------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| FLTA1IF                           | RTCIF                                                                                                       | DMA5IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | _                | QEI1IF          | PWM1IF           | _                                                                            |  |  |  |  |  |  |  |  |  |  |

| bit 15                            |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | ·                |                 |                  | bit 8                                                                        |  |  |  |  |  |  |  |  |  |  |

|                                   |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                  |                 |                  |                                                                              |  |  |  |  |  |  |  |  |  |  |

| U-0                               | U-0                                                                                                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U-0          | U-0              | U-0             | U-0              | U-0                                                                          |  |  |  |  |  |  |  |  |  |  |

|                                   | <u> </u>                                                                                                    | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _            |                  |                 | —                | _                                                                            |  |  |  |  |  |  |  |  |  |  |

| bit 7                             |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                  |                 |                  | bit (                                                                        |  |  |  |  |  |  |  |  |  |  |

|                                   |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                  |                 |                  |                                                                              |  |  |  |  |  |  |  |  |  |  |

| Legend:                           |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                  |                 |                  |                                                                              |  |  |  |  |  |  |  |  |  |  |

| R = Readable bit W = Writable bit |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | U = Unimple      | mented bit, rea | d as '0'         |                                                                              |  |  |  |  |  |  |  |  |  |  |

| -n = Value at                     | POR                                                                                                         | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              | '0' = Bit is cle | eared           | x = Bit is unkno | own                                                                          |  |  |  |  |  |  |  |  |  |  |

| bit 14<br>bit 13                  | 0 = Interrupt<br><b>RTCIF:</b> Real<br>1 = Interrupt<br>0 = Interrupt<br><b>DMA5IF:</b> DM<br>1 = Interrupt | <ul> <li>FLTA1IF: PWM1 Fault A Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>RTCIF: Real-Time Clock and Calendar Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>DMA5IF: DMA Channel 5 Data Transfer Complete Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>DMA5IF: DMA Channel 5 Data Transfer Complete Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>D = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |              |                  |                 |                  |                                                                              |  |  |  |  |  |  |  |  |  |  |

| bit 12-11                         | Unimpleme                                                                                                   | nted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ,            |                  |                 |                  |                                                                              |  |  |  |  |  |  |  |  |  |  |

| bit 10                            | 1 = Interrupt                                                                                               | 1 Event Interrupt<br>request has occ<br>request has not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | urred        | s bit            |                 |                  |                                                                              |  |  |  |  |  |  |  |  |  |  |

| bit 9                             | PWM1IF: PV                                                                                                  | VM1 Event Interr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | upt Flag Sta | atus bit         |                 |                  |                                                                              |  |  |  |  |  |  |  |  |  |  |

|                                   |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                  |                 |                  | 1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred |  |  |  |  |  |  |  |  |  |  |

## REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

Unimplemented: Read as '0'

bit 8-0

| U-0           | R/W-1                                                                        | R/W-0                    | R/W-0 | U-0          | R/W-1           | R/W-0                 | R/W-0 |  |  |  |  |

|---------------|------------------------------------------------------------------------------|--------------------------|-------|--------------|-----------------|-----------------------|-------|--|--|--|--|

| _             |                                                                              | C1IP<2:0> <sup>(1)</sup> |       |              |                 | C1RXIP<2:0>(1)        |       |  |  |  |  |

| bit 15        |                                                                              |                          |       |              |                 |                       | bit   |  |  |  |  |

|               |                                                                              | D444 0                   | DANO  |              |                 |                       |       |  |  |  |  |

| U-0           | R/W-1                                                                        | R/W-0<br>SPI2IP<2:0>     | R/W-0 | U-0          | R/W-1           | R/W-0<br>SPI2EIP<2:0> | R/W-0 |  |  |  |  |

| bit 7         |                                                                              | 011211 32.07             |       |              |                 | 0112211 42.05         | bit   |  |  |  |  |

|               |                                                                              |                          |       |              |                 |                       |       |  |  |  |  |

| Legend:       | a hit                                                                        |                          | :4    |              | nonted bit no   |                       |       |  |  |  |  |

| R = Readabl   |                                                                              | W = Writable b           | ut.   | 0 = Onimpler | mented bit, rea |                       |       |  |  |  |  |

| -n = Value at | PUR                                                                          | '1' = Bit is set         |       |              | areu            | x = Bit is unkno      | own   |  |  |  |  |

| bit 15        | Unimpleme                                                                    | ented: Read as '0        | ,     |              |                 |                       |       |  |  |  |  |

| bit 14-12     | C1IP<2:0>: ECAN1 Event Interrupt Priority bits <sup>(1)</sup>                |                          |       |              |                 |                       |       |  |  |  |  |

|               | 111 = Interrupt is priority 7 (highest priority interrupt)                   |                          |       |              |                 |                       |       |  |  |  |  |

|               | •                                                                            |                          | 0     | <b>,</b>     |                 |                       |       |  |  |  |  |

|               | •                                                                            |                          |       |              |                 |                       |       |  |  |  |  |

|               | •<br>001 - Intor                                                             | rupt is priority 1       |       |              |                 |                       |       |  |  |  |  |

|               |                                                                              | rupt source is disa      | bled  |              |                 |                       |       |  |  |  |  |

| bit 11        |                                                                              | ented: Read as '0        |       |              |                 |                       |       |  |  |  |  |

| bit 10-8      | C1RXIP<2:0>: ECAN1 Receive Data Ready Interrupt Priority bits <sup>(1)</sup> |                          |       |              |                 |                       |       |  |  |  |  |

|               | 111 = Interrupt is priority 7 (highest priority interrupt)                   |                          |       |              |                 |                       |       |  |  |  |  |

|               | •                                                                            |                          | •     | /            |                 |                       |       |  |  |  |  |

|               | •                                                                            |                          |       |              |                 |                       |       |  |  |  |  |

|               | •<br>001 - Inter                                                             | rupt is priority 1       |       |              |                 |                       |       |  |  |  |  |

|               |                                                                              | rupt source is disa      | bled  |              |                 |                       |       |  |  |  |  |

| bit 7         |                                                                              | ented: Read as '0        |       |              |                 |                       |       |  |  |  |  |

| bit 6-4       | SPI2IP<2:0>: SPI2 Event Interrupt Priority bits                              |                          |       |              |                 |                       |       |  |  |  |  |

|               | 111 = Interrupt is priority 7 (highest priority interrupt)                   |                          |       |              |                 |                       |       |  |  |  |  |

|               | •                                                                            |                          | 0     | <b>,</b>     |                 |                       |       |  |  |  |  |

|               | •                                                                            |                          |       |              |                 |                       |       |  |  |  |  |

|               | •<br>001 = Inter                                                             | rupt is priority 1       |       |              |                 |                       |       |  |  |  |  |

|               |                                                                              | rupt source is disa      | bled  |              |                 |                       |       |  |  |  |  |

| bit 3         |                                                                              | ented: Read as '0        |       |              |                 |                       |       |  |  |  |  |

| bit 2-0       | -                                                                            | :0>: SPI2 Error Int      |       | itv bits     |                 |                       |       |  |  |  |  |

|               |                                                                              | rupt is priority 7 (h    | -     | -            |                 |                       |       |  |  |  |  |

|               | •                                                                            |                          | - ' ' |              |                 |                       |       |  |  |  |  |

|               | •                                                                            |                          |       |              |                 |                       |       |  |  |  |  |

|               | •                                                                            |                          |       |              |                 |                       |       |  |  |  |  |

|               | 001 - Intor                                                                  | rupt is priority 1       |       |              |                 |                       |       |  |  |  |  |

#### DECISTED 7 22

| —                               |                                                                                                        | R/W-0                                                                                                                                                                           | R/W-0                   | U-0              | R/W-1           | R/W-0           | R/W-0 |

|---------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------|-----------------|-----------------|-------|

|                                 |                                                                                                        | FLTA1IP<2:0>                                                                                                                                                                    |                         |                  |                 | RTCIP<2:0>      |       |

| bit 15                          |                                                                                                        |                                                                                                                                                                                 |                         |                  |                 |                 | bit   |

|                                 |                                                                                                        |                                                                                                                                                                                 |                         |                  |                 |                 |       |

| U-0                             | R/W-1                                                                                                  |                                                                                                                                                                                 |                         |                  |                 |                 |       |

| —                               |                                                                                                        | DMA5IP<2:0>                                                                                                                                                                     |                         | —                | —               | —               | —     |

| bit 7                           |                                                                                                        |                                                                                                                                                                                 |                         |                  |                 |                 | bit   |

| Legend:                         |                                                                                                        |                                                                                                                                                                                 |                         |                  |                 |                 |       |

| R = Readable                    | bit                                                                                                    | W = Writable I                                                                                                                                                                  | oit                     | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at I                 | POR                                                                                                    | '1' = Bit is set                                                                                                                                                                |                         | '0' = Bit is cle | ared            | x = Bit is unkn | lown  |

| bit 14-12<br>bit 11<br>bit 10-8 | 111 = Interr<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | <ul> <li>10&gt;: PWM Fault A</li> <li>upt is priority 7 (h</li> <li>upt is priority 1</li> <li>upt source is disa</li> <li>ented: Read as '0</li> <li>Real-Time Cloo</li> </ul> | nighest priori<br>abled | ty interrupt)    | lag Status bits |                 |       |

|                                 | 111 = Interr<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | upt is priority 7 (f<br>upt is priority 1<br>upt source is disa                                                                                                                 | nighest priori<br>abled | -                |                 |                 |       |

| bit 7                           | Unimpleme                                                                                              | ented: Read as '0                                                                                                                                                               | )'                      |                  |                 |                 |       |

| bit 6-4                         | 111 = Interr<br>•<br>•                                                                                 | 0>: DMA Channe<br>upt is priority 7 (h<br>upt is priority 1                                                                                                                     |                         | •                | Interrupt Prior | ity bits        |       |

|                                 | 000 = Interr                                                                                           | upt source is disa                                                                                                                                                              |                         |                  |                 |                 |       |

##

bit 3-0 Unimplemented: Read as '0'

| R/W-0                | U-0         | U-0              | U-0                   | U-0              | U-0              | U-0             | U-0   |

|----------------------|-------------|------------------|-----------------------|------------------|------------------|-----------------|-------|

| FORCE <sup>(1)</sup> | _           | —                | _                     |                  | —                |                 | —     |

| bit 15               |             |                  |                       |                  | •                |                 | bit 8 |

|                      |             |                  |                       |                  |                  |                 |       |

| U-0                  | R/W-0       | R/W-0            | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| _                    |             |                  |                       | IRQSEL<6:0>      | (2)              |                 |       |

| bit 7                |             |                  |                       |                  |                  |                 | bit 0 |

|                      |             |                  |                       |                  |                  |                 |       |

| Legend:              |             |                  |                       |                  |                  |                 |       |

| R = Readable         | e bit       | W = Writable b   | oit                   | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value at        | POR         | '1' = Bit is set |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                      |             |                  |                       |                  |                  |                 |       |

| bit 15               | FORCE: For  | rce DMA Transfe  | er bit <sup>(1)</sup> |                  |                  |                 |       |

|                      |             | single DMA trans | •                     | ,                |                  |                 |       |

|                      | 0 = Automat | ic DMA transfer  | initiation by D       | MA request       |                  |                 |       |

| bit 14-7             | Unimpleme   | nted: Read as '0 | )'                    |                  |                  |                 |       |

**Note 1:** This bit cannot be cleared by the user. It is cleared by hardware when the forced DMA transfer is complete.

000000-1111111 = DMAIRQ0-DMAIRQ127 selected to be Channel DMAREQ

2: Refer to Table 7-1 for a complete listing of IRQ numbers for all interrupt sources.

IRQSEL<6:0>: DMA Peripheral IRQ Number Select bits<sup>(2)</sup>

bit 6-0

## REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0                               | U-0 | U-0              | U-0                                    | U-0                                | U-0   | U-0             | U-0   |

|-----------------------------------|-----|------------------|----------------------------------------|------------------------------------|-------|-----------------|-------|

|                                   | _   | —                | _                                      | —                                  | —     | _               | _     |

| bit 15                            |     |                  |                                        |                                    |       |                 | bit 8 |

|                                   |     |                  |                                        |                                    |       |                 |       |

| U-0                               | U-0 | U-0              | R/W-1                                  | R/W-1                              | R/W-1 | R/W-1           | R/W-1 |

| —                                 | _   | —                | INTR2R<4:0>                            |                                    |       |                 |       |

| bit 7                             |     |                  |                                        |                                    |       |                 | bit 0 |

|                                   |     |                  |                                        |                                    |       |                 |       |

| Legend:                           |     |                  |                                        |                                    |       |                 |       |

| R = Readable bit W = Writable bit |     |                  | bit                                    | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at Po                  | OR  | '1' = Bit is set | set '0' = Bit is cleared x = Bit is ur |                                    |       | x = Bit is unkı | nown  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 INTR2R<4:0>: Assign External Interrupt 2 (INTR2) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25 •

00001 = Input tied to RP1 00000 = Input tied to RP0