Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Active                                                                           |

| Core Processor            | dsPIC                                                                            |

| Core Size                 | 16-Bit                                                                           |

| Speed                     | 40 MIPs                                                                          |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals               | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| lumber of I/O             | 21                                                                               |

| Program Memory Size       | 128KB (128K x 8)                                                                 |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AM Size                   | 8K x 8                                                                           |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| ata Converters            | A/D 6x10b/12b                                                                    |

| Scillator Type            | Internal                                                                         |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Nounting Type             | Surface Mount                                                                    |

| ackage / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package   | 28-SOIC                                                                          |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc202-i-so |

#### 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device specific information for the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 Digital Signal Controller (DSC) devices. The dsPIC33F devices contain extensive Digital Signal Processor (DSP) functionality with a high performance 16-bit Microcontroller (MCU) architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules in the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 families of devices. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

| dsPIC33FJ3 | 32MC302/304 | , dsPIC33FJ6 | 4MCX02/X0 | 4 AND dsPIC | 33FJ128MC | X02/X04 |

|------------|-------------|--------------|-----------|-------------|-----------|---------|

| NOTES:     |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

TABLE 2-2: RESONATOR RECOMMENDATIONS

| Part<br>Number | Vendor    | Freq.  | Load<br>Cap. | Package<br>Case | Frequency<br>Tolerance | Mounting<br>Type | Operating<br>Temperature |

|----------------|-----------|--------|--------------|-----------------|------------------------|------------------|--------------------------|

| FCR4.0M5T      | TDK Corp. | 4 MHz  | N/A          | Radial          | ±0.5%                  | TH               | -40°C to +85°C           |

| FCR8.0M5       | TDK Corp. | 8 MHz  | N/A          | Radial          | ±0.5%                  | TH               | -40°C to +85°C           |

| HWZT-10.00MD   | TDK Corp. | 10 MHz | N/A          | Radial          | ±0.5%                  | TH               | -40°C to +85°C           |

| HWZT-20.00MD   | TDK Corp. | 20 MHz | N/A          | Radial          | ±0.5%                  | TH               | -40°C to +85°C           |

Legend: TH = Through Hole

# 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to less than or equal to 8 MHz for start-up with PLL enabled to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

# 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the analog-to-digital input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in this register that correspond to the analog-to-digital pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain analog-to-digital pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all analog-to-digital pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

#### 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor between Vss and the unused pin.

#### **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup> 111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8) bit 4

RA: REPEAT Loop Active bit

1 = REPEAT loop in progress 0 = REPEAT loop not in progress

bit 3 N: MCU ALU Negative bit

1 = Result was negative

0 = Result was non-negative (zero or positive)

bit 2 OV: MCU ALU Overflow bit

> This bit is used for signed arithmetic (two's complement). It indicates an overflow of a magnitude that causes the sign bit to change state.

1 = Overflow occurred for signed arithmetic (in this arithmetic operation)

0 = No overflow occurred

Z: MCU ALU Zero bit bit 1

1 = An operation that affects the Z bit has set it at some time in the past

0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)

C: MCU ALU Carry/Borrow bit bit 0

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

Note 1: This bit can be read or cleared (not set).

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: This bit can be read or cleared (not set). Clearing this bit clears SA and SB.

TABLE 4-23: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1 (FOR dsPIC33FJ128MC802/804 AND dsPIC33FJ64MC802/804) (CONTINUED)

| File Name  | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                         | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------------------------------|----------|-------|-------|-------|-------|-------|-------|---------------|

| C1RXF11EID | 046E |        |        |        | EID<   | 15:8>  |        |       |       | EID<7:0>                      |          |       |       |       |       |       | xxxx  |               |

| C1RXF12SID | 0470 |        |        |        | SID<   | 10:3>  |        |       |       |                               | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C1RXF12EID | 0472 |        |        |        | EID<   | 15:8>  |        |       |       |                               |          |       | EID<  | 7:0>  |       |       |       | xxxx          |

| C1RXF13SID | 0474 |        |        |        | SID<   | 10:3>  |        |       |       |                               | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C1RXF13EID | 0476 |        |        |        | EID<   | 15:8>  |        |       |       |                               |          |       | EID<  | 7:0>  |       |       |       | xxxx          |

| C1RXF14SID | 0478 |        |        |        | SID<   | 10:3>  |        |       |       |                               | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A |        |        |        | EID<   | 15:8>  |        |       |       | EID<7:0>                      |          |       |       |       | xxxx  |       |       |               |

| C1RXF15SID | 047C |        |        |        | SID<   | 10:3>  |        |       |       | SID<2:0> — EXIDE — EID<17:16> |          |       |       | 7:16> | xxxx  |       |       |               |

| C1RXF15EID | 047E |        |        |        | EID<   | 15:8>  |        |       |       | EID<7:0>                      |          |       |       |       | xxxx  |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 6.0 RESETS

Note 1: This data sheet summarizes the features of the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

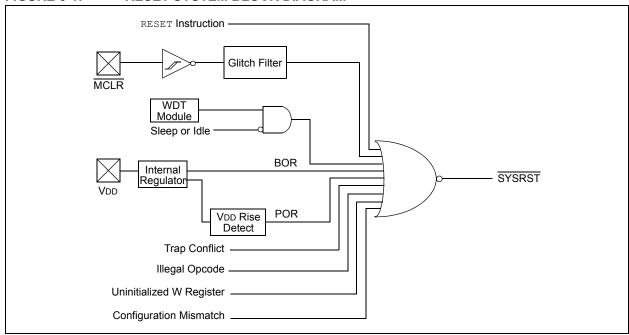

The Reset module combines all reset <u>sources</u> and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

POR: Power-on Reset

· BOR: Brown-out Reset

MCLR: Master Clear Pin Reset

• SWR: RESET Instruction

· WDTO: Watchdog Timer Reset

· CM: Configuration Mismatch Reset

· TRAPR: Trap Conflict Reset

· IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

**Note:** Refer to the specific peripheral section or Section 3.0 "CPU" in this data sheet for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR bit (RCON<0>), that are set. The user application can set or clear any bit at any time during the code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

#### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

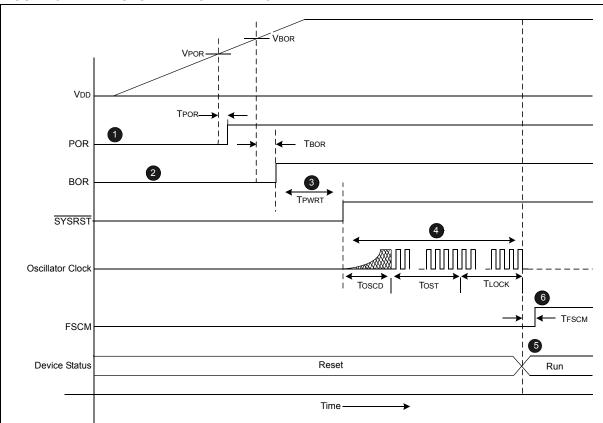

FIGURE 6-2: SYSTEM RESET TIMING

- **Note 1: POR:** A POR circuit holds the device in Reset when the power supply is turned on. The POR circuit is active until VDD crosses the VPOR threshold and the delay TPOR has elapsed.

- 2: BOR: The on-chip voltage regulator has a BOR circuit that keeps the device in Reset until VDD crosses the VBOR threshold and the delay TBOR has elapsed. The delay TBOR ensures the voltage regulator output becomes stable.

- 3: **PWRT Timer:** The programmable power-up timer continues to hold the processor in Reset for a specific period of time (TPWRT) after a BOR. The delay TPWRT ensures that the system power supplies have stabilized at the appropriate level for full-speed operation. After the delay TPWRT has elapsed, the SYSRST becomes inactive, which in turn enables the selected oscillator to start generating clock cycles.

- **4: Oscillator Delay:** The total delay for the clock to be ready for various clock source selections are given in Table 6-1. Refer to **Section 9.0 "Oscillator Configuration"** for more information.

- **5:** When the oscillator clock is ready, the processor begins execution from location 0x000000. The user application programs a GOTO instruction at the reset address, which redirects program execution to the appropriate start-up routine.

- **6:** The Fail-Safe Clock Monitor (FSCM), if enabled, begins to monitor the system clock when the system clock is ready and the delay TFSCM has elapsed.

#### 7.0 INTERRUPT CONTROLLER

Note 1: This data sheet summarizes the features of the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 32. "Interrupts (Part III)" (DS70214) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- · Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- · Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- · Fixed interrupt entry and return latencies

#### 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) shown in Figure 7-1, resides in program memory, starting at location 000004h. The IVT contains 126 vectors consisting of eight nonmaskable trap vectors plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with vector 0 takes priority over interrupts at any other vector address.

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 devices implement up to 53 unique interrupts and five nonmaskable traps. These are summarized in Table 7-1.

# 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

#### 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 device clears its registers in response to a Reset, which forces the PC to zero. The digital signal controller then begins program execution at location 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

bit 2 CMIE: Comparator Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 1 MI2C1IE: I2C1 Master Events Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 0 SI2C1IE: I2C1 Slave Events Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

#### REGISTER 7-22: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

| U-0    | R/W-1 | R/W-0       | R/W-0 | U-0 | R/W-1 | R/W-0       | R/W-0 |

|--------|-------|-------------|-------|-----|-------|-------------|-------|

| _      |       | U2TXIP<2:0> |       | _   |       | U2RXIP<2:0> |       |

| bit 15 |       |             |       |     |       |             | bit 8 |

| U-0   | R/W-1 | R/W-0       | R/W-0 | U-0 | R/W-1 | R/W-0     | R/W-0 |

|-------|-------|-------------|-------|-----|-------|-----------|-------|

| _     |       | INT2IP<2:0> |       | _   |       | T5IP<2:0> |       |

| bit 7 |       |             |       |     |       |           | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 U2TXIP<2:0>: UART2 Transmitter Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 **U2RXIP<2:0>:** UART2 Receiver Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 7 **Unimplemented:** Read as '0'

bit 6-4 INT2IP<2:0>: External Interrupt 2 Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

\_

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3 Unimplemented: Read as '0'

bit 2-0 T5IP<2:0>: Timer5 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

| dsPIC33FJ3 | 32MC302/304 | , dsPIC33FJ6 | 4MCX02/X0 | 4 AND dsPIC | 33FJ128MC | X02/X04 |

|------------|-------------|--------------|-----------|-------------|-----------|---------|

| NOTES:     |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

|            |             |              |           |             |           |         |

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

bit 3 **CF:** Clock Fail Detect bit (read/clear by application)

1 = FSCM has detected clock failure0 = FSCM has not detected clock failure

bit 2 Unimplemented: Read as '0'

bit 0

bit 1 LPOSCEN: Secondary (LP) Oscillator Enable bit

1 = Enable secondary oscillator0 = Disable secondary oscillator

**OSWEN:** Oscillator Switch Enable bit

1 = Request oscillator switch to selection specified by NOSC<2:0> bits

0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to **Section 39. "Oscillator (Part III)"** (DS70216) in the "dsPIC33F/PIC24H Family Reference Manual" (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: This register is reset only on a Power-on Reset (POR).

#### REGISTER 21-8: CIEC: ECAN™ TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0    | R-0 | R-0 | R-0   | R-0     | R-0 | R-0 | R-0   |

|--------|-----|-----|-------|---------|-----|-----|-------|

|        |     |     | TERRC | NT<7:0> |     |     |       |

| bit 15 |     |     |       |         |     |     | bit 8 |

| R-0   | R-0 | R-0 | R-0   | R-0     | R-0 | R-0 | R-0   |

|-------|-----|-----|-------|---------|-----|-----|-------|

|       |     |     | RERRC | NT<7:0> |     |     |       |

| bit 7 |     |     |       |         |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **TERRCNT<7:0>:** Transmit Error Count bits bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

#### REGISTER 21-9: CICFG1: ECAN™ BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-------|--------|-------|-------|

| SJW   | <1:0> |       |       | BRP   | °<5:0> |       |       |

| bit 7 |       |       |       |       |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-6 SJW<1:0>: Synchronization Jump Width bits

11 = Length is 4 x TQ

10 = Length is 3 x TQ

01 = Length is 2 x TQ

00 = Length is 1 x TQ

bit 5-0 **BRP<5:0>:** Baud Rate Prescaler bits

11 1111 = TQ = 2 x 64 x 1/FCAN

•

•

00 0010 =  $TQ = 2 \times 3 \times 1/FCAN$

00 0001 = TQ = 2 x 2 x 1/FCAN

00 0000 = TQ = 2 x 1 x 1/FCAN

#### 21.6 ECAN Message Buffers

ECAN Message Buffers are part of DMA RAM memory. They are not ECAN special function registers. The user application must directly write into the DMA RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0    | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-------|-------|-------|-------|-------|

| _      | _   | _   | SID10 | SID9  | SID8  | SID7  | SID6  |

| bit 15 |     |     |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID5  | SID4  | SID3  | SID2  | SID1  | SID0  | SRR   | IDE   |

| bit 7 |       |       |       |       | _     | _     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12-2 SID<10:0>: Standard Identifier bits

bit 1 SRR: Substitute Remote Request bit

1 = Message will request remote transmission

0 = Normal message

bit 0 **IDE:** Extended Identifier bit

1 = Message will transmit extended identifier0 = Message will transmit standard identifier

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0    | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      | _   | _   | _   | EID17 | EID16 | EID15 | EID14 |

| bit 15 |     |     |     |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID13 | EID12 | EID11 | EID10 | EID9  | EID8  | EID7  | EID6  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 **Unimplemented:** Read as '0' bit 11-0 **EID<17:6>:** Extended Identifier bits

#### 22.6 ADC Control Registers

#### REGISTER 22-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0  | R/W-0   | U-0 | R/W-0 | R/W-0     | R/W-0 |

|--------|-----|--------|---------|-----|-------|-----------|-------|

| ADON   | _   | ADSIDL | ADDMABM | -   | AD12B | FORM<1:0> |       |

| bit 15 |     |        |         |     |       |           | bit 8 |

| R/W-0 | R/W-0     | R/W-0 | U-0 | R/W-0  | R/W-0 | R/W-0<br>HC, HS | R/C-0<br>HC, HS |

|-------|-----------|-------|-----|--------|-------|-----------------|-----------------|

|       | SSRC<2:0> |       | _   | SIMSAM | ASAM  | SAMP            | DONE            |

| bit 7 |           |       |     |        |       |                 | bit 0           |

| Legend:           | HC = Cleared by hardware | HS = Set by hardware               |                    |

|-------------------|--------------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared               | x = Bit is unknown |

bit 15 ADON: ADC Operating Mode bit

1 = ADC module is operating

0 = ADC is off

bit 14 **Unimplemented:** Read as '0'

bit 13 ADSIDL: Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12 ADDMABM: DMA Buffer Build Mode bit

1 = DMA buffers are written in the order of conversion. The module provides an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer

0 = DMA buffers are written in Scatter/Gather mode. The module provides a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer

bit 11 **Unimplemented:** Read as '0'

bit 10 AD12B: 10-bit or 12-bit Operation Mode bit

1 = 12-bit, 1-channel ADC operation

0 = 10-bit, 4-channel ADC operation

bit 9-8 **FORM<1:0>:** Data Output Format bits

For 10-bit operation:

11 = Signed fractional (Dout = sddd dddd dd00 0000, where s =.NOT.d<9>)

10 = Fractional (Dout = dddd dddd dd00 0000)

01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NOT.d<9>)

00 = Integer (Dout = 0000 00dd dddd dddd)

For 12-bit operation:

11 = Signed fractional (Dout = sddd dddd dddd 0000, where s = .NOT.d<11>)

10 = Fractional (Dout = dddd dddd dddd 0000)

01 = Signed Integer (Dout = ssss sddd dddd dddd, where s = .NOT.d<11>)

00 = Integer (Dout = 0000 dddd dddd dddd)

bit 7-5 SSRC<2:0>: Sample Clock Source Select bits

111 = Internal counter ends sampling and starts conversion (auto-convert)

110 = Reserved

101 = Motor Control PWM2 interval ends sampling and starts conversion

100 = GP timer (Timer5 for ADC1) compare ends sampling and starts conversion

011 = Motor Control PWM1 interval ends sampling and starts conversion

010 = GP timer (Timer3 for ADC1) compare ends sampling and starts conversion

001 = Active transition on INTO pin ends sampling and starts conversion

000 = Clearing sample bit ends sampling and starts conversion

bit 4 Unimplemented: Read as '0'

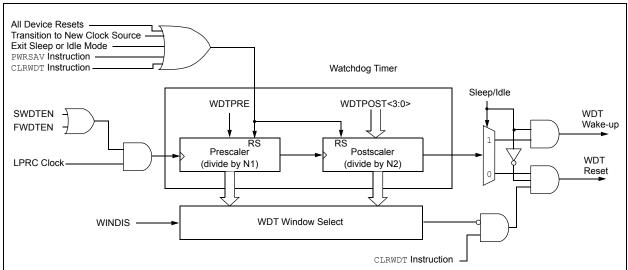

#### 28.4 Watchdog Timer (WDT)

For dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 28.4.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler than can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

**Note:** The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### 28.4.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3,2>) needs to be cleared in software after the device wakes up.

#### 28.4.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

Note: If the WINDIS bit (FWDT<6>) is cleared, the CLRWDT instruction should be executed by the application software only during the last 1/4 of the WDT period. This CLRWDT window can be determined by using a timer. If a CLRWDT instruction is executed before

this window, a WDT Reset occurs.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

#### FIGURE 28-2: WDT BLOCK DIAGRAM

#### 31.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(4)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD ≥ 3.0V <sup>(4)</sup> | 0.3V to +5.6V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(4)</sup> | 0.3V to 3.6V         |

| Maximum current out of Vss pin                                                    | 300 mA               |

| Maximum current into VDD pin <sup>(2)</sup>                                       | 250 mA               |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                     | 8 mA                 |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                     | 15 mA                |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                     | 25 mA                |

| Maximum current sunk by all ports                                                 | 200 mA               |

| Maximum current sourced by all ports <sup>(2)</sup>                               | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

- **3:** Exceptions are CLKOUT, which is able to sink/source 25 mA, and the VREF+, VREF-, SCLx, SDAx, PGECx and PGEDx pins, which are able to sink/source 12 mA.

- 4: See the "Pin Diagrams" section for 5V tolerant pins.

TABLE 31-37: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                       | Standard Op<br>(unless othe<br>Operating ter | rwise st           | <b>ated)</b><br>e -40° | C ≤Ta ≤+ | V to 3.6V<br>85°C for Industrial<br>125°C for Extended |

|--------------------|-----------------------|-------------------------------------------------------|----------------------------------------------|--------------------|------------------------|----------|--------------------------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                         | Min                                          | Typ <sup>(2)</sup> | Max                    | Units    | Conditions                                             |

| SP70               | TscP                  | Maximum SCK Input Frequency                           | _                                            | _                  | 11                     | MHz      | See Note 3                                             |

| SP72               | TscF                  | SCKx Input Fall Time                                  | _                                            | 1                  | 1                      | ns       | See parameter DO32 and Note 4                          |

| SP73               | TscR                  | SCKx Input Rise Time                                  |                                              |                    | ı                      | ns       | See parameter DO31 and Note 4                          |

| SP30               | TdoF                  | SDOx Data Output Fall Time                            | _                                            | l                  |                        | ns       | See parameter DO32 and Note 4                          |

| SP31               | TdoR                  | SDOx Data Output Rise Time                            | _                                            |                    | 1                      | ns       | See parameter DO31 and Note 4                          |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge                |                                              | 6                  | 20                     | ns       | _                                                      |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to First SCKx Edge             | 30                                           | _                  | _                      | ns       | _                                                      |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge            | 30                                           |                    | 1                      | ns       | _                                                      |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge             | 30                                           | I                  | I                      | ns       | _                                                      |

| SP50               | TssL2scH,<br>TssL2scL | SSx ↓to SCKx ↑ or SCKx Input                          | 120                                          | _                  | _                      | ns       | _                                                      |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup> | 10                                           |                    | 50                     | ns       | _                                                      |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                   | 1.5 Tcy + 40                                 | _                  | _                      | ns       | See Note 4                                             |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge              | _                                            |                    | 50                     | ns       | _                                                      |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

<sup>2:</sup> Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**<sup>3:</sup>** The minimum clock period for SCKx is 91 ns. Therefore, the SCK clock generated by the Master must not violate this specification.

<sup>4:</sup> Assumes 50 pF load on all SPIx pins.

#### 32.0 HIGH TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between -40°C to +150°C are identical to those shown in **Section 31.0 "Electrical Characteristics"** for operation between -40°C to +125°C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, parameter DC10 in **Section 31.0** "Electrical Characteristics" is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 high temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(4)</sup>                                     | 40°C to +150°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(5)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(5)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD ≥ 3.0V <sup>(5)</sup> | 0.3V to 5.6V         |

| Maximum current out of Vss pin                                                    | 60 mA                |

| Maximum current into VDD pin <sup>(2)</sup>                                       | 60 mA                |

| Maximum junction temperature                                                      | +155°C               |

| Maximum current sourced/sunk by any 2x I/O pin(3)                                 |                      |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                     | 4 mA                 |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                     | 8 mA                 |

| Maximum current sunk by all ports combined                                        | 70 mA                |

| Maximum current sourced by all ports combined <sup>(2)</sup>                      | 70 mA                |

|                                                                                   |                      |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 32-2).

- **3:** Unlike devices at 125°C and below, the specifications in this section also apply to the CLKOUT, VREF+, VREF-, SCLx, SDAx, PGCx and PGDx pins.

- **4:** AEC-Q100 reliability testing for devices intended to operate at 150°C is 1,000 hours. Any design in which the total operating time from 125°C to 150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 5: Refer to the "Pin Diagrams" section for 5V tolerant pins.

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

#### TABLE 32-7: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHARACTERISTICS |        |                               | (unless | otherwi           | ise stated | d)    | 3.0V to 3.6V<br>ΓA ≤+150°C for High Temperature                  |

|--------------------|--------|-------------------------------|---------|-------------------|------------|-------|------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min     | Min Typ Max Units |            | Units | Conditions                                                       |

|                    |        | Program Flash Memory          |         |                   |            |       |                                                                  |

| HD130              | EP     | Cell Endurance                | 10,000  | _                 | _          | E/W   | -40° C to +150° C <sup>(2)</sup>                                 |

| HD134              | TRETD  | Characteristic Retention      | 20      | _                 | _          | Year  | 1000 E/W cycles or less and no other specifications are violated |

Note 1: These parameters are assured by design, but are not characterized or tested in manufacturing.

<sup>2:</sup> Programming of the Flash memory is allowed up to 150°C.