Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

|                            |                                                                                   |

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                    |

| Supplier Device Package    | 28-SOIC                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc202t-i-so |

## **Table of Contents**

| dsPl  | C33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 Product Families |     |

|-------|-----------------------------------------------------------------------------------|-----|

| 1.0   | Device Overview                                                                   |     |

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers             |     |

| 3.0   | Memory Organization                                                               |     |

| 4.0   | Flash Program Memory                                                              |     |

| 5.0   | · · · · · · · · · · · · · · · · · · ·                                             |     |

| 6.0   | Resets                                                                            |     |

| 7.0   | Interrupt Controller                                                              |     |

| 0.8   | Direct Memory Access (DMA)                                                        |     |

| 9.0   | Oscillator Configuration                                                          |     |

|       | Power-Saving Features                                                             |     |

|       | I/O Ports                                                                         |     |

|       | Timer1                                                                            |     |

|       | Timer2/3 And Timer4/5                                                             |     |

|       | Input Capture                                                                     |     |

|       | Output Compare                                                                    |     |

|       | Motor Control PWM Module                                                          |     |

|       | Quadrature Encoder Interface (QEI) Module                                         |     |

|       | Serial Peripheral Interface (SPI)                                                 |     |

|       | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                     |     |

|       | Universal Asynchronous Receiver Transmitter (UART)                                |     |

|       | Enhanced CAN (ECAN™) Module                                                       |     |

|       | 10-bit/12-bit Analog-to-Digital Converter (ADC1)                                  |     |

|       | Audio Digital-to-Analog Converter (DAC)                                           |     |

|       | Comparator Module                                                                 |     |

|       | Real-Time Clock and Calendar (RTCC)                                               |     |

|       | Programmable Cyclic Redundancy Check (CRC) Generator                              |     |

|       | Parallel Master Port (PMP)                                                        |     |

|       | Special Features                                                                  |     |

|       | Instruction Set Summary                                                           |     |

|       | Development Support                                                               |     |

|       | Electrical Characteristics                                                        |     |

|       | High Temperature Electrical Characteristics                                       |     |

|       | DC and AC Device Characteristics Graphs                                           |     |

|       | Packaging Information                                                             |     |

| Appe  | endix A: Revision History                                                         | 439 |

| Index | x                                                                                 | 449 |

| The I | Microchip Web Site                                                                | 455 |

| Cust  | omer Change Notification Service                                                  | 455 |

| Cust  | omer Support                                                                      | 455 |

| Read  | der Response                                                                      | 456 |

| Prod  | uct Identification System                                                         | 457 |

#### 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device specific information for the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 Digital Signal Controller (DSC) devices. The dsPIC33F devices contain extensive Digital Signal Processor (DSP) functionality with a high performance 16-bit Microcontroller (MCU) architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules in the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 families of devices. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

TABLE 1-1: PINOUT I/O DESCRIPTIONS

| Pin Name      | Pin<br>Type | Buffer<br>Type | PPS        | Description                                                                                                                                                                                                                                                |

|---------------|-------------|----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN8       | I           | Analog         | No         | Analog input channels.                                                                                                                                                                                                                                     |

| CLKO          | 0           | ST/CMOS        | No<br>No   | External clock source input. Always associated with OSC1 pin function. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally, functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

|               | -           | ST/CMOS        |            | ·                                                                                                                                                                                                                                                          |

| OSC1          | '           | ST/CIVIOS      | No         | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                                                                            |

| OSC2          | I/O         | _              | No         | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                                   |

| SOSCI         | I           | ST/CMOS        | No         | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                                                                             |

| SOSCO         | 0           | _              | No         | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                                                                            |

| CN0-CN30      | I           | ST             | No         | Change notification inputs. Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                           |

| IC1-IC2       | I           | ST             | Yes        | Capture inputs 1/2.                                                                                                                                                                                                                                        |

| IC7-IC8       | I           | ST             | Yes        | Capture inputs 7/8.                                                                                                                                                                                                                                        |

| OCFA          | I           | ST             | Yes        | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).                                                                                                                                                                                                |

| OC1-OC4       | 0           | _              | Yes        | Compare outputs 1 through 4.                                                                                                                                                                                                                               |

| INT0          | I           | ST             | No         | External interrupt 0.                                                                                                                                                                                                                                      |

| INT1          | I           | ST             | Yes        | External interrupt 1.                                                                                                                                                                                                                                      |

| INT2          | I           | ST             | Yes        | External interrupt 2.                                                                                                                                                                                                                                      |

| RA0-RA4       | I/O         | ST             | No         | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                         |

| RA7-RA10      | I/O         | ST             | No         | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                         |

| RB0-RB15      | I/O         | ST             | No         | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                         |

| RC0-RC9       | I/O         | ST             | No         | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                         |

| T1CK          | I           | ST             | No         | Timer1 external clock input.                                                                                                                                                                                                                               |

| T2CK          | I           | ST             | Yes        | Timer2 external clock input.                                                                                                                                                                                                                               |

| T3CK          | I           | ST             | Yes        | Timer3 external clock input.                                                                                                                                                                                                                               |

| T4CK          | I           | ST             | Yes        | Timer4 external clock input.                                                                                                                                                                                                                               |

| T5CK          | I           | ST             | Yes        | Timer5 external clock input.                                                                                                                                                                                                                               |

| U1CTS         | I           | ST             | Yes        | UART1 clear to send.                                                                                                                                                                                                                                       |

| U1RTS         | 0           |                | Yes        | UART1 ready to send.                                                                                                                                                                                                                                       |

| U1RX          |             | ST             | Yes        | UART1 receive. UART1 transmit.                                                                                                                                                                                                                             |

| U1TX          | 0           |                | Yes        |                                                                                                                                                                                                                                                            |

| U2CTS         |             | ST             | Yes        | UART2 clear to send.                                                                                                                                                                                                                                       |

| U2RTS<br>U2RX | 0           | ST             | Yes<br>Yes | UART2 ready to send. UART2 receive.                                                                                                                                                                                                                        |

| U2TX          | 0           | 51             | Yes        | UART2 transmit.                                                                                                                                                                                                                                            |

| SCK1          | 1/0         | ST             | Yes        | Synchronous serial clock input/output for SPI1.                                                                                                                                                                                                            |

| SDI1          | 1/0         | ST             | Yes        | SPI1 data in.                                                                                                                                                                                                                                              |

| SDO1          | Ö           | <u> </u>       | Yes        | SPI1 data out.                                                                                                                                                                                                                                             |

| SS1           | 1/0         | ST             | Yes        | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                                                                                             |

| SCK2          | I/O         | ST             | Yes        | Synchronous serial clock input/output for SPI2.                                                                                                                                                                                                            |

| SDI2          | ı. O        | ST             | Yes        | SPI2 data in.                                                                                                                                                                                                                                              |

| SDO2          | Ö           | _              | Yes        | SPI2 data out.                                                                                                                                                                                                                                             |

| SS2           | I/O         | ST             | Yes        | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                                                             |

| SCL1          | I/O         | ST             | No         | Synchronous serial clock input/output for I2C1.                                                                                                                                                                                                            |

| SDA1          | I/O         | ST             | No         | Synchronous serial data input/output for I2C1.                                                                                                                                                                                                             |

| ASCL1         | I/O         | ST             | No         | Alternate synchronous serial clock input/output for I2C1.                                                                                                                                                                                                  |

| ASDA1         | I/O         | ST             | No         | Alternate synchronous serial data input/output for I2C1.                                                                                                                                                                                                   |

**Legend:** CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

PPS = Peripheral Pin Select

Analog = Analog input

P = Power

O = Output TTL = TTL input buffer

I = Input

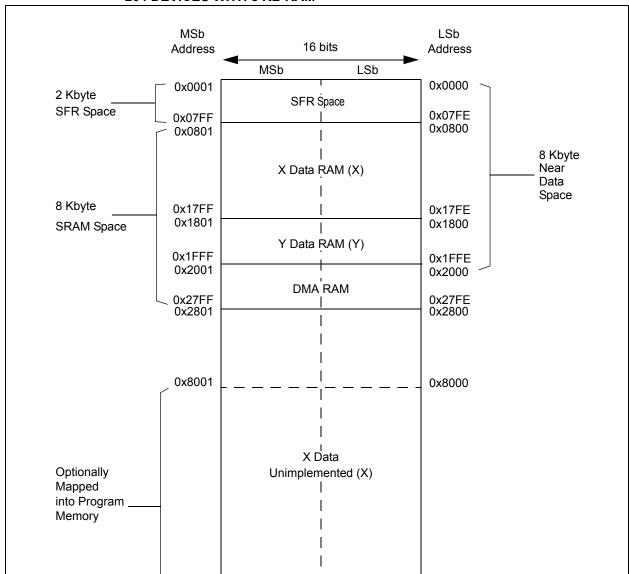

FIGURE 4-4: DATA MEMORY MAP FOR dsPIC33FJ128MC202/204 AND dsPIC33FJ64MC202/204 DEVICES WITH 8 KB RAM

0xFFFF

0xFFFE

TABLE 4-21: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 0 OR 1 (FOR dsPIC33FJ128MC802/804 AND dsPIC33FJ64MC802/804)

| File Name  | Addr | Bit 15  | Bit 14   | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9    | Bit 8  | Bit 7    | Bit 6                                       | Bit 5  | Bit 4                             | Bit 3     | Bit 2    | Bit 1    | Bit 0  | All<br>Resets |

|------------|------|---------|----------|---------|---------|---------|------------|----------|--------|----------|---------------------------------------------|--------|-----------------------------------|-----------|----------|----------|--------|---------------|

| C1CTRL1    | 0400 | _       | _        | CSIDL   | ABAT    | _       | RI         | EQOP<2:0 | >      | OPN      | 10DE<2:0                                    | >      | _                                 | CANCAP    | _        | _        | WIN    | 0480          |

| C1CTRL2    | 0402 | -       | _        | _       | 1       | -       | _          | _        | _      | _        | _                                           | _      |                                   | 1D        | NCNT<4:0 | >        |        | 0000          |

| C1VEC      | 0404 | -       | _        | _       |         | F       | ILHIT<4:0> |          |        | _        |                                             |        | ı                                 | CODE<6:0> | •        |          |        | 0000          |

| C1FCTRL    | 0406 | D       | MABS<2:0 | >       |         | _       | _          | _        | _      | _        | _                                           | _      |                                   | 1         | FSA<4:0> |          |        | 0000          |

| C1FIFO     | 0408 | _       | _        |         |         | FBP<    | 5:0>       |          |        | _        | _                                           |        |                                   | FNRB      | <5:0>    |          |        | 0000          |

| C1INTF     | 040A | -       |          | TXBO    | TXBP    | RXBP    | TXWAR      | RXWAR    | EWARN  | IVRIF    | WAKIF                                       | ERRIF  | _                                 | FIFOIF    | RBOVIF   | RBIF     | TBIF   | 0000          |

| C1INTE     | 040C | -       |          | _       | 1       | -       | _          | _        | _      | IVRIE    | WAKIE                                       | ERRIE  | _                                 | FIFOIE    | RBOVIE   | RBIE     | TBIE   | 0000          |

| C1EC       | 040E |         |          |         | TERRCN  | NT<7:0> |            |          |        |          |                                             |        | RERRCN                            | T<7:0>    |          |          |        | 0000          |

| C1CFG1     | 0410 | -       |          | _       | 1       | -       | _          | _        | _      | SJW<1    | :0>                                         |        |                                   | BRP<      | 5:0>     |          |        | 0000          |

| C1CFG2     | 0412 | -       | WAKFIL   | _       | 1       | -       | SE         | G2PH<2:0 | )>     | SEG2PHTS | SAM                                         | S      | EG1PH<2:                          | <0>       | Р        | RSEG<2:0 | )>     | 0000          |

| C1FEN1     | 0414 | FLTEN15 | FLTEN14  | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10    | FLTEN9   | FLTEN8 | FLTEN7   | FLTEN6                                      | FLTEN5 | FLTEN4                            | FLTEN3    | FLTEN2   | FLTEN1   | FLTEN0 | FFFF          |

| C1FMSKSEL1 | 0418 | F7MSk   | <1:0>    | F6MSk   | <<1:0>  | F5MSI   | <<1:0>     | F4MS     | K<1:0> | F3MSK<   | F3MSK<1:0> F2MSK<1:0> F1MSK<1:0> F0MSK<1:0> |        |                                   | 0000      |          |          |        |               |

| C1FMSKSEL2 | 041A | F15MS   | K<1:0>   | F14MS   | K<1:0>  | F13MS   | K<1:0>     | F12MS    | K<1:0> | F11MSK   | <1:0>                                       | F10MS  | F10MSK<1:0> F9MSK<1:0> F8MSK<1:0> |           |          | 0000     |        |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-22: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 0 (FOR dsPIC33FJ128MC802/804 AND dsPIC33FJ64MC802/804)

|           |               |         |                             |         |         |         |                                                                            | (-      |          |           |         |         |         |         |         | ,       |         |               |

|-----------|---------------|---------|-----------------------------|---------|---------|---------|----------------------------------------------------------------------------|---------|----------|-----------|---------|---------|---------|---------|---------|---------|---------|---------------|

| File Name | Addr          | Bit 15  | Bit 14                      | Bit 13  | Bit 12  | Bit 11  | Bit 10                                                                     | Bit 9   | Bit 8    | Bit 7     | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|           | 0400-<br>041E |         | See definition when WIN = x |         |         |         |                                                                            |         |          |           |         |         |         |         |         |         |         |               |

| C1RXFUL1  | 0420          | RXFUL15 | RXFUL14                     | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10                                                                    | RXFUL9  | RXFUL8   | RXFUL7    | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C1RXFUL2  | 0422          | RXFUL31 | RXFUL30                     | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26                                                                    | RXFUL25 | RXFUL24  | RXFUL23   | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C1RXOVF1  | 0428          | RXOVF15 | RXOVF14                     | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10                                                                    | RXOVF9  | RXOVF8   | RXOVF7    | RXOVF6  | RXOVF5  | RXOVF4  | RXOVF3  | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C1RXOVF2  | 042A          | RXOVF31 | RXOVF30                     | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26                                                                    | RXOVF25 | RXOVF24  | RXOVF23   | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C1TR01CON | 0430          | TXEN1   | TXABT1                      | TXLARB1 | TXERR1  | TXREQ1  | RTREN1                                                                     | TX1PF   | RI<1:0>  | TXEN0     | TXABT0  | TXLARB0 | TXERR0  | TXREQ0  | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C1TR23CON | 0432          | TXEN3   | TXABT3                      | TXLARB3 | TXERR3  | TXREQ3  | RTREN3                                                                     | TX3PF   | RI<1:0>  | TXEN2     | TXABT2  | TXLARB2 | TXERR2  | TXREQ2  | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C1TR45CON | 0434          | TXEN5   | TXABT5                      | TXLARB5 | TXERR5  | TXREQ5  | RTREN5                                                                     | TX5PF   | RI<1:0>  | TXEN4     | TXABT4  | TXLARB4 | TXERR4  | TXREQ4  | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C1TR67CON | 0436          | TXEN7   | TXABT7                      | TXLARB7 | TXERR7  | TXREQ7  | Q7 RTREN7 TX7PRI<1:0> TXEN6 TXABT6 TXLARB6 TXER6 TXREQ6 RTREN6 TX6PRI<1:0> |         |          |           |         |         | RI<1:0> | 0000    |         |         |         |               |

| C1RXD     | 0440          |         | •                           |         |         | •       |                                                                            | •       | Received | Data Word |         | •       | •       | •       |         |         | •       | xxxx          |

| C1TXD     | 0442          |         | Transmit Data Word xxxx     |         |         |         |                                                                            |         |          |           |         |         |         |         |         |         |         |               |

dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 4.6.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note

The modulo corrected effective address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the effective address. When an address offset (such as [W7 + W2]) is used, Modulo Address correction is performed, but the contents of the register remain unchanged.

## 4.7 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Therefore, the only operand requiring reversal is the modifier.

# 4.7.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- The BWM bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing)

- · The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

The XB<14:0> bits is the Bit-Reversed Address modifier, or pivot point, which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

Note:

All bit-reversed EA calculations assume word-sized data (LSb of every EA is always clear). The XB value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data, and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB), and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note:

The Modulo Addressing and Bit-Reversed Addressing should not be enabled together. If an application attempts to do so, Bit-Reversed Addressing assumes priority when active for the X WAGU and X WAGU, Modulo Addressing is disabled. However, Modulo Addressing continues to function in the X RAGU.

If Bit-Reversed Addressing has already been enabled by setting the BREN bit (XBREV<15>), a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the bit-reversed pointer.

#### 6.1 Resets Resources

Many useful resources related to Resets are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

#### 6.1.1 KEY RESOURCES

- Section 8. "Reset" (DS70192)

- · Code Samples

- · Application Notes

- · Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- · Development Tools

## REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

bit 2 CMIE: Comparator Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 1 MI2C1IE: I2C1 Master Events Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 0 SI2C1IE: I2C1 Slave Events Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

#### REGISTER 7-22: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

| U-0    | R/W-1 | R/W-0       | R/W-0 | U-0 | R/W-1 | R/W-0       | R/W-0 |

|--------|-------|-------------|-------|-----|-------|-------------|-------|

| _      |       | U2TXIP<2:0> |       | _   |       | U2RXIP<2:0> |       |

| bit 15 |       |             |       |     |       |             | bit 8 |

| U-0   | R/W-1 | R/W-0       | R/W-0 | U-0 | R/W-1 | R/W-0     | R/W-0 |

|-------|-------|-------------|-------|-----|-------|-----------|-------|

| _     |       | INT2IP<2:0> |       | _   |       | T5IP<2:0> |       |

| bit 7 |       |             |       |     |       |           | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 U2TXIP<2:0>: UART2 Transmitter Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 **U2RXIP<2:0>:** UART2 Receiver Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 7 **Unimplemented:** Read as '0'

bit 6-4 INT2IP<2:0>: External Interrupt 2 Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

\_

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3 Unimplemented: Read as '0'

bit 2-0 T5IP<2:0>: Timer5 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

#### REGISTER 8-9: DSADR: MOST RECENT DMA RAM ADDRESS

| R-0    | R-0 | R-0 | R-0   | R-0     | R-0 | R-0 | R-0 |  |  |  |  |  |  |  |

|--------|-----|-----|-------|---------|-----|-----|-----|--|--|--|--|--|--|--|

|        |     |     | DSADF | R<15:8> |     |     |     |  |  |  |  |  |  |  |

| bit 15 |     |     |       |         |     |     |     |  |  |  |  |  |  |  |

| R-0   | R-0 | R-0 | R-0  | R-0    | R-0 | R-0 | R-0   |

|-------|-----|-----|------|--------|-----|-----|-------|

|       |     | _   | DSAD | R<7:0> | _   |     |       |

| bit 7 |     |     |      |        |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 DSADR<15:0>: Most Recent DMA RAM Address Accessed by DMA Controller bits

#### REGISTER 11-4: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| _      | _   | _   |       |       | T5CKR<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| _     | _   | _   |       |       | T4CKR<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

Legend:

bit 12-8

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

T5CKR<4:0>: Assign Timer5 External Clock (T5CK) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

•

•

•

00001 = Input tied to RP1

00000 = Input tied to RP0

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 T4CKR<4:0>: Assign Timer4 External Clock (T4CK) to the corresponding RPn pin

11111 = Input tied to Vss

11001 = Input tied to RP25

•

00001 = Input tied to RP1

00000 = Input tied to RP0

#### REGISTER 11-18: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| _      | _   | _   |       |       | SCK2R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| _     | _   | _   |       |       | SDI2R<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12-8 SCK2R<4:0>: Assign SPI2 Clock Input (SCK2) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

•

•

•

00001 = Input tied to RP1 00000 = Input tied to RP0

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 SDI2R<4:0>: Assign SPI2 Data Input (SDI2) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

•

•

•

00001 = Input tied to RP1 00000 = Input tied to RP0

#### 12.1 Timer Resources

Many useful resources related to Timers are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

### 12.1.1 KEY RESOURCES

- Section 11. "Timers" (DS70205)

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- · Development Tools

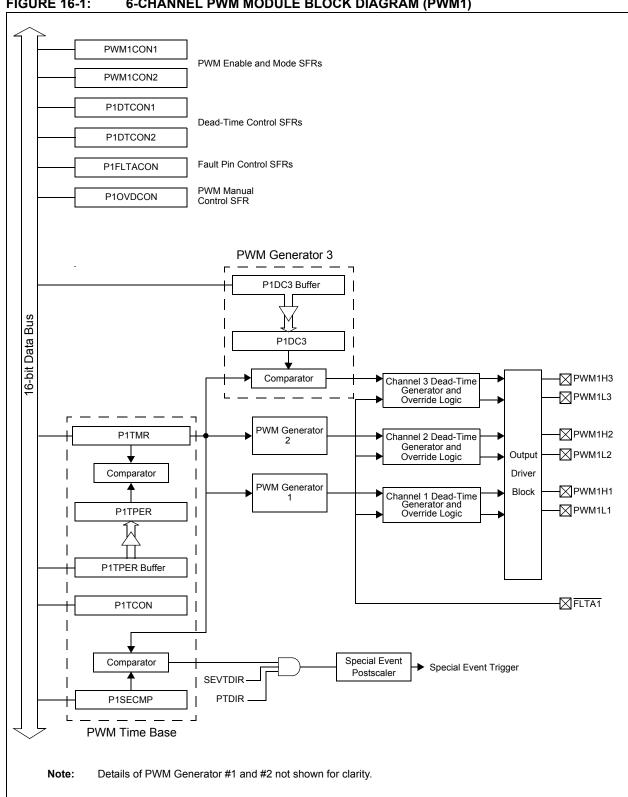

**FIGURE 16-1:** 6-CHANNEL PWM MODULE BLOCK DIAGRAM (PWM1)

#### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID5   | EID4  | EID3  | EID2  | EID1  | EID0  | RTR   | RB1   |

| bit 15 |       |       |       |       |       |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-------|-------|-------|-------|-------|

| _     | _   | _   | RB0   | DLC3  | DLC2  | DLC1  | DLC0  |

| bit 7 |     |     |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **EID<5:0>:** Extended Identifier bits bit 9 **RTR:** Remote Transmission Request bit

1 = Message will request remote transmission

0 = Normal message

bit 8 RB1: Reserved Bit 1

User must set this bit to '0' per CAN protocol.

bit 7-5 **Unimplemented:** Read as '0'

bit 4 RB0: Reserved Bit 0

User must set this bit to '0' per CAN protocol.

bit 3-0 **DLC<3:0>:** Data Length Code bits

#### BUFFER 21-4: ECAN™ MESSAGE BUFFER WORD 3

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | Byt   | e 1   |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x            | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x              | R/W-x |

|------------------|-------|------------------|-------|-------------------|-----------------|--------------------|-------|

|                  |       |                  | Ву    | te 0              |                 |                    |       |

| bit 7            |       |                  |       |                   |                 |                    | bit 0 |

| Legend:          |       |                  |       |                   |                 |                    |       |

| R = Readable b   | oit   | W = Writable bit |       | U = Unimplem      | nented bit, rea | d as '0'           |       |

| -n = Value at Po | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unknown | n     |

bit 15-8 **Byte 1<15:8>:** ECAN™ Message byte 0 bit 7-0 **Byte 0<7:0>:** ECAN Message byte 1

### 23.6 DAC Control Registers

#### REGISTER 23-1: DAC1CON: DAC CONTROL REGISTER

| R/W-0  | U-0    | R/W-0   | R/W-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|--------|---------|-------|-----|-----|-----|-------|

| DACEN  | _      | DACSIDL | AMPON | _   | _   | _   | FORM  |

| bit 15 | bit 15 |         |       |     |     |     |       |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-1 | R/W-0 | R/W-1 |

|-------|-------|-------|-------|-------------|-------|-------|-------|

| _     |       |       |       | DACFDIV<6:0 | )>    |       |       |

| bit 7 |       |       |       |             | _     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 DACEN: DAC1 Enable bit

1 = Enables module

0 = Disables module

bit 14 **Unimplemented:** Read as '0'

bit 13 DACSIDL: Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12 AMPON: Enable Analog Output Amplifier in Sleep Mode/Stop-in Idle Mode bit

1 = Analog Output Amplifier is enabled during Sleep Mode/Stop-in Idle mode

0 = Analog Output Amplifier is disabled during Sleep Mode/Stop-in Idle mode

bit 11-9 **Unimplemented:** Read as '0'

bit 8 FORM: Data Format Select bit

1 = Signed integer

0 = Unsigned integer

bit 7 **Unimplemented:** Read as '0'

bit 6-0 DACFDIV<6:0>: DAC Clock Divider bits

1111111 = Divide input clock by 128

•

•

•

0000101 = Divide input clock by 6 (default)

\_

•

•

0000010 = Divide input clock by 3

0000001 = Divide input clock by 2

0000000 = Divide input clock by 1 (no divide)

TABLE 28-2: dsPIC33F CONFIGURATION BITS DESCRIPTION

| Bit Field               | Register           | RTSP Effect | Description                                                                                                                                                                                            |

|-------------------------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BWRP                    | FBS                | Immediate   | Boot Segment Program Flash Write Protection  1 = Boot segment can be written  0 = Boot segment is write-protected                                                                                      |

| BSS<2:0>                | FBS                | Immediately | Boot Segment Program Flash Code Protection Size x11 = No Boot program Flash segment                                                                                                                    |

|                         |                    |             | Boot space is 1K Instruction Words (except interrupt vectors)  110 = Standard security; boot program Flash segment ends at  0x0007FE  010 = High security; boot program Flash segment ends at 0x0007FE |

|                         |                    |             | Boot space is 4K Instruction Words (except interrupt vectors)  101 = Standard security; boot program Flash segment, ends at                                                                            |

|                         |                    |             | 0x001FFE  001 = High security; boot program Flash segment ends at 0x001FFE                                                                                                                             |

|                         |                    |             | Boot space is 8K Instruction Words (except interrupt vectors)  100 = Standard security; boot program Flash segment ends at  0x003FFE                                                                   |

|                         |                    |             | 000 = High security; boot program Flash segment ends at 0x003FFE                                                                                                                                       |

| RBS<1:0> <sup>(1)</sup> | FBS                | Immediate   | Boot Segment RAM Code Protection Size  11 = No Boot RAM defined                                                                                                                                        |

|                         |                    |             | 10 = Boot RAM is 128 bytes                                                                                                                                                                             |

|                         |                    |             | 01 = Boot RAM is 256 bytes                                                                                                                                                                             |

| SWRP <sup>(1)</sup>     | FSS <sup>(1)</sup> | Immediate   | 00 = Boot RAM is 1024 bytes                                                                                                                                                                            |

| SWRF                    | F33\*/             | inimediate  | Secure Segment Program Flash Write-Protect bit  1 = Secure Segment can bet written  0 = Secure Segment is write-protected                                                                              |

| SSS<2:0>                | FSS                | Immediate   | Secure Segment Program Flash Code Protection Size (Secure segment is not implemented on 32K devices) x11 = No Secure program flash segment                                                             |

|                         |                    |             | Secure space is 4K IW less BS<br>110 = Standard security; secure program Flash segment starts at End<br>of BS, ends at 0x001FFE                                                                        |

|                         |                    |             | 010 = High security; secure program Flash segment starts at End of BS, ends at 0x001FFE                                                                                                                |

|                         |                    |             | Secure space is 8K IW less BS<br>101 = Standard security; secure program Flash segment starts at End<br>of BS, ends at 0x003FFE                                                                        |

|                         |                    |             | 001 = High security; secure program Flash segment starts at End of BS, ends at 0x003FFE                                                                                                                |

|                         |                    |             | Secure space is 16K IW less BS<br>100 = Standard security; secure program Flash segment starts at End<br>of BS, ends at 007FFEh                                                                        |

|                         |                    |             | 000 = High security; secure program Flash segment starts at End of BS, ends at 0x007FFE                                                                                                                |

| RSS<1:0> <sup>(1)</sup> | FSS <sup>(1)</sup> | Immediate   | Secure Segment RAM Code Protection  11 = No Secure RAM defined                                                                                                                                         |

|                         |                    |             | 10 = Secure RAM is 256 Bytes less BS RAM                                                                                                                                                               |

|                         |                    |             | 01 = Secure RAM is 2048 Bytes less BS RAM                                                                                                                                                              |

|                         |                    |             | 00 = Secure RAM is 4096 Bytes less BS RAM                                                                                                                                                              |

Note 1: This Configuration register is not available on dsPIC33FJ32MC302/304 devices.

## TABLE 29-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |                                        | Assembly Syntax      | Description                                                     | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|----------------------------------------|----------------------|-----------------------------------------------------------------|---------------|----------------|--------------------------|

| 48                 | MPY                  | MPY<br>Wm*Wn,A                         | cc, Wx, Wxd, Wy, Wyd | Multiply Wm by Wn to Accumulator                                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY<br>Wm*Wm,A                         | cc, Wx, Wxd, Wy, Wyd | Square Wm to Accumulator                                        | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 49                 | MPY.N                | MPY.N<br>Wm*Wn,A                       | cc, Wx, Wxd, Wy, Wyd | -(Multiply Wm by Wn) to Accumulator                             | 1             | 1              | None                     |

| 50                 | MSC                  | MSC Wm*Wm, Acc, Wx, Wxd, Wy, Wyd , AWB |                      | Multiply and Subtract from Accumulator                          | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 51                 | MUL                  | MUL.SS                                 | Wb, Ws, Wnd          | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)                        | 1             | 1              | None                     |

|                    |                      | MUL.SU                                 | Wb, Ws, Wnd          | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)                      | 1             | 1              | None                     |

|                    |                      | MUL.US                                 | Wb, Ws, Wnd          | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)                      | 1             | 1              | None                     |

|                    |                      | MUL.UU                                 | Wb, Ws, Wnd          | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(Ws)                    | 1             | 1              | None                     |

|                    |                      | MUL.SU                                 | Wb,#lit5,Wnd         | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)                    | 1             | 1              | None                     |

|                    |                      | MUL.UU                                 | Wb,#lit5,Wnd         | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(lit5)                  | 1             | 1              | None                     |

|                    |                      | MUL                                    | f                    | W3:W2 = f * WREG                                                | 1             | 1              | None                     |

| 52                 | NEG                  | NEG                                    | Acc                  | Negate Accumulator                                              | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG                                    | f                    | $f = \overline{f} + 1$                                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG                                    | f,WREG               | WREG = <del>f</del> + 1                                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG                                    | Ws,Wd                | $Wd = \overline{Ws} + 1$                                        | 1             | 1              | C,DC,N,OV,Z              |

| 53                 | NOP                  | NOP                                    |                      | No Operation                                                    | 1             | 1              | None                     |

|                    |                      | NOPR                                   |                      | No Operation                                                    | 1             | 1              | None                     |

| 54                 | POP                  | POP                                    | f                    | Pop f from Top-of-Stack (TOS)                                   | 1             | 1              | None                     |

|                    |                      | POP                                    | Wdo                  | Pop from Top-of-Stack (TOS) to Wdo                              | 1             | 1              | None                     |

|                    |                      | POP.D                                  | Wnd                  | Pop from Top-of-Stack (TOS) to W(nd):W(nd + 1)                  | 1             | 2              | None                     |

|                    |                      | POP.S                                  |                      | Pop Shadow Registers                                            | 1             | 1              | All                      |

| 55                 | PUSH                 | PUSH                                   | f                    | Push f to Top-of-Stack (TOS)                                    | 1             | 1              | None                     |

|                    |                      | PUSH                                   | Wso                  | Push Wso to Top-of-Stack (TOS)                                  | 1             | 1              | None                     |

|                    |                      | PUSH.D                                 | Wns                  | Push W(ns):W(ns + 1) to Top-of-Stack (TOS)                      | 1             | 2              | None                     |

|                    |                      | PUSH.S                                 |                      | Push Shadow Registers                                           | 1             | 1              | None                     |

| 56                 | PWRSAV               | PWRSAV                                 | #lit1                | Go into Sleep or Idle mode                                      | 1             | 1              | WDTO,Sleep               |

| 57                 | RCALL                | RCALL                                  | Expr                 | Relative Call                                                   | 1             | 2              | None                     |

|                    |                      | RCALL                                  | Wn                   | Computed Call                                                   | 1             | 2              | None                     |

| 58                 | REPEAT               | REPEAT                                 | #lit14               | Repeat Next Instruction lit14 + 1 times                         | 1             | 1              | None                     |

|                    |                      | REPEAT                                 | Wn                   | Repeat Next Instruction (Wn) + 1 times                          | 1             | 1              | None                     |

| 59                 | RESET                | RESET                                  |                      | Software device Reset                                           | 1             | 1              | None                     |

| 60                 | RETFIE               | RETFIE                                 |                      | Return from interrupt                                           | 1             | 3 (2)          | None                     |

| 61                 | RETLW                | RETLW                                  | #lit10,Wn            | Return with literal in Wn                                       | 1             | 3 (2)          | None                     |

| 62                 | RETURN               | RETURN                                 |                      | Return from Subroutine                                          | 1             | 3 (2)          | None                     |

| 63                 | RLC                  | RLC                                    | f                    | f = Rotate Left through Carry f                                 | 1             | 1              | C,N,Z                    |

|                    |                      | RLC                                    | f, WREG              | WREG = Rotate Left through Carry Wa                             | 1             | 1              | C,N,Z                    |

| 64                 | DING                 | RLC                                    | Ws,Wd                | Wd = Rotate Left through Carry Ws                               | 1             | 1              | C,N,Z                    |

| 64                 | RLNC                 | RLNC                                   | f whec               | f = Rotate Left (No Carry) f                                    | 1             | 1              | N,Z                      |

|                    |                      | RLNC                                   | f, WREG              | WREG = Rotate Left (No Carry) f  Wd = Rotate Left (No Carry) Ws | 1             | 1              | N,Z<br>N,Z               |

| 65                 | DDC                  | RLNC                                   | Ws,Wd<br>f           | f = Rotate Left (No Carry) ws                                   | 1             | 1              |                          |

| 00                 | RRC                  | RRC                                    | f,WREG               | WREG = Rotate Right through Carry f                             | 1             | 1              | C,N,Z<br>C,N,Z           |

|                    |                      | RRC                                    |                      | Wd = Rotate Right through Carry Ws                              | 1             | 1              | C,N,Z                    |

|                    | <u> </u>             | LLC                                    | Ws,Wd                | TVG - Notate Night through Cally WS                             | <u>'</u>      | 1              | ∪,11,∠                   |

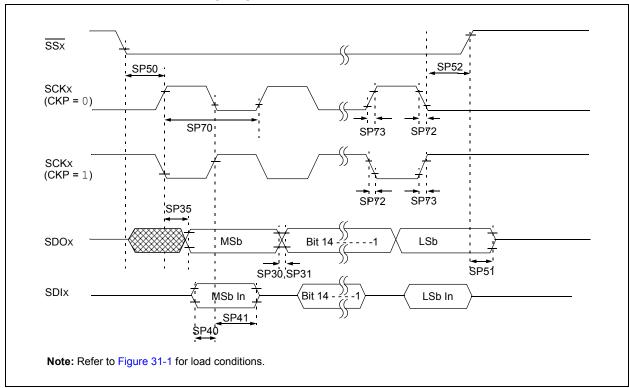

FIGURE 31-20: SPIX SLAVE MODE (FULL-DUPLEX CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

## Revision C (May 2009)

This revision includes minor typographical and formatting changes throughout the data sheet text.

Global changes include:

- Changed all instances of OSCI to OSC1 and OSCO to OSC2

- Changed all instances of VDDCORE and VDDCORE/ VCAP to VCAP/VDDCORE

The other changes are referenced by their respective section in the following table.

TABLE A-2: MAJOR SECTION UPDATES

| Section Name                                                                              | Update Description                                                                                                      |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit Digital Signal Controllers"                                     | Updated all pin diagrams to denote the pin voltage tolerance (see "Pin Diagrams").                                      |

|                                                                                           | Added Note 2 to the 28-Pin QFN-S and 44-Pin QFN pin diagrams, which references pin connections to Vss.                  |

| Section 1.0 "Device Overview"                                                             | Updated AVDD in the PINOUT I/O Descriptions (see Table 1-1).                                                            |

| Section 2.0 "Guidelines for Getting<br>Started with 16-bit Digital Signal<br>Controllers" | Added new section to the data sheet that provides guidelines on getting started with 16-bit Digital Signal Controllers. |

| Section 3.0 "CPU"                                                                         | Updated CPU Core Block Diagram with a connection from the DSP Engine to the Y Data Bus (see Figure 3-1).                |

|                                                                                           | Vertically extended the X and Y Data Bus lines in the DSP Engine Block Diagram (see Figure 3-3).                        |

| Section 4.0 "Memory Organization"                                                         | Updated Reset value for CORCON in the CPU Core Register Map (see Table 4-1).                                            |

|                                                                                           | Removed the FLTA1IE bit (IEC3) from the Interrupt Controller Register Map (see Table 4-4).                              |

|                                                                                           | Updated bit locations for RPINR25 in the Peripheral Pin Select Input Register Map (see Table 4-24).                     |

|                                                                                           | Updated the Reset value for CLKDIV in the System Control Register Map (see Table 4-36).                                 |

| Section 5.0 "Flash Program<br>Memory"                                                     | Updated <b>Section 5.3 "Programming Operations"</b> with programming time formula.                                      |

| Section 9.0 "Oscillator                                                                   | Updated the Oscillator System Diagram and added Note 2 (see Figure 9-1).                                                |

| Configuration"                                                                            | Updated default bit values for DOZE<2:0> and FRCDIV<2:0> in the Clock Divisor (CLKDIV) Register (see Register 9-2).     |

|                                                                                           | Added a paragraph regarding FRC accuracy at the end of <b>Section 9.1.1</b> "System Clock Sources".                     |

|                                                                                           | Added Note 3 to Section 9.2.2 "Oscillator Switching Sequence".                                                          |

|                                                                                           | Added Note 1 to the FRC Oscillator Tuning (OSCTUN) Register (see Register 9-4).                                         |

| Section 10.0 "Power-Saving                                                                | Added the following registers:                                                                                          |

| Features"                                                                                 | PMD1: Peripheral Module Disable Control Register 1 (Register 10-1)                                                      |

|                                                                                           | PMD2: Peripheral Module Disable Control Register 2 (Register 10-2)                                                      |

|                                                                                           | PMD3: Peripheral Module Disable Control Register 3 (Register 10-3)                                                      |