Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XEI

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

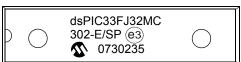

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc204-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

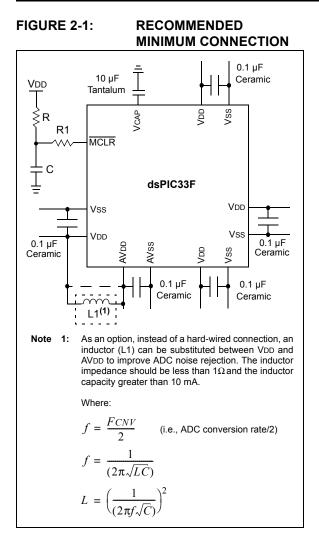

### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, preferably surface mount connected within one-eights inch of the VCAP pin connected to ground. The type can be ceramic or tantalum. Refer to **Section 31.0** "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to Section 28.2 "On-Chip Voltage Regulator" for details.

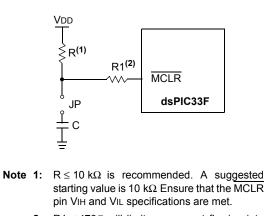

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides for two specific device functions:

- Device Reset

- Device programming and debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

## EXAMPLE OF MCLR PIN CONNECTIONS

2:  $\underline{R1} \leq 470\Omega$  will limit any current flowing into MCLR from the external capacitor C, in the event of MCLR pin breakdown due to Electrostatic Discharge (ESD) or <u>Electrical</u> Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met.

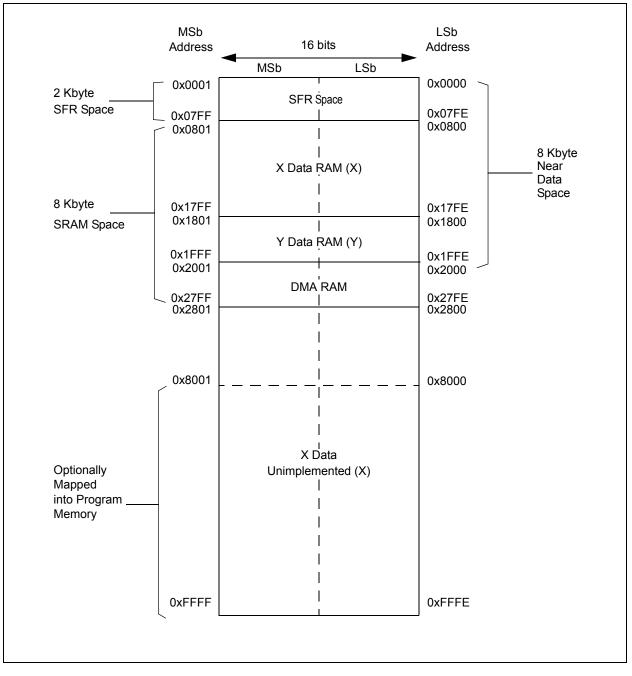

### FIGURE 4-4: DATA MEMORY MAP FOR dsPIC33FJ128MC202/204 AND dsPIC33FJ64MC202/ 204 DEVICES WITH 8 KB RAM

# TABLE 4-1: CPU CORE REGISTERS MAP (CONTINUED)

|          |      |        |        |        |          |        | ,      |        |          |              |           |         |       |       |       |       |       |               |

|----------|------|--------|--------|--------|----------|--------|--------|--------|----------|--------------|-----------|---------|-------|-------|-------|-------|-------|---------------|

| SFR Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12   | Bit 11 | Bit 10 | Bit 9  | Bit 8    | Bit 7        | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| MODCON   | 0046 | XMODEN | YMODEN | -      | —        |        | BWN    | /<3:0> |          |              | YWM       | <3:0>   |       |       | XWM   | <3:0> |       | 0000          |

| XMODSRT  | 0048 |        |        |        |          |        |        | >      | (S<15:1> |              |           |         |       |       |       |       | 0     | XXXX          |

| XMODEND  | 004A |        |        |        |          |        |        | >      | (E<15:1> |              |           |         |       |       |       |       | 1     | XXXX          |

| YMODSRT  | 004C |        |        |        |          |        |        | Y      | ′S<15:1> |              |           |         |       |       |       |       | 0     | XXXX          |

| YMODEND  | 004E |        |        |        |          |        |        | γ      | ′E<15:1> |              |           |         |       |       |       |       | 1     | XXXX          |

| XBREV    | 0050 | BREN   |        |        | XB<14:0> |        |        |        |          |              |           |         | XXXX  |       |       |       |       |               |

| DISICNT  | 0052 | —      | _      |        |          |        |        |        | Disabl   | e Interrupts | Counter R | egister |       |       |       |       |       | XXXX          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-12: I2C1 REGISTER MAP

| SFR Name | Addr     | Bit 15       | Bit 14     | Bit 13     | Bit 12      | Bit 11       | Bit 10       | Bit 9        | Bit 8       | Bit 7 | Bit 6 | Bit 5      | Bit 4        | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|----------|--------------|------------|------------|-------------|--------------|--------------|--------------|-------------|-------|-------|------------|--------------|----------|-------|-------|-------|---------------|

| I2C1RCV  | 0200     | _            | -          |            | _           | _            |              | _            |             |       |       |            | Receive      | Register |       |       |       | 0000          |

| I2C1TRN  | 0202     | _            | _          |            | —           | —            |              | —            | _           |       |       |            | Transmit     | Register |       |       |       | OOFF          |

| I2C1BRG  | 0204     | _            | _          |            | —           | —            |              | —            |             |       |       | Baud Rat   | e Generato   | Register |       |       |       | 0000          |

| I2C1CON  | 0206     | I2CEN        |            | I2CSIDL    | SCLREL      | IPMIEN       | A10M         | DISSLW       | SMEN        | GCEN  | STREN | ACKDT      | ACKEN        | RCEN     | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208     | ACKSTAT      | TRSTAT     | _          | _           | _            | BCL          | GCSTAT       | ADD10       | IWCOL | I2COV | D_A        | Р            | S        | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A     | -            | _          | _          | _           | _            | _            |              |             |       |       | Address    | Register     |          |       |       |       | 0000          |

| I2C1MSK  | 020C     | -            | _          | _          | _           | _            | _            |              |             |       |       | Address Ma | isk Register |          |       |       |       | 0000          |

| Legend:  | x = unkr | nown value o | n Reset, — | = unimpler | nented, rea | d as '0'. Re | set values a | are shown ir | n hexadecir | nal.  |       |            |              |          |       |       |       |               |

# TABLE 4-13: UART1 REGISTER MAP

| SFR Name | Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7        | Bit 6   | Bit 5 | Bit 4       | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|------|----------|--------|----------|--------|--------|--------|-------|------------|--------------|---------|-------|-------------|--------------|-------|--------|-------|---------------|

| U1MODE   | 0220 | UARTEN   | —      | USIDL    | IREN   | RTSMD  |        | UEN1  | UEN0       | WAKE         | LPBACK  | ABAUD | URXINV      | BRGH         | PDSE  | _<1:0> | STSEL | 0000          |

| U1STA    | 0222 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT       | URXISI       | EL<1:0> | ADDEN | RIDLE       | PERR         | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224 | _        | _      | _        | _      | _      | _      | _     | UTX8       |              |         | U     | ART Transm  | nit Register |       |        |       | XXXX          |

| U1RXREG  | 0226 | _        | _      | _        | _      | _      | _      | _     | URX8       |              |         | U     | ART Receive | ed Register  |       |        |       | 0000          |

| U1BRG    | 0228 |          |        |          |        |        |        | Bau   | d Rate Ger | erator Presc | aler    |       |             |              |       |        |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-14: UART2 REGISTER MAP

| SFR Name | Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7                            | Bit 6   | Bit 5 | Bit 4      | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|------|----------|--------|----------|--------|--------|--------|-------|------------|----------------------------------|---------|-------|------------|--------------|-------|--------|-------|---------------|

| U2MODE   | 0230 | UARTEN   |        | USIDL    | IREN   | RTSMD  |        | UEN1  | UEN0       | WAKE                             | LPBACK  | ABAUD | URXINV     | BRGH         | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA    | 0232 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT       | URXISE                           | EL<1:0> | ADDEN | RIDLE      | PERR         | FERR  | OERR   | URXDA | 0110          |

| U2TXREG  | 0234 | —        |        | —        |        | —      |        |       | UTX8       |                                  |         | U     | ART Transm | nit Register |       |        |       | XXXX          |

| U2RXREG  | 0236 | —        |        | —        |        | —      |        |       | URX8       |                                  |         | U     | ART Receiv | e Register   |       |        |       | 0000          |

| U2BRG    | 0238 |          |        |          |        |        |        | Bau   | d Rate Ger | Baud Rate Generator Prescaler 00 |         |       |            |              |       |        | 0000  |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TADLE 4                | -2-4. |        |        |        | IN SELEC |        | INE OID IE |       |       |       |       |       |       |       |            |       |       |               |

|------------------------|-------|--------|--------|--------|----------|--------|------------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| File Name              | Addr  | Bit 15 | Bit 14 | Bit 13 | Bit 12   | Bit 11 | Bit 10     | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

| RPINR0                 | 0680  | _      | _      | _      |          |        | INT1R<4:0> |       |       | _     | _     | _     |       | —     | —          | _     | —     | 1F00          |

| RPINR1                 | 0682  | _      |        | _      |          |        | _          |       | _     | _     |       | _     |       |       | INT2R<4:0  | >     |       | 001F          |

| RPINR3                 | 0686  | —      | _      | —      |          |        | T3CKR<4:0> |       |       | _     | _     | _     |       |       | T2CKR<4:0  | >     |       | 1F1F          |

| RPINR4                 | 0688  | _      |        | _      |          |        | T5CKR<4:0> |       |       | _     |       | _     |       |       | T4CKR<4:0  | >     |       | 1F1F          |

| RPINR7                 | 068E  | —      | _      | —      |          |        | IC2R<4:0>  |       |       | _     | _     | _     |       |       | IC1R<4:0>  |       |       | 1F1F          |

| RPINR10                | 0694  | _      |        | _      |          |        | IC8R<4:0>  |       |       | _     |       | _     |       |       | IC7R<4:0>  |       |       | 1F1F          |

| RPINR11                | 0696  | _      |        | _      |          |        | _          |       | _     | _     |       | _     |       |       | OCFAR<4:0  | >     |       | 001F          |

| RPINR12                | 0698  | _      |        | _      |          |        | _          |       | _     | _     | _     | _     |       |       | FLTA1R<4:( | )>    |       | 001F          |

| RPINR13                | 069A  | _      |        | _      |          |        | _          |       | _     | _     |       | _     |       |       | FLTA2R<4:( | )>    |       | 001F          |

| RPINR14                | 069C  | _      |        | _      |          |        | QEB1R<4:0> |       |       | _     | _     | _     |       |       | QEA1R<4:0  | >     |       | 1F1F          |

| RPINR15                | 069E  | _      |        | _      |          |        | _          |       | _     | _     |       | _     |       |       | INDX1R<4:( | )>    |       | 001F          |

| RPINR16                | 06A0  | _      |        | _      |          |        | QEB2R<4:0> |       |       | _     | _     | _     |       |       | QEA2R<4:0  | >     |       | 1F1F          |

| RPINR17                | 06A2  | _      |        | _      |          |        | _          |       | _     | _     |       | _     |       |       | INDX2R<4:( | )>    |       | 001F          |

| RPINR18                | 06A4  | —      | _      | _      |          |        | U1CTSR<4:0 | >     |       | _     | _     | _     |       |       | U1RXR<4:0  | >     |       | 1F1F          |

| RPINR19                | 06A6  | _      |        | _      |          |        | U2CTSR<4:0 | >     |       | _     |       | _     |       |       | U2RXR<4:0  | >     |       | 1F1F          |

| RPINR20                | 06A8  | _      |        | _      |          |        | SCK1R<4:0> |       |       | _     |       | _     |       |       | SDI1R<4:0  | >     |       | 1F1F          |

| RPINR21                | 06AA  | —      | _      | _      | _        | _      | _          | _     | —     | _     | _     | _     |       |       | SS1R<4:0   | >     |       | 001F          |

| RPINR22                | 06AC  | _      |        | _      |          |        | SCK2R<4:0> |       |       | _     |       | _     |       |       | SDI2R<4:0  | >     |       | 1F1F          |

| RPINR23                | 06AE  | _      |        | _      | _        | _      | _          |       | _     | _     | _     | _     |       |       | SS2R<4:0   | >     |       | 001F          |

| RPINR26 <sup>(1)</sup> | 06B4  | _      | _      | _      | _        | _      | _          | _     | _     | _     | _     | _     |       |       | C1RXR<4:0  | >     |       | 001F          |

# TABLE 4-24: PERIPHERAL PIN SELECT INPUT REGISTER MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is present in dsPIC33FJ128MC802/804 and dsPIC33FJ64MC802/804 devices only.

# \_\_\_\_\_ IC3

DS70291G-page 57

# 6.1 Resets Resources

Many useful resources related to Resets are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en532315                                                       |

# 6.1.1 KEY RESOURCES

- Section 8. "Reset" (DS70192)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| U-0          | R/W-1            | R/W-0                                     | R/W-0           | U-0               | R/W-1           | R/W-0            | R/W-0          |

|--------------|------------------|-------------------------------------------|-----------------|-------------------|-----------------|------------------|----------------|

| _            |                  | T1IP<2:0>                                 |                 |                   |                 | OC1IP<2:0>       |                |

| oit 15       |                  |                                           |                 |                   |                 |                  | bit            |

|              | <b>D</b> (1) (1) | <b>D</b> 444 0                            | 5444.0          |                   | <b>D</b> 4 4 4  | <b>D</b> # 44 0  | <b>D</b> 444 0 |

| U-0          | R/W-1            | R/W-0                                     | R/W-0           | U-0               | R/W-1           | R/W-0            | R/W-0          |

| —<br>bit 7   |                  | IC1IP<2:0>                                |                 |                   |                 | INT0IP<2:0>      | hit            |

| bit 7        |                  |                                           |                 |                   |                 |                  | bit            |

| Legend:      |                  |                                           |                 |                   |                 |                  |                |

| R = Readab   | le bit           | W = Writable I                            | bit             | U = Unimpler      | mented bit, rea | ad as '0'        |                |

| -n = Value a | t POR            | '1' = Bit is set                          |                 | '0' = Bit is cle  | eared           | x = Bit is unkno | own            |

|              |                  |                                           |                 |                   |                 |                  |                |

| bit 15       | -                | ented: Read as 'o                         |                 |                   |                 |                  |                |

| bit 14-12    |                  | Timer1 Interrupt                          |                 |                   |                 |                  |                |

|              | 111 = Interr     | rupt is priority 7 (I                     | highest prior   | ity interrupt)    |                 |                  |                |

|              | •                |                                           |                 |                   |                 |                  |                |

|              | •                |                                           |                 |                   |                 |                  |                |

|              |                  | rupt is priority 1                        | ablad           |                   |                 |                  |                |

| bit 11       |                  | rupt source is disa                       |                 |                   |                 |                  |                |

|              | -                | ented: Read as '                          |                 |                   | 11 L 11 .       |                  |                |

| bit 10-8     |                  | Cutput Compart<br>Cupt is priority 7 (It  |                 | -                 | ity bits        |                  |                |

|              | •                | upt is priority 7 (i                      | lighest phon    | ity interrupt)    |                 |                  |                |

|              | •                |                                           |                 |                   |                 |                  |                |

|              | •                |                                           |                 |                   |                 |                  |                |

|              |                  | rupt is priority 1                        | ablad           |                   |                 |                  |                |

| bit 7        |                  | rupt source is disa<br>ented: Read as '0  |                 |                   |                 |                  |                |

| bit 6-4      | -                | : Input Capture C                         |                 | orrupt Drigrity b | ito             |                  |                |

| DIL 0-4      |                  | rupt is priority 7 (I                     |                 |                   | 115             |                  |                |

|              | •                |                                           | ingricot priori | ity interrupt)    |                 |                  |                |

|              | •                |                                           |                 |                   |                 |                  |                |

|              | •                |                                           |                 |                   |                 |                  |                |

|              |                  | rupt is priority 1<br>rupt source is disa | abled           |                   |                 |                  |                |

| bit 3        |                  | ented: Read as '(                         |                 |                   |                 |                  |                |

| bit 2-0      | -                | >: External Interr                        |                 | / bite            |                 |                  |                |

| DIL 2-0      |                  | rupt is priority 7 (I                     |                 |                   |                 |                  |                |

|              | •                |                                           | iignest prior   | ity menuply       |                 |                  |                |

|              | •                |                                           |                 |                   |                 |                  |                |

|              | •                |                                           |                 |                   |                 |                  |                |

|              |                  | rupt is priority 1<br>rupt source is disa | ahlad           |                   |                 |                  |                |

|              |                  |                                           |                 |                   |                 |                  |                |

### DECISTED 7 16

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

# **REGISTER 7-32: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER**

| U-0          | U-0                                     | U-0                                           | U-0                             | R-0              | R-0            | R-0             | R-0   |

|--------------|-----------------------------------------|-----------------------------------------------|---------------------------------|------------------|----------------|-----------------|-------|

|              | _                                       | _                                             | _                               |                  | IL             | R<3:0>          |       |

| bit 15       |                                         |                                               |                                 |                  |                |                 | bit 8 |

|              |                                         |                                               |                                 |                  |                |                 |       |

| U-0          | R-0                                     | R-0                                           | R-0                             | R-0              | R-0            | R-0             | R-0   |

| —            |                                         |                                               |                                 | VECNUM<6:0       | >              |                 |       |

| bit 7        |                                         |                                               |                                 |                  |                |                 | bit 0 |

| Legend:      |                                         |                                               |                                 |                  |                |                 |       |

| R = Readab   | le bit                                  | W = Writable                                  | bit                             | U = Unimpler     | nented bit, re | ad as '0'       |       |

| -n = Value a | t POR                                   | '1' = Bit is set                              |                                 | '0' = Bit is cle | ared           | x = Bit is unkr | nown  |

| bit 11-8     | 1111 = CPU<br>•<br>•<br>•<br>0001 = CPU | ew CPU Interru<br>Interrupt Priorit           | y Level is 15<br>y Level is 1   | /el dits         |                |                 |       |

| bit 7        |                                         | Interrupt Priorit<br><b>ted:</b> Read as '    | -                               |                  |                |                 |       |

| bit 6-0      | VECNUM<6:<br>0111111 =  <br>•<br>•      | • <b>0&gt;:</b> Vector Nun<br>nterrupt Vector | nber of Pendii<br>pending is nu | imber 135        | :              |                 |       |

|              |                                         | nterrupt Vector<br>nterrupt Vector            |                                 |                  |                |                 |       |

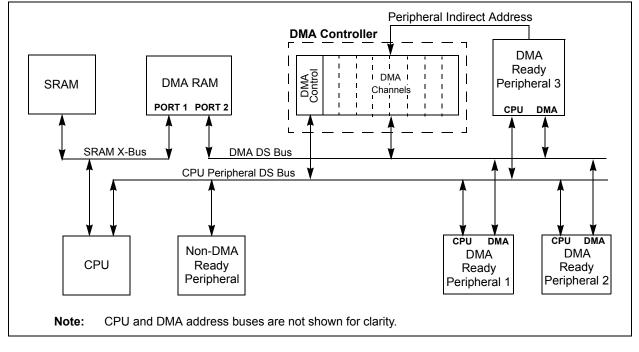

The DMA controller features eight identical data transfer channels.

Each channel has its own set of control and status registers. Each DMA channel can be configured to copy data either from buffers stored in dual port DMA RAM to peripheral SFRs, or from peripheral SFRs to buffers in DMA RAM.

The DMA controller supports the following features:

- Eight DMA channels

- Register Indirect with Post-increment Addressing mode

- Register Indirect without Post-increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- · Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or Automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat block transfer modes

- Ping-Pong mode (automatic switch between two DPSRAM start addresses after each block transfer complete)

- DMA request for each channel can be selected from any supported interrupt source

- · Debug support features

For each DMA channel, a DMA interrupt request is generated when a block transfer is complete. Alternatively, an interrupt can be generated when half of the block has been filled.

## FIGURE 8-1: TOP LEVEL SYSTEM ARCHITECTURE USING A DEDICATED TRANSACTION BUS

NOTES:

| TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTI | ON) <sup>(1)</sup> |

|------------------------------------------------------------|--------------------|

|------------------------------------------------------------|--------------------|

| Input Name              | Function Name | Register | Configuration<br>Bits |

|-------------------------|---------------|----------|-----------------------|

| External Interrupt 1    | INT1          | RPINR0   | INT1R<4:0>            |

| External Interrupt 2    | INT2          | RPINR1   | INT2R<4:0>            |

| Timer2 External Clock   | T2CK          | RPINR3   | T2CKR<4:0>            |

| Timer3 External Clock   | T3CK          | RPINR3   | T3CKR<4:0>            |

| Timer4 External Clock   | T4CK          | RPINR4   | T4CKR<4:0>            |

| Timer5 External Clock   | T5CK          | RPINR4   | T5CKR<4:0>            |

| Input Capture 1         | IC1           | RPINR7   | IC1R<4:0>             |

| Input Capture 2         | IC2           | RPINR7   | IC2R<4:0>             |

| Input Capture 7         | IC7           | RPINR10  | IC7R<4:0>             |

| Input Capture 8         | IC8           | RPINR10  | IC8R<4:0>             |

| Output Compare Fault A  | OCFA          | RPINR11  | OCFAR<4:0>            |

| PWM1 Fault              | FLTA1         | RPINR12  | FLTA1R<4:0>           |

| PWM2 Fault              | FLTA2         | RPINR13  | FLTA2R<4:0>           |

| QEI1 Phase A            | QEA1          | RPINR14  | QEA1R<4:0>            |

| QEI1 Phase B            | QEB1          | RPINR14  | QEB1R<4:0>            |

| QEI1 Index              | INDX1         | RPINR15  | INDX1R<4:0>           |

| QEI2 Phase A            | QEA2          | RPINR16  | QEA2R<4:0>            |

| QEI2Phase B             | QEB2          | RPINR16  | QEB2R<4:0>            |

| QEI2 Index              | INDX2         | RPINR17  | INDX2R<4:0>           |

| UART1 Receive           | U1RX          | RPINR18  | U1RXR<4:0>            |

| UART1 Clear To Send     | U1CTS         | RPINR18  | U1CTSR<4:0>           |

| UART2 Receive           | U2RX          | RPINR19  | U2RXR<4:0>            |

| UART2 Clear To Send     | U2CTS         | RPINR19  | U2CTSR<4:0>           |

| SPI1 Data Input         | SDI1          | RPINR20  | SDI1R<4:0>            |

| SPI1 Clock Input        | SCK1          | RPINR20  | SCK1R<4:0>            |

| SPI1 Slave Select Input | SS1           | RPINR21  | SS1R<4:0>             |

| SPI2 Data Input         | SDI2          | RPINR22  | SDI2R<4:0>            |

| SPI2 Clock Input        | SCK2          | RPINR22  | SCK2R<4:0>            |

| SPI2 Slave Select Input | SS2           | RPINR23  | SS2R<4:0>             |

| ECAN1 Receive           | CIRX          | RPINR26  | CIRXR<4:0>            |

**Note 1:** Unless otherwise noted, all inputs use Schmitt input buffers.

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

# REGISTER 11-11: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15

| U-0             | U-0 | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |

|-----------------|-----|------------------|-------|------------------|------------------|-----------------|-------|

| _               |     | _                |       | —                | —                | _               | _     |

| bit 15          |     | •                | •     |                  |                  |                 | bit 8 |

|                 |     |                  |       |                  |                  |                 |       |

| U-0             | U-0 | U-0              | R/W-1 | R/W-1            | R/W-1            | R/W-1           | R/W-1 |

|                 | _   | —                |       |                  | INDX1R<4:0>      | >               |       |

| bit 7           |     |                  |       |                  |                  |                 | bit ( |

|                 |     |                  |       |                  |                  |                 |       |

| Legend:         |     |                  |       |                  |                  |                 |       |

| R = Readable I  | oit | W = Writable     | bit   | U = Unimpler     | mented bit, read | 1 as '0'        |       |

| -n = Value at P | OR  | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unki | nown  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0

INDX1R<4:0>: Assign QEI1 INDEX (INDX1) to the corresponding RPn pin 11111 = Input tied to Vss 11001 = Input tied to RP25

© 2007-2012 Microchip Technology Inc.

| REGISTER 16-2: PxT | MR: PWM TIMER COUNT VALUE REGISTER |

|--------------------|------------------------------------|

|--------------------|------------------------------------|

| R-0                           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|-------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|

| PTDIR                         |       |                  |       | PTMR<14:8>                         | •     |                 |       |

| bit 15                        |       |                  |       |                                    |       |                 | bit 8 |

| R/W-0                         | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|                               |       |                  | PTM   | R<7:0>                             |       |                 |       |

| bit 7                         |       |                  |       |                                    |       |                 | bit C |

| Legend:                       |       |                  |       |                                    |       |                 |       |

| R = Readable bit W = Writable |       | W = Writable     | bit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at POR             |       | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unkr | nown  |

| bit 15   | PTDIR: PWM Time Base Count Direction Status bit (read-only) |

|----------|-------------------------------------------------------------|

|          | 1 = PWM time base is counting down                          |

|          | 0 = PWM time base is counting up                            |

| bit 14-0 | PTMR<14:0>: PWM Time Base Register Count Value bits         |

# REGISTER 16-3: PxTPER: PWM TIME BASE PERIOD REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                                             | R/W-0                                                                                           | R/W-0                                                                                                     | R/W-0                                                                                                                          |  |

|-----------------------------------|-------|------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

|                                   |       |                  | PTPER<14:8>                                       | >                                                                                               |                                                                                                           |                                                                                                                                |  |

|                                   |       |                  |                                                   |                                                                                                 |                                                                                                           | bit 8                                                                                                                          |  |

|                                   |       |                  |                                                   |                                                                                                 |                                                                                                           |                                                                                                                                |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                                             | R/W-0                                                                                           | R/W-0                                                                                                     | R/W-0                                                                                                                          |  |

|                                   |       | PTPE             | R<7:0>                                            |                                                                                                 |                                                                                                           |                                                                                                                                |  |

|                                   |       |                  |                                                   |                                                                                                 |                                                                                                           | bit 0                                                                                                                          |  |

|                                   |       |                  |                                                   |                                                                                                 |                                                                                                           |                                                                                                                                |  |

|                                   |       |                  |                                                   |                                                                                                 |                                                                                                           |                                                                                                                                |  |

| R = Readable bit W = Writable bit |       |                  | U = Unimplemented bit, read as '0'                |                                                                                                 |                                                                                                           |                                                                                                                                |  |

| -n = Value at POR '               |       | '1' = Bit is set |                                                   | ared                                                                                            | x = Bit is unknown                                                                                        |                                                                                                                                |  |

|                                   | R/W-0 | R/W-0 R/W-0      | R/W-0 R/W-0 R/W-0<br>PTPE<br>bit W = Writable bit | PTPER<14:8:     R/W-0   R/W-0   R/W-0     PTPER<7:0>      bit   W = Writable bit   U = Unimpler | PTPER<14:8>   R/W-0 R/W-0   R/W-0 R/W-0   PTPER<7:0>   bit W = Writable bit   U = Unimplemented bit, real | PTPER<14:8>     R/W-0   R/W-0   R/W-0   R/W-0     PTPER<7:0>       bit   W = Writable bit   U = Unimplemented bit, read as '0' |  |

bit 15 Unimplemented: Read as '0'

bit 14-0 **PTPER<14:0>:** PWM Time Base Period Value bits

# 26.5 Programmable CRC Registers

| U-0             | U-0                                                                                                          | R/W-0                                                                                   | R-0                               | R-0                     | R-0            | R-0             | R-0         |

|-----------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------|-------------------------|----------------|-----------------|-------------|

| _               | _                                                                                                            | CSIDL                                                                                   |                                   |                         | VWORD<4:0      | >               |             |

| bit 15          |                                                                                                              |                                                                                         |                                   |                         |                |                 | bit 8       |

|                 |                                                                                                              |                                                                                         |                                   |                         |                |                 |             |

| R-0             | R-1                                                                                                          | U-0                                                                                     | R/W-0                             | R/W-0                   | R/W-0          | R/W-0           | R/W-0       |

| CRCFUL          | CRCMPT                                                                                                       | —                                                                                       | CRCGO                             |                         | PLEI           | N<3:0>          |             |

| bit 7           |                                                                                                              |                                                                                         |                                   |                         |                |                 | bit C       |

|                 |                                                                                                              |                                                                                         |                                   |                         |                |                 |             |

| Legend:         |                                                                                                              |                                                                                         |                                   |                         |                |                 |             |

| R = Readable    | bit                                                                                                          | W = Writable                                                                            | bit                               | U = Unimplem            | ented bit, rea | d as '0'        |             |

| -n = Value at F | POR                                                                                                          | '1' = Bit is set                                                                        |                                   | '0' = Bit is clea       | ired           | x = Bit is unkn | iown        |

|                 |                                                                                                              |                                                                                         |                                   |                         |                |                 |             |

| bit 15-14       | •                                                                                                            | ted: Read as '                                                                          |                                   |                         |                |                 |             |

| bit 13          |                                                                                                              | Stop in Idle Me                                                                         |                                   |                         |                |                 |             |

|                 |                                                                                                              |                                                                                         | eration when d<br>tion in Idle mo | evice enters Id         | e mode         |                 |             |

| bit 12-8        |                                                                                                              | Pointer Valu                                                                            |                                   |                         |                |                 |             |

|                 |                                                                                                              | number of vali<br>LEN<3:0> ≤7.                                                          | d words in the                    | FIFO. Has a m           | aximum value   | e of 8 when PLE | N<3:0> > 7, |

| bit 7           | CRCFUL: FIF                                                                                                  | O Full bit                                                                              |                                   |                         |                |                 |             |

|                 | 1 = FIFO is f                                                                                                | ull                                                                                     |                                   |                         |                |                 |             |

|                 | 0 = FIFO is n                                                                                                | ot full                                                                                 |                                   |                         |                |                 |             |

|                 |                                                                                                              |                                                                                         |                                   |                         |                |                 |             |

| bit 6           | CRCMPT: FIF                                                                                                  | O Empty Bit                                                                             |                                   |                         |                |                 |             |

| bit 6           | 1 = FIFO is e                                                                                                | empty                                                                                   |                                   |                         |                |                 |             |

|                 | 1 = FIFO is e<br>0 = FIFO is n                                                                               | empty<br>not empty                                                                      | o'                                |                         |                |                 |             |

| bit 5           | 1 = FIFO is e<br>0 = FIFO is n<br>Unimplemen                                                                 | empty<br>lot empty<br><b>ted:</b> Read as f                                             | 0'                                |                         |                |                 |             |

|                 | 1 = FIFO is e<br>0 = FIFO is n<br>Unimplemen<br>CRCGO: Star                                                  | empty<br>lot empty<br><b>ted:</b> Read as <sup>c</sup><br>t CRC bit                     | 0'                                |                         |                |                 |             |

| bit 5           | 1 = FIFO is e<br>0 = FIFO is n<br><b>Unimplemen</b><br><b>CRCGO:</b> Star<br>1 = Start CR0                   | empty<br>lot empty<br><b>ted:</b> Read as <sup>o</sup><br>t CRC bit<br>C serial shifter |                                   | e FIFO is emot          | /              |                 |             |

| bit 5           | 1 = FIFO is e<br>0 = FIFO is n<br><b>Unimplemen</b><br><b>CRCGO:</b> Star<br>1 = Start CRC<br>0 = Turn off t | empty<br>lot empty<br><b>ted:</b> Read as <sup>o</sup><br>t CRC bit<br>C serial shifter | shifter after the                 | e FIFO is empt <u>y</u> | 1              |                 |             |

# REGISTER 26-1: CRCCON: CRC CONTROL REGISTER

NOTES:

| Register 27-2:   | PMMODE: PARALLEL PORT MODE REGISTER                      |                                                                              |                                                    |                                              |                                                                                       |                                   |                      |  |  |

|------------------|----------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------|----------------------|--|--|

| R-0              | R/W-0                                                    | R/W-0                                                                        | R/W-0                                              | R/W-0                                        | R/W-0                                                                                 | R/W-0                             | R/W-0                |  |  |

| BUSY             | IRQ                                                      | M<1:0>                                                                       | INC                                                | N<1:0>                                       | MODE16                                                                                | MODE                              | =<1:0>               |  |  |

| bit 15           |                                                          |                                                                              |                                                    |                                              |                                                                                       |                                   | bit 8                |  |  |

| R/W-0            | R/W-0                                                    | R/W-0                                                                        | R/W-0                                              | R/W-0                                        | R/W-0                                                                                 | R/W-0                             | R/W-0                |  |  |

| WAITB<1          | :0> <sup>(1)</sup>                                       |                                                                              | WAI                                                | ГM<3:0>                                      |                                                                                       | WAITE                             | <1:0> <sup>(1)</sup> |  |  |

| bit 7            |                                                          |                                                                              |                                                    |                                              |                                                                                       |                                   | bit (                |  |  |

| Legend:          |                                                          |                                                                              |                                                    |                                              |                                                                                       |                                   |                      |  |  |

| R = Readable bit | :                                                        | W = Writable                                                                 | bit                                                | U = Unimple                                  | mented bit, read                                                                      | as '0'                            |                      |  |  |

| -n = Value at PO | R                                                        | '1' = Bit is se                                                              | t                                                  | '0' = Bit is cle                             | eared                                                                                 | x = Bit is unkr                   | nown                 |  |  |

| bit 15 E         | BUSY: Busv                                               | bit (Master mo                                                               | de onlv)                                           |                                              |                                                                                       |                                   |                      |  |  |

| 1                | -                                                        | usy (not useful                                                              | • ·                                                | cessor stall is a                            | active)                                                                               |                                   |                      |  |  |

| bit 14-13        | RQM<1:0>:                                                | Interrupt Requ                                                               | est Mode bits                                      |                                              |                                                                                       |                                   |                      |  |  |

| 1<br>0           | or on a<br>0 = No inte<br>1 = Interrup                   |                                                                              | peration when<br>l, processor si<br>the end of the | PMA<1:0> = :<br>all activated                | Write Buffer 3 is<br>11 (Addressable<br>cle                                           |                                   |                      |  |  |

| bit 12-11 II     | NCM<1:0>:                                                | Increment Mod                                                                | le bits                                            |                                              |                                                                                       |                                   |                      |  |  |

| 1<br>0           | 0 = Decren                                               | ad and write bu<br>nent ADDR<10:<br>ent ADDR<10:0<br>ement or decre          | 0> by 1 every<br>)> by 1 every                     | read/write cyc<br>read/write cycl            |                                                                                       | <i>y</i> )                        |                      |  |  |

| bit 10           | <b>/ODE16:</b> 8/                                        | 16-bit Mode bit                                                              |                                                    |                                              |                                                                                       |                                   |                      |  |  |

|                  |                                                          |                                                                              |                                                    |                                              | o the data registe<br>the data register                                               |                                   |                      |  |  |

| bit 9-8 N        | /ODE<1:0>                                                | : Parallel Port                                                              | Node Select b                                      | its                                          |                                                                                       |                                   |                      |  |  |

| 1<br>0           | 0 = Master                                               | mode 2 (PMCS<br>ced PSP, contro                                              | 61, PMRD <u>, PN</u><br>I signals (PM              | <u>IWR, PMBE, F</u><br>RD, PM <u>WR, P</u> I | PMBE, PMA <x:0<br>PMA<x:0> and P<br/>MCS1, PMD&lt;7:0<br/>, PMWR, PMCS</x:0></x:0<br> | MD<7:0>)<br><u>&gt;</u> and PMA<1 | :0>)                 |  |  |

| bit 7-6 V        | VAITB<1:0                                                | >: Data Setup to                                                             | Read/Write                                         | Wait State Con                               | figuration bits <sup>(1)</sup>                                                        |                                   |                      |  |  |

| 1<br>0           | 0 <b>= Data w</b><br>1 <b>= Data w</b>                   | ait of 4 Tcy; mu<br>ait of 3 Tcy; mu<br>ait of 2 Tcy; mu<br>ait of 1 Tcy; mu | Itiplexed addr<br>Itiplexed addr                   | ess phase of 3<br>ess phase of 2             | TCY<br>TCY                                                                            |                                   |                      |  |  |

| bit 5-2 V        | VAITM<3:0                                                | >: Read to Byte                                                              | Enable Strob                                       | e Wait State C                               | onfiguration bits                                                                     |                                   |                      |  |  |

| 1                | .111 <b>= Wait</b>                                       | of additional 1                                                              | 5 TCY                                              |                                              |                                                                                       |                                   |                      |  |  |

| •                |                                                          |                                                                              |                                                    |                                              |                                                                                       |                                   |                      |  |  |

|                  |                                                          | of additional 1<br>additional wait c                                         |                                                    | on forced into                               | one Tcy)                                                                              |                                   |                      |  |  |

|                  |                                                          | >: Data Hold Aff                                                             | • • • •                                            |                                              |                                                                                       |                                   |                      |  |  |

| 1<br>1<br>0      | 1 = Wait of<br>0 = Wait of<br>1 = Wait of<br>0 = Wait of | 4 Tcy<br>3 Tcy<br>2 Tcy                                                      |                                                    |                                              |                                                                                       |                                   |                      |  |  |

# Register 27-2: PMMODE: PARALLEL PORT MODE REGISTER

**Note 1:** WAITB and WAITE bits are ignored whenever WAITM3:WAITM0 = 0000.

# 31.1 DC Characteristics

# TABLE 31-1: OPERATING MIPS VS. VOLTAGE

|                |                         |                       | Max MIPS                                                                   |  |

|----------------|-------------------------|-----------------------|----------------------------------------------------------------------------|--|

| Characteristic | VDD Range<br>(in Volts) | Temp Range<br>(in °C) | dsPIC33FJ32MC302/304,<br>dsPIC33FJ64MCX02/X04 and<br>dsPIC33FJ128MCX02/X04 |  |

| _              | 3.0-3.6V <sup>(1)</sup> | -40°C to +85°C        | 40                                                                         |  |

|                | 3.0-3.6V <sup>(1)</sup> | -40°C to +125°C       | 40                                                                         |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 31-11 for the minimum and maximum BOR values.

### TABLE 31-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                    | Symbol | Min           | Тур         | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------|--------|---------------|-------------|------|------|

| Industrial Temperature Devices                                                                                            |        |               |             |      |      |

| Operating Junction Temperature Range                                                                                      | TJ     | -40           | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                                                       | TA     | -40           | —           | +85  | °C   |

| Extended Temperature Devices                                                                                              |        |               |             |      |      |

| Operating Junction Temperature Range                                                                                      | TJ     | -40           | —           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                       | TA     | -40           | —           | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation: | PD     | PINT + PI/O W |             |      | W    |

| $I/O = \Sigma (\{VDD - VOH\} \times IOH\} + \Sigma (VOL \times IOL)$                                                      |        |               |             |      |      |

| Maximum Allowed Power Dissipation                                                                                         | PDMAX  | (             | TJ – TA)/θJ | IA   | W    |

# TABLE 31-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур | Мах | Unit | Notes |

|------------------------------------------|--------|-----|-----|------|-------|

| Package Thermal Resistance, 44-pin QFN   | θja    | 30  | _   | °C/W | 1     |

| Package Thermal Resistance, 44-pin TFQP  | θја    | 40  | —   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SPDIP | θја    | 45  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SOIC  | θја    | 50  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin QFN-S | θја    | 30  | —   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| АС СНА       | RACTERIS | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |           |           |            |           |                                                  |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|------------|-----------|--------------------------------------------------|

| Param<br>No. | Symbol   | Characteristic                                                                                                                                                                                                                                                                          | Min       | Тур       | Max        | Units     | Conditions                                       |

|              |          | ADC Accuracy (10-bit Mode                                                                                                                                                                                                                                                               | e) – Meas | urement   | ts with e  | xternal   | VREF+/VREF-                                      |

| AD20b        | Nr       | Resolution <sup>(1)</sup>                                                                                                                                                                                                                                                               | 1(        | ) data bi | ts         | bits      |                                                  |

| AD21b        | INL      | Integral Nonlinearity                                                                                                                                                                                                                                                                   | -1.5      | _         | +1.5       | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| AD22b        | DNL      | Differential Nonlinearity                                                                                                                                                                                                                                                               | >-1       | —         | <1         | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| AD23b        | Gerr     | Gain Error                                                                                                                                                                                                                                                                              | —         | 3         | 6          | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| AD24b        | EOFF     | Offset Error                                                                                                                                                                                                                                                                            | —         | 2         | 5          | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| AD25b        | —        | Monotonicity                                                                                                                                                                                                                                                                            | _         |           |            | —         | Guaranteed                                       |

|              |          | ADC Accuracy (10-bit Mode                                                                                                                                                                                                                                                               | e) – Meas | uremen    | ts with ir | nternal V | VREF+/VREF-                                      |

| AD20b        | Nr       | Resolution <sup>(1)</sup>                                                                                                                                                                                                                                                               | 1(        | 0 data bi | ts         | bits      |                                                  |

| AD21b        | INL      | Integral Nonlinearity                                                                                                                                                                                                                                                                   | -1        | —         | +1         | LSb       | VINL = AVSS = 0V, AVDD = 3.6V                    |

| AD22b        | DNL      | Differential Nonlinearity                                                                                                                                                                                                                                                               | >-1       | _         | <1         | LSb       | VINL = AVSS = 0V, AVDD = 3.6V                    |

| AD23b        | Gerr     | Gain Error                                                                                                                                                                                                                                                                              | 3         | 7         | 15         | LSb       | VINL = AVSS = 0V, AVDD = 3.6V                    |

| AD24b        | EOFF     | Offset Error                                                                                                                                                                                                                                                                            | 1.5       | 3         | 7          | LSb       | VINL = AVSS = 0V, AVDD = 3.6V                    |

| AD25b        | —        | Monotonicity                                                                                                                                                                                                                                                                            | —         |           | _          | —         | Guaranteed                                       |

|              |          | Dynamic                                                                                                                                                                                                                                                                                 | Performa  | nce (10-  | bit Mode   | e)        |                                                  |

| AD30b        | THD      | Total Harmonic Distortion                                                                                                                                                                                                                                                               |           |           | -64        | dB        | _                                                |

| AD31b        | SINAD    | Signal to Noise and Distortion                                                                                                                                                                                                                                                          | 57        | 58.5      |            | dB        |                                                  |

| AD32b        | SFDR     | Spurious Free Dynamic<br>Range                                                                                                                                                                                                                                                          | 72        | _         |            | dB        | _                                                |