Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20 MIPS                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc802-h-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup><br>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | RA: REPEAT Loop Active bit<br>1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | N: MCU ALU Negative bit<br>1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 2   | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (two's complement). It indicates an overflow of a magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                  |

| bit 1   | <ul> <li>Z: MCU ALU Zero bit</li> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                       |

| bit 0   | <b>C</b> : MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                      |

- Note 1: This bit can be read or cleared (not set).

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: This bit can be read or cleared (not set). Clearing this bit clears SA and SB.

### 3.7 Arithmetic Logic Unit (ALU)

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register. The C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.7.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- · 8-bit unsigned x 8-bit unsigned

### 3.7.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.8 DSP Engine

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- · Fractional or integer DSP multiply (IF)

- Signed or unsigned DSP multiply (US)

- Conventional or convergent rounding (RND)

- Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

A block diagram of the DSP engine is shown in Figure 3-3.

| TABLE 3-1: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

| Algebraic ACC Write |                         |      |  |  |  |  |  |

|---------------------|-------------------------|------|--|--|--|--|--|

| Instruction         | Algebraic<br>Operation  | Back |  |  |  |  |  |

| CLR                 | A = 0                   | Yes  |  |  |  |  |  |

| ED                  | $A = (x - y)^2$         | No   |  |  |  |  |  |

| EDAC                | $A = A + (x - y)^2$     | No   |  |  |  |  |  |

| MAC                 | $A = A + (x \bullet y)$ | Yes  |  |  |  |  |  |

| MAC                 | A = A + x2              | No   |  |  |  |  |  |

| MOVSAC              | No change in A          | Yes  |  |  |  |  |  |

| MPY                 | $A = x \bullet y$       | No   |  |  |  |  |  |

| MPY                 | A = x 2                 | No   |  |  |  |  |  |

| MPY.N               | $A = -x \bullet y$      | No   |  |  |  |  |  |

| MSC                 | $A = A - x \bullet y$   | Yes  |  |  |  |  |  |

#### 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All effective addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

#### 4.2.6 DMA RAM

Every dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 device contains up to 2 Kbytes of dual ported DMA RAM located at the end of Y data space, and is a part of Y data space. Memory locations in the DMA RAM space are accessible simultaneously by the CPU and the DMA controller module. The DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU.

When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

Note: The DMA RAM can be used for general purpose data storage if the DMA function is not required in an application.

### 4.3 Memory Resources

Many useful resources related to Memory Organization are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

### 4.3.1 KEY RESOURCES

- Section 4. "Program Memory" (DS70203)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

## REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit                                           |

|-------|-----------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit                                            |

|       | <ol> <li>Interrupt request has occurred</li> </ol>                                                  |

|       | 0 = Interrupt request has not occurred                                                              |

| bit 0 | INT0IF: External Interrupt 0 Flag Status bit                                                        |

|       | 1 = Interrupt request has occurred                                                                  |

0 = Interrupt request has not occurred

| REGISTER     | 7-7: IFS2:                                                                                                                                                    | NTERRUPT                                                                                           | FLAG STAT       | US REGISTI          | ER 2                  |                |         |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------|---------------------|-----------------------|----------------|---------|--|--|

| U-0          | R/W-0                                                                                                                                                         | R/W-0                                                                                              | U-0             | U-0                 | U-0                   | U-0            | U-0     |  |  |

|              | DMA4IF                                                                                                                                                        | PMPIF                                                                                              |                 | —                   |                       | _              | _       |  |  |

| bit 15       |                                                                                                                                                               |                                                                                                    |                 |                     |                       |                | bit     |  |  |

| U-0          | U-0                                                                                                                                                           | U-0                                                                                                | R/W-0           | R/W-0               | R/W-0                 | R/W-0          | R/W-0   |  |  |

|              | _                                                                                                                                                             | _                                                                                                  | DMA3IF          | C1IF <sup>(1)</sup> | C1RXIF <sup>(1)</sup> | SPI2IF         | SPI2EIF |  |  |

| bit 7        |                                                                                                                                                               |                                                                                                    |                 |                     |                       |                | bit     |  |  |

| Legend:      |                                                                                                                                                               |                                                                                                    |                 |                     |                       |                |         |  |  |

| R = Readab   | le bit                                                                                                                                                        | W = Writable                                                                                       | bit             | U = Unimplei        | mented bit, read      | as '0'         |         |  |  |

| -n = Value a | t POR                                                                                                                                                         | '1' = Bit is se                                                                                    | t               | '0' = Bit is cle    | eared                 | x = Bit is unk | nown    |  |  |

| bit 14       | <b>DMA4IF:</b> DMA Channel 4 Data Transfer Complete Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred |                                                                                                    |                 |                     |                       |                |         |  |  |

|              | •                                                                                                                                                             | •                                                                                                  |                 |                     |                       |                |         |  |  |

| bit 13       |                                                                                                                                                               | <b>PMPIF:</b> Parallel Master Port Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                 |                     |                       |                |         |  |  |

|              |                                                                                                                                                               | request has oc                                                                                     |                 |                     |                       |                |         |  |  |

| bit 12-5     | Unimplemented: Read as '0'                                                                                                                                    |                                                                                                    |                 |                     |                       |                |         |  |  |

| bit 4        | DMA3IF: DM                                                                                                                                                    | A Channel 3 E                                                                                      | Data Transfer C | Complete Interr     | rupt Flag Status I    | oit            |         |  |  |

|              | 1 = Interrupt request has occurred                                                                                                                            |                                                                                                    |                 |                     |                       |                |         |  |  |

|              | •                                                                                                                                                             | request has no                                                                                     |                 | (4)                 |                       |                |         |  |  |

| bit 3        |                                                                                                                                                               |                                                                                                    | pt Flag Status  | bit <sup>(1)</sup>  |                       |                |         |  |  |

|              |                                                                                                                                                               | request has ou<br>request has no                                                                   |                 |                     |                       |                |         |  |  |

| bit 2        | •                                                                                                                                                             | •                                                                                                  |                 | errupt Flag Sta     | itus bit(1)           |                |         |  |  |

| 5112         | <b>C1RXIF:</b> ECAN1 Receive Data Ready Interrupt Flag Status bit <sup>(1)</sup><br>1 = Interrupt request has occurred                                        |                                                                                                    |                 |                     |                       |                |         |  |  |

|              |                                                                                                                                                               | request has no                                                                                     |                 |                     |                       |                |         |  |  |

| bit 1        | SPI2IF: SPI2 Event Interrupt Flag Status bit                                                                                                                  |                                                                                                    |                 |                     |                       |                |         |  |  |

|              | 1 = Interrupt request has occurred                                                                                                                            |                                                                                                    |                 |                     |                       |                |         |  |  |

| <b>h</b> # 0 | •                                                                                                                                                             | request has no                                                                                     |                 | L:4                 |                       |                |         |  |  |

| bit 0        | SPI2EIF: SPI2 Error Interrupt Flag Status bit<br>1 = Interrupt request has occurred                                                                           |                                                                                                    |                 |                     |                       |                |         |  |  |

|              |                                                                                                                                                               | request has oc                                                                                     |                 |                     |                       |                |         |  |  |

|              |                                                                                                                                                               |                                                                                                    |                 |                     |                       |                |         |  |  |

## REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

Note 1: Interrupts are disabled on devices without an ECAN<sup>™</sup> module.

| R/W-0                  | R/W-0                                                                                                  | U-0                             | U-0              | R/W-0                        | R/W-0                     | R/W-0            | U-0 |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------|------------------|------------------------------|---------------------------|------------------|-----|--|--|

| DAC1LIF <sup>(2)</sup> | DAC1RIF <sup>(2)</sup>                                                                                 | _                               | —                | QEI2IF                       | FLTA2IF                   | PWM2IF           | —   |  |  |

| bit 15                 |                                                                                                        |                                 |                  |                              |                           |                  | bit |  |  |

| U-0                    | R/W-0                                                                                                  | R/W-0                           | R/W-0            | R/W-0                        | R/W-0                     | R/W-0            | U-0 |  |  |

|                        | C1TXIF <sup>(1)</sup>                                                                                  | DMA7IF                          | DMA6IF           | CRCIF                        | U2EIF                     | U1EIF            |     |  |  |

| bit 7                  |                                                                                                        |                                 |                  |                              |                           |                  | bit |  |  |

| Legend:                |                                                                                                        |                                 |                  |                              |                           |                  |     |  |  |

| R = Readable           | bit                                                                                                    | W = Writable                    | bit              | U = Unimple                  | mented bit, read          | d as '0'         |     |  |  |

| -n = Value at F        | POR                                                                                                    | '1' = Bit is set                |                  | '0' = Bit is cle             | eared                     | x = Bit is unkno | own |  |  |

| bit 15                 | DAC1LIF: DA                                                                                            | C Left Channe                   | el Interrupt Fla | g Status bit <sup>(2)</sup>  |                           |                  |     |  |  |

|                        | 1 = Interrupt r                                                                                        | equest has oc                   | curred           |                              |                           |                  |     |  |  |

|                        |                                                                                                        | equest has not                  |                  |                              |                           |                  |     |  |  |

| bit 14                 |                                                                                                        | C Right Chan                    | •                | lag Status bit <sup>(2</sup> | 2)                        |                  |     |  |  |

|                        |                                                                                                        | equest has oc<br>equest has not |                  |                              |                           |                  |     |  |  |

| bit 13-12              |                                                                                                        | ted: Read as '                  |                  |                              |                           |                  |     |  |  |

| bit 11                 | •                                                                                                      |                                 |                  | bit                          |                           |                  |     |  |  |

|                        | <b>QEI2IF:</b> QEI2 Event Interrupt Flag Status bit<br>1 = Interrupt request has occurred              |                                 |                  |                              |                           |                  |     |  |  |

|                        | 0 = Interrupt r                                                                                        | equest has not                  | t occurred       |                              |                           |                  |     |  |  |

| bit 10                 | FLTA2IF: PWM2 Fault A Interrupt Flag Status bit                                                        |                                 |                  |                              |                           |                  |     |  |  |

|                        | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                 |                  |                              |                           |                  |     |  |  |

|                        |                                                                                                        | •                               |                  |                              |                           |                  |     |  |  |

| bit 9                  |                                                                                                        | M2 Error Inter                  | •                | t                            |                           |                  |     |  |  |

|                        |                                                                                                        | equest has oc<br>equest has not |                  |                              |                           |                  |     |  |  |

| bit 8-7                |                                                                                                        | ted: Read as '                  |                  |                              |                           |                  |     |  |  |

| bit 6                  | -                                                                                                      | N1 Transmit D                   |                  | nterrupt Flag S              | Status bit <sup>(1)</sup> |                  |     |  |  |

|                        | 1 = Interrupt r                                                                                        | equest has oc<br>equest has no  | curred           |                              |                           |                  |     |  |  |

| bit 5                  |                                                                                                        | •                               |                  | `omolete Interi              | rupt Flag Status          | bit              |     |  |  |

| bit 5                  | 1 = Interrupt r                                                                                        | equest has oc                   | curred           |                              | lupt i lag Status         | DI               |     |  |  |

|                        | -                                                                                                      | equest has not                  |                  |                              |                           |                  |     |  |  |

| bit 4                  | DMA6IF: DMA Channel 6 Data Transfer Complete Interrupt Flag Status bit                                 |                                 |                  |                              |                           |                  |     |  |  |

|                        | 1 = Interrupt request has occurred                                                                     |                                 |                  |                              |                           |                  |     |  |  |

| bit 3                  | 0 = Interrupt request has not occurred                                                                 |                                 |                  |                              |                           |                  |     |  |  |

| bit 0                  | <b>CRCIF:</b> CRC Generator Interrupt Flag Status bit<br>1 = Interrupt request has occurred            |                                 |                  |                              |                           |                  |     |  |  |

|                        |                                                                                                        | equest has not                  |                  |                              |                           |                  |     |  |  |

| bit 2                  | U2EIF: UART                                                                                            | 2 Error Interru                 | pt Flag Status   | bit                          |                           |                  |     |  |  |

|                        | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                 |                  |                              |                           |                  |     |  |  |

| bit 1                  | -                                                                                                      | 1 Error Interru                 |                  | bit                          |                           |                  |     |  |  |

|                        |                                                                                                        |                                 | -                |                              |                           |                  |     |  |  |

|                        | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                 |                  |                              |                           |                  |     |  |  |

| bit 0                  | Unimplement                                                                                            | ted: Read as '                  | 0'               |                              |                           |                  |     |  |  |

|                        |                                                                                                        |                                 |                  |                              |                           |                  |     |  |  |

| Note 1: Inte           | errupts are disat                                                                                      | plea on devices                 | s without an E   | :∪AN '‴ modul                | e.                        |                  |     |  |  |

### REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

**Note 1:** Interrupts are disabled on devices without an ECAN<sup>™</sup> module.

2: Interrupts are disabled on devices without an Audio DAC module.

| Oscillator Mode                                    | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Note |

|----------------------------------------------------|-------------------|-------------|------------|-------------|

| Fast RC Oscillator with Divide-by-N<br>(FRCDIVN)   | Internal          | XX          | 111        | 1, 2        |

| Fast RC Oscillator with Divide-by-16<br>(FRCDIV16) | Internal          | XX          | 110        | 1           |

| Low-Power RC Oscillator (LPRC)                     | Internal          | XX          | 101        | 1           |

| Secondary (Timer1) Oscillator (Sosc)               | Secondary         | XX          | 100        | 1           |

| Primary Oscillator (HS) with PLL<br>(HSPLL)        | Primary           | 10          | 011        | -           |

| Primary Oscillator (XT) with PLL<br>(XTPLL)        | Primary           | 01          | 011        | -           |

| Primary Oscillator (EC) with PLL<br>(ECPLL)        | Primary           | 00          | 011        | 1           |

| Primary Oscillator (HS)                            | Primary           | 10          | 010        | _           |

| Primary Oscillator (XT)                            | Primary           | 01          | 010        | -           |

| Primary Oscillator (EC)                            | Primary           | 00          | 010        | 1           |

| Fast RC Oscillator with PLL (FRCPLL)               | Internal          | XX          | 001        | 1           |

| Fast RC Oscillator (FRC)                           | Internal          | XX          | 000        | 1           |

**Note 1:** OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

### 9.2 Oscillator Resources

Many useful resources related to Oscillator Configuration are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532315              |

### 9.2.1 KEY RESOURCES

- Section 39. "Oscillator (Part III)" (DS70216)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# 9.3 Oscillator Control Registers

| U-0        | R-0                  | R-0                                                                                                                                                                                                                                                                       | R-0           | U-0               | R/W-y            | R/W-y                       | R/W-y      |  |

|------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|------------------|-----------------------------|------------|--|

|            |                      | COSC<2:0>                                                                                                                                                                                                                                                                 |               |                   |                  | NOSC<2:0> <sup>(2)</sup>    |            |  |

| bit 15     |                      |                                                                                                                                                                                                                                                                           |               |                   |                  |                             | bit 8      |  |

| R/W-0      | ) R/W-0              | R-0                                                                                                                                                                                                                                                                       | U-0           | R/C-0             | U-0              | R/W-0                       | R/W-0      |  |

| CLKLO      |                      | LOCK                                                                                                                                                                                                                                                                      | 0-0           | CF                | 0-0              | LPOSCEN                     | OSWEN      |  |

| bit 7      |                      | LOOK                                                                                                                                                                                                                                                                      |               |                   |                  |                             | bit 0      |  |

|            |                      |                                                                                                                                                                                                                                                                           |               |                   |                  |                             |            |  |

| Legend:    |                      | C = Clear only bit y = Value set from Configuration bits on POR                                                                                                                                                                                                           |               |                   |                  |                             |            |  |

| R = Read   | able bit             | W = Writable                                                                                                                                                                                                                                                              | oit           | U = Unimple       | mented bit, rea  | d as '0'                    |            |  |

| -n = Value | e at POR             | '1' = Bit is set                                                                                                                                                                                                                                                          |               | '0' = Bit is cle  | ared             | x = Bit is unkno            | own        |  |

| bit 15     | Unimplomor           | ted: Dood oo '                                                                                                                                                                                                                                                            | `,            |                   |                  |                             |            |  |

| bit 14-12  | -                    | nted: Read as '                                                                                                                                                                                                                                                           |               | hite (road only   | )                |                             |            |  |

| DIL 14-12  |                      | Current Oscilla<br>C (FRC) oscilla                                                                                                                                                                                                                                        |               |                   | )                |                             |            |  |

|            |                      | C (FRC) oscilla                                                                                                                                                                                                                                                           |               |                   |                  |                             |            |  |

|            |                      | ower RC (LPR                                                                                                                                                                                                                                                              |               |                   |                  |                             |            |  |

|            |                      | dary Oscillator                                                                                                                                                                                                                                                           |               |                   |                  |                             |            |  |

|            |                      | y oscillator (XT,                                                                                                                                                                                                                                                         |               | PLL               |                  |                             |            |  |

|            |                      | y oscillator (XT,                                                                                                                                                                                                                                                         |               | -by-N and PL      | (FRCDIVN +       | PLL)                        |            |  |

|            |                      | 001 = Fast RC (FRC) oscillator with divide-by-N and PLL (FRCDIVN + PLL)<br>000 = Fast RC (FRC) oscillator                                                                                                                                                                 |               |                   |                  |                             |            |  |

| bit 11     | Unimplemer           | ted: Read as '                                                                                                                                                                                                                                                            | )'            |                   |                  |                             |            |  |

| bit 10-8   | NOSC<2:0>:           | NOSC<2:0>: New Oscillator Selection bits <sup>(2)</sup>                                                                                                                                                                                                                   |               |                   |                  |                             |            |  |

|            |                      | C (FRC) oscilla                                                                                                                                                                                                                                                           |               |                   |                  |                             |            |  |

|            |                      | C (FRC) oscilla                                                                                                                                                                                                                                                           |               | e-by-16           |                  |                             |            |  |

|            |                      | ower RC (LPRC<br>dary Oscillator                                                                                                                                                                                                                                          | ·             |                   |                  |                             |            |  |

|            |                      | y oscillator (XT,                                                                                                                                                                                                                                                         |               | PLL               |                  |                             |            |  |

|            |                      | y oscillator (XT,                                                                                                                                                                                                                                                         |               |                   |                  |                             |            |  |

|            |                      | C (FRC) oscilla                                                                                                                                                                                                                                                           |               | e-by-N and PL     | L (FRCDIVN +     | PLL)                        |            |  |

| bit 7      |                      | 000 = Fast RC (FRC) oscillator<br>CLKLOCK: Clock Lock Enable bit                                                                                                                                                                                                          |               |                   |                  |                             |            |  |

|            | -                    |                                                                                                                                                                                                                                                                           |               | disabled (FCI     | (SM<1:0> (FO     | SC<7:6>) = 0b0 <sup>-</sup> | 1)         |  |

|            |                      | itching is disab                                                                                                                                                                                                                                                          |               |                   |                  | 00 1.0 / 0.00               | <u>· /</u> |  |

|            | 0 = Clock sv         | vitching is enabl                                                                                                                                                                                                                                                         | ed, system cl | ock source ca     | n be modified b  | y clock switching           | 9          |  |

| bit 6      |                      | ripheral Pin Sel                                                                                                                                                                                                                                                          |               |                   |                  |                             |            |  |

|            | •                    | ial pin select is                                                                                                                                                                                                                                                         |               |                   | •                |                             |            |  |

| hit 5      | -                    | ial pin select is<br>₋ock Status bit (                                                                                                                                                                                                                                    |               | nte to peripher   | ai pin select re | gisters allowed             |            |  |

| bit 5      |                      | s that PLL is in I                                                                                                                                                                                                                                                        | • /           | tart-un timer is  | satisfied        |                             |            |  |

|            |                      | s that PLL is out                                                                                                                                                                                                                                                         |               |                   |                  | L is disabled               |            |  |

| bit 4      | Unimplemer           | nted: Read as '                                                                                                                                                                                                                                                           | )'            |                   |                  |                             |            |  |

| Note 1:    | Writes to this regis |                                                                                                                                                                                                                                                                           |               |                   |                  |                             |            |  |

| •          | in the "dsPIC33F/    | -                                                                                                                                                                                                                                                                         |               |                   |                  |                             |            |  |

| 2:         | This applies to clo  | ect clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted.<br>applies to clock switches in either direction. In these instances, the application must switch to FRC<br>de as a transition clock source between the two PLL modes. |               |                   |                  |                             |            |  |

| 3:         | This register is res |                                                                                                                                                                                                                                                                           |               |                   | :5.              |                             |            |  |

| 5.         | THIS TEGISLET IS LES | ber only on a Po                                                                                                                                                                                                                                                          | wei-on Resel  | $(1^{\circ}OR)$ . |                  |                             |            |  |

**REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

© 2007-2012 Microchip Technology Inc.

#### 11.6 Peripheral Pin Select

Peripheral pin select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral pin select is performed in software, and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

#### 11.6.1 AVAILABLE PINS

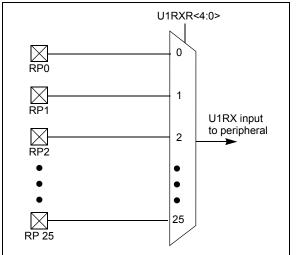

The peripheral pin select feature is used with a range of up to 26 pins. The number of available pins depends on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation RPn in their full pin designation, where RP designates a remappable peripheral and n is the remappable pin number.

#### 11.6.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of special function registers: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 11.6.2.1 Input Mapping

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it is mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-20). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of peripheral pin selections supported by the device.

Figure 11-2 Illustrates remappable pin selection for U1RX input.

| Note: | For input mapping only, the Peripheral Pin |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | Select (PPS) functionality does not have   |  |  |  |  |  |

|       | priority over the TRISx settings.          |  |  |  |  |  |

|       | Therefore, when configuring the RPx pin    |  |  |  |  |  |

|       | for input, the corresponding bit in the    |  |  |  |  |  |

|       | TRISx register must also be configured for |  |  |  |  |  |

|       | input (i.e., set to '1').                  |  |  |  |  |  |

#### FIGURE 11-2: REMAPPABLE MUX INPUT FOR U1RX

| REGISTER 16-2: PxT | MR: PWM TIMER COUNT VALUE REGISTER |

|--------------------|------------------------------------|

|--------------------|------------------------------------|

| R-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| PTDIR           |       |                  |       | PTMR<14:8>       | •               |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PTM   | R<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, rea | ad as '0'       |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

| bit 15   | PTDIR: PWM Time Base Count Direction Status bit (read-only) |

|----------|-------------------------------------------------------------|

|          | 1 = PWM time base is counting down                          |

|          | 0 = PWM time base is counting up                            |

| bit 14-0 | PTMR<14:0>: PWM Time Base Register Count Value bits         |

### REGISTER 16-3: PxTPER: PWM TIME BASE PERIOD REGISTER

| U-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| _               |       |                  |       | PTPER<14:8       | >               |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PTPE  | ER<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

| -n = Value at P | POR   | '1' = Bit is set |       | -                |                 |                 | nown  |

bit 15 Unimplemented: Read as '0'

bit 14-0 **PTPER<14:0>:** PWM Time Base Period Value bits

#### **REGISTER 16-7: PxDTCON1: DEAD-TIME CONTROL REGISTER 1**

| R/W-0                                           | R/W-0                                                              | R/W-0                  | R/W-0           | R/W-0            | R/W-0                             | R/W-0    | R/W-0   |  |

|-------------------------------------------------|--------------------------------------------------------------------|------------------------|-----------------|------------------|-----------------------------------|----------|---------|--|

|                                                 | PS<1:0>                                                            | 1000-0                 | 10,00-0         |                  | 3<5:0>                            | 10,00-0  | 10,00-0 |  |

| bit 15                                          | F371.02                                                            |                        |                 | DIE              | 5-5.02                            |          | hit 9   |  |

|                                                 |                                                                    |                        |                 |                  |                                   |          | bit 8   |  |

| R/W-0                                           | R/W-0                                                              | R/W-0                  | R/W-0           | R/W-0            | R/W-0                             | R/W-0    | R/W-0   |  |

| DTA                                             | PS<1:0>                                                            |                        |                 | DTA              | <5:0>                             |          |         |  |

| bit 7                                           |                                                                    | 1                      |                 |                  |                                   |          | bit 0   |  |

|                                                 |                                                                    |                        |                 |                  |                                   |          |         |  |

| Legend:                                         |                                                                    |                        |                 |                  |                                   |          |         |  |

| R = Readab                                      | le bit                                                             | W = Writable           | bit             | U = Unimpler     | nented bit, read                  | l as '0' |         |  |

| -n = Value a                                    | t POR                                                              | '1' = Bit is set '0' = |                 | '0' = Bit is cle | '0' = Bit is cleared x = Bit is u |          | unknown |  |

|                                                 |                                                                    |                        |                 |                  |                                   |          |         |  |

| bit 15-14                                       | DTBPS<1:0                                                          | >: Dead-Time U         | Init B Prescale | e Select bits    |                                   |          |         |  |

|                                                 | 11 = Clock                                                         | period for Dead-       | Time Unit B is  | 8 TCY            |                                   |          |         |  |

|                                                 |                                                                    | period for Dead-       |                 |                  |                                   |          |         |  |

|                                                 |                                                                    | period for Dead-       |                 |                  |                                   |          |         |  |

|                                                 | 00 = Clock period for Dead-Time Unit B is TCY                      |                        |                 |                  |                                   |          |         |  |

| bit 13-8                                        | DTB<5:0>: Unsigned 6-bit Dead-Time Value for Dead-Time Unit B bits |                        |                 |                  |                                   |          |         |  |

| bit 7-6                                         | DTAPS<1:0>: Dead-Time Unit A Prescale Select bits                  |                        |                 |                  |                                   |          |         |  |

|                                                 | 11 = Clock period for Dead-Time Unit A is 8 TCY                    |                        |                 |                  |                                   |          |         |  |

| 10 = Clock period for Dead-Time Unit A is 4 Tcy |                                                                    |                        |                 |                  |                                   |          |         |  |

|                                                 | 01 = Clock                                                         | period for Dead-       | Time Unit A is  | S 2 TCY          |                                   |          |         |  |

|                                                 | 00 = Clock                                                         | period for Dead-       | Time Unit A is  | з Тсү            |                                   |          |         |  |

bit 5-0 DTA<5:0>: Unsigned 6-bit Dead-Time Value for Dead-Time Unit A bits

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| REGISTER 1        | 6-8: PXDIC   | ON2: DEAD        | -TIME CON  | IROL REGIS       | IER 2(")         |                 |       |

|-------------------|--------------|------------------|------------|------------------|------------------|-----------------|-------|

| U-0               | U-0          | U-0              | U-0        | U-0              | U-0              | U-0             | U-0   |

|                   | —            | —                | —          | —                | —                | —               | —     |

| bit 15            |              |                  |            |                  |                  |                 | bit 8 |

| U-0               | U-0          | R/W-0            | R/W-0      | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| —                 |              | DTS3A            | DTS3I      | DTS2A            | DTS2I            | DTS1A           | DTS1I |

| bit 7             |              | I                | 1          | -                |                  |                 | bit 0 |

|                   |              |                  |            |                  |                  |                 |       |

| Legend:           |              |                  |            |                  |                  |                 |       |

| R = Readable      | bit          | W = Writable     | bit        | U = Unimplen     | nented bit, read | d as '0'        |       |

| -n = Value at F   | POR          | '1' = Bit is set |            | '0' = Bit is cle | ared             | x = Bit is unkr | iown  |

| bit 15-6<br>bit 5 |              |                  |            |                  |                  |                 |       |

| bit 4             | DTS3I: Dead- | Time Select fo   | r PWMxL3 S | gnal Going Ina   | ctive bit        |                 |       |

|                   |              |                  |            |                  |                  |                 |       |

# REGISTER 16-8: PxDTCON2: DEAD-TIME CONTROL REGISTER 2<sup>(1)</sup>

| bit 4 | <b>DTS3I:</b> Dead-Time Select for PWMxL3 Signal Going Inactive bit<br>1 = Dead time provided from Unit B<br>0 = Dead time provided from Unit A |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3 | <b>DTS2A:</b> Dead-Time Select for PWMxH2 Signal Going Active bit<br>1 = Dead time provided from Unit B<br>0 = Dead time provided from Unit A   |

| bit 2 | <b>DTS2I:</b> Dead-Time Select for PWMxL2 Signal Going Inactive bit<br>1 = Dead time provided from Unit B<br>0 = Dead time provided from Unit A |

| bit 1 | <b>DTS1A:</b> Dead-Time Select for PWMxH1 Signal Going Active bit<br>1 = Dead time provided from Unit B<br>0 = Dead time provided from Unit A   |

| bit 0 | <b>DTS1I:</b> Dead-Time Select for PWMxL1 Signal Going Inactive bit<br>1 = Dead time provided from Unit B<br>0 = Dead time provided from Unit A |

Note 1: PWM2 supports only one PWM I/O pin pair.

#### REGISTER 20-1: UxMODE: UARTx MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <ul> <li>BRGH: High Baud Rate Enable bit</li> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                                                       |

| bit 0   | <b>STSEL:</b> Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                               |

- **Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

|              | n (n =                                                                                                                                                                                                     | 0-15)                                                                                                                                          |             |                  |                 |                 |       |