#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20 MIPS                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc802-h-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

#### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table**".

| msw<br>Address | most significant we                               |          | east significant wo | rd PC Address<br>(Isw Address) |

|----------------|---------------------------------------------------|----------|---------------------|--------------------------------|

|                | 23                                                | 16       | 8                   | 0                              |

| 0x000001       | 0000000                                           |          |                     | 0x000000                       |

| 0x000003       | 0000000                                           |          |                     | 0x000002                       |

| 0x000005       | 0000000                                           |          |                     | 0x000004                       |

| 0x000007       | 0000000                                           |          |                     | 0x000006                       |

|                |                                                   |          | ~                   |                                |

|                | Program Memory<br>'Phantom' Byte<br>(read as '0') | Instruct | ion Width           |                                |

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

# TABLE 4-27: PARALLEL MASTER/SLAVE PORT REGISTER MAP FOR dsPIC33FJ128MC202/802, dsPIC33FJ64MC202/802 AND dsPIC33FJ32MC302

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9          | Bit 8       | Bit 7         | Bit 6       | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|---------|--------|----------------|-------------|---------------|-------------|-------|-------|--------|-------|-------|--------|---------------|

| PMCON     | 0600 | PMPEN  | _      | PSIDL  | ADRMU  | IX<1:0> | PTBEEN | PTWREN         | PTRDEN      | CSF1          | CSF0        | ALP   | —     | CS1P   | BEP   | WRSP  | RDSP   | 0000          |

| PMMODE    | 0602 | BUSY   | IRQM   | <1:0>  | INCM   | <1:0>   | MODE16 | MODE           | <1:0>       | WAITE         | 3<1:0>      |       | WAITM | /<3:0> |       | WAITE | E<1:0> | 0000          |

| PMADDR    | 0604 | ADDR15 | CS1    |        |        |         |        |                |             | ADDR<         | 13:0>       |       |       |        |       |       |        | 0000          |

| PMDOUT1   |      |        |        |        |        |         | Pa     | rallel Port D  | ata Out Reg | gister 1 (But | ffers 0 and | 1)    |       |        |       |       |        | 0000          |

| PMDOUT2   | 0606 |        |        |        |        |         | Pa     | rallel Port D  | ata Out Re  | gister 2 (But | ffers 2 and | 3)    |       |        |       |       |        | 0000          |

| PMDIN1    | 0608 |        |        |        |        |         | Pa     | arallel Port I | Data In Reg | ister 1 (Buff | ers 0 and 1 | )     |       |        |       |       |        | 0000          |

| PMPDIN2   | 060A |        |        |        |        |         | Pa     | arallel Port I | Data In Reg | ister 2 (Buff | ers 2 and 3 | )     |       |        |       |       |        | 0000          |

| PMAEN     | 060C | _      | PTEN14 | _      | _      | _       | _      | _              | _           | _             | _           | _     | _     | _      | _     | PTEN  | <1:0>  | 0000          |

| PMSTAT    | 060E | IBF    | IBOV   | _      | _      | IB3F    | IB2F   | IB1F           | IB0F        | OBE           | OBUF        | -     | _     | OB3E   | OB2E  | OB1E  | OB0E   | 008F          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-28: PARALLEL MASTER/SLAVE PORT REGISTER MAP FOR dsPIC33FJ128MC204/804, dsPIC33FJ64MC204/804 AND dsPIC33FJ32MC304

|           |      |        |        |        |        |         | 1      |                |              |              |             |           |       |        |       |       |        |               |

|-----------|------|--------|--------|--------|--------|---------|--------|----------------|--------------|--------------|-------------|-----------|-------|--------|-------|-------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9          | Bit 8        | Bit 7        | Bit 6       | Bit 5     | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

| PMCON     | 0600 | PMPEN  | —      | PSIDL  | ADRMU  | JX<1:0> | PTBEEN | PTWREN         | PTRDEN       | CSF1         | CSF0        | ALP       | —     | CS1P   | BEP   | WRSP  | RDSP   | 0000          |

| PMMODE    | 0602 | BUSY   | IRQM   | <1:0>  | INCM   | <1:0>   | MODE16 | MODE           | =<1:0>       | WAITE        | 3<1:0>      |           | WAITM | /<3:0> |       | WAITE | =<1:0> | 0000          |

| PMADDR    | 0604 | ADDR15 | CS1    |        |        |         |        |                |              | ADDR<        | 13:0>       |           |       |        |       |       |        | 0000          |

| PMDOUT1   |      |        |        |        |        |         | Pa     | rallel Port D  | ata Out Reg  | ister 1 (Bu  | ffers 0 and | 1)        |       |        |       |       |        | 0000          |

| PMDOUT2   | 0606 |        |        |        |        |         | Pa     | rallel Port D  | ata Out Reg  | ister 2 (Bu  | ffers 2 and | 3)        |       |        |       |       |        | 0000          |

| PMDIN1    | 0608 |        |        |        |        |         | Pa     | arallel Port I | Data In Regi | ster 1 (Buff | ers 0 and 1 | )         |       |        |       |       |        | 0000          |

| PMPDIN2   | 060A |        |        |        |        |         | Pa     | arallel Port I | Data In Regi | ster 2 (Buff | ers 2 and 3 | 5)        |       |        |       |       |        | 0000          |

| PMAEN     | 060C | _      | PTEN14 | —      | _      |         |        |                |              |              | I           | PTEN<10:0 | >     |        |       |       |        | 0000          |

| PMSTAT    | 060E | IBF    | IBOV   | _      | —      | IB3F    | IB2F   | IB1F           | IB0F         | OBE          | OBUF        | —         | _     | OB3E   | OB2E  | OB1E  | OB0E   | 008F          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

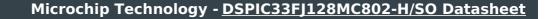

### 4.6 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (because the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing as these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

### 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

#### FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 15, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

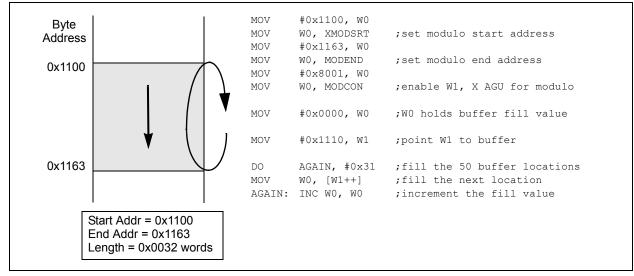

#### **BROWN-OUT SITUATIONS** FIGURE 6-3:

#### 6.5 **External Reset (EXTR)**

The external Reset is generated by driving the MCLR pin low. The MCLR pin is a Schmitt trigger input with an additional glitch filter. Reset pulses that are longer than the minimum pulse width will generate a Reset. Refer to Section 31.0 "Electrical Characteristics" for minimum pulse width specifications. The External Reset (MCLR) Pin bit (EXTR) in the Reset Control register (RCON<7>) is set to indicate the MCLR Reset.

#### EXTERNAL SUPERVISORY CIRCUIT 6.5.0.1

Many systems have external supervisory circuits that generate reset signals to Reset multiple devices in the system. This external Reset signal can be directly connected to the MCLR pin to Reset the device when the rest of system is Reset.

#### 6.5.0.2 INTERNAL SUPERVISORY CIRCUIT

When using the internal power supervisory circuit to Reset the device, the external reset pin (MCLR) should be tied directly or resistively to VDD. In this case, the MCLR pin will not be used to generate a Reset. The external reset pin (MCLR) does not have an internal pull-up and must not be left unconnected.

#### 6.6 Software RESET Instruction (SWR)

Whenever the RESET instruction is executed, the device will assert SYSRST, placing the device in a special Reset state. This Reset state will not re-initialize the clock. The clock source in effect prior to the RESET instruction will remain. SYSRST is released at the next instruction cycle, and the reset vector fetch will commence.

The Software Reset (Instruction) Flag bit (SWR) in the Reset Control register (RCON<6>) is set to indicate the software Reset.

#### 6.7 Watchdog Time-out Reset (WDTO)

Whenever a Watchdog time-out occurs, the device will asynchronously assert SYSRST. The clock source will remain unchanged. A WDT time-out during Sleep or Idle mode will wake-up the processor, but will not reset the processor.

The Watchdog Timer Time-out Flag bit (WDTO) in the Reset Control register (RCON<4>) is set to indicate the Watchdog Reset. Refer to Section 28.4 "Watchdog Timer (WDT)" for more information on Watchdog Reset.

#### 6.8 Trap Conflict Reset

If a lower-priority hard trap occurs while a higher-priority trap is being processed, a hard trap conflict Reset occurs. The hard traps include exceptions of priority level 13 through level 15, inclusive. The address error (level 13) and oscillator error (level 14) traps fall into this category.

The Trap Reset Flag bit (TRAPR) in the Reset Control register (RCON<15>) is set to indicate the Trap Conflict Reset. Refer to Section 7.0 "Interrupt Controller" for more information on trap conflict Resets.

| U-0          | R/W-0       | R/W-0                              | U-0                          | U-0                 | U-0                   | U-0             | U-0     |

|--------------|-------------|------------------------------------|------------------------------|---------------------|-----------------------|-----------------|---------|

| _            | DMA4IE      | PMPIE                              | —                            | _                   | —                     | _               | _       |

| it 15        |             |                                    |                              |                     | I                     |                 | bit     |

|              |             |                                    |                              |                     |                       |                 |         |

| U-0          | U-0         | U-0                                | R/W-0                        | R/W-0               | R/W-0                 | R/W-0           | R/W-0   |

| —            |             | —                                  | DMA3IE                       | C1IE <sup>(1)</sup> | C1RXIE <sup>(1)</sup> | SPI2IE          | SPI2EIE |

| bit 7        |             |                                    |                              |                     |                       |                 | bit     |

|              |             |                                    |                              |                     |                       |                 |         |

| Legend:      | 1. 1.9      |                                    | 1.11                         |                     |                       |                 |         |

| R = Readab   |             | W = Writable                       |                              |                     | mented bit, read      |                 |         |

| -n = Value a | at POR      | '1' = Bit is se                    | t                            | '0' = Bit is cle    | ared                  | x = Bit is unki | nown    |

| bit 15       | Unimplomor  | ted: Read as                       | ·^'                          |                     |                       |                 |         |

| bit 14       | -           |                                    | o<br>Data Transfer C         | omploto Intorr      | runt Enable bit       |                 |         |

| JIL 14       |             | request enable                     |                              | omplete inten       |                       |                 |         |

|              |             | request not en                     |                              |                     |                       |                 |         |

| bit 13       | PMPIE: Para | Ilel Master Por                    | t Interrupt Ena              | ble bit             |                       |                 |         |

|              |             | request enable                     |                              |                     |                       |                 |         |

|              | •           | request not en                     |                              |                     |                       |                 |         |

| bit 12-5     | -           | nted: Read as                      |                              |                     |                       |                 |         |

| bit 4        |             |                                    | Data Transfer C              | complete Interr     | rupt Enable bit       |                 |         |

|              |             | request enable<br>request not en   |                              |                     |                       |                 |         |

| bit 3        |             | •                                  | pt Enable bit <sup>(1)</sup> |                     |                       |                 |         |

| 511 5        |             | request enable                     | •                            |                     |                       |                 |         |

|              |             | request not en                     |                              |                     |                       |                 |         |

| bit 2        | C1RXIE: EC/ | AN1 Receive I                      | Data Ready Inte              | errupt Enable I     | oit <sup>(1)</sup>    |                 |         |

|              |             | request enable                     |                              |                     |                       |                 |         |

|              | -           | request not en                     |                              |                     |                       |                 |         |

| bit 1        |             | Event Interrup                     |                              |                     |                       |                 |         |

|              |             | request enable                     |                              |                     |                       |                 |         |

|              |             |                                    |                              |                     |                       |                 |         |

| ait O        |             | •                                  |                              |                     |                       |                 |         |

| oit O        | SPI2EIE: SP | I2 Error Interru<br>request enable | pt Enable bit                |                     |                       |                 |         |

# REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

**Note 1:** Interrupts are disabled on devices without an ECAN<sup>™</sup> module.

| REGISTER     | 7-16: IPC1              | : INTERRUPT                              | PRIORITY       | CONTROL R         | EGISTER 1        |                 |       |

|--------------|-------------------------|------------------------------------------|----------------|-------------------|------------------|-----------------|-------|

| U-0          | R/W-1                   | R/W-0                                    | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

| —            |                         | T2IP<2:0>                                |                | —                 |                  | OC2IP<2:0>      |       |

| bit 15       |                         |                                          |                |                   |                  |                 | bit   |

| U-0          | R/W-1                   | R/W-0                                    | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

|              |                         | IC2IP<2:0>                               |                | _                 |                  | DMA0IP<2:0>     |       |

| bit 7        |                         |                                          |                |                   |                  |                 | bit   |

| Legend:      |                         |                                          |                |                   |                  |                 |       |

| R = Readab   | le bit                  | W = Writable                             | bit            | U = Unimple       | mented bit, rea  | ad as '0'       |       |

| -n = Value a | t POR                   | '1' = Bit is set                         |                | '0' = Bit is cle  | eared            | x = Bit is unkn | own   |

|              |                         |                                          |                |                   |                  |                 |       |

| bit 15       | Unimpleme               | ented: Read as '                         | כי             |                   |                  |                 |       |

| bit 14-12    | T2IP<2:0>:              | Timer2 Interrupt                         | Priority bits  |                   |                  |                 |       |

|              |                         | rupt is priority 7 (I                    |                | ty interrupt)     |                  |                 |       |

|              | •                       |                                          |                |                   |                  |                 |       |

|              | •                       |                                          |                |                   |                  |                 |       |

|              | •<br>001 = Inter        | rupt is priority 1                       |                |                   |                  |                 |       |

|              |                         | rupt source is dis                       | abled          |                   |                  |                 |       |

| bit 11       | Unimpleme               | ented: Read as '                         | o'             |                   |                  |                 |       |

| bit 10-8     | OC2IP<2:0               | >: Output Compa                          | re Channel     | 2 Interrupt Prior | ity bits         |                 |       |

|              | 111 = Interi            | rupt is priority 7 (I                    | highest priori | ty interrupt)     |                  |                 |       |

|              | •                       |                                          |                |                   |                  |                 |       |

|              | •                       |                                          |                |                   |                  |                 |       |

|              |                         | rupt is priority 1<br>rupt source is dis | abled          |                   |                  |                 |       |

| bit 7        |                         | ented: Read as '                         |                |                   |                  |                 |       |

| bit 6-4      | -                       | : Input Capture C                        |                | errupt Prioritv b | its              |                 |       |

|              |                         | rupt is priority 7 (I                    |                |                   |                  |                 |       |

|              | •                       |                                          | •              |                   |                  |                 |       |

|              | •                       |                                          |                |                   |                  |                 |       |

|              | •<br>001 <b>– Inter</b> | rupt is priority 1                       |                |                   |                  |                 |       |

|              |                         | rupt source is dis                       | abled          |                   |                  |                 |       |

| bit 3        |                         | ented: Read as '                         |                |                   |                  |                 |       |

| bit 2-0      | -                       | :0>: DMA Chann                           |                | nsfer Complete    | e Interrupt Prio | ritv bits       |       |

|              |                         | rupt is priority 7 (I                    |                |                   |                  | .,              |       |

|              | •                       |                                          |                | - • • /           |                  |                 |       |

|              | •                       |                                          |                |                   |                  |                 |       |

|              | •<br>001 = Inter        | rupt is priority 1                       |                |                   |                  |                 |       |

|              |                         | rupt source is dis                       | abled          |                   |                  |                 |       |

|              |                         |                                          |                |                   |                  |                 |       |

| U-0                         | U-0                                                                                                    | U-0                                                                                                                   | U-0                                           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|-----------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|-----------------|-----------------|-------|

| _                           |                                                                                                        |                                                                                                                       |                                               |                  |                 | DMA1IP<2:0>     |       |

| bit 15                      | ·                                                                                                      | ·                                                                                                                     |                                               |                  |                 |                 | bit 8 |

| U-0                         | R/W-1                                                                                                  | R/W-0                                                                                                                 | R/W-0                                         | U-0              | R/W-1           | R/W-0           | R/W-0 |

| _                           |                                                                                                        | AD1IP<2:0>                                                                                                            |                                               | —                |                 | U1TXIP<2:0>     |       |

| bit 7                       |                                                                                                        |                                                                                                                       |                                               |                  | ·               |                 | bit C |

| Legend:                     |                                                                                                        |                                                                                                                       |                                               |                  |                 |                 |       |

| R = Readab                  | ole bit                                                                                                | W = Writable I                                                                                                        | oit                                           | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value a                | at POR                                                                                                 | '1' = Bit is set                                                                                                      |                                               | '0' = Bit is cle | eared           | x = Bit is unkr | iown  |

|                             |                                                                                                        | upt is priority 1<br>upt source is disa                                                                               | abled                                         |                  |                 |                 |       |

| bit 7                       | Unimpleme                                                                                              | nted: Read as '                                                                                                       | ) <b>'</b>                                    |                  |                 |                 |       |

|                             |                                                                                                        |                                                                                                                       | )                                             |                  |                 |                 |       |

| bit 6-4                     | 111 = Interr<br>•<br>•<br>001 = Interr                                                                 | <ul> <li>ADC1 Convers</li> <li>upt is priority 7 (I</li> <li>upt is priority 1</li> <li>upt source is disa</li> </ul> | sion Complet<br>nighest priori                | •                | rity bits       |                 |       |

|                             | 111 = Interr<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | upt is priority 7 (ł                                                                                                  | sion Complet<br>nighest priori<br>abled       | •                | rity bits       |                 |       |

| bit 6-4<br>bit 3<br>bit 2-0 | 111 = Interr<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa                                                       | sion Complet<br>nighest priori<br>abled<br>)' | ty interrupt)    | rity bits       |                 |       |

001 = Interrupt is priority 1 000 = Interrupt source is disabled

•

### 7.6 Interrupt Setup Procedures

#### 7.6.1 INITIALIZATION

To configure an interrupt source at initialization:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level depends on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources can be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized such that all user interrupt sources are assigned to priority level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

#### 7.6.2 INTERRUPT SERVICE ROUTINE

The method used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (C or assembler) and the language development tool suite used to develop the application.

In general, the user application must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the program re-enters the ISR immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.6.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.6.4 INTERRUPT DISABLE

All user interrupts can be disabled using this procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the  ${\tt POP}$  instruction can be used to restore the previous SR value.

| Note: | Only user interrupts with a priority level of |

|-------|-----------------------------------------------|

|       | 7 or lower can be disabled. Trap sources      |

|       | (level 8-level 15) cannot be disabled.        |

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

NOTES:

# 19.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32MC302/304. dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet. refer to Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit ( $I^2C$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

### 19.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The  $l^2C$  module can operate either as a slave or a master on an  $l^2C$  bus.

The following types of  $I^2C$  operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

For details about the communication sequence in each of these modes, refer to the "*dsPIC33F/PIC24H Family Reference Manual*". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual chapters.

# 21.2 Frame Types

The ECAN module transmits various types of frames which include data messages, or remote transmission requests initiated by the user, as other frames that are automatically generated for control purposes. The following frame types are supported:

Standard Data Frame:

A standard data frame is generated by a node when the node wishes to transmit data. It includes an 11-bit Standard Identifier (SID), but not an 18-bit Extended Identifier (EID).

- Extended Data Frame:

- An extended data frame is similar to a standard data frame, but includes an extended identifier as well.

- Remote Frame:

- It is possible for a destination node to request the data from the source. For this purpose, the destination node sends a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node sends a data frame as a response to this remote request.

- Error Frame:

- An error frame is generated by any node that detects a bus error. An error frame consists of two fields: an error flag field and an error delimiter field.

- Overload Frame:

- An overload frame can be generated by a node as a result of two conditions. First, the node detects a dominant bit during interframe space which is an illegal condition. Second, due to internal conditions, the node is not yet able to start reception of the next message. A node can generate a maximum of 2 sequential overload frames to delay the start of the next message.

- · Interframe Space:

- Interframe space separates a proceeding frame (of whatever type) from a following data or remote frame.

### 21.3 Modes of Operation

The ECAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization mode

- · Disable mode

- Normal Operation mode

- Listen Only mode

- Listen All Messages mode

- · Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module does not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

### 21.3.1 INITIALIZATION MODE

In the Initialization mode, the module does not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The user application has access to Configuration registers that are access restricted in other modes. The module protects the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module can not be modified while the module is on-line. The ECAN module is not allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- · All Module Control registers

- Baud Rate and Interrupt Configuration registers

- Bus Timing registers

- Identifier Acceptance Filter registers

- Identifier Acceptance Mask registers

### 21.3.2 DISABLE MODE

In Disable mode, the module does not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts remains and the error counters retains their value.

If the REQOP<2:0> bits (CiCTRL1<10:8>) = 001, the module enters the Module Disable mode. If the module is active, the module waits for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins reverts to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note: Typically, if the ECAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the ECAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set and TXREQ bit is cleared.

# 21.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when the REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins assumes the CAN bus functions. The module transmits and receive CAN bus messages via the CiTX and CiRX pins.

#### 21.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

### 21.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting the REQOP<2:0 = 111. In this mode, the data which is in the message assembly buffer, until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

### 21.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module connects the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| REGISTER              | 22-0: AD1CI                                             | HSU: ADCT IN                                                                                                                                    | PUICHAN                                                     | NEL U SELE       | CI REGISTE       | R               |          |

|-----------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------|------------------|-----------------|----------|

| R/W-0                 | U-0                                                     | U-0                                                                                                                                             | R/W-0                                                       | R/W-0            | R/W-0            | R/W-0           | R/W-0    |

| CH0NB                 | —                                                       | —                                                                                                                                               |                                                             |                  | CH0SB<4:0>       |                 |          |

| bit 15                |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 | bit      |

| R/W-0                 | U-0                                                     | U-0                                                                                                                                             | R/W-0                                                       | R/W-0            | R/W-0            | R/W-0           | R/W-0    |

| <b>CH0NA</b>          |                                                         | _                                                                                                                                               |                                                             |                  | CH0SA<4:0>       |                 |          |

| bit 7                 |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 | bit      |

| Legend:               |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 |          |

| R = Readable          | e bit                                                   | W = Writable b                                                                                                                                  | oit                                                         | U = Unimpler     | mented bit, read | d as '0'        |          |

| -n = Value at         | POR                                                     | '1' = Bit is set                                                                                                                                |                                                             | '0' = Bit is cle |                  | x = Bit is unkr | nown     |

|                       |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 |          |

| bit 14-13<br>bit 12-8 | CH0SB<4:0><br>dsPIC33FJ32<br>01000 = Cha<br>00010 = Cha | <ul> <li>ited: Read as '0</li> <li>Channel 0 Pos</li> <li>Channel 0 positive i</li> <li>nnel 0 positive i</li> <li>nnel 0 positive i</li> </ul> | sitive Input Se<br>33FJ64MC20<br>nput is AN8<br>nput is AN2 |                  |                  | 204/804 devic   | es only: |

|                       |                                                         | nnel 0 positive i                                                                                                                               |                                                             |                  |                  |                 |          |

|                       | 00101 = Cha<br>•<br>•<br>00010 = Cha<br>00001 = Cha     | 2MC302, dsPIC<br>innel 0 positive i<br>innel 0 positive i<br>innel 0 positive i<br>innel 0 positive i                                           | nput is AN5<br>nput is AN2<br>nput is AN1                   | 2/802 and dsF    | PIC33FJ128MC     | 202/802 devic   | es only: |

| bit 7                 | <b>CH0NA:</b> Cha<br>1 = Channel (                      | nnel 0 Negative<br>0 negative input<br>0 negative input                                                                                         | Input Select is AN1                                         | for Sample A b   | it               |                 |          |

| bit 6-5               | Unimplemen                                              | ted: Read as '0                                                                                                                                 | ,                                                           |                  |                  |                 |          |

|                       |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 |          |

### REGISTER 22-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

| U-0           | U-0           | U-0               | U-0            | U-0                      | U-0             | U-0             | U-0   |

|---------------|---------------|-------------------|----------------|--------------------------|-----------------|-----------------|-------|

| _             | —             | —                 | —              | —                        | _               | —               | —     |

| bit 15        |               |                   |                |                          |                 |                 | bit 8 |

|               |               |                   |                |                          |                 |                 |       |

| R/W-0         | R/W-0         | R/W-0             | R/W-0          | R/W-0                    | R/W-0           | R/W-0           | R/W-0 |

| CVREN         | CVROE         | CVRR              | CVRSS          |                          | CVF             | २<3:0>          |       |

| bit 7         |               |                   |                |                          |                 |                 | bit C |

|               |               |                   |                |                          |                 |                 |       |

| Legend:       |               |                   |                |                          |                 |                 |       |

| R = Readable  | e bit         | W = Writable      | bit            | U = Unimplen             | nented bit, rea | ıd as '0'       |       |

| -n = Value at | POR           | '1' = Bit is set  | t              | '0' = Bit is clea        | ared            | x = Bit is unkr | nown  |

|               |               |                   |                |                          |                 |                 |       |

| bit 15-8      | Unimplemen    | ted: Read as '    | 0'             |                          |                 |                 |       |

| bit 7         | CVREN: Con    | nparator Voltag   | je Reference E | Enable bit               |                 |                 |       |

|               |               | rcuit powered     |                |                          |                 |                 |       |

|               |               | rcuit powered     |                |                          |                 |                 |       |

| bit 6         |               | nparator VREF     |                |                          |                 |                 |       |

|               |               | oltage level is o | •              | ef pin<br>from CVref pin |                 |                 |       |

| bit 5         |               | arator VREF R     |                | •                        |                 |                 |       |

|               | •             |                   | •              | CVRSRC with C            | /RSRC/24 step   | size            |       |

|               |               |                   |                | 9 CVRSRC with            |                 |                 |       |

| bit 4         | CVRSS: Corr   | parator VREF      | Source Select  | ion bit                  |                 |                 |       |

|               | 1 = Compara   | ator reference s  | source CVRSR   | c = Vref+ – Vr           | REF-            |                 |       |

|               | 0 = Compara   | tor reference s   | source CVRSR   | c = AVDD - AVS           | SS              |                 |       |

| bit 3-0       |               | •                 | EF Value Selec | ction 0 ⊴CVR<3           | :0> ≤15 bits    |                 |       |

|               | When CVRR     |                   |                |                          |                 |                 |       |

|               | CVREF = (CVR) | (≪3:0>/ 24) • (0  | _VRSRC)        |                          |                 |                 |       |

#### REGISTER 24-2: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

$\frac{VREF}{CVREF} = (CVRES.0) + (24) \bullet (CVRSRC)$   $\frac{When CVRR}{CVREF} = 1/4 \bullet (CVRSRC) + (CVRES.0) + (CVRSRC) \bullet (CVRSRC)$

#### 27.1 **PMP Resources**

Many useful resources related to PMP are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532315              |

#### 27.1.1 KEY RESOURCES

- Section 35. "Parallel Master Port (PMP)" (DS70299)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

### 30.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 30.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

# 30.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

# 30.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 30.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- · Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

| AC CHARAG            | CTERISTICS                               |                                             | Standard Operating<br>(unless otherwise s<br>Operating temperate | ,   |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|------------------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                       | CKE | СКР | SMP |  |  |

| 15 Mhz               | Table 31-33                              | —                                           | _                                                                | 0,1 | 0,1 | 0,1 |  |  |

| 9 Mhz                | _                                        | Table 31-34                                 | —                                                                | 1   | 0,1 | 1   |  |  |

| 9 Mhz                | —                                        | Table 31-35                                 | —                                                                | 0   | 0,1 | 1   |  |  |

| 15 Mhz               | _                                        | _                                           | Table 31-36                                                      | 1   | 0   | 0   |  |  |

| 11 Mhz               | _                                        | _                                           | Table 31-37                                                      | 1   | 1   | 0   |  |  |

| 15 Mhz               |                                          |                                             | Table 31-38                                                      | 0   | 1   | 0   |  |  |

| 11 Mhz               | _                                        | _                                           | Table 31-39                                                      | 0   | 0   | 0   |  |  |

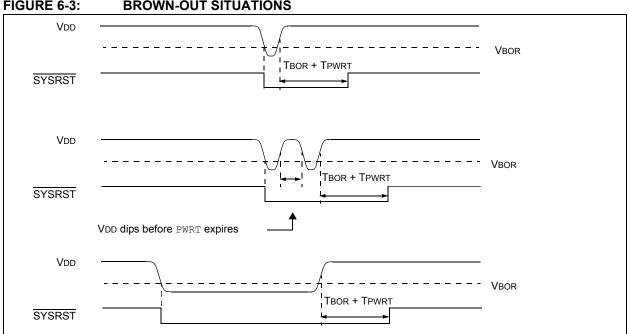

#### TABLE 31-32: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

#### FIGURE 31-14: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY CKE = 0) TIMING CHARACTERISTICS

#### FIGURE 31-15: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY CKE = 1) TIMING CHARACTERISTICS

| АС СНА | RACTER      | ISTICS                        |                           | REMENTS (SLAVE MODE)Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |          |       |                                                       |  |  |

|--------|-------------|-------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-------------------------------------------------------|--|--|

| Param. | Symbol      | Charac                        | teristic                  | Min                                                                                                                                                                                                                      | Max      | Units | Conditions                                            |  |  |

| IS10   | TLO:SCL     | Clock Low Time                | 100 kHz mode              | 4.7                                                                                                                                                                                                                      | —        | μs    | Device must operate at a minimum of 1.5 MHz           |  |  |

|        |             |                               | 400 kHz mode              | 1.3                                                                                                                                                                                                                      | —        | μs    | Device must operate at a minimum of 10 MHz            |  |  |

|        |             |                               | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                      |          | μs    | —                                                     |  |  |

| IS11   | THI:SCL     | Clock High Time               | 100 kHz mode              | 4.0                                                                                                                                                                                                                      | —        | μs    | Device must operate at a minimum of 1.5 MHz           |  |  |

|        |             |                               | 400 kHz mode              | 0.6                                                                                                                                                                                                                      | —        | μs    | Device must operate at a minimum of 10 MHz            |  |  |

|        |             |                               | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                      |          | μs    | —                                                     |  |  |

| IS20   | TF:SCL      | SDAx and SCLx<br>Fall Time    | 100 kHz mode              | _                                                                                                                                                                                                                        | 300      | ns    | CB is specified to be from                            |  |  |

|        |             |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                              | 300      | ns    | 10 to 400 pF                                          |  |  |

|        |             |                               | 1 MHz mode <sup>(1)</sup> | —                                                                                                                                                                                                                        | 100      | ns    |                                                       |  |  |

| IS21   | TR:SCL      | SDAx and SCLx<br>Rise Time    | 100 kHz mode              | —                                                                                                                                                                                                                        | 1000     | ns    | CB is specified to be from<br>10 to 400 pF            |  |  |

|        |             |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                              | 300      | ns    |                                                       |  |  |

|        |             |                               | 1 MHz mode <sup>(1)</sup> |                                                                                                                                                                                                                          | 300      | ns    |                                                       |  |  |

| IS25   | TSU:DAT     | Data Input<br>Setup Time      | 100 kHz mode              | 250                                                                                                                                                                                                                      |          | ns    | —                                                     |  |  |

|        |             |                               | 400 kHz mode              | 100                                                                                                                                                                                                                      |          | ns    |                                                       |  |  |

|        |             |                               | 1 MHz mode <sup>(1)</sup> | 100                                                                                                                                                                                                                      |          | ns    |                                                       |  |  |

| IS26   | THD:DAT     | Data Input<br>Hold Time       | 100 kHz mode              | 0                                                                                                                                                                                                                        |          | μs    | _                                                     |  |  |

|        |             |                               | 400 kHz mode              | 0                                                                                                                                                                                                                        | 0.9      | μs    |                                                       |  |  |

|        |             |                               | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                                                                                                        | 0.3      | μs    |                                                       |  |  |

| IS30   | Tsu:sta     | Start Condition<br>Setup Time | 100 kHz mode              | 4.7                                                                                                                                                                                                                      |          | μs    | Only relevant for Repeated Start condition            |  |  |

|        |             |                               | 400 kHz mode              | 0.6                                                                                                                                                                                                                      |          | μs    |                                                       |  |  |

|        |             |                               | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                                                                                                     |          | μs    |                                                       |  |  |

| IS31   | Thd:sta     | Start Condition<br>Hold Time  | 100 kHz mode              | 4.0                                                                                                                                                                                                                      |          | μs    | After this period, the first clock pulse is generated |  |  |

|        |             |                               | 400 kHz mode              | 0.6                                                                                                                                                                                                                      |          | μs    |                                                       |  |  |

|        |             |                               | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                                                                                                     |          | μs    |                                                       |  |  |

| IS33   | Tsu:sto     | Stop Condition<br>Setup Time  | 100 kHz mode              | 4.7                                                                                                                                                                                                                      |          | μs    | _                                                     |  |  |

|        |             |                               | 400 kHz mode              | 0.6                                                                                                                                                                                                                      |          | μs    |                                                       |  |  |

|        |             |                               | 1 MHz mode <sup>(1)</sup> | 0.6                                                                                                                                                                                                                      |          | μs    |                                                       |  |  |

| IS34   | THD:ST<br>O | Stop Condition<br>Hold Time   | 100 kHz mode              | 4000                                                                                                                                                                                                                     |          | ns    | _                                                     |  |  |

|        |             |                               | 400 kHz mode              | 600                                                                                                                                                                                                                      | _        | ns    | ]                                                     |  |  |

|        |             |                               | 1 MHz mode <sup>(1)</sup> | 250                                                                                                                                                                                                                      |          | ns    |                                                       |  |  |

| IS40   | TAA:SCL     | Output Valid<br>From Clock    | 100 kHz mode              | 0                                                                                                                                                                                                                        | 3500     | ns    | —                                                     |  |  |

|        |             |                               | 400 kHz mode              | 0                                                                                                                                                                                                                        | 1000     | ns    |                                                       |  |  |

|        |             |                               | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                                                                                                        | 350      | ns    | 1                                                     |  |  |

| IS45   | TBF:SDA     | Bus Free Time                 | 100 kHz mode              | 4.7                                                                                                                                                                                                                      | <b>—</b> | μs    | Time bus must be free                                 |  |  |