Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc802-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

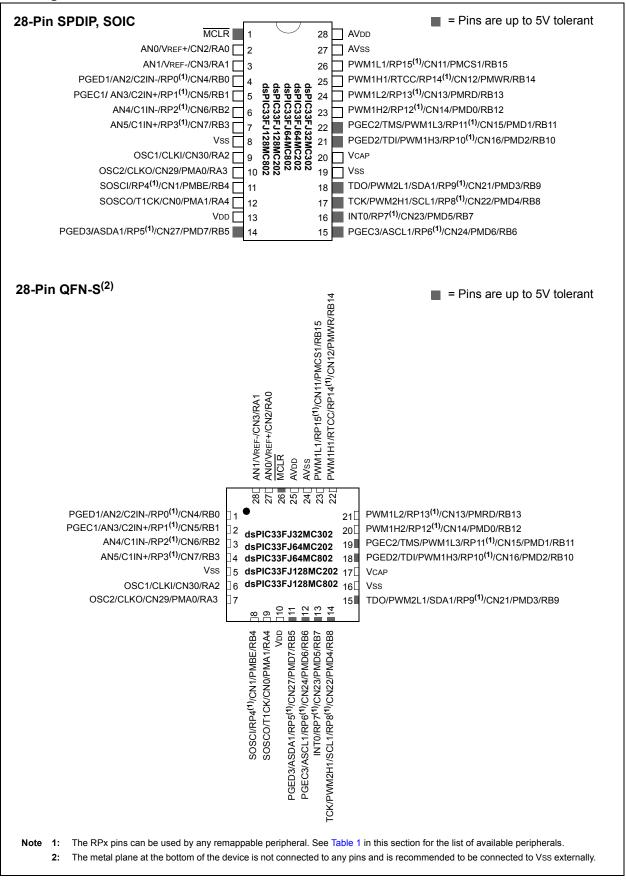

## dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

#### Pin Diagrams

NOTES:

| Symbol | Parameter                        | Value            |

|--------|----------------------------------|------------------|

| VPOR   | POR threshold                    | 1.8V nominal     |

| TPOR   | POR extension time               | 30 μs maximum    |

| VBOR   | BOR threshold                    | 2.5V nominal     |

| TBOR   | BOR extension time               | 100 μs maximum   |

| TPWRT  | Programmable power-up time delay | 0-128 ms nominal |

| TFSCM  | Fail-Safe Clock Monitor Delay    | 900 μs maximum   |

| IABLE 6-2: USCILLATUR PARAMETERS | <b>TABLE 6-2:</b> | <b>OSCILLATOR PARAMETERS</b> |

|----------------------------------|-------------------|------------------------------|

|----------------------------------|-------------------|------------------------------|

Note: When the device exits the Reset condition (begins normal operation), the device operating parameters (voltage, frequency, temperature, etc.) must be within their operating ranges, otherwise, the device may not function correctly. The user application must ensure that the delay between the time power is first applied, and the time SYSRST becomes inactive, is long enough to get operating parameters all within specification.

#### 6.4 Power-on Reset (POR)

A Power-on Reset (POR) circuit ensures the device is reset from power-on. The POR circuit is active until VDD crosses the VPOR threshold and the delay TPOR has elapsed. The delay TPOR ensures the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to Section 31.0 "Electrical Characteristics" for details.

The POR status bit (POR) in the Reset Control register (RCON<0>) is set to indicate the Power-on Reset.

## 6.4.1 Brown-out Reset (BOR) and Power-up Timer (PWRT)

The on-chip regulator has a Brown-out Reset (BOR) circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses VBOR threshold and the delay TBOR has elapsed. The delay TBOR ensures the voltage regulator output becomes stable.

The BOR status bit (BOR) in the Reset Control register (RCON<1>) is set to indicate the Brown-out Reset.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The PWRT provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

The power-up timer delay (TPWRT) is programmed by the Power-on Reset Timer Value Select bits (FPWRT<2:0>) in the POR Configuration register (FPOR<2:0>), which provides eight settings (from 0 ms to 128 ms). Refer to **Section 28.0 "Special Features"** for further details.

Figure 6-3 shows the typical brown-out scenarios. The reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point

| R/W-0                  | R/W-0                                                                                                               | U-0                             | U-0              | R/W-0                        | R/W-0                     | R/W-0            | U-0 |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|------------------------------|---------------------------|------------------|-----|--|--|--|

| DAC1LIF <sup>(2)</sup> | DAC1RIF <sup>(2)</sup>                                                                                              | _                               | —                | QEI2IF                       | FLTA2IF                   | PWM2IF           | —   |  |  |  |

| bit 15                 |                                                                                                                     |                                 |                  |                              |                           |                  | bit |  |  |  |

| U-0                    | R/W-0                                                                                                               | R/W-0                           | R/W-0            | R/W-0                        | R/W-0                     | R/W-0            | U-0 |  |  |  |

|                        | C1TXIF <sup>(1)</sup>                                                                                               | DMA7IF                          | DMA6IF           | CRCIF                        | U2EIF                     | U1EIF            |     |  |  |  |

| bit 7                  |                                                                                                                     |                                 |                  |                              |                           |                  | bit |  |  |  |

| Legend:                |                                                                                                                     |                                 |                  |                              |                           |                  |     |  |  |  |

| R = Readable           | bit                                                                                                                 | W = Writable                    | bit              | U = Unimple                  | mented bit, read          | d as '0'         |     |  |  |  |

| -n = Value at F        | POR                                                                                                                 | '1' = Bit is set                |                  | '0' = Bit is cle             | eared                     | x = Bit is unkno | own |  |  |  |

| bit 15                 | DAC1LIF: DA                                                                                                         | C Left Channe                   | el Interrupt Fla | g Status bit <sup>(2)</sup>  |                           |                  |     |  |  |  |

|                        | 1 = Interrupt r                                                                                                     | equest has oc                   | curred           |                              |                           |                  |     |  |  |  |

|                        |                                                                                                                     | equest has not                  |                  |                              |                           |                  |     |  |  |  |

| bit 14                 |                                                                                                                     | C Right Chan                    | •                | lag Status bit <sup>(2</sup> | 2)                        |                  |     |  |  |  |

|                        |                                                                                                                     | equest has oc<br>equest has not |                  |                              |                           |                  |     |  |  |  |

| bit 13-12              |                                                                                                                     | ted: Read as '                  |                  |                              |                           |                  |     |  |  |  |

| bit 11                 | •                                                                                                                   |                                 |                  | bit                          |                           |                  |     |  |  |  |

|                        | <b>QEI2IF:</b> QEI2 Event Interrupt Flag Status bit<br>1 = Interrupt request has occurred                           |                                 |                  |                              |                           |                  |     |  |  |  |

|                        | 0 = Interrupt request has not occurred                                                                              |                                 |                  |                              |                           |                  |     |  |  |  |

| bit 10                 | FLTA2IF: PWM2 Fault A Interrupt Flag Status bit                                                                     |                                 |                  |                              |                           |                  |     |  |  |  |

|                        | 1 = Interrupt request has occurred                                                                                  |                                 |                  |                              |                           |                  |     |  |  |  |

|                        | <ul> <li>0 = Interrupt request has not occurred</li> <li>PWM2IF: PWM2 Error Interrupt Enable bit</li> </ul>         |                                 |                  |                              |                           |                  |     |  |  |  |

| bit 9                  |                                                                                                                     |                                 | •                | t                            |                           |                  |     |  |  |  |

|                        |                                                                                                                     | equest has oc<br>equest has not |                  |                              |                           |                  |     |  |  |  |

| bit 8-7                |                                                                                                                     | ted: Read as '                  |                  |                              |                           |                  |     |  |  |  |

| bit 6                  | -                                                                                                                   | N1 Transmit D                   |                  | nterrupt Flag S              | Status bit <sup>(1)</sup> |                  |     |  |  |  |

|                        | 1 = Interrupt r                                                                                                     | equest has oc<br>equest has no  | curred           |                              |                           |                  |     |  |  |  |

| bit 5                  |                                                                                                                     | •                               |                  | `omolete Interi              | runt Elan Status          | bit              |     |  |  |  |

| bit 5                  | <b>DMA7IF:</b> DMA Channel 7 Data Transfer Complete Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                 |                  |                              |                           |                  |     |  |  |  |

|                        | 0 = Interrupt request has not occurred                                                                              |                                 |                  |                              |                           |                  |     |  |  |  |

| bit 4                  |                                                                                                                     |                                 |                  | Complete Interi              | rupt Flag Status          | bit              |     |  |  |  |

|                        | 1 = Interrupt request has occurred                                                                                  |                                 |                  |                              |                           |                  |     |  |  |  |

| bit 3                  | <ul> <li>0 = Interrupt request has not occurred</li> <li>CRCIF: CRC Generator Interrupt Flag Status bit</li> </ul>  |                                 |                  |                              |                           |                  |     |  |  |  |

| bit 0                  |                                                                                                                     |                                 |                  |                              |                           |                  |     |  |  |  |

|                        | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>              |                                 |                  |                              |                           |                  |     |  |  |  |

| bit 2                  | U2EIF: UART                                                                                                         | 2 Error Interru                 | pt Flag Status   | bit                          |                           |                  |     |  |  |  |

|                        |                                                                                                                     | equest has oc<br>equest has not |                  |                              |                           |                  |     |  |  |  |

| bit 1                  | -                                                                                                                   | 1 Error Interru                 |                  | bit                          |                           |                  |     |  |  |  |

|                        |                                                                                                                     | equest has oc                   | -                |                              |                           |                  |     |  |  |  |

|                        |                                                                                                                     | equest has not                  |                  |                              |                           |                  |     |  |  |  |

| bit 0                  | Unimplement                                                                                                         | ted: Read as '                  | 0'               |                              |                           |                  |     |  |  |  |

|                        |                                                                                                                     |                                 |                  |                              |                           |                  |     |  |  |  |

| Note 1: Inte           | errupts are disat                                                                                                   | plea on devices                 | s without an E   | :∪AN '‴ modul                | e.                        |                  |     |  |  |  |

#### REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

**Note 1:** Interrupts are disabled on devices without an ECAN<sup>™</sup> module.

2: Interrupts are disabled on devices without an Audio DAC module.

|               | <b>—</b> /                                                                                                 |                                                                           |                |                  | <b>B a</b> · · · · |                 |        |  |  |

|---------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------|------------------|--------------------|-----------------|--------|--|--|

| U-0           | R/W-0                                                                                                      | R/W-0                                                                     | R/W-0          | R/W-0            | R/W-0              | R/W-0           | R/W-0  |  |  |

|               | DMA1IE                                                                                                     | AD1IE                                                                     | U1TXIE         | U1RXIE           | SPI1IE             | SPI1EIE         | T3IE   |  |  |

| bit 15        |                                                                                                            |                                                                           |                |                  |                    |                 | bit    |  |  |

| R/W-0         | R/W-0                                                                                                      | R/W-0                                                                     | R/W-0          | R/W-0            | R/W-0              | R/W-0           | R/W-0  |  |  |

| T2IE          | OC2IE                                                                                                      | IC2IE                                                                     | DMA0IE         | T1IE             | OC1IE              | IC1IE           | INTOIE |  |  |

| bit 7         | OOLIE                                                                                                      | IOZIE                                                                     | DIVINIOIL      |                  | OONE               | IOTIL           | bit    |  |  |

|               |                                                                                                            |                                                                           |                |                  |                    |                 |        |  |  |

| Legend:       |                                                                                                            |                                                                           |                |                  |                    |                 |        |  |  |

| R = Readable  | e bit                                                                                                      | W = Writable                                                              | bit            | U = Unimplen     | mented bit, read   | d as '0'        |        |  |  |

| -n = Value at | POR                                                                                                        | '1' = Bit is set                                                          |                | '0' = Bit is cle | ared               | x = Bit is unkn | own    |  |  |

|               |                                                                                                            |                                                                           |                |                  |                    |                 |        |  |  |

| bit 15        | Unimplemen                                                                                                 | ted: Read as '                                                            | 0'             |                  |                    |                 |        |  |  |

| bit 14        |                                                                                                            |                                                                           |                | Complete Interr  | upt Enable bit     |                 |        |  |  |

|               |                                                                                                            | equest enable<br>equest not ena                                           |                |                  |                    |                 |        |  |  |

| bit 13        | •                                                                                                          | •                                                                         |                | rupt Enable bit  |                    |                 |        |  |  |

|               |                                                                                                            | equest enable                                                             | -              |                  |                    |                 |        |  |  |

|               | 0 = Interrupt r                                                                                            | equest not ena                                                            | abled          |                  |                    |                 |        |  |  |

| bit 12        |                                                                                                            | RT1 Transmitte                                                            | •              | ible bit         |                    |                 |        |  |  |

|               |                                                                                                            | equest enable                                                             |                |                  |                    |                 |        |  |  |

| bit 11        | <ul> <li>0 = Interrupt request not enabled</li> <li>U1RXIE: UART1 Receiver Interrupt Enable bit</li> </ul> |                                                                           |                |                  |                    |                 |        |  |  |

|               | 1 = Interrupt request enabled                                                                              |                                                                           |                |                  |                    |                 |        |  |  |

|               | 0 = Interrupt request not enabled                                                                          |                                                                           |                |                  |                    |                 |        |  |  |

| bit 10        |                                                                                                            | Event Interrup                                                            |                |                  |                    |                 |        |  |  |

|               |                                                                                                            | equest enable<br>equest not ena                                           |                |                  |                    |                 |        |  |  |

| bit 9         | -                                                                                                          | 1 Error Interru                                                           |                |                  |                    |                 |        |  |  |

| bit o         |                                                                                                            | equest enable                                                             |                |                  |                    |                 |        |  |  |

|               |                                                                                                            | equest not ena                                                            |                |                  |                    |                 |        |  |  |

| bit 8         |                                                                                                            | Interrupt Enab                                                            |                |                  |                    |                 |        |  |  |

|               |                                                                                                            | equest enable<br>equest not ena                                           |                |                  |                    |                 |        |  |  |

| bit 7         | •                                                                                                          | •                                                                         |                |                  |                    |                 |        |  |  |

|               |                                                                                                            | <b>T2IE:</b> Timer2 Interrupt Enable bit<br>1 = Interrupt request enabled |                |                  |                    |                 |        |  |  |

|               |                                                                                                            | equest not ena                                                            |                |                  |                    |                 |        |  |  |

| bit 6         | OC2IE: Outpu                                                                                               | ut Compare Ch                                                             | annel 2 Interr | upt Enable bit   |                    |                 |        |  |  |

|               |                                                                                                            | equest enable                                                             |                |                  |                    |                 |        |  |  |

| bit 5         | •                                                                                                          | equest not ena<br>Capture Chann                                           |                | Enabla bit       |                    |                 |        |  |  |

| DIL D         |                                                                                                            | equest enable                                                             |                |                  |                    |                 |        |  |  |

|               |                                                                                                            | request not ena                                                           |                |                  |                    |                 |        |  |  |

| bit 4         | DMA0IE: DM                                                                                                 | A Channel 0 D                                                             | ata Transfer C | Complete Interr  | upt Enable bit     |                 |        |  |  |

|               |                                                                                                            | equest enable                                                             |                |                  |                    |                 |        |  |  |

| hit 2         | -                                                                                                          | equest not ena                                                            |                |                  |                    |                 |        |  |  |

| bit 3         |                                                                                                            | Interrupt Enab<br>equest enable                                           |                |                  |                    |                 |        |  |  |

|               | ⊥ – monupti                                                                                                | Squear chable                                                             | u .            |                  |                    |                 |        |  |  |

© 2007-2012 Microchip Technology Inc.

## REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 2 | CMIE: Comparator Interrupt Enable bit                                                     |

|-------|-------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| bit 1 | MI2C1IE: I2C1 Master Events Interrupt Enable bit                                          |

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| bit 0 | SI2C1IE: I2C1 Slave Events Interrupt Enable bit                                           |

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

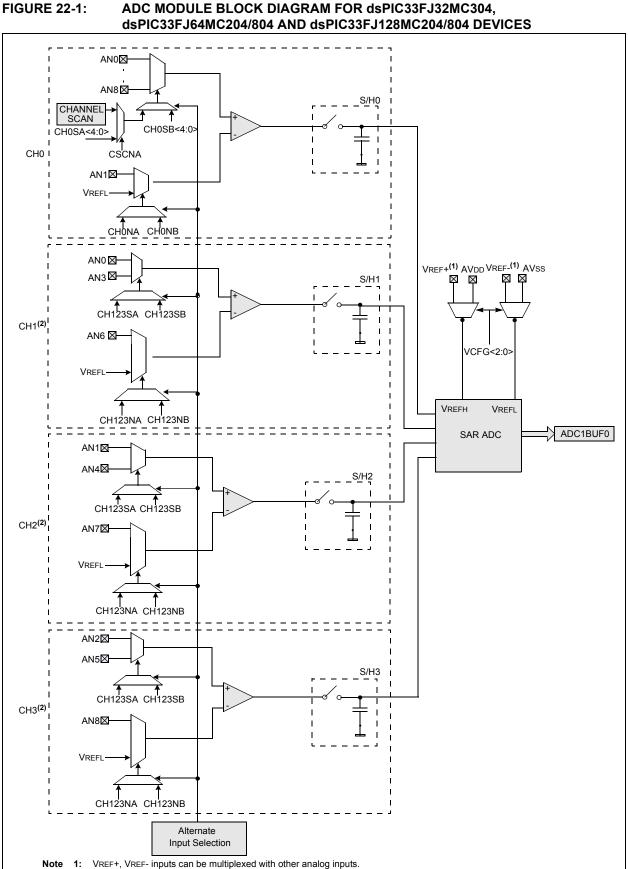

2: Channels 1, 2 and 3 are not applicable for the 12-bit mode of operation.

| R/W-0        | U-0                            | U-0                             | R/W-0          | R/W-0                  | R/W-0           | R/W-0          | R/W-0 |

|--------------|--------------------------------|---------------------------------|----------------|------------------------|-----------------|----------------|-------|

| ADRC         | _                              | _                               |                |                        | SAMC<4:0>(      | 1)             |       |

| bit 15       |                                |                                 |                |                        |                 |                | bit   |

|              |                                |                                 |                |                        |                 |                |       |

| R/W-0        | R/W-0                          | R/W-0                           | R/W-0          | R/W-0                  | R/W-0           | R/W-0          | R/W-0 |

|              |                                |                                 | ADCS           | <7:0> <sup>(2)</sup>   |                 |                |       |

| bit 7        |                                |                                 |                |                        |                 |                | bit   |

| Legend:      |                                |                                 |                |                        |                 |                |       |

| R = Readab   | le bit                         | W = Writable t                  | oit            | U = Unimpler           | mented bit, rea | ad as '0'      |       |

| -n = Value a | t POR                          | '1' = Bit is set                |                | '0' = Bit is cle       | ared            | x = Bit is unk | nown  |

|              |                                |                                 |                |                        |                 |                |       |

| bit 15       |                                | Conversion Clo<br>rnal RC clock | CK Source bit  |                        |                 |                |       |

|              |                                | rived from syste                | m clock        |                        |                 |                |       |

| bit 14-13    |                                | nted: Read as '0                |                |                        |                 |                |       |

| bit 12-8     | •                              | : Auto Sample T                 |                |                        |                 |                |       |

|              | 11111 <b>= 31</b> <sup>-</sup> | •                               |                |                        |                 |                |       |

|              | •                              |                                 |                |                        |                 |                |       |

|              | •                              |                                 |                |                        |                 |                |       |

|              | •                              |                                 |                |                        |                 |                |       |

|              | 00001 = 1 TA<br>00000 = 0 TA   |                                 |                |                        |                 |                |       |

| bit 7-0      | ADCS<7:0>:                     | ADC Conversion                  | on Clock Sele  | ct bits <sup>(2)</sup> |                 |                |       |

|              | 11111111 =                     | Reserved                        |                |                        |                 |                |       |

|              | •                              |                                 |                |                        |                 |                |       |

|              | •                              |                                 |                |                        |                 |                |       |

|              | •                              |                                 |                |                        |                 |                |       |

|              | •                              |                                 |                |                        |                 |                |       |

|              | 01000000 =                     |                                 |                | <b>T T</b>             |                 |                |       |

|              | 00111111 =                     | TCY · (ADCS<7                   | (:0> + 1) = 64 | $\cdot$ ICY = IAD      |                 |                |       |

|              | •                              |                                 |                |                        |                 |                |       |

|              | •                              |                                 |                |                        |                 |                |       |

|              | -                              | TCY · (ADCS<7                   | 7.0> + 1) = 3  | · TCY = TAD            |                 |                |       |

|              |                                | TCY · (ADCS<7                   |                |                        |                 |                |       |

|              | 00000000 =                     | 、 <i>-</i>                      |                |                        |                 |                |       |

####

2: This bit is not used if AD1CON3<15> (ADRC) = 1.

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| REGISTER              | 22-0: AD1CI                                             | HSU: ADCT IN                                                                                                                                    | PUICHAN                                                     | NEL U SELE       | CI REGISTE       | R               |          |

|-----------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------|------------------|-----------------|----------|

| R/W-0                 | U-0                                                     | U-0                                                                                                                                             | R/W-0                                                       | R/W-0            | R/W-0            | R/W-0           | R/W-0    |

| CH0NB                 | —                                                       | —                                                                                                                                               |                                                             |                  | CH0SB<4:0>       |                 |          |

| bit 15                |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 | bit      |

| R/W-0                 | U-0                                                     | U-0                                                                                                                                             | R/W-0                                                       | R/W-0            | R/W-0            | R/W-0           | R/W-0    |

| <b>CH0NA</b>          |                                                         | _                                                                                                                                               |                                                             |                  | CH0SA<4:0>       |                 |          |

| bit 7                 |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 | bit      |

| Legend:               |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 |          |

| R = Readable          | e bit                                                   | W = Writable b                                                                                                                                  | oit                                                         | U = Unimpler     | mented bit, read | d as '0'        |          |

| -n = Value at         | POR                                                     | '1' = Bit is set                                                                                                                                |                                                             | '0' = Bit is cle |                  | x = Bit is unkr | nown     |

|                       |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 |          |

| bit 14-13<br>bit 12-8 | CH0SB<4:0><br>dsPIC33FJ32<br>01000 = Cha<br>00010 = Cha | <ul> <li>ited: Read as '0</li> <li>Channel 0 Pos</li> <li>Channel 0 positive i</li> <li>nnel 0 positive i</li> <li>nnel 0 positive i</li> </ul> | sitive Input Se<br>33FJ64MC20<br>nput is AN8<br>nput is AN2 |                  |                  | 204/804 devic   | es only: |

|                       |                                                         | nnel 0 positive i                                                                                                                               |                                                             |                  |                  |                 |          |

|                       | 00101 = Cha<br>•<br>•<br>00010 = Cha<br>00001 = Cha     | 2MC302, dsPIC<br>innel 0 positive i<br>innel 0 positive i<br>innel 0 positive i<br>innel 0 positive i                                           | nput is AN5<br>nput is AN2<br>nput is AN1                   | 2/802 and dsF    | PIC33FJ128MC     | 202/802 devic   | es only: |

| bit 7                 | <b>CH0NA:</b> Cha<br>1 = Channel (                      | nnel 0 Negative<br>0 negative input<br>0 negative input                                                                                         | Input Select is AN1                                         | for Sample A b   | it               |                 |          |

| bit 6-5               | Unimplemen                                              | ted: Read as '0                                                                                                                                 | ,                                                           |                  |                  |                 |          |

|                       |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 |          |

#### REGISTER 22-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

## REGISTER 27-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

| bit 2 | BEP: Byte Enable Polarity bit                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Byte enable active-high (PMBE)</li> <li>0 = Byte enable active-low (PMBE)</li> </ul>                                        |

| bit 1 | WRSP: Write Strobe Polarity bit                                                                                                          |

|       | For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):<br>1 = Write strobe active-high (PMWR)<br>0 = Write strobe active-low (PMWR) |

|       | For Master mode 1 (PMMODE<9:8> = 11):<br>1 = Enable strobe active-high (PMENB)<br>0 = Enable strobe active-low (PMENB)                   |

| bit 0 | RDSP: Read Strobe Polarity bit                                                                                                           |

|       | For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):<br>1 = Read strobe active-high (PMRD)<br>0 = Read strobe active-low (PMRD)   |

|       | For Master mode 1 (PMMODE<9:8> = 11):<br>1 = Read/write strobe active-high (PMRD/PMWR)<br>0 = Read/write strobe active-low (PMRD/PMWR)   |

- Note 1: 28-pin devices do not have PMA<10:2>.

- 2: These bits have no effect when their corresponding pins are used as address lines.

| Register 27-2:   | PMMODE: PARALLEL PORT MODE REGISTER                                                                      |                                                                              |                                                    |                                             |                                                                                        |                                    |                      |  |

|------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------|----------------------|--|

| R-0              | R/W-0                                                                                                    | R/W-0                                                                        | R/W-0                                              | R/W-0                                       | R/W-0                                                                                  | R/W-0                              | R/W-0                |  |

| BUSY             | IRQ                                                                                                      | M<1:0>                                                                       | INC                                                | VI<1:0>                                     | MODE16                                                                                 | MODE                               | =<1:0>               |  |

| bit 15           |                                                                                                          |                                                                              |                                                    |                                             |                                                                                        |                                    | bit 8                |  |

| R/W-0            | R/W-0                                                                                                    | R/W-0                                                                        | R/W-0                                              | R/W-0                                       | R/W-0                                                                                  | R/W-0                              | R/W-0                |  |

| WAITB<1          | :0> <sup>(1)</sup>                                                                                       |                                                                              | WAI                                                | ГM<3:0>                                     |                                                                                        | WAITE                              | <1:0> <sup>(1)</sup> |  |

| bit 7            |                                                                                                          |                                                                              |                                                    |                                             |                                                                                        |                                    | bit (                |  |

| Legend:          |                                                                                                          |                                                                              |                                                    |                                             |                                                                                        |                                    |                      |  |

| R = Readable bi  | t                                                                                                        | W = Writable                                                                 | bit                                                | U = Unimple                                 | mented bit, read                                                                       | as '0'                             |                      |  |

| -n = Value at PC | R                                                                                                        | '1' = Bit is se                                                              | t                                                  | ʻ0' = Bit is cle                            | eared                                                                                  | x = Bit is unkr                    | nown                 |  |

| bit 15           | BUSY: Busv                                                                                               | v bit (Master mo                                                             | de onlv)                                           |                                             |                                                                                        |                                    |                      |  |

| :                | -                                                                                                        | usy (not useful                                                              | • ·                                                | cessor stall is a                           | ictive)                                                                                |                                    |                      |  |

| bit 14-13        | RQM<1:0>:                                                                                                | Interrupt Requ                                                               | est Mode bits                                      |                                             |                                                                                        |                                    |                      |  |

|                  | or on a<br>10 = No inte<br>11 = Interrup                                                                 |                                                                              | peration when<br>l, processor si<br>the end of the | PMA<1:0> = :<br>all activated               | Write Buffer 3 is v<br>11 (Addressable<br>de                                           |                                    |                      |  |

| bit 12-11 I      | NCM<1:0>:                                                                                                | Increment Mod                                                                | le bits                                            |                                             |                                                                                        |                                    |                      |  |

|                  | 10 = Decren                                                                                              | ad and write bu<br>nent ADDR<10:<br>ent ADDR<10:0<br>rement or decre         | 0> by 1 every<br>)> by 1 every                     | read/write cyc<br>read/write cycl           |                                                                                        | ()                                 |                      |  |

| bit 10           | MODE16: 8/                                                                                               | /16-bit Mode bit                                                             |                                                    |                                             |                                                                                        |                                    |                      |  |

|                  |                                                                                                          |                                                                              |                                                    |                                             | o the data registe<br>the data register                                                |                                    |                      |  |

| bit 9-8          | MODE<1:0>                                                                                                | ·: Parallel Port                                                             | Mode Select b                                      | vits                                        | -                                                                                      |                                    |                      |  |

|                  | 10 = Master                                                                                              | mode 2 (PMCS<br>ced PSP, contro                                              | 61, PMRD <u>, PN</u><br>I signals (PM              | <u>IWR, PMBE, F</u><br>RD, PM <u>WR, PI</u> | PMBE, PMA <x:0<br>PMA<x:0> and Pl<br/>MCS1, PMD&lt;7:0<br/>, PMWR, PMCS</x:0></x:0<br> | MD<7:0>)<br><u>&gt;</u> and PMA<1: | .0>)                 |  |

| bit 7-6          | NAITB<1:0                                                                                                | >: Data Setup to                                                             | Read/Write                                         | Wait State Con                              | figuration bits <sup>(1)</sup>                                                         |                                    |                      |  |

|                  | 10 <b>= Data w</b><br>01 <b>= Data w</b>                                                                 | ait of 4 Tcy; mu<br>ait of 3 Tcy; mu<br>ait of 2 Tcy; mu<br>ait of 1 Tcy; mu | Itiplexed addr<br>Itiplexed addr                   | ess phase of 3<br>ess phase of 2            | TCY<br>TCY                                                                             |                                    |                      |  |

| bit 5-2          | NAITM<3:0                                                                                                | >: Read to Byte                                                              | Enable Strob                                       | e Wait State C                              | onfiguration bits                                                                      |                                    |                      |  |

|                  | WAITM<3:0>: Read to Byte Enable Strobe Wait State Configuration bits<br>1111 = Wait of additional 15 Tcy |                                                                              |                                                    |                                             |                                                                                        |                                    |                      |  |

|                  | ,                                                                                                        |                                                                              |                                                    |                                             |                                                                                        |                                    |                      |  |

|                  |                                                                                                          | of additional 1<br>additional wait c                                         |                                                    | on forced into (                            | ane Tcv)                                                                               |                                    |                      |  |

|                  |                                                                                                          | <ul> <li>Data Hold Aft</li> </ul>                                            | • • • •                                            |                                             |                                                                                        |                                    |                      |  |

|                  | 11 = Wait of<br>10 = Wait of<br>11 = Wait of<br>10 = Wait of<br>10 = Wait of                             | 4 Tcy<br>3 Tcy<br>2 Tcy                                                      |                                                    |                                             |                                                                                        |                                    |                      |  |

### Register 27-2: PMMODE: PARALLEL PORT MODE REGISTER

**Note 1:** WAITB and WAITE bits are ignored whenever WAITM3:WAITM0 = 0000.

| CONFIG BITS           | BSS<2:0> = x11 0K                                                                                                                                                                                                                                                                                                                                                                                                                                     | BSS<2:0> = x10 1K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BSS<2:0> = x01 4K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BSS<2:0> = x00 8K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSS<2:0> = x11<br>0K  | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>002000h<br>003FFEh<br>004000h<br>007FFEh           GS = 21760 IW         007FFEh<br>008000h<br>007FFEh           0157FEh                                                                                                                                                                                                                                        | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>002000h<br>003FFEh<br>004000h<br>003FFEh<br>004000h<br>003FFEh           GS = 20992 IW         000000h<br>0000h<br>003FFEh<br>004000h<br>000ABFEh           0157FEh                                                                                                                                                                                                                                                                                                                 | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>002000h<br>003FFEh<br>004000h<br>003FFEh<br>004000h<br>007FFEh           GS = 17920 IW         0157FEh                                                                                                                                                                                                                                                                                                                    | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>000800h<br>003FFEh           GS = 13824 IW         00000h<br>003FFEh<br>004000h<br>003FFEh           004000h<br>007FFEh           004000h<br>007FFEh           004000h<br>007FFEh           004000h<br>007FFEh           004000h           007FFEh           008000h           007FFEh           004000h           007FFEh           004000h           007FFEh           004000h           007FFEh           004000h           007FFEh           004000h           007FFEh           008000h           007FFEh           008000h           007FFEh           00000h           007FFEh |

| SSS<2:0> = x10<br>4K  | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>00200h<br>003FFEh           SS = 3840 IW         0014FEh<br>00200h<br>003FFEh<br>004000h<br>007FFEh<br>008000h<br>007FFEh           GS = 17920 IW         0057FEh<br>008000h<br>007FFEh           00157FEh         0057FEh                                                                                                                                      | VS = 256 IW         000000h<br>0001FEh<br>000200h           BS = 768 IW         000200h<br>0007FEh<br>000800h           SS = 3072 IW         001FFEh<br>002000h           GS = 17920 IW         00800h<br>003FFEh           004BFEh         008000h<br>003FFEh           00400h         007FFEh           00400h         007FFEh           00400h         007FFEh           00400h         007FFEh           00800h         007FFEh           0040FFEh         008000h           007FFEh         008000h           007FFEh         008000h                                | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>00200h<br>003FFEh<br>004000h<br>007FFEh<br>004000h<br>007FFEh<br>004000h<br>007FFEh           GS = 17920 IW         0157FEh                                                                                                                                                                                                                                                                                               | VS = 256 IW         000000h           BS = 7936 IW         0007FEh           000200h         0007FEh           000800h         001FFEh           00200h         003FFEh           003FFEh         004000h           007FFEh         008000h           003FFEh         004000h           007FFEh         008000h           007FFEh         004000h           007FFEh         004000h           007FFEh         004000h           007FFEh         004000h           007FFEh         004000h           007FFEh         00157FEh                                                                                                                                                |

| SSS<2:0> = x01<br>8K  | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>002000h<br>003FFEh<br>004000h<br>003FFEh<br>004000h<br>007FFEh           GS = 13824 IW         00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>00000h<br>000000 | VS = 256 IW         000000h<br>0001FEh           BS = 768 IW         000200h           000800h         001FFEh           000300h         001FFEh           003200h         003FFEh           004000h         007FFEh           00157FEh         0157FEh | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh           SS = 3840 IW         0007FEh<br>000800h<br>003FFEh           SS = 4096 IW         004000h<br>007FFEh           GS = 13824 IW         00400h<br>007FFEh           00400h<br>007FFEh         00400h<br>007FFEh           00400h         007FFEh           00400h         007FFEh           00400h         007FFEh           00400h         007FFEh           00400h         007FFEh           00400h         007FFEh | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>002000h<br>003FFEh<br>004000h<br>003FFEh<br>004000h<br>007FFEh           GS = 13824 IW         0157FEh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SSS<2:0> = x00<br>16K | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>000800h<br>003FFEh<br>004000h<br>003FFEh<br>004000h<br>007FFEh<br>008000h<br>003FFEh           SS = 16128 IW         0007FFEh<br>004000h<br>007FFEh<br>008000h<br>007FFEh           GS = 5632 IW         0157FEh                                                                                                                                                | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>000800h<br>003FFEh<br>004000h<br>003FFEh<br>004000h<br>003FFEh<br>004000h<br>007FFEh           SS = 15360 IW         0007FFEh<br>004000h<br>003FFEh<br>004000h<br>00ABFEh           GS = 5632 IW         0157FEh                                                                                                                                                                                                                                                                    | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>002000h<br>003FFEh<br>004000h<br>003FFEh<br>004000h<br>007FFEh           SS = 12288 IW         004000h<br>007FFEh<br>008000h<br>007FFEh           GS = 5632 IW         0157FEh                                                                                                                                                                                                                                            | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>002000h<br>003FFEh           SS = 8192 IW         004000h<br>007FFEh<br>004000h<br>007FFEh           GS = 5632 IW         0157FEh                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## TABLE 28-4: CODE FLASH SECURITY SEGMENT SIZES FOR 64 KB DEVICES

#### 29.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33FJ32MC302/ 304. dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

The dsPIC33F instruction set is identical to that of the dsPIC30F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- Word or byte-oriented operations

- Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 29-1 shows the general symbols used in describing the instructions.

The dsPIC33F instruction set summary in Table 29-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The  ${\tt MAC}$  class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- · The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- · The accumulator write back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

| Base<br>Instr<br># | Assembly<br>Mnemonic |                   | Assembly Syntax                     | Description                                                               | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-------------------|-------------------------------------|---------------------------------------------------------------------------|---------------|----------------|--------------------------|

| 48                 | MPY                  | MPY<br>Wm*Wn,Ad   | cc,Wx,Wxd,Wy,Wyd                    | Multiply Wm by Wn to Accumulator                                          | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY<br>Wm*Wm,A    | cc,Wx,Wxd,Wy,Wyd                    | Square Wm to Accumulator                                                  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 49                 | MPY.N                | MPY.N<br>Wm*Wn,Ad | cc,Wx,Wxd,Wy,Wyd                    | -(Multiply Wm by Wn) to Accumulator                                       | 1             | 1              | None                     |

| 50                 | MSC                  | MSC               | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd<br>,<br>AWB | Multiply and Subtract from Accumulator                                    | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |