Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc802-i-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1:   PINOUT I/O DESCRIPTIONS |             |                                |            |                                                                                                                                                                                                                                                                     |  |  |  |  |

|--------------------------------------|-------------|--------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                             | Pin<br>Type | Buffer<br>Type                 | PPS        | Description                                                                                                                                                                                                                                                         |  |  |  |  |

| AN0-AN8                              | I           | Analog                         | No         | Analog input channels.                                                                                                                                                                                                                                              |  |  |  |  |

| CLKI                                 | <br>  0     | ST/CMOS                        | No<br>No   | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally, functions as CLKO in RC and EC modes.<br>Always associated with OSC2 pin function. |  |  |  |  |

| OSC1                                 |             | ST/CMOS                        | No         | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                                                                                                                |  |  |  |  |

| OSC2                                 | I/O         | _                              | No         | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                           |  |  |  |  |

| SOSCI<br>SOSCO                       | <br>  0     | ST/CMOS                        | No<br>No   | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.<br>32.768 kHz low-power oscillator crystal output.                                                                                                                                                   |  |  |  |  |

| CN0-CN30                             | I           | ST                             | No         | Change notification inputs. Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                    |  |  |  |  |

| IC1-IC2<br>IC7-IC8                   |             | ST<br>ST                       | Yes<br>Yes | Capture inputs 1/2.<br>Capture inputs 7/8.                                                                                                                                                                                                                          |  |  |  |  |

| OCFA<br>OC1-OC4                      | <br>  0     | ST<br>—                        | Yes<br>Yes | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).<br>Compare outputs 1 through 4.                                                                                                                                                                         |  |  |  |  |

| INT0                                 | I           | ST                             | No         | External interrupt 0.                                                                                                                                                                                                                                               |  |  |  |  |

| INT1                                 |             | ST                             | Yes        | External interrupt 1.                                                                                                                                                                                                                                               |  |  |  |  |

| INT2<br>RA0-RA4                      | 1           | ST                             | Yes        | External interrupt 2.                                                                                                                                                                                                                                               |  |  |  |  |

| RA0-RA4<br>RA7-RA10                  | 1/O<br>1/O  | ST<br>ST                       | No<br>No   | PORTA is a bidirectional I/O port.<br>PORTA is a bidirectional I/O port.                                                                                                                                                                                            |  |  |  |  |

| RB0-RB15                             | I/O         | ST                             | No         | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                  |  |  |  |  |

| RC0-RC9                              | I/O         | ST                             | No         | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                  |  |  |  |  |

| T1CK                                 | I           | ST                             | No         | Timer1 external clock input.                                                                                                                                                                                                                                        |  |  |  |  |

| T2CK                                 |             | ST                             | Yes        | Timer2 external clock input.                                                                                                                                                                                                                                        |  |  |  |  |

| T3CK<br>T4CK                         |             | ST<br>ST                       | Yes<br>Yes | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                                                                                                        |  |  |  |  |

| T5CK                                 |             | ST                             | Yes        | Timer5 external clock input.                                                                                                                                                                                                                                        |  |  |  |  |

| U1CTS                                | 1           | ST                             | Yes        | UART1 clear to send.                                                                                                                                                                                                                                                |  |  |  |  |

| U1RTS                                | 0           | _                              | Yes        | UART1 ready to send.                                                                                                                                                                                                                                                |  |  |  |  |

| U1RX                                 | I           | ST                             | Yes        | UART1 receive.                                                                                                                                                                                                                                                      |  |  |  |  |

| U1TX                                 | 0           | —                              | Yes        | UART1 transmit.                                                                                                                                                                                                                                                     |  |  |  |  |

| U2CTS                                | I I         | ST                             | Yes        | UART2 clear to send.                                                                                                                                                                                                                                                |  |  |  |  |

| U2RTS                                | 0           | -                              | Yes        | UART2 ready to send.                                                                                                                                                                                                                                                |  |  |  |  |

| U2RX<br>U2TX                         |             | ST<br>—                        | Yes<br>Yes | UART2 receive.<br>UART2 transmit.                                                                                                                                                                                                                                   |  |  |  |  |

|                                      |             |                                |            |                                                                                                                                                                                                                                                                     |  |  |  |  |

| SCK1<br>SDI1                         | I/O         | ST<br>ST                       | Yes<br>Yes | Synchronous serial clock input/output for SPI1.<br>SPI1 data in.                                                                                                                                                                                                    |  |  |  |  |

| SD01                                 | 0           |                                | Yes        | SPI1 data out.                                                                                                                                                                                                                                                      |  |  |  |  |

| SS1                                  | I/O         | ST                             | Yes        | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                      |  |  |  |  |

| SCK2                                 | I/O         | ST                             | Yes        | Synchronous serial clock input/output for SPI2.                                                                                                                                                                                                                     |  |  |  |  |

| SDI2                                 | I           | ST                             | Yes        | SPI2 data in.                                                                                                                                                                                                                                                       |  |  |  |  |

| SDO2                                 | 0           | —                              | Yes        | SPI2 data out.                                                                                                                                                                                                                                                      |  |  |  |  |

| SS2                                  | I/O         | ST                             | Yes        | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                      |  |  |  |  |

| SCL1                                 | I/O         | ST                             | No         | Synchronous serial clock input/output for I2C1.                                                                                                                                                                                                                     |  |  |  |  |

| SDA1                                 | I/O         | ST                             | No         | Synchronous serial data input/output for I2C1.                                                                                                                                                                                                                      |  |  |  |  |

| ASCL1                                | I/O         | ST                             | No         | Alternate synchronous serial clock input/output for I2C1.                                                                                                                                                                                                           |  |  |  |  |

| ASDA1                                | I/O         | ST                             | No         | Alternate synchronous serial data input/output for I2C1.                                                                                                                                                                                                            |  |  |  |  |

|                                      |             | S compatibl                    |            |                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                      |             | Frigger input<br>eral Pin Sele |            | MOS levels O = Output I = Input<br>TTL = TTL input buffer                                                                                                                                                                                                           |  |  |  |  |

| сг                                   |             |                                |            |                                                                                                                                                                                                                                                                     |  |  |  |  |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS

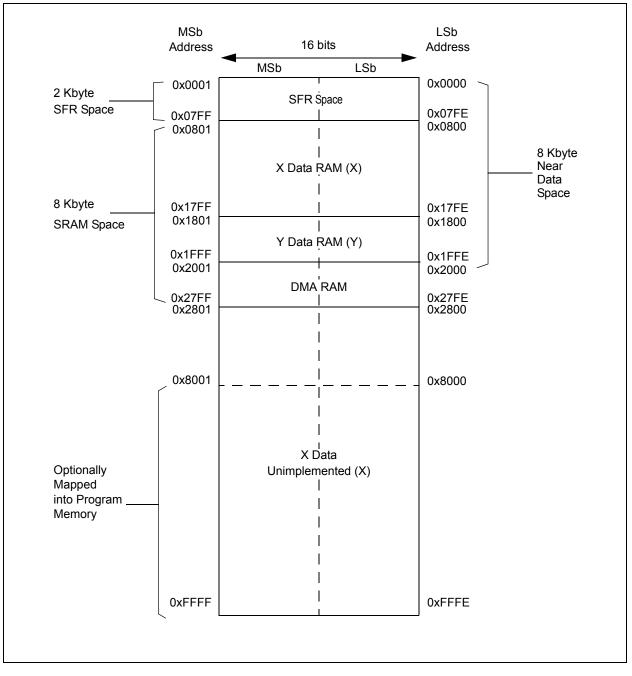

#### FIGURE 4-4: DATA MEMORY MAP FOR dsPIC33FJ128MC202/204 AND dsPIC33FJ64MC202/ 204 DEVICES WITH 8 KB RAM

| Bit 15  | Bit 14  |                                                                                |                                                                                                                               |                                                                                                                                                                   |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|---------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | DICIT   | Bit 13                                                                         | Bit 12                                                                                                                        | Bit 11                                                                                                                                                            | Bit 10                                                                                                                                                                                                           | Bit 9                                                                                                                                                                                                                                          | Bit 8                                                                                                                     | Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | All<br>Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CN15IE  | CN14IE  | CN13IE                                                                         | CN12IE                                                                                                                        | CN11IE                                                                                                                                                            | -                                                                                                                                                                                                                | —                                                                                                                                                                                                                                              | -                                                                                                                         | CN7IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CN6IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CN5IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CN4IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CN3IE                                                                                                                                                                                                                                                                                                                                                                                                                                               | CN2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CN1IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CN0IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| —       | CN30IE  | CN29IE                                                                         | -                                                                                                                             | CN27IE                                                                                                                                                            | -                                                                                                                                                                                                                | _                                                                                                                                                                                                                                              | CN24IE                                                                                                                    | CN23IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CN22IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CN21IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CN16IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CN15PUE | CN14PUE | CN13PUE                                                                        | CN12PUE                                                                                                                       | CN11PUE                                                                                                                                                           | -                                                                                                                                                                                                                | _                                                                                                                                                                                                                                              | —                                                                                                                         | CN7PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CN6PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CN5PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CN4PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CN3PUE                                                                                                                                                                                                                                                                                                                                                                                                                                              | CN2PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CN1PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CN0PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| —       | CN30PUE | CN29PUE                                                                        | —                                                                                                                             | CN27PUE                                                                                                                                                           | —                                                                                                                                                                                                                | _                                                                                                                                                                                                                                              | CN24PUE                                                                                                                   | CN23PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CN22PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CN21PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CN16PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |