Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20 MIPS                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b; D/A 6x16b                                                         |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc804-h-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.7 Arithmetic Logic Unit (ALU)

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register. The C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.7.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- · 8-bit unsigned x 8-bit unsigned

## 3.7.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.8 DSP Engine

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- · Fractional or integer DSP multiply (IF)

- Signed or unsigned DSP multiply (US)

- Conventional or convergent rounding (RND)

- Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

A block diagram of the DSP engine is shown in Figure 3-3.

| TABLE 3-1: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

|             | Algebraic ACC Write     |      |  |  |  |  |  |  |  |

|-------------|-------------------------|------|--|--|--|--|--|--|--|

| Instruction | Algebraic<br>Operation  | Back |  |  |  |  |  |  |  |

| CLR         | A = 0                   | Yes  |  |  |  |  |  |  |  |

| ED          | $A = (x - y)^2$         | No   |  |  |  |  |  |  |  |

| EDAC        | $A = A + (x - y)^2$     | No   |  |  |  |  |  |  |  |

| MAC         | $A = A + (x \bullet y)$ | Yes  |  |  |  |  |  |  |  |

| MAC         | A = A + x2              | No   |  |  |  |  |  |  |  |

| MOVSAC      | No change in A          | Yes  |  |  |  |  |  |  |  |

| MPY         | $A = x \bullet y$       | No   |  |  |  |  |  |  |  |

| MPY         | A = x 2                 | No   |  |  |  |  |  |  |  |

| MPY.N       | $A = -x \bullet y$      | No   |  |  |  |  |  |  |  |

| MSC         | $A = A - x \bullet y$   | Yes  |  |  |  |  |  |  |  |

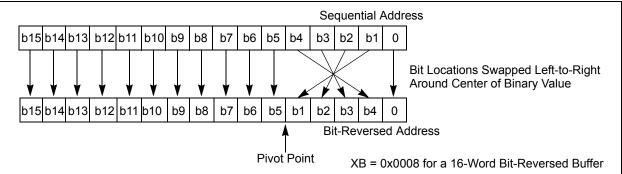

### TABLE 4-41: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

| Normal Address |    |    |    |         |    | Bit-Reversed Address |    |    |         |

|----------------|----|----|----|---------|----|----------------------|----|----|---------|

| A3             | A2 | A1 | A0 | Decimal | A3 | A2                   | A1 | A0 | Decimal |

| 0              | 0  | 0  | 0  | 0       | 0  | 0                    | 0  | 0  | 0       |

| 0              | 0  | 0  | 1  | 1       | 1  | 0                    | 0  | 0  | 8       |

| 0              | 0  | 1  | 0  | 2       | 0  | 1                    | 0  | 0  | 4       |

| 0              | 0  | 1  | 1  | 3       | 1  | 1                    | 0  | 0  | 12      |

| 0              | 1  | 0  | 0  | 4       | 0  | 0                    | 1  | 0  | 2       |

| 0              | 1  | 0  | 1  | 5       | 1  | 0                    | 1  | 0  | 10      |

| 0              | 1  | 1  | 0  | 6       | 0  | 1                    | 1  | 0  | 6       |

| 0              | 1  | 1  | 1  | 7       | 1  | 1                    | 1  | 0  | 14      |

| 1              | 0  | 0  | 0  | 8       | 0  | 0                    | 0  | 1  | 1       |

| 1              | 0  | 0  | 1  | 9       | 1  | 0                    | 0  | 1  | 9       |

| 1              | 0  | 1  | 0  | 10      | 0  | 1                    | 0  | 1  | 5       |

| 1              | 0  | 1  | 1  | 11      | 1  | 1                    | 0  | 1  | 13      |

| 1              | 1  | 0  | 0  | 12      | 0  | 0                    | 1  | 1  | 3       |

| 1              | 1  | 0  | 1  | 13      | 1  | 0                    | 1  | 1  | 11      |

| 1              | 1  | 1  | 0  | 14      | 0  | 1                    | 1  | 1  | 7       |

| 1              | 1  | 1  | 1  | 15      | 1  | 1                    | 1  | 1  | 15      |

# 7.3 Interrupt Control and Status Registers

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 devices implement a total of 30 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFSx

- IECx

- IPCx

- INTTREG

## 7.3.1 INTCON1 AND INTCON2

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS) as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table (AIVT).

### 7.3.2 IFSx

The IFS registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

## 7.3.3 IECx

The IEC registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

## 7.3.4 IPCx

The IPC registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

## 7.3.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into vector number bits (VECNUM<6:0>) and Interrupt level bits (ILR<3:0>) in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having vector number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0>, and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

### 7.3.6 STATUS/CONTROL REGISTERS

Although they are not specifically part of the interrupt control hardware, two of the CPU control registers contain bits that control interrupt functionality.

- The CPU Status register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU interrupt priority level. The user software can change the current CPU priority level by writing to the IPL bits.

- The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU priority level. The IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-32.

# 7.4 Interrupts Resources

Many useful resources related to Interrupts are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the<br>product page using the link above, enter<br>this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en532315                                              |

## 7.4.1 KEY RESOURCES

- Section 32. "Interrupts (Part III)" (DS70214)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit                                                                          |

|-------|-----------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Address error trap has occurred</li><li>0 = Address error trap has not occurred</li></ul>           |

| bit 2 | STKERR: Stack Error Trap Status bit                                                                             |

|       | 1 = Stack error trap has occurred                                                                               |

|       | 0 = Stack error trap has not occurred                                                                           |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit                                                              |

|       | <ul><li>1 = Oscillator failure trap has occurred</li><li>0 = Oscillator failure trap has not occurred</li></ul> |

| bit 0 | Unimplemented: Read as '0'                                                                                      |

# REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | OC1IE: Output Compare Channel 1 Interrupt Enable bit                                      |

|-------|-------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| bit 1 | IC1IE: Input Capture Channel 1 Interrupt Enable bit                                       |

|       | 1 = Interrupt request enabled                                                             |

|       | 0 = Interrupt request not enabled                                                         |

| bit 0 | INTOIE: External Interrupt 0 Flag Status bit                                              |

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| R/W-0        | R/W-0         | R/W-0                                                                                                     | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |

|--------------|---------------|-----------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|---------|--|--|--|--|

| U2TXIE       | U2RXIE        | INT2IE                                                                                                    | T5IE           | T4IE             | OC4IE           | OC3IE           | DMA2IE  |  |  |  |  |

| bit 15       | ·             | ·                                                                                                         | ·              | •<br>•           |                 |                 | bit 8   |  |  |  |  |

|              |               |                                                                                                           |                |                  |                 |                 |         |  |  |  |  |

| R/W-0        | R/W-0         | U-0                                                                                                       | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |

| IC8IE        | IC7IE         |                                                                                                           | INT1IE         | CNIE             | CMIE            | MI2C1IE         | SI2C1IE |  |  |  |  |

| bit 7        |               |                                                                                                           |                |                  |                 |                 | bit 0   |  |  |  |  |

|              |               |                                                                                                           |                |                  |                 |                 |         |  |  |  |  |

| Legend:      | I I.:.        |                                                                                                           | L :4           |                  |                 |                 |         |  |  |  |  |

| R = Readab   |               | W = Writable                                                                                              |                |                  | nented bit, rea |                 |         |  |  |  |  |

| -n = Value a | t POR         | '1' = Bit is set                                                                                          | t              | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |  |  |  |  |

| bit 15       |               | RT2 Transmitte                                                                                            | r Intorrunt En | abla hit         |                 |                 |         |  |  |  |  |

| DIL 15       |               | request enable                                                                                            | -              |                  |                 |                 |         |  |  |  |  |

|              |               | request not en                                                                                            |                |                  |                 |                 |         |  |  |  |  |

| bit 14       | U2RXIE: UA    | RT2 Receiver I                                                                                            | nterrupt Enab  | le bit           |                 |                 |         |  |  |  |  |

|              | 1 = Interrupt | request enable                                                                                            | d              |                  |                 |                 |         |  |  |  |  |

|              | 0 = Interrupt | request not ena                                                                                           | abled          |                  |                 |                 |         |  |  |  |  |

| bit 13       |               | rnal Interrupt 2                                                                                          |                |                  |                 |                 |         |  |  |  |  |

|              |               | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>              |                |                  |                 |                 |         |  |  |  |  |

| bit 12       | -             | -                                                                                                         |                |                  |                 |                 |         |  |  |  |  |

| DIL 12       |               | i Interrupt Enab<br>request enable                                                                        |                |                  |                 |                 |         |  |  |  |  |

|              |               | request not enable                                                                                        |                |                  |                 |                 |         |  |  |  |  |

| bit 11       | T4IE: Timer4  | Interrupt Enab                                                                                            | le bit         |                  |                 |                 |         |  |  |  |  |

|              | 1 = Interrupt | Interrupt request enabled                                                                                 |                |                  |                 |                 |         |  |  |  |  |

|              | 0 = Interrupt | request not ena                                                                                           | abled          |                  |                 |                 |         |  |  |  |  |

| bit 10       | -             | out Compare Ch                                                                                            |                | upt Enable bit   |                 |                 |         |  |  |  |  |

|              |               | request enable                                                                                            |                |                  |                 |                 |         |  |  |  |  |

| hit 0        | •             | request not ena                                                                                           |                | unt Enchlo hit   |                 |                 |         |  |  |  |  |

| bit 9        | •             | out Compare Ch<br>request enable                                                                          |                | upt Enable bit   |                 |                 |         |  |  |  |  |

|              |               | request not enable                                                                                        |                |                  |                 |                 |         |  |  |  |  |

| bit 8        | -             | -                                                                                                         |                | Complete Interr  | upt Enable bit  |                 |         |  |  |  |  |

|              |               | <b>DMA2IE:</b> DMA Channel 2 Data Transfer Complete Interrupt Enable bit<br>1 = Interrupt request enabled |                |                  |                 |                 |         |  |  |  |  |

|              | 0 = Interrupt | request not ena                                                                                           | abled          |                  |                 |                 |         |  |  |  |  |

| bit 7        | IC8IE: Input  | Capture Chann                                                                                             | el 8 Interrupt | Enable bit       |                 |                 |         |  |  |  |  |

|              |               | request enable                                                                                            |                |                  |                 |                 |         |  |  |  |  |

|              | •             | request not en                                                                                            |                |                  |                 |                 |         |  |  |  |  |

| bit 6        | -             | Capture Chann                                                                                             | -              | Enable bit       |                 |                 |         |  |  |  |  |

|              |               | request enable<br>request not ena                                                                         |                |                  |                 |                 |         |  |  |  |  |

| hit 5        |               | ntequest not only                                                                                         |                |                  |                 |                 |         |  |  |  |  |

bit 5Unimplemented: Read as '0'bit 4INT1IE: External Interrupt 1 Enable

### bit 4 INT1IE: External Interrupt 1 Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled

# bit 3 CNIE: Input Change Notification Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

# 11.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. The dsPIC33F devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Continuous state monitoring

- Configuration bit pin select lock

#### 11.6.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers;

clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) the IOLOCK bit as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register:            |

|-------|-------------------------------------------------------------------------------------------------------------|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)<br>See MPLAB IDE Help for more<br>information. |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the peripheral pin selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

#### 11.6.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset is triggered.

#### 11.6.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY Configuration bit (FOSC<5>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the peripheral pin select registers.

# 20.3 UART Control Registers

# REGISTER 20-1: UxMODE: UARTx MODE REGISTER

| R/W-0                 | U-0 | R/W-0 | R/W-0               | R/W-0 | U-0 | R/W-0 | R/W-0 |

|-----------------------|-----|-------|---------------------|-------|-----|-------|-------|

| UARTEN <sup>(1)</sup> | —   | USIDL | IREN <sup>(2)</sup> | RTSMD | —   | UEN   | <1:0> |

| bit 15                |     |       |                     |       |     |       | bit 8 |

| R/W-0, HC | R/W-0  | R/W-0, HC | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------|--------|-----------|--------|-------|-------|-------|-------|

| WAKE      | LPBACK | ABAUD     | URXINV | BRGH  | PDSEL | <1:0> | STSEL |

| bit 7     |        |           |        |       |       |       | bit 0 |

| Legend:           | HC = Hardware cleared |                             |                    |  |  |

|-------------------|-----------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared        | x = Bit is unknown |  |  |

| bit 15  | UARTEN: UARTx Enable bit                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = UARTx is enabled; all UARTx pins are controlled by UARTx as defined by UEN&lt;1:0&gt;</li> <li>0 = UARTx is disabled; all UARTx pins are controlled by port latches; UARTx power consumption minimal</li> </ul>                                                                                                                                                                    |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                      |

| bit 13  | USIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                                                                                                                                                                                                                                                           |

| bit 12  | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = IrDA encoder and decoder enabled</li> <li>0 = IrDA encoder and decoder disabled</li> </ul>                                                                                                                                                                                                                                                                                         |

| bit 11  | RTSMD: Mode Selection for UxRTS Pin bit                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = UxRTS pin in Simplex mode</li> <li>0 = UxRTS pin in Flow Control mode</li> </ul>                                                                                                                                                                                                                                                                                                   |

| bit 10  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                      |

| bit 9-8 | UEN<1:0>: UARTx Enable bits                                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>11 = UxTX, UxRX and BCLK pins are enabled and used; UxCTS pin controlled by port latches</li> <li>10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used</li> <li>01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin controlled by port latches</li> <li>00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/BCLK pins controlled by port latches</li> </ul> |

| bit 7   | WAKE: Wake-up on Start bit Detect During Sleep Mode Enable bit                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = UARTx continues to sample the UxRX pin; interrupt generated on falling edge; bit cleared<br/>in hardware on following rising edge</li> <li>0 = No wake-up enabled</li> </ul>                                                                                                                                                                                                       |

| bit 6   | LPBACK: UARTx Loopback Mode Select bit                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>1 = Enable Loopback mode</li> <li>0 = Loopback mode is disabled</li> </ul>                                                                                                                                                                                                                                                                                                             |

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Enable baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul>                                                                                                                                                           |

| Note 1: | Refer to <b>Section 17. "UART"</b> (DS70188) in the <i>"dsPIC33F/PIC24H Family Reference Manual"</i> for information on enabling the UART module for receive or transmit operation.                                                                                                                                                                                                             |

2: This feature is only available for the 16x BRG mode (BRGH = 0).

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| U-0           | U-0                            | U-0                                | R-0    | R-0              | R-0              | R-0             | R-0   |

|---------------|--------------------------------|------------------------------------|--------|------------------|------------------|-----------------|-------|

|               | _                              | _                                  |        |                  | FILHIT<4:0>      |                 |       |

| oit 15        |                                |                                    |        |                  |                  |                 | bit   |

| U-0           | R-1                            | R-0                                | R-0    | R-0              | R-0              | R-0             | R-0   |

|               |                                | IX U                               | i t u  | ICODE<6:0>       | -                | IX U            | i t u |

| oit 7         |                                |                                    |        |                  |                  |                 | bit   |

| _egend:       |                                |                                    |        |                  |                  |                 |       |

| R = Readabl   | le bit                         | W = Writable                       | bit    | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at |                                | '1' = Bit is set                   |        | '0' = Bit is cle |                  | x = Bit is unkr | nown  |

| bit 15-13     | Unimplemen                     | ted: Read as '                     | 0'     |                  |                  |                 |       |

| bit 12-8      | •                              | Filter Hit Num                     |        |                  |                  |                 |       |

|               | 10000-1111                     | 1 = Reserved                       |        |                  |                  |                 |       |

|               | 01111 = Filte                  | er 15                              |        |                  |                  |                 |       |

|               | •                              |                                    |        |                  |                  |                 |       |

|               | •                              |                                    |        |                  |                  |                 |       |

|               | •                              |                                    |        |                  |                  |                 |       |

|               | 00001 = Filte<br>00000 = Filte |                                    |        |                  |                  |                 |       |

| bit 7         |                                | ted: Read as '                     | 0'     |                  |                  |                 |       |

| bit 6-0       | -                              | Interrupt Flag                     |        |                  |                  |                 |       |

|               |                                | 11111 = Rese                       |        |                  |                  |                 |       |

|               |                                | IFO almost full                    |        |                  |                  |                 |       |

|               |                                | leceiver overflo                   |        |                  |                  |                 |       |

|               | 1000010 = V<br>1000001 = E     | Vake-up interru<br>rror interrupt  | ρι     |                  |                  |                 |       |

|               | 1000000 = N                    |                                    |        |                  |                  |                 |       |

|               | •                              |                                    |        |                  |                  |                 |       |

|               | •                              |                                    |        |                  |                  |                 |       |

|               | •                              |                                    |        |                  |                  |                 |       |

|               |                                | 11111 = Rese                       |        |                  |                  |                 |       |

|               | 0001111 <b>= R</b>             | B15 buffer Inte                    | errupt |                  |                  |                 |       |

|               | •                              |                                    |        |                  |                  |                 |       |

|               | •                              |                                    |        |                  |                  |                 |       |

|               | 0001001 <b>= R</b>             | B9 buffer inter                    | rupt   |                  |                  |                 |       |

|               | 0001000 <b>= R</b>             | B8 buffer inter                    | rupt   |                  |                  |                 |       |

|               |                                | RB7 buffer inte                    | •      |                  |                  |                 |       |

|               |                                | RB6 buffer inte<br>RB5 buffer inte |        |                  |                  |                 |       |

|               |                                | RB4 buffer inte                    |        |                  |                  |                 |       |

|               | 0000011 <b>= T</b>             | RB3 buffer inte                    | errupt |                  |                  |                 |       |

|               |                                | RB2 buffer inte                    |        |                  |                  |                 |       |

|               | 0000001 = 1                    | RB1 buffer inte                    | HUDL   |                  |                  |                 |       |

| U-0             | R/W-x                                                                                                 | U-0             | U-0               | U-0              | R/W-x                   | R/W-x                | R/W-x |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|-------------------------|----------------------|-------|--|--|--|

| _               | WAKFIL                                                                                                | _               | _                 | _                |                         | SEG2PH<2:0>          |       |  |  |  |

| bit 15          |                                                                                                       |                 |                   |                  |                         |                      | bit   |  |  |  |

|                 |                                                                                                       |                 |                   |                  |                         |                      |       |  |  |  |

| R/W-x           | R/W-x                                                                                                 | R/W-x           | R/W-x             | R/W-x            | R/W-x                   | R/W-x                | R/W-x |  |  |  |

| SEG2PHTS        | SAM                                                                                                   |                 | SEG1PH<2:0>       | >                |                         | PRSEG<2:0>           |       |  |  |  |

| bit 7           |                                                                                                       |                 |                   |                  |                         |                      | bit   |  |  |  |

| Legend:         |                                                                                                       |                 |                   |                  |                         |                      |       |  |  |  |

| R = Readable    | bit                                                                                                   | W = Writable    | e bit             | U = Unimpler     | mented bit, re          | ad as '0'            |       |  |  |  |

| -n = Value at F | POR                                                                                                   | '1' = Bit is se | et                | '0' = Bit is cle |                         | x = Bit is unkno     | wn    |  |  |  |

|                 |                                                                                                       |                 |                   |                  |                         |                      |       |  |  |  |

| bit 15          | Unimplemen                                                                                            | ted: Read as    | ʻ0 <b>'</b>       |                  |                         |                      |       |  |  |  |

| bit 14          | WAKFIL: Sel                                                                                           | ect CAN Bus     | Line Filter for V | Vake-up bit      |                         |                      |       |  |  |  |

|                 |                                                                                                       | bus line filter |                   |                  |                         |                      |       |  |  |  |

|                 |                                                                                                       |                 | ot used for wake  | e-up             |                         |                      |       |  |  |  |

| bit 13-11       | •                                                                                                     | ted: Read as    |                   |                  |                         |                      |       |  |  |  |

| bit 10-8        | SEG2PH<2:0>: Phase Segment 2 bits                                                                     |                 |                   |                  |                         |                      |       |  |  |  |

|                 | 111 = Length                                                                                          | i is 8 x TQ     |                   |                  |                         |                      |       |  |  |  |

|                 | •                                                                                                     |                 |                   |                  |                         |                      |       |  |  |  |

|                 | •                                                                                                     |                 |                   |                  |                         |                      |       |  |  |  |

|                 | •                                                                                                     | ·               |                   |                  |                         |                      |       |  |  |  |

| L :+ 7          | 000 = Length                                                                                          |                 |                   | -4 1- :4         |                         |                      |       |  |  |  |

| bit 7           |                                                                                                       | -               | ent 2 Time Sele   | Ct Dit           |                         |                      |       |  |  |  |

|                 | 1 = Freely pro                                                                                        |                 | nite or Informati | ion Processing   | Time (IPT)              | vhichever is greate  | ar.   |  |  |  |

| bit 6           |                                                                                                       |                 |                   | ion nocessing    | j mne (n 1 <i>)</i> , v | villenevel is greate | 51    |  |  |  |

| DIT O           | <b>SAM:</b> Sample of the CAN Bus Line bit<br>1 = Bus line is sampled three times at the sample point |                 |                   |                  |                         |                      |       |  |  |  |

|                 | 0 = Bus line is sampled once at the sample point                                                      |                 |                   |                  |                         |                      |       |  |  |  |

| bit 5-3         |                                                                                                       | )>: Phase Seg   | -                 | ·                |                         |                      |       |  |  |  |

|                 | 111 = Length                                                                                          |                 |                   |                  |                         |                      |       |  |  |  |

|                 | •                                                                                                     |                 |                   |                  |                         |                      |       |  |  |  |

|                 | •                                                                                                     |                 |                   |                  |                         |                      |       |  |  |  |

|                 | •                                                                                                     |                 |                   |                  |                         |                      |       |  |  |  |

|                 | 000 = Length                                                                                          | is 1 x Tq       |                   |                  |                         |                      |       |  |  |  |

| bit 2-0         | PRSEG<2:0>                                                                                            | -: Propagation  | Time Segmen       | t bits           |                         |                      |       |  |  |  |

|                 | 111 = Length                                                                                          | is 8 x Tq       |                   |                  |                         |                      |       |  |  |  |

|                 | •                                                                                                     |                 |                   |                  |                         |                      |       |  |  |  |

|                 | •                                                                                                     |                 |                   |                  |                         |                      |       |  |  |  |

|                 |                                                                                                       |                 |                   |                  |                         |                      |       |  |  |  |

|                 | •                                                                                                     |                 |                   |                  |                         |                      |       |  |  |  |

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| REGISTER              | 22-0: AD1CI                                             | HSU: ADCT IN                                                                                                                                    | PUICHAN                                                     | NEL U SELE       | CI REGISTE       | R               |          |

|-----------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------|------------------|-----------------|----------|

| R/W-0                 | U-0                                                     | U-0                                                                                                                                             | R/W-0                                                       | R/W-0            | R/W-0            | R/W-0           | R/W-0    |

| CH0NB                 | —                                                       | —                                                                                                                                               |                                                             |                  | CH0SB<4:0>       |                 |          |

| bit 15                |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 | bit      |

| R/W-0                 | U-0                                                     | U-0                                                                                                                                             | R/W-0                                                       | R/W-0            | R/W-0            | R/W-0           | R/W-0    |

| <b>CH0NA</b>          |                                                         | _                                                                                                                                               |                                                             |                  | CH0SA<4:0>       |                 |          |

| bit 7                 |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 | bit      |

| Legend:               |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 |          |

| R = Readable          | e bit                                                   | W = Writable b                                                                                                                                  | oit                                                         | U = Unimpler     | mented bit, read | d as '0'        |          |

| -n = Value at         | POR                                                     | '1' = Bit is set                                                                                                                                |                                                             | '0' = Bit is cle |                  | x = Bit is unkr | nown     |

|                       |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 |          |

| bit 14-13<br>bit 12-8 | CH0SB<4:0><br>dsPIC33FJ32<br>01000 = Cha<br>00010 = Cha | <ul> <li>ited: Read as '0</li> <li>Channel 0 Pos</li> <li>Channel 0 positive i</li> <li>nnel 0 positive i</li> <li>nnel 0 positive i</li> </ul> | sitive Input Se<br>33FJ64MC20<br>nput is AN8<br>nput is AN2 |                  |                  | 204/804 devic   | es only: |

|                       |                                                         | nnel 0 positive i                                                                                                                               |                                                             |                  |                  |                 |          |

|                       | 00101 = Cha<br>•<br>•<br>00010 = Cha<br>00001 = Cha     | 2MC302, dsPIC<br>innel 0 positive i<br>innel 0 positive i<br>innel 0 positive i<br>innel 0 positive i                                           | nput is AN5<br>nput is AN2<br>nput is AN1                   | 2/802 and dsF    | PIC33FJ128MC     | 202/802 devic   | es only: |

| bit 7                 | <b>CH0NA:</b> Cha<br>1 = Channel (                      | nnel 0 Negative<br>0 negative input<br>0 negative input                                                                                         | Input Select is AN1                                         | for Sample A b   | it               |                 |          |

| bit 6-5               | Unimplemen                                              | ted: Read as '0                                                                                                                                 | ,                                                           |                  |                  |                 |          |

|                       |                                                         |                                                                                                                                                 |                                                             |                  |                  |                 |          |

# REGISTER 22-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

## 24.3 Comparator Voltage Reference

# 24.3.1 CONFIGURING THE COMPARATOR VOLTAGE REFERENCE

The voltage reference module is controlled through the CVRCON register (Register 24-2). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR3:CVR0), with one range offering finer resolution.

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

#### FIGURE 24-2: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

### 25.1 RTCC Module Registers

The RTCC module registers are organized into three categories:

- RTCC Control Registers

- RTCC Value Registers

- Alarm Value Registers

## 25.1.1 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Time registers are accessed through corresponding register pointers. The RTCC Value register window (RTCVALH and RTCVALL) uses the RTCPTR bits (RCFGCAL<9:8>) to select the desired timer register pair (see Table 25-1).

By writing the RTCVALH byte, the RTCC Pointer value, RTCPTR<1:0> bits, decrement by one until they reach '00'. Once they reach '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

| TABLE 25-1: | RTCVAL | REGISTER | MAPPING |

|-------------|--------|----------|---------|

|-------------|--------|----------|---------|

| RTCPTR | RTCC Value Register Window |             |  |  |  |  |

|--------|----------------------------|-------------|--|--|--|--|

| <1:0>  | RTCVAL<15:8>               | RTCVAL<7:0> |  |  |  |  |

| 00     | MINUTES                    | SECONDS     |  |  |  |  |

| 01     | WEEKDAY                    | HOURS       |  |  |  |  |

| 10     | MONTH                      | DAY         |  |  |  |  |

| 11     | —                          | YEAR        |  |  |  |  |

The Alarm Value register window (ALRMVALH and ALRMVALL) uses the ALRMPTR bits (ALCFGRPT<9:8>) to select the desired Alarm register pair (see Table 25-2).

By writing the ALRMVALH byte, the Alarm Pointer value, ALRMPTR<1:0> bits, decrement by one until they reach '00'. Once they reach '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL until the pointer value is manually changed.

#### TABLE 25-2: ALRMVAL REGISTER MAPPING

| ALRMPTR | Alarm Value Register Window |              |  |  |  |  |

|---------|-----------------------------|--------------|--|--|--|--|

| <1:0>   | ALRMVAL<15:8>               | ALRMVAL<7:0> |  |  |  |  |

| 00      | ALRMMIN                     | ALRMSEC      |  |  |  |  |

| 01      | ALRMWD                      | ALRMHR       |  |  |  |  |

| 10      | ALRMMNTH                    | ALRMDAY      |  |  |  |  |

| 11      | —                           | —            |  |  |  |  |

Considering that the 16-bit core does not distinguish between 8-bit and 16-bit read operations, the user must be aware that when reading either the ALRMVALH or ALRMVALL bytes will decrement the ALRMPTR<1:0> value. The same applies to the RTCVALH or RTCVALL bytes with the RTCPTR<1:0> being decremented.

| Note: | This only applies to read operations and |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|

|       | not write operations.                    |  |  |  |  |  |  |  |  |

## 25.1.2 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RCFGCAL<13>) must be set (refer to Example 25-1).

Note: To avoid accidental writes to the timer, it is recommended that the RTCWREN bit (RCFGCAL<13>) is kept clear at any other time. For the RTCWREN bit to be set, there is only 1 instruction cycle time window allowed between the 55h/AA sequence and the setting of RTCWREN; therefore, it is recommended that code follow the procedure in Example 25-1.

#### EXAMPLE 25-1: SETTING THE RTCWREN BIT

| MOV  | #NVMKEY, W1  | ;move the address of NVMKEY into W1 |

|------|--------------|-------------------------------------|

| MOV  | #0x55, W2    |                                     |

| MOV  | #0xAA, W3    |                                     |

| MOV  | W2, [W1]     | ;start 55/AA sequence               |

| MOV  | W3, [W1]     |                                     |

| BSET | RCFGCAL, #13 | ;set the RTCWREN bit                |

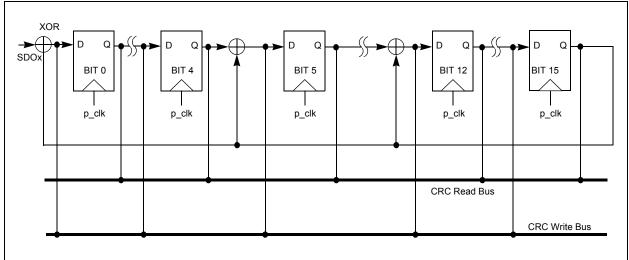

# FIGURE 26-2: CRC GENERATOR RECONFIGURED FOR $x^{16} + x^{12} + x^5 + 1$

## 26.2 User Interface

### 26.2.1 DATA INTERFACE

To start serial shifting, a '1' must be written to the CRCGO bit.

The module incorporates a FIFO that is 8 deep when PLEN (PLEN<3:0>) > 7, and 16 deep, otherwise. The data for which the CRC is to be calculated must first be written into the FIFO. The smallest data element that can be written into the FIFO is one byte. For example, if PLEN = 5, then the size of the data is PLEN + 1 = 6. The data must be written as follows:

```

data[5:0] = crc_input[5:0]

data[7:6] = `bxx

```

Once data is written into the CRCWDAT MSb (as defined by PLEN), the value of VWORD (VWORD<4:0>) increments by one. The serial shifter starts shifting data into the CRC engine when CRCGO = 1 and VWORD > 0. When the MSb is shifted out, VWORD decrements by one. The serial shifter continues shifting until the VWORD reaches 0. Therefore, for a given value of PLEN, it will take (PLEN + 1) \* VWORD number of clock cycles to complete the CRC calculations.

When VWORD reaches 8 (or 16), the CRCFUL bit will be set. When VWORD reaches 0, the CRCMPT bit will be set.

To continually feed data into the CRC engine, the recommended mode of operation is to initially "prime" the FIFO with a sufficient number of words so no interrupt is generated before the next word can be written. Once that is done, start the CRC by setting the CRCGO bit to '1'. From that point onward, the VWORD bits should be polled. If they read less than 8 or 16, another word can be written into the FIFO.

To empty words already written into a FIFO, the CRCGO bit must be set to '1' and the CRC shifter allowed to run until the CRCMPT bit is set.

Also, to get the correct CRC reading, it will be necessary to wait for the CRCMPT bit to go high before reading the CRCWDAT register.

If a word is written when the CRCFUL bit is set, the VWORD Pointer will roll over to 0. The hardware will then behave as if the FIFO is empty. However, the condition to generate an interrupt will not be met; therefore, no interrupt will be generated (See Section 26.2.2 "Interrupt Operation").

At least one instruction cycle must pass after a write to CRCWDAT before a read of the VWORD bits is done.

#### 26.2.2 INTERRUPT OPERATION

When the VWORD4:VWORD0 bits make a transition from a value of '1' to '0', an interrupt will be generated.

# 26.3 Operation in Power-Saving Modes

#### 26.3.1 SLEEP MODE

If Sleep mode is entered while the module is operating, the module will be suspended in its current state until clock execution resumes.

#### 26.3.2 IDLE MODE

To continue full module operation in Idle mode, the CSIDL bit must be cleared prior to entry into the mode.

If CSIDL = 1, the module will behave the same way as it does in Sleep mode; pending interrupt events will be passed on, even though the module clocks are not available.

| Base<br>Instr<br># |        |        | # of<br>Words  | # of<br>Cycles                        | Status Flags<br>Affected |   |                         |

|--------------------|--------|--------|----------------|---------------------------------------|--------------------------|---|-------------------------|

| 66 RRNC            |        | RRNC   | f              | f = Rotate Right (No Carry) f         | 1                        | 1 | N,Z                     |

|                    |        | RRNC   | f,WREG         | WREG = Rotate Right (No Carry) f      | 1                        | 1 | N,Z                     |

|                    |        | RRNC   | Ws,Wd          | Wd = Rotate Right (No Carry) Ws       | 1                        | 1 | N,Z                     |

| 67                 | SAC    | SAC    | Acc,#Slit4,Wdo | Store Accumulator                     | 1                        | 1 | None                    |

|                    |        | SAC.R  | Acc,#Slit4,Wdo | Store Rounded Accumulator             | 1                        | 1 | None                    |

| 68                 | SE     | SE     | Ws,Wnd         | Wnd = sign-extended Ws                | 1                        | 1 | C,N,Z                   |

| 69                 | SETM   | SETM   | f              | f = 0xFFFF                            | 1                        | 1 | None                    |

|                    |        | SETM   | WREG           | WREG = 0xFFFF                         | 1                        | 1 | None                    |

|                    |        | SETM   | Ws             | Ws = 0xFFFF                           | 1                        | 1 | None                    |

| 70                 | SFTAC  | SFTAC  | Acc,Wn         | Arithmetic Shift Accumulator by (Wn)  | 1                        | 1 | OA,OB,OAB,<br>SA,SB,SAB |

|                    |        | SFTAC  | Acc,#Slit6     | Arithmetic Shift Accumulator by Slit6 | 1                        | 1 | OA,OB,OAB<br>SA,SB,SAB  |

| 71                 | SL     | SL     | f              | f = Left Shift f                      | 1                        | 1 | C,N,OV,Z                |

|                    |        | SL     | f,WREG         | WREG = Left Shift f                   | 1                        | 1 | C,N,OV,Z                |

|                    |        | SL     | Ws,Wd          | Wd = Left Shift Ws                    | 1                        | 1 | C,N,OV,Z                |

|                    |        | SL     | Wb,Wns,Wnd     | Wnd = Left Shift Wb by Wns            | 1                        | 1 | N,Z                     |

|                    |        | SL     | Wb,#lit5,Wnd   | Wnd = Left Shift Wb by lit5           | 1                        | 1 | N,Z                     |

| 72                 | SUB    | SUB    | Acc            | Subtract Accumulators                 | 1                        | 1 | OA,OB,OAB<br>SA,SB,SAB  |

|                    |        | SUB    | f              | f = f – WREG                          | 1                        | 1 | C,DC,N,OV,2             |

|                    |        | SUB    | f,WREG         | WREG = f – WREG                       | 1                        | 1 | C,DC,N,OV,2             |

|                    |        | SUB    | #lit10,Wn      | Wn = Wn - lit10                       | 1                        | 1 | C,DC,N,OV,2             |

|                    |        | SUB    | Wb,Ws,Wd       | Wd = Wb – Ws                          | 1                        | 1 | C,DC,N,OV,2             |

|                    |        | SUB    | Wb,#lit5,Wd    | Wd = Wb – lit5                        | 1                        | 1 | C,DC,N,OV,2             |

| 73                 | SUBB   | SUBB   | f              | f = f - WREG - (C)                    | 1                        | 1 | C,DC,N,OV,Z             |

|                    |        | SUBB   | f,WREG         | WREG = $f - WREG - (\overline{C})$    | 1                        | 1 | C,DC,N,OV,Z             |

|                    |        | SUBB   | #lit10,Wn      | $Wn = Wn - lit10 - (\overline{C})$    | 1                        | 1 | C,DC,N,OV,2             |

|                    |        | SUBB   | Wb,Ws,Wd       | $Wd = Wb - Ws - (\overline{C})$       | 1                        | 1 | C,DC,N,OV,2             |

|                    |        | SUBB   | Wb,#lit5,Wd    | $Wd = Wb - Iit5 - (\overline{C})$     | 1                        | 1 | C,DC,N,OV,Z             |

| 74                 | SUBR   | SUBR   | f              | f = WREG – f                          | 1                        | 1 | C,DC,N,OV,Z             |

|                    |        | SUBR   | f,WREG         | WREG = WREG – f                       | 1                        | 1 | C,DC,N,OV,2             |

|                    |        | SUBR   | Wb,Ws,Wd       | Wd = Ws – Wb                          | 1                        | 1 | C,DC,N,OV,2             |

|                    |        | SUBR   | Wb,#lit5,Wd    | Wd = lit5 – Wb                        | 1                        | 1 | C,DC,N,OV,2             |

| 75                 | SUBBR  | SUBBR  | f              | $f = WREG - f - (\overline{C})$       | 1                        | 1 | C,DC,N,OV,Z             |

|                    |        | SUBBR  | f,WREG         | WREG = WREG – f – $(\overline{C})$    | 1                        | 1 | C,DC,N,OV,Z             |

|                    |        | SUBBR  | Wb,Ws,Wd       | $Wd = Ws - Wb - (\overline{C})$       | 1                        | 1 | C,DC,N,OV,Z             |

|                    |        | SUBBR  | Wb,#lit5,Wd    | $Wd = lit5 - Wb - (\overline{C})$     | 1                        | 1 | C,DC,N,OV,Z             |

| 76                 | SWAP   | SWAP.b | Wn             | Wn = nibble swap Wn                   | 1                        | 1 | None                    |

|                    |        | SWAP   | Wn             | Wn = byte swap Wn                     | 1                        | 1 | None                    |

| 77                 | TBLRDH | TBLRDH | Ws,Wd          | Read Prog<23:16> to Wd<7:0>           | 1                        | 2 | None                    |

| 78                 | TBLRDL | TBLRDL | Ws,Wd          | Read Prog<15:0> to Wd                 | 1                        | 2 | None                    |

| 79                 | TBLWTH | TBLWTH | Ws,Wd          | Write Ws<7:0> to Prog<23:16>          | 1                        | 2 | None                    |

| 80                 | TBLWTL | TBLWTL | Ws,Wd          | Write Ws to Prog<15:0>                | 1                        | 2 | None                    |

| 81                 | ULNK   | ULNK   |                | Unlink Frame Pointer                  | 1                        | 1 | None                    |

| 82                 | XOR    | XOR    | f              | f = f .XOR. WREG                      | 1                        | 1 | N,Z                     |

|                    |        | XOR    | f,WREG         | WREG = f .XOR. WREG                   | 1                        | 1 | N,Z                     |

|                    |        | XOR    | #lit10,Wn      | Wd = lit10 .XOR. Wd                   | 1                        | 1 | N,Z                     |

|                    |        | XOR    | Wb,Ws,Wd       | Wd = Wb .XOR. Ws                      | 1                        | 1 | N,Z                     |

|                    |        | XOR    | Wb,#lit5,Wd    | Wd = Wb .XOR. lit5                    | 1                        | 1 | N,Z                     |

| 83                 | ZE     | ZE     | Ws,Wnd         | Wnd = Zero-extend Ws                  | 1                        | 1 | C,Z,N                   |

## TABLE 29-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| AC CHARACTERISTICS |        |                                |           | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |            |           |                                                  |  |

|--------------------|--------|--------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|--------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                 | Min       | Тур                                                                                                                                                                                                      | Max        | Units     | Conditions                                       |  |

|                    |        | ADC Accuracy (10-bit Mode      | e) – Meas | urement                                                                                                                                                                                                  | ts with e  | xternal   | VREF+/VREF-                                      |  |

| AD20b              | Nr     | Resolution <sup>(1)</sup>      | 1(        | ) data bi                                                                                                                                                                                                | ts         | bits      |                                                  |  |