#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc302-e-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.6 CPU Control Registers

|                                                     | NO-1. OK. O                                            |                                                                      |                   |                        |                   |                   |                |  |  |  |

|-----------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------|-------------------|------------------------|-------------------|-------------------|----------------|--|--|--|

| R-0                                                 | R-0                                                    | R/C-0                                                                | R/C-0             | R-0                    | R/C-0             | R -0              | R/W-0          |  |  |  |

| OA                                                  | OB                                                     | SA <sup>(1)</sup>                                                    | SB <sup>(1)</sup> | OAB                    | SAB               | DA                | DC             |  |  |  |

| bit 15                                              |                                                        |                                                                      |                   |                        |                   |                   | bit 8          |  |  |  |

| (0)                                                 | (0)                                                    | (0)                                                                  |                   |                        |                   |                   |                |  |  |  |

| R/W-0 <sup>(3)</sup>                                |                                                        | R/W-0 <sup>(3)</sup>                                                 | R-0               | R/W-0                  | R/W-0             | R/W-0             | R/W-0          |  |  |  |

|                                                     | IPL<2:0> <sup>(2)</sup>                                |                                                                      | RA                | N                      | OV                | Z                 | С              |  |  |  |

| bit 7                                               |                                                        |                                                                      |                   |                        |                   |                   | bit 0          |  |  |  |

| Legend:                                             |                                                        |                                                                      |                   |                        |                   |                   |                |  |  |  |

| C = Clear o                                         | nly bit                                                | R = Readable                                                         | e bit             | U = Unimplei           | mented bit, read  | l as '0'          |                |  |  |  |

| S = Set only bit W = Writable bit -n = Value at POR |                                                        |                                                                      |                   |                        |                   |                   |                |  |  |  |

| '1' = Bit is s                                      | et                                                     | '0' = Bit is clea                                                    | ared              | x = Bit is unk         | nown              |                   |                |  |  |  |

|                                                     |                                                        |                                                                      |                   |                        |                   |                   |                |  |  |  |

| bit 15                                              | OA: Accumul                                            | ator A Overflow                                                      | v Status bit      |                        |                   |                   |                |  |  |  |

|                                                     | 1 = Accumulator A overflowed                           |                                                                      |                   |                        |                   |                   |                |  |  |  |

|                                                     | 0 = Accumulator A has not overflowed                   |                                                                      |                   |                        |                   |                   |                |  |  |  |

| bit 14 OB: Accumulator B Overflow Status bit        |                                                        |                                                                      |                   |                        |                   |                   |                |  |  |  |

|                                                     |                                                        | 1 = Accumulator B overflowed<br>0 = Accumulator B has not overflowed |                   |                        |                   |                   |                |  |  |  |

| bit 13                                              |                                                        | ator A Saturatio                                                     |                   | tus hit(1)             |                   |                   |                |  |  |  |

|                                                     |                                                        | ator A is saturat                                                    |                   |                        | some time         |                   |                |  |  |  |

|                                                     | 0 = Accumula                                           | 0 = Accumulator A is not saturated                                   |                   |                        |                   |                   |                |  |  |  |

| bit 12                                              | SB: Accumul                                            | ator B Saturatio                                                     | on 'Sticky' Sta   | tus bit <sup>(1)</sup> |                   |                   |                |  |  |  |

|                                                     |                                                        | ator B is saturat<br>ator B is not sat                               |                   | en saturated at        | some time         |                   |                |  |  |  |

| bit 11                                              | <b>0AB:</b> 0A    0                                    | B Combined A                                                         | ccumulator C      | verflow Status         | bit               |                   |                |  |  |  |

|                                                     |                                                        | ators A or B hav<br>ccumulators A                                    |                   |                        |                   |                   |                |  |  |  |

| bit 10                                              | <b>SAB:</b> SA    S                                    | B Combined A                                                         | ccumulator (S     | ticky) Status bi       | t <sup>(4)</sup>  |                   |                |  |  |  |

|                                                     | 1 = Accumula                                           |                                                                      | saturated or      | have been sat          | urated at some    | time in the past  | :              |  |  |  |

| bit 9                                               | DA: DO Loop                                            | Active bit                                                           |                   |                        |                   |                   |                |  |  |  |

|                                                     | 1 = DO loop ir                                         |                                                                      |                   |                        |                   |                   |                |  |  |  |

|                                                     | -                                                      | ot in progress                                                       |                   |                        |                   |                   |                |  |  |  |

| bit 8                                               |                                                        | U Half Carry/Bo                                                      |                   |                        |                   |                   |                |  |  |  |

|                                                     |                                                        | out from the 4th sult occurred                                       | low-order bit (   | for byte-sized of      | data) or 8th low- | order bit (for wo | rd-sized data) |  |  |  |

|                                                     | 0 = No carry                                           |                                                                      |                   | bit (for byte-siz      | ed data) or 8th   | low-order bit (f  | or word-sized  |  |  |  |

| Note 1:                                             | This bit can be rea                                    | ad or cleared (n                                                     | ot set).          |                        |                   |                   |                |  |  |  |

| <b>2:</b> 1                                         | The IPL<2:0> bits<br>₋evel. The value iı<br>PL<3> = 1. | are concatenat                                                       | ted with the IF   | •                      | ,                 |                   | • •            |  |  |  |

## REGISTER 3-1: SR: CPU STATUS REGISTER

3: The IPL<2:0> Status bits are read only when the NSTDIS bit (INTCON1<15>) = 1.

4: This bit can be read or cleared (not set). Clearing this bit clears SA and SB.

### 5.6.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to <sup>(0010)</sup> to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

## EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| ; Set up NVMCON for block erase operation |                                          |

|-------------------------------------------|------------------------------------------|

| MOV #0x4042, W0                           | ;                                        |

| MOV W0, NVMCON                            | ; Initialize NVMCON                      |

| ; Init pointer to row to be ERASED        |                                          |

| MOV #tblpage(PROG_ADDR), W0               | ;                                        |

| MOV W0, TBLPAG                            | ; Initialize PM Page Boundary SFR        |

| MOV #tbloffset(PROG_ADDR), W0             | ; Initialize in-page EA[15:0] pointer    |

| TBLWTL W0, [W0]                           | ; Set base address of erase block        |

| DISI #5                                   | ; Block all interrupts with priority < 7 |

|                                           | ; for next 5 instructions                |

| MOV #0x55, W0                             |                                          |

| MOV W0, NVMKEY                            | ; Write the 55 key                       |

| MOV #0xAA, W1                             | ;                                        |

| MOV W1, NVMKEY                            | ; Write the AA key                       |

| BSET NVMCON, #WR                          | ; Start the erase sequence               |

| NOP                                       | ; Insert two NOPs after the erase        |

| NOP                                       | ; command is asserted                    |

|                                           |                                          |

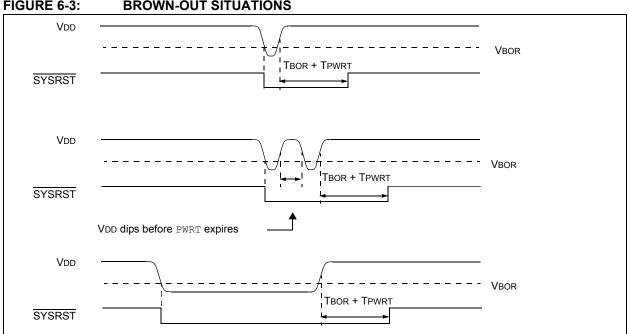

#### **BROWN-OUT SITUATIONS** FIGURE 6-3:

#### 6.5 **External Reset (EXTR)**

The external Reset is generated by driving the MCLR pin low. The MCLR pin is a Schmitt trigger input with an additional glitch filter. Reset pulses that are longer than the minimum pulse width will generate a Reset. Refer to Section 31.0 "Electrical Characteristics" for minimum pulse width specifications. The External Reset (MCLR) Pin bit (EXTR) in the Reset Control register (RCON<7>) is set to indicate the MCLR Reset.

#### EXTERNAL SUPERVISORY CIRCUIT 6.5.0.1

Many systems have external supervisory circuits that generate reset signals to Reset multiple devices in the system. This external Reset signal can be directly connected to the MCLR pin to Reset the device when the rest of system is Reset.

#### 6.5.0.2 INTERNAL SUPERVISORY CIRCUIT

When using the internal power supervisory circuit to Reset the device, the external reset pin (MCLR) should be tied directly or resistively to VDD. In this case, the MCLR pin will not be used to generate a Reset. The external reset pin (MCLR) does not have an internal pull-up and must not be left unconnected.

#### 6.6 Software RESET Instruction (SWR)

Whenever the RESET instruction is executed, the device will assert SYSRST, placing the device in a special Reset state. This Reset state will not re-initialize the clock. The clock source in effect prior to the RESET instruction will remain. SYSRST is released at the next instruction cycle, and the reset vector fetch will commence.

The Software Reset (Instruction) Flag bit (SWR) in the Reset Control register (RCON<6>) is set to indicate the software Reset.

#### 6.7 Watchdog Time-out Reset (WDTO)

Whenever a Watchdog time-out occurs, the device will asynchronously assert SYSRST. The clock source will remain unchanged. A WDT time-out during Sleep or Idle mode will wake-up the processor, but will not reset the processor.

The Watchdog Timer Time-out Flag bit (WDTO) in the Reset Control register (RCON<4>) is set to indicate the Watchdog Reset. Refer to Section 28.4 "Watchdog Timer (WDT)" for more information on Watchdog Reset.

#### 6.8 Trap Conflict Reset

If a lower-priority hard trap occurs while a higher-priority trap is being processed, a hard trap conflict Reset occurs. The hard traps include exceptions of priority level 13 through level 15, inclusive. The address error (level 13) and oscillator error (level 14) traps fall into this category.

The Trap Reset Flag bit (TRAPR) in the Reset Control register (RCON<15>) is set to indicate the Trap Conflict Reset. Refer to Section 7.0 "Interrupt Controller" for more information on trap conflict Resets.

## 7.0 INTERRUPT CONTROLLER

- This data sheet summarizes the features Note 1: of dsPIC33FJ32MC302/304, the dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 32. "Interrupts (Part III)" (DS70214) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) shown in Figure 7-1, resides in program memory, starting at location 000004h. The IVT contains 126 vectors consisting of eight nonmaskable trap vectors plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with vector 0 takes priority over interrupts at any other vector address.

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 devices implement up to 53 unique interrupts and five nonmaskable traps. These are summarized in Table 7-1.

### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 device clears its registers in response to a Reset, which forces the PC to zero. The digital signal controller then begins program execution at location 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

## REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

| bit 2 | CMIF: Comparator Interrupt Flag Status bit                                                          |

|-------|-----------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |

| bit 1 | MI2C1IF: I2C1 Master Events Interrupt Flag Status bit                                               |

|       | 1 = Interrupt request has occurred                                                                  |

|       | 0 = Interrupt request has not occurred                                                              |

| bit 0 | SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit                                                |

|       | <ol> <li>I = Interrupt request has occurred</li> </ol>                                              |

0 = Interrupt request has not occurred

## 11.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See **"Pin Diagrams**" for the available pins and their functionality.

## 11.3 Configuring Analog Port Pins

The AD1PCFGL and TRIS registers control the operation of the analog-to-digital port pins. The port pins that are to function as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

The AD1PCFGL register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

### 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be an NOP, as shown in Example 11-1.

## 11.5 Input Change Notification

The input change notification function of the I/O ports allows the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/ X04 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 21 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a change-ofstate.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on change notification pins should always be disabled when the port pin is configured as a digital output.

### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | OxFFOO, WO | ; | Configure PORTB<15:8> as inputs |

|------|------------|---|---------------------------------|

| MOV  | W0, TRISBB | ; | and PORTB<7:0> as outputs       |

| NOP  |            | ; | Delay 1 cycle                   |

| btss | PORTB, #13 | ; | Next Instruction                |

|      |            |   |                                 |

## dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| REGISTER      | 11-4: RPINF                                | R4: PERIPHEI                                                             | RAL PIN SE    | ELECT INPU           | T REGISTER      | 4               |       |

|---------------|--------------------------------------------|--------------------------------------------------------------------------|---------------|----------------------|-----------------|-----------------|-------|

| U-0           | U-0                                        | U-0                                                                      | R/W-1         | R/W-1                | R/W-1           | R/W-1           | R/W-1 |

| —             | —                                          | _                                                                        |               |                      | T5CKR<4:0       | >               |       |

| bit 15        |                                            | ·                                                                        |               |                      |                 |                 | bit   |

| U-0           | U-0                                        | U-0                                                                      | R/W-1         | R/W-1                | R/W-1           | R/W-1           | R/W-1 |

| _             | _                                          | _                                                                        |               |                      | T4CKR<4:0       | >               |       |

| bit 7         |                                            |                                                                          |               |                      | bit (           |                 |       |

| Legend:       |                                            |                                                                          |               |                      |                 |                 |       |

| R = Readabl   | le bit                                     | W = Writable                                                             | oit           | U = Unimple          | mented bit, rea | ad as '0'       |       |

| -n = Value at | t POR                                      | '1' = Bit is set                                                         |               | '0' = Bit is cleared |                 | x = Bit is unki | nown  |

|               | 11001 = Inpo<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to Vss<br>ut tied to RP25<br>ut tied to RP1<br>ut tied to RP0    |               |                      |                 |                 |       |

| bit 7-5       | Unimplemer                                 | nted: Read as '                                                          | )'            |                      |                 |                 |       |

| bit 4-0       | 11111 = Inpr<br>11001 = Inpr<br>•          | <ul> <li>Assign Timera<br/>ut tied to Vss<br/>ut tied to RP25</li> </ul> | t External Cl | ock (T4CK) to t      | the correspond  | ling RPn pin    |       |

|               |                                            | ut tied to RP1                                                           |               |                      |                 |                 |       |

00000 = Input tied to RP0

## 15.2 Output Compare Resources

Many useful resources related to Output Compare are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

### 15.2.1 KEY RESOURCES

- Section 13. "Output Compare" (DS70209)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

## 15.3 Output Compare Registers

## **REGISTER 15-1:** OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2, 3 or 4)

| bit 15 |     |        |     |     |     |     | bit 8 |

|--------|-----|--------|-----|-----|-----|-----|-------|

|        |     | OCSIDL |     |     |     |     |       |

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

| U-0   | U-0 | U-0 | R-0, HC | R/W-0  | R/W-0 | R/W-0    | R/W-0 |

|-------|-----|-----|---------|--------|-------|----------|-------|

| —     | —   | —   | OCFLT   | OCTSEL |       | OCM<2:0> |       |

| bit 7 |     |     |         |        |       |          | bit 0 |

| Legend:           | HC = Cleared in Hardware | HS = Set in Hardware               |                    |  |  |

|-------------------|--------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Stop Output Compare in Idle Mode Control bit                                                                                                                                             |

|           | 1 = Output Compare x halts in CPU Idle mode                                                                                                                                                      |

|           | 0 = Output Compare x continues to operate in CPU Idle mode                                                                                                                                       |

| bit 12-5  | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                                                                                                                                            |

|           | <ul> <li>1 = PWM Fault condition has occurred (cleared in hardware only)</li> <li>0 = No PWM Fault condition has occurred</li> <li>(This bit is only used when OCM&lt;2:0&gt; = 111).</li> </ul> |

| bit 2     |                                                                                                                                                                                                  |

| bit 3     | OCTSEL: Output Compare Timer Select bit                                                                                                                                                          |

|           | <ol> <li>1 = Timer3 is the clock source for Compare x</li> <li>0 = Timer2 is the clock source for Compare x</li> </ol>                                                                           |

| bit 2-0   | OCM<2:0>: Output Compare Mode Select bits                                                                                                                                                        |

|           | 111 = PWM mode on OCx, Fault pin enabled                                                                                                                                                         |

|           | 110 = PWM mode on OCx, Fault pin disabled                                                                                                                                                        |

|           | 101 = Initialize OCx pin low, generate continuous output pulses on OCx pin                                                                                                                       |

|           | 100 = Initialize OCx pin low, generate single output pulse on OCx pin                                                                                                                            |

|           | 011 = Compare event toggles OCx pin<br>010 = Initialize OCx pin high, compare event forces OCx pin low                                                                                           |

|           | 001 = Initialize OCx pin low, compare event forces OCx pin high                                                                                                                                  |

|           | 000 = Output compare channel is disabled                                                                                                                                                         |

## 21.4 ECAN Resources

Many useful resources related to ECAN are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

### 21.4.1 KEY RESOURCES

- Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70185)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| U-0                 | U-0                                                                                               | R-0                                                                                                               | R-0              | R-0                             | R-0                | R-0             | R-0   |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------|--------------------|-----------------|-------|--|--|--|--|

| _                   |                                                                                                   | ТХВО                                                                                                              | TXBP             | RXBP                            | TXWAR              | RXWAR           | EWARN |  |  |  |  |

| bit 15              |                                                                                                   | .,                                                                                                                |                  |                                 |                    |                 | bit 8 |  |  |  |  |

|                     |                                                                                                   |                                                                                                                   |                  |                                 |                    |                 |       |  |  |  |  |

| R/C-0               | R/C-0                                                                                             | R/C-0                                                                                                             | U-0              | R/C-0                           | R/C-0              | R/C-0           | R/C-0 |  |  |  |  |

| IVRIF               | WAKIF                                                                                             | ERRIF                                                                                                             | _                | FIFOIF                          | RBOVIF             | RBIF            | TBIF  |  |  |  |  |

| bit 7               | •                                                                                                 |                                                                                                                   | L                |                                 |                    |                 | bit C |  |  |  |  |

|                     |                                                                                                   |                                                                                                                   |                  |                                 |                    |                 |       |  |  |  |  |

| Legend:             |                                                                                                   | C = Writable                                                                                                      | bit, but only '0 |                                 | n to clear the bit |                 |       |  |  |  |  |

| R = Readabl         | le bit                                                                                            | W = Writable                                                                                                      | bit              | -                               | mented bit, read   |                 |       |  |  |  |  |

| -n = Value at       | POR                                                                                               | '1' = Bit is set                                                                                                  |                  | '0' = Bit is cle                | eared              | x = Bit is unkr | nown  |  |  |  |  |

| 6:4 A F A A         |                                                                                                   | ted. Deed oo f                                                                                                    | 0'               |                                 |                    |                 |       |  |  |  |  |

| bit 15-14<br>bit 13 | -                                                                                                 | i <b>ted:</b> Read as '<br>mitter in Error                                                                        |                  | hit                             |                    |                 |       |  |  |  |  |

| DIE 13              |                                                                                                   | er is in Bus Of                                                                                                   |                  | DIL                             |                    |                 |       |  |  |  |  |

|                     |                                                                                                   | er is not in Bus                                                                                                  |                  |                                 |                    |                 |       |  |  |  |  |

| bit 12              | TXBP: Trans                                                                                       | mitter in Error                                                                                                   | State Bus Pas    | sive bit                        |                    |                 |       |  |  |  |  |

|                     | 1 = Transmitt                                                                                     | er is in Bus Pa                                                                                                   | ssive state      |                                 |                    |                 |       |  |  |  |  |

|                     |                                                                                                   | er is not in Bus                                                                                                  |                  |                                 |                    |                 |       |  |  |  |  |

| bit 11              |                                                                                                   | ver in Error Sta                                                                                                  |                  | ve bit                          |                    |                 |       |  |  |  |  |

|                     |                                                                                                   | 1 = Receiver is in Bus Passive state<br>0 = Receiver is not in Bus Passive state                                  |                  |                                 |                    |                 |       |  |  |  |  |

| bit 10              |                                                                                                   |                                                                                                                   |                  | na hit                          |                    |                 |       |  |  |  |  |

|                     | <b>TXWAR:</b> Transmitter in Error State Warning bit<br>1 = Transmitter is in Error Warning state |                                                                                                                   |                  |                                 |                    |                 |       |  |  |  |  |

|                     |                                                                                                   | 0 = Transmitter is not in Error Warning state                                                                     |                  |                                 |                    |                 |       |  |  |  |  |

| bit 9               | RXWAR: Red                                                                                        | eiver in Error                                                                                                    | State Warning    | bit                             |                    |                 |       |  |  |  |  |

|                     | 1 = Receiver is in Error Warning state                                                            |                                                                                                                   |                  |                                 |                    |                 |       |  |  |  |  |

| 1.11.0              |                                                                                                   | is not in Error                                                                                                   | -                |                                 |                    |                 |       |  |  |  |  |

| bit 8               |                                                                                                   |                                                                                                                   |                  | State Warning<br>te Warning sta |                    |                 |       |  |  |  |  |

|                     |                                                                                                   |                                                                                                                   |                  | State Warning                   |                    |                 |       |  |  |  |  |

| bit 7               |                                                                                                   |                                                                                                                   |                  |                                 | ,                  |                 |       |  |  |  |  |

|                     | IVRIF: Invalid Message Received Interrupt Flag bit<br>1 = Interrupt Request has occurred          |                                                                                                                   |                  |                                 |                    |                 |       |  |  |  |  |

|                     | 0 = Interrupt I                                                                                   | Request has n                                                                                                     | ot occurred      |                                 |                    |                 |       |  |  |  |  |

| bit 6               | WAKIF: Bus                                                                                        | Wake-up Activ                                                                                                     | ity Interrupt Fl | ag bit                          |                    |                 |       |  |  |  |  |

|                     | <ol> <li>Interrupt Request has occurred</li> <li>Interrupt Request has not occurred</li> </ol>    |                                                                                                                   |                  |                                 |                    |                 |       |  |  |  |  |

| bit 5               |                                                                                                   | -                                                                                                                 |                  | ourcos in CilNT                 | TE<12.8> rogist    | or)             |       |  |  |  |  |

| DIL D               |                                                                                                   | ERRIF: Error Interrupt Flag bit (multiple sources in CiINTF<13:8> register)<br>1 = Interrupt Request has occurred |                  |                                 |                    |                 |       |  |  |  |  |

|                     |                                                                                                   | Request has n                                                                                                     |                  |                                 |                    |                 |       |  |  |  |  |

| bit 4               | -                                                                                                 | ted: Read as '                                                                                                    |                  |                                 |                    |                 |       |  |  |  |  |

| bit 3               | •                                                                                                 | Almost Full In                                                                                                    |                  | it                              |                    |                 |       |  |  |  |  |

|                     |                                                                                                   | Request has o                                                                                                     |                  |                                 |                    |                 |       |  |  |  |  |

|                     | 0 = Interrupt I                                                                                   | 0 = Interrupt Request has not occurred                                                                            |                  |                                 |                    |                 |       |  |  |  |  |

| bit 2               |                                                                                                   | Buffer Overflo                                                                                                    | -                | ag bit                          |                    |                 |       |  |  |  |  |

|                     |                                                                                                   | Request has o                                                                                                     |                  |                                 |                    |                 |       |  |  |  |  |

| <b>L:1</b>          | -                                                                                                 | Request has n                                                                                                     |                  |                                 |                    |                 |       |  |  |  |  |

| bit 1               |                                                                                                   | ffer Interrupt Fl<br>Request has o                                                                                |                  |                                 |                    |                 |       |  |  |  |  |

|                     |                                                                                                   | Request has n                                                                                                     |                  |                                 |                    |                 |       |  |  |  |  |

| bit 0               | -                                                                                                 | fer Interrupt Fl                                                                                                  |                  |                                 |                    |                 |       |  |  |  |  |

|                     |                                                                                                   | Request has o                                                                                                     |                  |                                 |                    |                 |       |  |  |  |  |

|                     |                                                                                                   |                                                                                                                   |                  |                                 |                    |                 |       |  |  |  |  |

## 24.1 Comparator Resources

Many useful resources related to Comparators are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwprod-<br>ucts/Devices.aspx?dDoc-<br>Name=en532315                                  |

### 24.1.1 KEY RESOURCES

- Section 34. "Comparators" (DS70212)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| REGISTER 25-4: | RTCVAL | (WHEN RTCPTR<1:0> = 11): YEAR VALUE REGISTER <sup>(1)</sup> |

|----------------|--------|-------------------------------------------------------------|

|----------------|--------|-------------------------------------------------------------|

|                 |       |                  |       | -                |                  |                 |       |  |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|-------|--|

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |  |

| —               | _     | —                |       | —                | _                | _               | _     |  |

| bit 15          |       |                  |       |                  |                  |                 | bit 8 |  |

|                 |       |                  |       |                  |                  |                 |       |  |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x            | R/W-x           | R/W-x |  |

|                 | YRTE  | N<3:0>           |       | YRONE<3:0>       |                  |                 |       |  |

| bit 7           |       |                  |       |                  |                  |                 | bit 0 |  |

|                 |       |                  |       |                  |                  |                 |       |  |

| Legend:         |       |                  |       |                  |                  |                 |       |  |

| R = Readable b  | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, read | 1 as '0'        |       |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |

bit 15-8 Unimplemented: Read as '0'

bit 7-4 YRTEN<3:0>: Binary Coded Decimal Value of Year's Tens Digit; contains a value from 0 to 9

bit 3-0 YRONE<3:0>: Binary Coded Decimal Value of Year's Ones Digit; contains a value from 0 to 9

**Note 1:** A write to the YEAR register is only allowed when RTCWREN = 1.

## REGISTER 25-5: RTCVAL (WHEN RTCPTR<1:0> = 10): MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R-x     | R-x | R-x   | R-x     | R-x   |

|--------|-----|-----|---------|-----|-------|---------|-------|

| —      | —   | —   | MTHTEN0 |     | MTHON | IE<3:0> |       |

| bit 15 |     |     |         |     |       |         | bit 8 |

| U-0   | U-0 | R/W-x | R/W-x  | R/W-x | R/W-x | R/W-x   | R/W-x |

|-------|-----|-------|--------|-------|-------|---------|-------|

| —     | —   | DAYTE | N<1:0> |       | DAYON | IE<3:0> |       |

| bit 7 |     |       |        |       |       |         | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12 MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit; contains a value of 0 or 1

bit 11-8MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit; contains a value from 0 to 9bit 7-6Unimplemented: Read as '0'

bit 5-4 DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit; contains a value from 0 to 3

bit 3-0 DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit; contains a value from 0 to 9

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

## TABLE 28-5: CODE FLASH SECURITY SEGMENT SIZES FOR 128 KB DEVICES

| CONFIG BITS           | BSS<2:0> = x11 0K                                                                                                                                                                                                                                                                                                                                                                                                                              | BSS<2:0> = x10 1K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BSS<2:0> = x01 4K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | BSS<2:0> = x00 8K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSS<2:0> = x11<br>0K  | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>002000h<br>003FFEh<br>004000h<br>007FFEh           GS = 43776 IW         000000h<br>005FFEh           0157FEh                                                                                                                                                                                                                                            | VS = 256 IW         000000h           BS = 768 IW         000200h           0007FEh         000800h           001FFEh         00200h           003FFEh         003FFEh           004000h         007FFEh           000300h         0007FFEh           00000h         0007FFEh           00000h         007FFEh           00000h         007FFEh           00800h         007FFEh | VS = 256 IW         000000h           BS = 3840 IW         000200h           000800h         0007FEh           000200h         0003FFEh           003400h         003FFEh           00800h         007FFEh           000200h         003FFEh           00800h         007FFEh                                                                                                                                                 | VS = 256 IW         000000h           BS = 7936 IW         000200h           000800h         0007FEh           000800h         001FFEh           002200h         003FFEh           0037FEh         004000h           0037FEh         004000h           003FFEh         004000h           007FFEh         008000h           007FFEh         008000h           007FFEh         008000h           007FFEh         010000h           0157FEh         0157FEh                                                                                                                                                                                                                                                 |

| SSS<2:0> = x10<br>4K  | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>002000h           SS = 3840 IW         000800h<br>001FFEh<br>002000h           GS = 39936 IW         0157FEh                                                                                                                                                                                                                                             | VS = 256 IW         000000h           BS = 768 IW         000200h           SS = 3072 IW         0001FEh           000800h         001FFEh           0003FEh         002000h           003FFEh         002000h           003FFEh         004000h           007FFEh         004000h           007FFEh         008000h           007FFEh         004000h           007FFEh         008000h           004000h         007FFEh           008000h         000ABFEh           000800h         00157FEh                                                                                       | VS = 256 IW         000000h<br>0001FEh           BS = 3840 IW         000200h<br>0007FEh           000200h         001FFEh           003FFEh         004000h           004000h         003FFEh           004000h         003FFEh           004000h         003FFEh           004000h         000ABFEh           00000h         003FFEh           004000h         000ABFEh           00000h         001FFEh           004000h         001FFEh           00157FEh         0157FEh                                                                                                                                                                                      | VS = 256 IW         000000h           BS = 7936 IW         000200h           0007FEh         000800h           001FEFh         000200h           001FEFh         000200h           003FFEh         00200h           003FFEh         00200h           003FFEh         004000h           007FFEh         004000h           007FFEh         004000h           007FFEh         008000h           0004000h         0007FFEh           004000h         007FFEh           0004000h         007FFEh           004000h         007FFEh           004000h         007FFEh           004000h         007FFEh           004000h         007FFEh           004000h         007FFEh           004000h         0007FFEh |

| SSS<2:0> = x01<br>8K  | VS = 256 IW         000000h           0001FEh         000200h           0007FEh         000800h           001FFEh         001FFEh           002000h         001FFEh           003FFEh         004000h           004000h         007FFEh           00800h         007FFEh           00800h         007FFEh           00800h         00FFFEh           00800h         00FFFEh           00800h         00FFFEh           010000h         0157FEh | VS = 256 IW         000000h           BS = 768 IW         000200h           0007FEh         000800h           001FFEh         000300h           SS = 7168 IW         003FFEh           004000h         003FFEh           0007FEh         004000h           007FFEh         004000h           007FFEh         008000h           007FFEh         008000h           007FFEh         008000h           007FFEh         008000h           005FFFEh         008000h           005FFFEh         010000h           0157FEh         0157FEh                                                     | VS = 256 IW         000000h           BS = 3840 IW         0007FEh           000800h         0007FEh           000800h         001FFEh           000200h         003FFEh           003500h         003FFEh           000800h         003FFEh           007FFEh         004000h           007FFEh         008000h           007FFEh         010000h | VS = 256 IW         000000h           BS = 7936 IW         0007FEh           000800h         0007FEh           000800h         001FFEh           0022000h         003FFEh           003FFEh         004000h           007FFEh         008000h           007FFEh         004000h           007FFEh         004000h           007FFEh         004000h           007FFEh         008000h           007FFEh         008000h           007FFEh         010000h           0157FEh         0157FEh                                                                                                                                                                                                              |

| SSS<2:0> = x00<br>16K | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FFEh<br>002000h<br>003FFEh<br>004000h<br>007FFEh           SS = 16128 IW         004000h<br>007FFEh<br>008000h<br>007FFEh           GS = 27648 IW         0157FEh                                                                                                                                                                                                | VS = 256 IW         000000h           BS = 768 IW         000200h           0007FEh         000800h           001FFEh         0002000h           003FFEh         002000h           003FFEh         004000h           0044000h         007FFEh           008000h         007FFEh           0010000h         007FFFEh                                                        | VS = 256 IW         000000h           BS = 3840 IW         000200h           000800h         0007FEh           000800h         001FFEh           0035FEh         00200h           0035FEh         004000h           007FFEh         00800h           0037FEh         0037FEh           008000h         007FFEh                                                                       | VS = 256 IW         000000h<br>0001FEh<br>000200h<br>0007FEh<br>000800h<br>001FEFh<br>002000h           SS = 7936 IW         000200h<br>003FFEh<br>002000h           SS = 8192 IW         004000h<br>007FFEh<br>008000h           GS = 27648 IW         0157FEh                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                     | Description                            | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------|-------------------------------------|----------------------------------------|---------------|----------------|--------------------------|

| 29                 | DIV                  | DIV.S  | Wm,Wn                               | Signed 16/16-bit Integer Divide        | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.SD | Wm,Wn                               | Signed 32/16-bit Integer Divide        | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.U  | Wm,Wn                               | Unsigned 16/16-bit Integer Divide      | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.UD | Wm,Wn                               | Unsigned 32/16-bit Integer Divide      | 1             | 18             | N,Z,C,OV                 |

| 30                 | DIVF                 | DIVF   | Wm,Wn                               | Signed 16/16-bit Fractional Divide     | 1             | 18             | N,Z,C,OV                 |

| 31                 | DO                   | DO     | #lit14,Expr                         | Do code to PC + Expr, lit14 + 1 times  | 2             | 2              | None                     |

|                    |                      | DO     | Wn,Expr                             | Do code to PC + Expr, (Wn) + 1 times   | 2             | 2              | None                     |

| 32                 | ED                   | ED     | Wm*Wm,Acc,Wx,Wy,Wxd                 | Euclidean Distance (no accumulate)     | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

| 33                 | EDAC                 | EDAC   | Wm*Wm,Acc,Wx,Wy,Wxd                 | Euclidean Distance                     | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

| 34                 | EXCH                 | EXCH   | Wns,Wnd                             | Swap Wns with Wnd                      | 1             | 1              | None                     |

| 35                 | FBCL                 | FBCL   | Ws,Wnd                              | Find Bit Change from Left (MSb) Side   | 1             | 1              | С                        |

| 36                 | FF1L                 | FF1L   | Ws,Wnd                              | Find First One from Left (MSb) Side    | 1             | 1              | С                        |

| 37                 | FF1R                 | FF1R   | Ws,Wnd                              | Find First One from Right (LSb) Side   | 1             | 1              | С                        |

| 38                 | GOTO                 | GOTO   | Expr                                | Go to address                          | 2             | 2              | None                     |

|                    |                      | GOTO   | Wn                                  | Go to indirect                         | 1             | 2              | None                     |

| 39                 | INC                  | INC    | f                                   | f = f + 1                              | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC    | f,WREG                              | WREG = f + 1                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC    | Ws,Wd                               | Wd = Ws + 1                            | 1             | 1              | C,DC,N,OV,Z              |

| 40                 | INC2                 | INC2   | f                                   | f = f + 2                              | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC2   | f,WREG                              | WREG = f + 2                           | 1             | 1              | C,DC,N,OV,Z              |