Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc302t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Pin Diagrams (Continued)

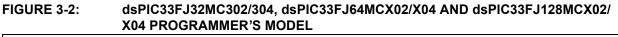

#### 3.3 DSP Engine Overview

The DSP engine features a high-speed 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner by dedicating certain working registers to each address space.

#### 3.4 Special MCU Features

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 features a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0).

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 supports 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

#### TABLE 4-12: I2C1 REGISTER MAP

| SFR Name                                                                                                   | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8                        | Bit 7              | Bit 6 | Bit 5   | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------------------------------------------------------------------------------------------------------|------|---------|--------|---------|--------|--------|--------|-----------------------|------------------------------|--------------------|-------|---------|----------|-------|-------|-------|-------|---------------|

| I2C1RCV                                                                                                    | 0200 | _       | -      |         | _      | _      |        | _                     |                              | - Receive Register |       |         |          |       | 0000  |       |       |               |

| I2C1TRN                                                                                                    | 0202 | _       | _      |         | —      | —      |        | —                     | — — Transmit Register        |                    |       |         |          | OOFF  |       |       |       |               |

| I2C1BRG                                                                                                    | 0204 | _       | _      |         | —      | —      |        | —                     | Baud Rate Generator Register |                    |       |         |          | 0000  |       |       |       |               |

| I2C1CON                                                                                                    | 0206 | I2CEN   |        | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                | SMEN                         | GCEN               | STREN | ACKDT   | ACKEN    | RCEN  | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT                                                                                                   | 0208 | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                | ADD10                        | IWCOL              | I2COV | D_A     | Р        | S     | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD                                                                                                    | 020A | -       | _      | _       | _      | _      | _      |                       |                              |                    |       | Address | Register |       |       |       |       | 0000          |

| I2C1MSK                                                                                                    | 020C | -       | _      | _       | _      | _      | _      | Address Mask Register |                              |                    |       |         | 0000     |       |       |       |       |               |

| Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |      |         |        |         |        |        |        |                       |                              |                    |       |         |          |       |       |       |       |               |

#### TABLE 4-13: UART1 REGISTER MAP

| SFR Name | Addr | Bit 15   | Bit 14                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                         | Bit 6  | Bit 5 | Bit 4      | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|------|----------|-------------------------------|----------|--------|--------|--------|-------|-------|-----------------------------------------------|--------|-------|------------|--------------|-------|--------|-------|---------------|

| U1MODE   | 0220 | UARTEN   | —                             | USIDL    | IREN   | RTSMD  |        | UEN1  | UEN0  | WAKE                                          | LPBACK | ABAUD | URXINV     | BRGH         | PDSE  | _<1:0> | STSEL | 0000          |

| U1STA    | 0222 | UTXISEL1 | UTXINV                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL<1:0> ADDEN RIDLE PERR FERR OERR URXDA |        |       |            | 0110         |       |        |       |               |

| U1TXREG  | 0224 | _        | _                             | _        | _      | _      | _      | _     | UTX8  |                                               |        | U     | ART Transm | nit Register |       |        |       | XXXX          |

| U1RXREG  | 0226 | _        | _                             | _        | _      | _      | _      | _     | URX8  | UART Received Register                        |        |       |            |              | 0000  |        |       |               |

| U1BRG    | 0228 |          | Baud Rate Generator Prescaler |          |        |        |        |       |       |                                               | 0000   |       |            |              |       |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-14: UART2 REGISTER MAP

| SFR Name | Addr | Bit 15   | Bit 14                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                 | Bit 6   | Bit 5 | Bit 4      | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|------|----------|-------------------------------|----------|--------|--------|--------|-------|-------|-----------------------|---------|-------|------------|--------------|-------|--------|-------|---------------|

| U2MODE   | 0230 | UARTEN   |                               | USIDL    | IREN   | RTSMD  |        | UEN1  | UEN0  | WAKE                  | LPBACK  | ABAUD | URXINV     | BRGH         | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA    | 0232 | UTXISEL1 | UTXINV                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISE                | EL<1:0> | ADDEN | RIDLE      | PERR         | FERR  | OERR   | URXDA | 0110          |

| U2TXREG  | 0234 | —        |                               | —        |        | —      |        |       | UTX8  |                       |         | U     | ART Transm | nit Register |       |        |       | XXXX          |

| U2RXREG  | 0236 | —        |                               | —        |        | —      |        |       | URX8  | UART Receive Register |         |       |            |              | 0000  |        |       |               |

| U2BRG    | 0238 |          | Baud Rate Generator Prescaler |          |        |        |        |       |       |                       |         | 0000  |            |              |       |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

#### TABLE 4-40: FUNDAMENTAL ADDRESSING MODES SUPPORTED

#### 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than any other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing mode specified in the instruction can differ |

|-------|---------------------------------------------------------------------------------------|

|       | for the source and destination EA.                                                    |

|       | However, the 4-bit Wb (Register Offset)                                               |

|       | field is shared by both source and                                                    |

|       | destination (but typically only used by                                               |

|       | one).                                                                                 |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

Note: Not all instructions support all the addressing modes listed above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the data pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The effective addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

| Note: | Register    | Indirect | with    | Register   | Offset |

|-------|-------------|----------|---------|------------|--------|

|       | Addressing  | g mode i | s avai  | lable only | for W9 |

|       | (in X space | e) and W | /11 (in | Y space).  |        |

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.5.5 OTHER INSTRUCTIONS

Apart from the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas, the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| ; Set up NVMCON for row programming oper | ations                                    |

|------------------------------------------|-------------------------------------------|

| MOV #0x4001, W0                          | ;                                         |

| MOV W0, NVMCON                           | ; Initialize NVMCON                       |

| ; Set up a pointer to the first program  | memory location to be written             |

| ; program memory selected, and writes en | abled                                     |

| MOV #0x0000, W0                          | ;                                         |

| MOV W0, TBLPAG                           | ; Initialize PM Page Boundary SFR         |

| MOV #0x6000, W0                          | ; An example program memory address       |

| ; Perform the TBLWT instructions to writ | e the latches                             |

| ; Oth_program_word                       |                                           |

| MOV #LOW_WORD_0, W2                      | ;                                         |

| MOV #HIGH_BYTE_0, W3                     | ;                                         |

|                                          | ; Write PM low word into program latch    |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch   |

| ; 1st_program_word                       |                                           |

| MOV #LOW_WORD_1, W2                      | ;                                         |

| MOV #HIGH_BYTE_1, W3                     | ;                                         |

|                                          | ; Write PM low word into program latch    |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch   |

| ; 2nd_program_word                       |                                           |

| MOV #LOW_WORD_2, W2                      | ;                                         |

| MOV #HIGH_BYTE_2, W3                     | ;                                         |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch    |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch   |

| •                                        |                                           |

| •                                        |                                           |

| •                                        |                                           |

| ; 63rd_program_word                      |                                           |

| MOV #LOW_WORD_31, W2                     | ;                                         |

| MOV #HIGH_BYTE_31, W3                    | i . Maite DM les send into program letter |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch    |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch   |

|                                          |                                           |

#### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | ; Block all interrupts with priority < 7<br>; for next 5 instructions |

|------|-------------|-----------------------------------------------------------------------|

| MOIT | #0FF 140    | ; for next 5 instructions                                             |

| MOV  | #0x55, W0   |                                                                       |

| MOV  | W0, NVMKEY  | ; Write the 55 key                                                    |

| MOV  | #0xAA, W1   | ;                                                                     |

| MOV  | W1, NVMKEY  | ; Write the AA key                                                    |

| BSET | NVMCON, #WR | ; Start the erase sequence                                            |

| NOP  |             | ; Insert two NOPs after the                                           |

| NOP  |             | ; erase command is asserted                                           |

|      |             |                                                                       |

| REGISTER     | 7-7: IFS2:                                                                                                                                                                             | NTERRUPT                          | FLAG STAT        | US REGISTI          | ER 2                  |                |         |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|---------------------|-----------------------|----------------|---------|--|--|--|

| U-0          | R/W-0                                                                                                                                                                                  | R/W-0                             | U-0              | U-0                 | U-0                   | U-0            | U-0     |  |  |  |

|              | DMA4IF                                                                                                                                                                                 | PMPIF                             |                  | —                   |                       | _              | _       |  |  |  |

| bit 15       |                                                                                                                                                                                        |                                   |                  |                     |                       |                | bit     |  |  |  |

| U-0          | U-0                                                                                                                                                                                    | U-0                               | R/W-0            | R/W-0               | R/W-0                 | R/W-0          | R/W-0   |  |  |  |

|              | _                                                                                                                                                                                      | _                                 | DMA3IF           | C1IF <sup>(1)</sup> | C1RXIF <sup>(1)</sup> | SPI2IF         | SPI2EIF |  |  |  |

| bit 7        |                                                                                                                                                                                        |                                   |                  |                     |                       |                | bit     |  |  |  |

| Legend:      |                                                                                                                                                                                        |                                   |                  |                     |                       |                |         |  |  |  |

| R = Readab   | le bit                                                                                                                                                                                 | W = Writable                      | bit              | U = Unimplei        | mented bit, read      | as '0'         |         |  |  |  |

| -n = Value a | t POR                                                                                                                                                                                  | '1' = Bit is se                   | t                | '0' = Bit is cle    | eared                 | x = Bit is unk | nown    |  |  |  |

| bit 14       | <ul> <li>DMA4IF: DMA Channel 4 Data Transfer Complete Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                   |                  |                     |                       |                |         |  |  |  |

|              | •                                                                                                                                                                                      | •                                 |                  |                     |                       |                |         |  |  |  |

| bit 13       |                                                                                                                                                                                        |                                   | t Interrupt Flag | Status bit          |                       |                |         |  |  |  |

|              |                                                                                                                                                                                        | request has ou<br>request has no  |                  |                     |                       |                |         |  |  |  |

| bit 12-5     | •                                                                                                                                                                                      | ted: Read as                      |                  |                     |                       |                |         |  |  |  |

| bit 4        | DMA3IF: DM                                                                                                                                                                             | A Channel 3 E                     | Data Transfer C  | Complete Interr     | rupt Flag Status I    | oit            |         |  |  |  |

|              |                                                                                                                                                                                        | request has or                    |                  |                     |                       |                |         |  |  |  |

|              | •                                                                                                                                                                                      | request has no                    |                  | (4)                 |                       |                |         |  |  |  |

| bit 3        |                                                                                                                                                                                        |                                   | pt Flag Status   | bit <sup>(1)</sup>  |                       |                |         |  |  |  |

|              |                                                                                                                                                                                        | request has ou<br>request has no  |                  |                     |                       |                |         |  |  |  |

| bit 2        | •                                                                                                                                                                                      | •                                 | Data Ready Inte  | errupt Flag Sta     | itus bit(1)           |                |         |  |  |  |

| 5112         |                                                                                                                                                                                        | request has or                    |                  | on up thing out     |                       |                |         |  |  |  |

|              |                                                                                                                                                                                        | request has no                    |                  |                     |                       |                |         |  |  |  |

| bit 1        | SPI2IF: SPI2 Event Interrupt Flag Status bit                                                                                                                                           |                                   |                  |                     |                       |                |         |  |  |  |

|              | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>                                                                                 |                                   |                  |                     |                       |                |         |  |  |  |

| <b>h</b> # 0 | •                                                                                                                                                                                      | •                                 |                  | L:4                 |                       |                |         |  |  |  |

| bit 0        |                                                                                                                                                                                        | 2 Error Interru<br>request has or | pt Flag Status   | JIQ                 |                       |                |         |  |  |  |

|              |                                                                                                                                                                                        | request has oc                    |                  |                     |                       |                |         |  |  |  |

|              |                                                                                                                                                                                        |                                   |                  |                     |                       |                |         |  |  |  |

# REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

Note 1: Interrupts are disabled on devices without an ECAN<sup>™</sup> module.

| U-0                                | R/W-1              | R/W-0                                  | R/W-0         | U-0              | R/W-1           | R/W-0           | R/W-0 |

|------------------------------------|--------------------|----------------------------------------|---------------|------------------|-----------------|-----------------|-------|

| _                                  |                    | U2TXIP<2:0>                            |               | —                |                 | U2RXIP<2:0>     |       |

| bit 15                             |                    |                                        |               |                  |                 |                 | bit 8 |

| U-0                                | R/W-1              | R/W-0                                  | R/W-0         | U-0              | R/W-1           | R/W-0           | R/W-0 |

| _                                  |                    | INT2IP<2:0>                            |               | _                |                 | T5IP<2:0>       |       |

| bit 7                              |                    |                                        |               |                  |                 |                 | bit C |

| Legend:                            |                    |                                        |               |                  |                 |                 |       |

| R = Readab                         | le bit             | W = Writable                           | bit           | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value at POR '1' = Bit is set |                    |                                        |               | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

| hit 1E                             | Unimplomo          | nted: Dood oo '                        | o'            |                  |                 |                 |       |

| bit 15                             | -                  | nted: Read as '                        |               |                  |                 |                 |       |

| bit 14-12                          |                    | >: UART2 Trans<br>upt is priority 7 (  |               |                  |                 |                 |       |

|                                    | •                  | -prio piioiii) i (                     |               | .,               |                 |                 |       |

|                                    | •                  |                                        |               |                  |                 |                 |       |

|                                    | •                  | unt in priority 1                      |               |                  |                 |                 |       |

|                                    |                    | upt is priority 1<br>upt source is dis | abled         |                  |                 |                 |       |

| bit 11                             |                    | nted: Read as '                        |               |                  |                 |                 |       |

| bit 10-8                           | -                  | >: UART2 Rece                          |               | Priority bits    |                 |                 |       |

|                                    |                    | upt is priority 7 (                    | •             | •                |                 |                 |       |

|                                    | •                  |                                        | <b>5</b>      | -,,              |                 |                 |       |

|                                    | •                  |                                        |               |                  |                 |                 |       |

|                                    | •<br>001 - Interru | upt is priority 1                      |               |                  |                 |                 |       |

|                                    |                    | upt is priority if                     | abled         |                  |                 |                 |       |

| bit 7                              |                    | nted: Read as '                        |               |                  |                 |                 |       |

| bit 6-4                            | -                  | : External Inter                       |               | bits             |                 |                 |       |

|                                    |                    | upt is priority 7 (                    |               |                  |                 |                 |       |

|                                    | •                  | -prio piioiii) i (                     |               | .,               |                 |                 |       |

|                                    | •                  |                                        |               |                  |                 |                 |       |

|                                    | •                  | unt in uniquity d                      |               |                  |                 |                 |       |

|                                    |                    | upt is priority 1<br>upt source is dis | abled         |                  |                 |                 |       |

| bit 3                              |                    | nted: Read as '                        |               |                  |                 |                 |       |

| bit 2-0                            | -                  | Timer5 Interrupt                       |               |                  |                 |                 |       |

|                                    |                    | upt is priority 7 (                    | -             | ty interrunt)    |                 |                 |       |

|                                    | •                  |                                        | giloot priori | , interrupt)     |                 |                 |       |

• • 001 = Interrupt is priority 1

000 = Interrupt source is disabled

© 2007-2012 Microchip Technology Inc.

#### 7.6 Interrupt Setup Procedures

#### 7.6.1 INITIALIZATION

To configure an interrupt source at initialization:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level depends on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources can be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized such that all user interrupt sources are assigned to priority level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

#### 7.6.2 INTERRUPT SERVICE ROUTINE

The method used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (C or assembler) and the language development tool suite used to develop the application.

In general, the user application must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the program re-enters the ISR immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.6.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.6.4 INTERRUPT DISABLE

All user interrupts can be disabled using this procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the  ${\tt POP}$  instruction can be used to restore the previous SR value.

| Note: | Only user interrupts with a priority level of |

|-------|-----------------------------------------------|

|       | 7 or lower can be disabled. Trap sources      |

|       | (level 8-level 15) cannot be disabled.        |

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

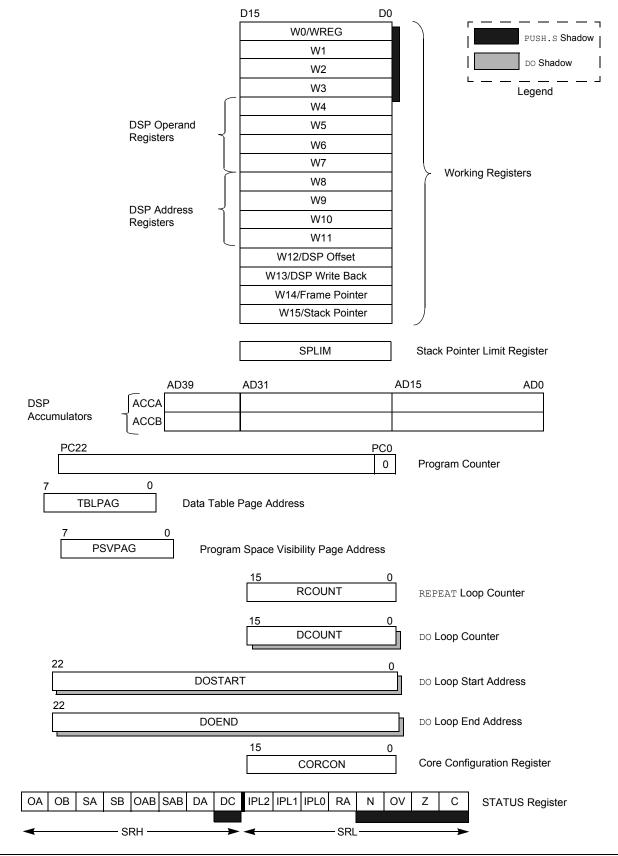

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features dsPIC33FJ32MC302/304, of the dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 39. "Oscillator (Part III)" (DS70216) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 oscillator system provides:

- External and internal oscillator options as clock sources

- An on-chip Phase-Locked Loop (PLL) to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- · Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Non-volatile Configuration bits for main oscillator selection

- · An auxiliary crystal oscillator for audio DAC

- A simplified diagram of the oscillator system is shown in Figure 9-1.

#### **REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)**

- bit 2 Unimplemented: Read as '0'

- bit 1 C1MD: ECAN1 Module Disable bit

- 1 = ECAN1 module is disabled

- 0 = ECAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit

- 1 = ADC1 module is disabled 0 = ADC1 module is enabled

#### REGISTER 11-23: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| -n = Value at P                   | OR  | '1' = Bit is set | set '0' = Bit is cleared x = Bit is unknown |                                    |           |       | nown  |  |

|-----------------------------------|-----|------------------|---------------------------------------------|------------------------------------|-----------|-------|-------|--|

| R = Readable bit W = Writable bit |     |                  | bit                                         | U = Unimplemented bit, read as '0' |           |       |       |  |

| Legend:                           |     |                  |                                             |                                    |           |       |       |  |

|                                   |     |                  |                                             |                                    |           |       |       |  |

| bit 7                             |     |                  | -                                           |                                    |           |       | bit 0 |  |

| —                                 | —   | —                |                                             |                                    | RP4R<4:0> |       |       |  |

| U-0                               | U-0 | U-0              | R/W-0                                       | R/W-0                              | R/W-0     | R/W-0 | R/W-0 |  |

| DIL IO                            |     |                  |                                             |                                    |           |       | bit o |  |

| bit 15                            |     |                  |                                             |                                    |           |       | bit 8 |  |

|                                   | _   | _                | RP5R<4:0>                                   |                                    |           |       |       |  |

| U-0                               | U-0 | U-0              | R/W-0                                       | R/W-0                              | R/W-0     | R/W-0 | R/W-0 |  |

bit 12-8 **RP5R<4:0>:** Peripheral Output Function is Assigned to RP5 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP4R<4:0>:** Peripheral Output Function is Assigned to RP4 Output Pin bits (see Table 11-2 for peripheral function numbers)

#### REGISTER 11-24: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| —      | —   | —   |       |       | RP7R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |  |  |

|-------|-----|-----|-------|-------|-----------|-------|-------|--|--|

| —     | —   | —   |       |       | RP6R<4:0> |       |       |  |  |

| bit 7 |     |     | b     |       |           |       |       |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP7R<4:0>:** Peripheral Output Function is Assigned to RP7 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP6R<4:0>:** Peripheral Output Function is Assigned to RP6 Output Pin bits (see Table 11-2 for peripheral function numbers)

| REGISTER 1      | 19-2: I2CxS                     | TAT: I2Cx S1                                                      | ATUS REG                         | ISTER                      |                             |                   |                |

|-----------------|---------------------------------|-------------------------------------------------------------------|----------------------------------|----------------------------|-----------------------------|-------------------|----------------|

| R-0, HSC        | R-0, HSC                        | U-0                                                               | U-0                              | U-0                        | R/C-0, HS                   | R-0, HSC          | R-0, HSC       |

| ACKSTAT         | TRSTAT                          |                                                                   | _                                | _                          | BCL                         | GCSTAT            | ADD10          |

| bit 15          |                                 |                                                                   |                                  |                            |                             |                   | bit 8          |

| R/C-0, HS       | R/C-0, HS                       | R-0, HSC                                                          | R/C-0, HSC                       | R/C-0, HSC                 | R-0, HSC                    | R-0, HSC          | R-0, HSC       |

| IWCOL           | I2COV                           | D_A                                                               | Р                                | S                          | R_W                         | RBF               | TBF            |

| bit 7           |                                 |                                                                   | 1                                |                            |                             |                   | bit (          |

| Legend:         |                                 | C = Clear on                                                      | ly bit                           | U = Unimpler               | nented bit, rea             | d as '0'          |                |

| R = Readable    | e bit                           | W = Writable                                                      | bit                              | HS = Set in h              | ardware                     | HSC = Hardw       | are set/cleare |

| -n = Value at I | POR                             | '1' = Bit is se                                                   | t                                | '0' = Bit is cle           | ared                        | x = Bit is unkr   | nown           |

| bit 15          | ACKSTAT: A                      | vcknowledge Si                                                    | tatus bit                        |                            |                             |                   |                |

|                 | 1 = NACK re                     | ting as l <sup>2</sup> C™ r<br>ceived from sla<br>eived from slav | ave                              | ble to master t            | ransmit operati             | on)               |                |

|                 |                                 | t or clear at en                                                  | -                                | nowledge.                  |                             |                   |                |

| bit 14          |                                 |                                                                   |                                  |                            | ster. applicable            | e to master trans | smit operatior |

|                 | 1 = Master tr<br>0 = Master tr  | ansmit is in pro<br>ansmit is not ir                              | ogress (8 bits -<br>n progress   | + ACK)                     |                             | end of slave Ack  |                |

| bit 13-11       |                                 | nted: Read as                                                     |                                  |                            |                             |                   | nomeage.       |

| bit 10          | •                               | Bus Collision                                                     |                                  |                            |                             |                   |                |

|                 | 1 = A bus co<br>0 = No collisi  | llision has bee                                                   | n detected dur                   |                            | peration                    |                   |                |

| bit 9           |                                 | eneral Call Stat                                                  |                                  | •                          |                             |                   |                |

| bit 9           | 1 = General<br>0 = General      | call address wa<br>call address wa                                | as received<br>as not receive    |                            | ess. Hardware o             | clear at Stop de  | tection.       |

| bit 8           | ADD10: 10-b                     | oit Address Sta<br>dress was mat                                  | tus bit                          |                            |                             |                   |                |

|                 | 0 = 10-bit ad                   | dress was not                                                     | matched                          | ched 10-bit ad             | dress. Hardwa               | re clear at Stop  | detection.     |

| bit 7           | IWCOL: Writ                     | te Collision Det                                                  | ect bit                          |                            |                             |                   |                |

|                 | 0 = No collisi                  | ion                                                               | C                                |                            | ause the I <sup>2</sup> C m | -                 |                |

| <b>L</b> H 0    |                                 |                                                                   |                                  |                            | usy (cleared by             | / soπware).       |                |

| bit 6           |                                 |                                                                   |                                  | CV register is s           | still holding the           | previous byte     |                |

|                 |                                 |                                                                   | transfer I2CxF                   | RSR to I2CxRC              | V (cleared by               | software).        |                |

| bit 5           |                                 | ddress bit (whe                                                   |                                  |                            | (                           |                   |                |

|                 | 1 = Indicates<br>0 = Indicates  | that the last b<br>that the last b                                | yte received w<br>yte received w | /as data<br>/as device add | ress<br>by reception of     | slave byte.       |                |

| bit 4           | P: Stop bit                     |                                                                   |                                  |                            | -                           | -                 |                |

|                 | 1 = Indicates<br>0 = Stop bit v | that a Stop bit<br>was not detecte                                | ed last                          |                            |                             |                   |                |

|                 | Hardware se                     | t or clear when                                                   | Start, Repeat                    | ted Start or Sto           | p detected.                 |                   |                |

# REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

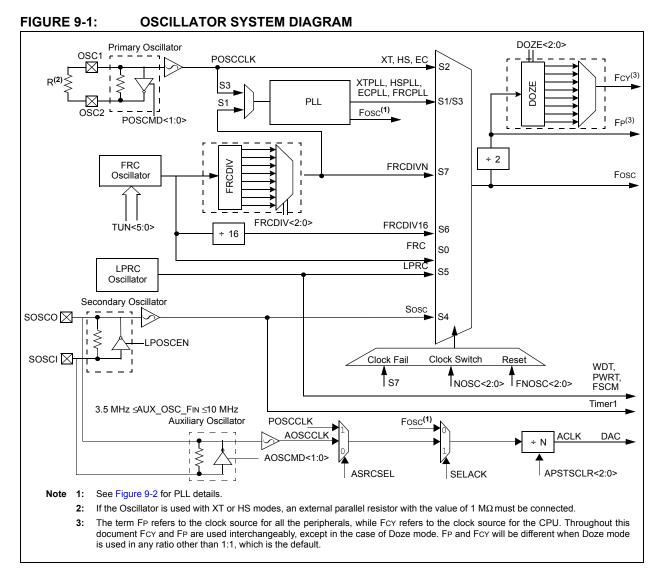

#### FIGURE 22-3: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

# 30.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

### 30.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| DC CHARACT                      | ERISTICS                  |     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq + 85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                  |        |           |  |  |  |

|---------------------------------|---------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------|-----------|--|--|--|

| Parameter<br>No. <sup>(3)</sup> | Typical <sup>(2)</sup>    | Max | Units                                                                                                                                                                                                                                                                                  | Jnits Conditions |        |           |  |  |  |

| Operating Cur                   | rent (IDD) <sup>(1)</sup> |     |                                                                                                                                                                                                                                                                                        |                  |        |           |  |  |  |

| DC20d                           | 18                        | 21  | mA                                                                                                                                                                                                                                                                                     | -40°C            |        |           |  |  |  |

| DC20a                           | 18                        | 22  | mA                                                                                                                                                                                                                                                                                     | +25°C            | - 3.3V | 10 MIPS   |  |  |  |

| DC20b                           | 18                        | 22  | mA                                                                                                                                                                                                                                                                                     | +85°C            | 3.30   | 10 101195 |  |  |  |

| DC20c                           | 18                        | 25  | mA                                                                                                                                                                                                                                                                                     | +125°C           |        |           |  |  |  |

| DC21d                           | 30                        | 35  | mA                                                                                                                                                                                                                                                                                     | -40°C            |        |           |  |  |  |

| DC21a                           | 30                        | 34  | mA                                                                                                                                                                                                                                                                                     | +25°C            | - 3.3V | 16 MIPS   |  |  |  |

| DC21b                           | 30                        | 34  | mA                                                                                                                                                                                                                                                                                     | +85°C            | 3.3V   | 10 1011-5 |  |  |  |

| DC21c                           | 30                        | 36  | mA                                                                                                                                                                                                                                                                                     | +125°C           |        |           |  |  |  |

| DC22d                           | 34                        | 42  | mA                                                                                                                                                                                                                                                                                     | -40°C            |        |           |  |  |  |

| DC22a                           | 34                        | 41  | mA                                                                                                                                                                                                                                                                                     | +25°C            | - 3.3V | 20 MIPS   |  |  |  |

| DC22b                           | 34                        | 42  | mA                                                                                                                                                                                                                                                                                     | +85°C            | 3.30   | 20 101195 |  |  |  |

| DC22c                           | 35                        | 44  | mA                                                                                                                                                                                                                                                                                     | +125°C           |        |           |  |  |  |

| DC23d                           | 49                        | 58  | mA                                                                                                                                                                                                                                                                                     | -40°C            |        |           |  |  |  |

| DC23a                           | 49                        | 57  | mA                                                                                                                                                                                                                                                                                     | +25°C            | 2.21/  |           |  |  |  |

| DC23b                           | 49                        | 57  | mA                                                                                                                                                                                                                                                                                     | +85°C            | - 3.3V | 30 MIPS   |  |  |  |

| DC23c                           | 49                        | 60  | mA                                                                                                                                                                                                                                                                                     | +125°C           |        |           |  |  |  |

| DC24d                           | 63                        | 75  | mA                                                                                                                                                                                                                                                                                     | -40°C            |        |           |  |  |  |

| DC24a                           | 63                        | 74  | mA                                                                                                                                                                                                                                                                                     | +25°C            | 2 2)/  |           |  |  |  |

| DC24b                           | 63                        | 74  | mA                                                                                                                                                                                                                                                                                     | +85°C            | - 3.3V | 40 MIPS   |  |  |  |

| DC24c                           | 63                        | 76  | mA                                                                                                                                                                                                                                                                                     | +125°C           | 1      |           |  |  |  |

#### TABLE 31-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode, no PLL until 10 MIPS, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (defined PMDx bits are set to zero)

- CPU executing while (1) statement

- JTAG is disabled

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** These parameters are characterized but not tested in manufacturing.

# TABLE 31-21:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                |      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |    |                                                                                        |  |  |

|--------------------|--------|----------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|----------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                  | Min  | Min Typ <sup>(2)</sup> Max Units                                                                                                                                                                     |     |    | Conditions                                                                             |  |  |

| SY10               | TMCL   | MCLR Pulse Width (low)                                         | 2    | —                                                                                                                                                                                                    | _   | μs | -40°C to +85°C                                                                         |  |  |

| SY11               | Tpwrt  | Power-up Timer Period                                          | _    | 2<br>4<br>8<br>16<br>32<br>64<br>128                                                                                                                                                                 |     | ms | -40°C to +85°C<br>User programmable                                                    |  |  |

| SY12               | TPOR   | Power-on Reset Delay                                           | 3    | 10                                                                                                                                                                                                   | 30  | μs | -40°C to +85°C                                                                         |  |  |

| SY13               | Tioz   | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | 0.68 | 0.72                                                                                                                                                                                                 | 1.2 | μs | _                                                                                      |  |  |

| SY20               | Twdt1  | Watchdog Timer Time-out<br>Period                              | —    | _                                                                                                                                                                                                    | —   | _  | See Section 28.4 "Watchdog<br>Timer (WDT)" and LPRC<br>specification F21 (Table 31-19) |  |  |

| SY30               | Tost   | Oscillator Start-up Time                                       | _    | 1024 Tosc                                                                                                                                                                                            |     |    | Tosc = OSC1 period                                                                     |  |  |

| SY35               | TFSCM  | Fail-Safe Clock Monitor<br>Delay                               | —    | 500                                                                                                                                                                                                  | 900 | μs | -40°C to +85°C                                                                         |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

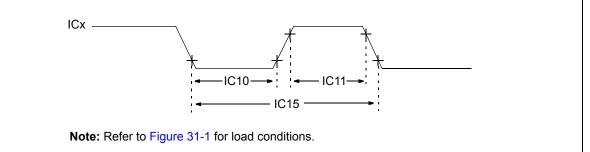

#### FIGURE 31-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

#### TABLE 31-26: INPUT CAPTURE TIMING REQUIREMENTS

| AC CHARACTERISTICS            |      |                     | (unless otherwis      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |       |                                  |  |  |  |

|-------------------------------|------|---------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|----------------------------------|--|--|--|

| Param<br>No. Symbol Character |      |                     | ristic <sup>(1)</sup> | Min                                                                                                                                                                                                  | Мах | Units | Conditions                       |  |  |  |

| IC10                          | TccL | ICx Input Low Time  | No Prescaler          | 0.5 Tcy + 20                                                                                                                                                                                         |     | ns    |                                  |  |  |  |

|                               |      |                     | With Prescaler        | 10                                                                                                                                                                                                   | _   | ns    |                                  |  |  |  |

| IC11                          | TccH | ICx Input High Time | No Prescaler          | 0.5 Tcy + 20                                                                                                                                                                                         | _   | ns    |                                  |  |  |  |

|                               |      |                     | With Prescaler        | 10                                                                                                                                                                                                   | _   | ns    |                                  |  |  |  |

| IC15                          | TccP | ICx Input Period    |                       | (Tcy + 40)/N                                                                                                                                                                                         | _   | ns    | N = prescale<br>value (1, 4, 16) |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

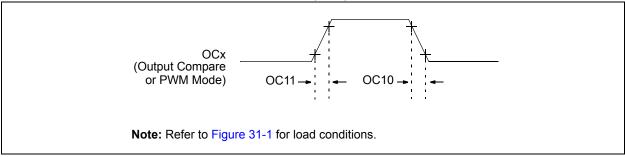

#### FIGURE 31-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 31-27: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

|              |        |                               | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |     |       |                    |  |  |

|--------------|--------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|--------------------|--|--|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup> | Min                                                                                                                                                                                                  | Тур | Мах | Units | Conditions         |  |  |

| OC10         | TccF   | OCx Output Fall Time          | —                                                                                                                                                                                                    | —   | _   | ns    | See parameter D032 |  |  |

| OC11         | TccR   | OCx Output Rise Time          | —                                                                                                                                                                                                    | —   | _   | ns    | See parameter D031 |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

| AC CHARACTERISTICS                                                  |        |                                | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |           |            |           |                                                  |  |  |  |  |