Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc304-e-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04 PRODUCT FAMILIES

The device names, pin counts, memory sizes, and peripheral availability of each device are listed in Table 1. The pages that follow show their pinout diagrams.

# TABLE 1:dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04CONTROLLER FAMILIES

|                   |      |                                 |                            |                 |                             |               | Remap                          | pable F                                        | Periphe                         | ral  |     |                    |                                    |      |                   |                      |                                 |                  | Ĵ.                                                  |                                               |          |                        |

|-------------------|------|---------------------------------|----------------------------|-----------------|-----------------------------|---------------|--------------------------------|------------------------------------------------|---------------------------------|------|-----|--------------------|------------------------------------|------|-------------------|----------------------|---------------------------------|------------------|-----------------------------------------------------|-----------------------------------------------|----------|------------------------|

| Device            | Pins | Program Flash Memory<br>(Kbyte) | RAM (Kbyte) <sup>(1)</sup> | Remappable Pins | 16-bit Timer <sup>(2)</sup> | Input Capture | Output Compare<br>Standard PWM | Motor Control PWM<br>(Channels) <sup>(3)</sup> | Quadrature Encoder<br>Interface | UART | SPI | ECAN <sup>TM</sup> | External Interrupts <sup>(4)</sup> | RTCC | I <sup>2</sup> C™ | <b>CRC Generator</b> | 10-bit/12-bit ADC<br>(Channels) | 6-pin 16-bit DAC | Analog Comparator<br>(2 Channels/Voltage Regulator) | 8-bit Parallel Master<br>Port (Address Lines) | I/O Pins | Packages               |

| dsPIC33FJ128MC804 | 44   | 128                             | 16                         | 26              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 1                  | 3                                  | 1    | 1                 | 1                    | 9                               | 1                | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ128MC802 | 28   | 128                             | 16                         | 16              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 1                  | 3                                  | 1    | 1                 | 1                    | 6                               | 0                | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ128MC204 | 44   | 128                             | 8                          | 26              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 0                  | 3                                  | 1    | 1                 | 1                    | 9                               | 0                | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ128MC202 | 28   | 128                             | 8                          | 16              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 0                  | 3                                  | 1    | 1                 | 1                    | 6                               | 0                | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ64MC804  | 44   | 64                              | 16                         | 26              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 1                  | 3                                  | 1    | 1                 | 1                    | 9                               | 1                | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ64MC802  | 28   | 64                              | 16                         | 16              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 1                  | 3                                  | 1    | 1                 | 1                    | 6                               | 0                | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ64MC204  | 44   | 64                              | 8                          | 26              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 0                  | 3                                  | 1    | 1                 | 1                    | 9                               | 0                | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ64MC202  | 28   | 64                              | 8                          | 16              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 0                  | 3                                  | 1    | 1                 | 1                    | 6                               | 0                | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ32MC304  | 44   | 32                              | 4                          | 26              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 0                  | 3                                  | 1    | 1                 | 1                    | 9                               | 0                | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ32MC302  | 28   | 32                              | 4                          | 16              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 0                  | 3                                  | 1    | 1                 | 1                    | 6                               | 0                | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

Note 1: RAM size is inclusive of 2 Kbytes of DMA RAM for all devices except dsPIC33FJ32MC302/304, which include 1 Kbyte of DMA RAM.

2: Only four out of five timers are remappable.

**3:** Only PWM fault pins are remappable.

4: Only two out of three interrupts are remappable.

#### TABLE 4-12: I2C1 REGISTER MAP

| SFR Name | Addr     | Bit 15       | Bit 14     | Bit 13     | Bit 12      | Bit 11       | Bit 10       | Bit 9                   | Bit 8       | Bit 7                        | Bit 6 | Bit 5   | Bit 4    | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|----------|--------------|------------|------------|-------------|--------------|--------------|-------------------------|-------------|------------------------------|-------|---------|----------|----------|-------|-------|-------|---------------|

| I2C1RCV  | 0200     | _            | -          |            | _           | _            |              | _                       |             | Receive Register             |       |         |          |          |       |       |       | 0000          |

| I2C1TRN  | 0202     | _            | _          |            | —           | —            |              | —                       | _           |                              |       |         | Transmit | Register |       |       |       | OOFF          |

| I2C1BRG  | 0204     | _            | _          |            | —           | —            |              | —                       |             | Baud Rate Generator Register |       |         |          |          |       |       |       | 0000          |

| I2C1CON  | 0206     | I2CEN        |            | I2CSIDL    | SCLREL      | IPMIEN       | A10M         | DISSLW                  | SMEN        | GCEN                         | STREN | ACKDT   | ACKEN    | RCEN     | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208     | ACKSTAT      | TRSTAT     | _          | _           | _            | BCL          | GCSTAT                  | ADD10       | IWCOL                        | I2COV | D_A     | Р        | S        | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A     | -            | _          | _          | _           | _            | _            |                         |             |                              |       | Address | Register |          |       |       |       | 0000          |

| I2C1MSK  | 020C     | -            | _          | _          | _           | _            | _            | Address Mask Register 0 |             |                              |       |         |          |          |       | 0000  |       |               |

| Legend:  | x = unkr | nown value o | n Reset, — | = unimpler | nented, rea | d as '0'. Re | set values a | are shown ir            | n hexadecir | nal.                         |       |         |          |          |       |       |       |               |

# TABLE 4-13: UART1 REGISTER MAP

| SFR Name | Addr | Bit 15   | Bit 14                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                        | Bit 6  | Bit 5 | Bit 4      | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|------|----------|-------------------------------|----------|--------|--------|--------|-------|-------|----------------------------------------------|--------|-------|------------|--------------|-------|--------|-------|---------------|

| U1MODE   | 0220 | UARTEN   | —                             | USIDL    | IREN   | RTSMD  |        | UEN1  | UEN0  | WAKE                                         | LPBACK | ABAUD | URXINV     | BRGH         | PDSE  | _<1:0> | STSEL | 0000          |

| U1STA    | 0222 | UTXISEL1 | UTXINV                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL<1:0> ADDEN RIDLE PERR FERR OERR URXD |        |       |            |              | URXDA | 0110   |       |               |

| U1TXREG  | 0224 | _        | _                             | _        | _      | _      | _      | _     | UTX8  |                                              |        | U     | ART Transm | nit Register |       |        |       | XXXX          |

| U1RXREG  | 0226 | _        | _                             | _        | _      | _      | _      | _     | URX8  | UART Received Register                       |        |       |            |              |       |        |       | 0000          |

| U1BRG    | 0228 |          | Baud Rate Generator Prescaler |          |        |        |        |       |       |                                              |        |       |            | 0000         |       |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-14: UART2 REGISTER MAP

| SFR Name | Addr | Bit 15   | Bit 14                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                         | Bit 6  | Bit 5 | Bit 4      | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|------|----------|-------------------------------|----------|--------|--------|--------|-------|-------|-----------------------------------------------|--------|-------|------------|--------------|-------|--------|-------|---------------|

| U2MODE   | 0230 | UARTEN   |                               | USIDL    | IREN   | RTSMD  |        | UEN1  | UEN0  | WAKE                                          | LPBACK | ABAUD | URXINV     | BRGH         | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA    | 0232 | UTXISEL1 | UTXINV                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL<1:0> ADDEN RIDLE PERR FERR OERR URXDA |        |       |            |              |       | URXDA  | 0110  |               |

| U2TXREG  | 0234 | —        |                               | —        |        | —      |        |       | UTX8  |                                               |        | U     | ART Transm | nit Register |       |        |       | XXXX          |

| U2RXREG  | 0236 | —        |                               | —        |        | —      |        |       | URX8  |                                               |        | U     | ART Receiv | e Register   |       |        |       | 0000          |

| U2BRG    | 0238 |          | Baud Rate Generator Prescaler |          |        |        |        |       |       |                                               |        |       |            | 0000         |       |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.6.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to <sup>(0010)</sup> to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

# EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| ; Set up NVMCON for block erase operation |                                          |

|-------------------------------------------|------------------------------------------|

| MOV #0x4042, W0                           | ;                                        |

| MOV W0, NVMCON                            | ; Initialize NVMCON                      |

| ; Init pointer to row to be ERASED        |                                          |

| MOV #tblpage(PROG_ADDR), W0               | ;                                        |

| MOV W0, TBLPAG                            | ; Initialize PM Page Boundary SFR        |

| MOV #tbloffset(PROG_ADDR), W0             | ; Initialize in-page EA[15:0] pointer    |

| TBLWTL W0, [W0]                           | ; Set base address of erase block        |

| DISI #5                                   | ; Block all interrupts with priority < 7 |

|                                           | ; for next 5 instructions                |

| MOV #0x55, W0                             |                                          |

| MOV W0, NVMKEY                            | ; Write the 55 key                       |

| MOV #0xAA, W1                             | ;                                        |

| MOV W1, NVMKEY                            | ; Write the AA key                       |

| BSET NVMCON, #WR                          | ; Start the erase sequence               |

| NOP                                       | ; Insert two NOPs after the erase        |

| NOP                                       | ; command is asserted                    |

|                                           |                                          |

# 6.3 System Reset

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices have two types of Reset:

- Cold Reset

- Warm Reset

A cold Reset is the result of a Power-on Reset (POR) or a Brown-out Reset (BOR). On a cold Reset, the FNOSC Configuration bits in the FOSC device Configuration register selects the device clock source. A warm Reset is the result of all other reset sources, including the RESET instruction. On warm Reset, the device will continue to operate from the current clock source as indicated by the Current Oscillator Selection bits (COSC<2:0>) in the Oscillator Control register (OSCCON<14:12>).

The device is kept in a Reset state until the system power supplies have stabilized at appropriate levels and the oscillator clock is ready. The description of the sequence in which this occurs is shown in Figure 6-2.

| Oscillator Mode        | Oscillator<br>Startup Delay | Oscillator<br>Startup Timer | PLL Lock Time | Total Delay             |

|------------------------|-----------------------------|-----------------------------|---------------|-------------------------|

| FRC, FRCDIV16, FRCDIVN | Toscd                       | _                           | —             | Toscd                   |

| FRCPLL                 | Toscd                       | —                           | TLOCK         | TOSCD + TLOCK           |

| XT                     | Toscd                       | Tost                        | —             | Toscd + Tost            |

| HS                     | Toscd                       | Tost                        | —             | Toscd + Tost            |

| EC                     | —                           | —                           | —             | —                       |

| XTPLL                  | Toscd                       | Тоят                        | Тьоск         | Toscd + Tost +<br>Tlock |

| HSPLL                  | Toscd                       | Тоѕт                        | Тьоск         | Toscd + Tost +<br>Tlock |

| ECPLL                  | —                           | —                           | Тьоск         | Тьоск                   |

| Sosc                   | Toscd                       | Tost                        | —             | Toscd + Tost            |

| LPRC                   | Toscd                       | —                           | —             | Toscd                   |

#### TABLE 6-1: OSCILLATOR DELAY

**Note 1:** ToscD = Oscillator Start-up Delay (1.1 μs max for FRC, 70 μs max for LPRC). Crystal Oscillator start-up times vary with crystal characteristics, load capacitance, etc.

**2:** TOST = Oscillator Start-up Timer Delay (1024 oscillator clock period). For example, TOST = 102.4 μs for a 10 MHz crystal and TOST = 32 ms for a 32 kHz crystal.

**3:** TLOCK = PLL lock time (1.5 ms nominal), if PLL is enabled.

| U-0           | R/W-1                                                                        | R/W-0                    | R/W-0 | U-0                     | R/W-1           | R/W-0                 | R/W-0 |  |  |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------|--------------------------|-------|-------------------------|-----------------|-----------------------|-------|--|--|--|--|--|--|--|

| _             |                                                                              | C1IP<2:0> <sup>(1)</sup> |       |                         |                 | C1RXIP<2:0>(1)        |       |  |  |  |  |  |  |  |

| bit 15        |                                                                              |                          |       |                         |                 |                       | bit   |  |  |  |  |  |  |  |

|               |                                                                              | D444 0                   | DANO  |                         |                 |                       |       |  |  |  |  |  |  |  |

| U-0           | R/W-1                                                                        | R/W-0<br>SPI2IP<2:0>     | R/W-0 | U-0                     | R/W-1           | R/W-0<br>SPI2EIP<2:0> | R/W-0 |  |  |  |  |  |  |  |

| bit 7         |                                                                              | 011211 32.07             |       |                         |                 | 0112211 42.05         | bit   |  |  |  |  |  |  |  |

|               |                                                                              |                          |       |                         |                 |                       |       |  |  |  |  |  |  |  |

| Legend:       | a hit                                                                        |                          | :4    |                         | nonted bit no   |                       |       |  |  |  |  |  |  |  |

| R = Readabl   |                                                                              | W = Writable b           | ut.   | 0 = Onimpler            | mented bit, rea |                       |       |  |  |  |  |  |  |  |

| -n = Value at | PUR                                                                          | '1' = Bit is set         |       |                         | areu            | x = Bit is unkno      | own   |  |  |  |  |  |  |  |

| bit 15        | Unimpleme                                                                    | ented: Read as '0        | ,     |                         |                 |                       |       |  |  |  |  |  |  |  |

| bit 14-12     | =                                                                            | ECAN1 Event Int          |       | ity bits <sup>(1)</sup> |                 |                       |       |  |  |  |  |  |  |  |

|               |                                                                              | rupt is priority 7 (h    | •     | •                       |                 |                       |       |  |  |  |  |  |  |  |

|               | •                                                                            |                          | 0     | <b>,</b>                |                 |                       |       |  |  |  |  |  |  |  |

|               | •                                                                            |                          |       |                         |                 |                       |       |  |  |  |  |  |  |  |

|               | •<br>001 - Intor                                                             | rupt is priority 1       |       |                         |                 |                       |       |  |  |  |  |  |  |  |

|               |                                                                              | rupt source is disa      | bled  |                         |                 |                       |       |  |  |  |  |  |  |  |

| bit 11        | Unimplemented: Read as '0'                                                   |                          |       |                         |                 |                       |       |  |  |  |  |  |  |  |

| bit 10-8      | C1RXIP<2:0>: ECAN1 Receive Data Ready Interrupt Priority bits <sup>(1)</sup> |                          |       |                         |                 |                       |       |  |  |  |  |  |  |  |

|               |                                                                              | rupt is priority 7 (h    |       |                         | ,               |                       |       |  |  |  |  |  |  |  |

|               | •                                                                            |                          | •     | /                       |                 |                       |       |  |  |  |  |  |  |  |

|               | •                                                                            |                          |       |                         |                 |                       |       |  |  |  |  |  |  |  |

|               | •<br>001 - Inter                                                             | rupt is priority 1       |       |                         |                 |                       |       |  |  |  |  |  |  |  |

|               |                                                                              | rupt source is disa      | bled  |                         |                 |                       |       |  |  |  |  |  |  |  |

| bit 7         |                                                                              | ented: Read as '0        |       |                         |                 |                       |       |  |  |  |  |  |  |  |

| bit 6-4       | -                                                                            | >: SPI2 Event Inte       |       | tv bits                 |                 |                       |       |  |  |  |  |  |  |  |

|               |                                                                              | rupt is priority 7 (h    | -     | -                       |                 |                       |       |  |  |  |  |  |  |  |

|               | •                                                                            |                          | 0     | <b>,</b>                |                 |                       |       |  |  |  |  |  |  |  |

|               | •                                                                            |                          |       |                         |                 |                       |       |  |  |  |  |  |  |  |

|               | •<br>001 = Inter                                                             | rupt is priority 1       |       |                         |                 |                       |       |  |  |  |  |  |  |  |

|               |                                                                              | rupt source is disa      | bled  |                         |                 |                       |       |  |  |  |  |  |  |  |

| bit 3         |                                                                              | ented: Read as '0        |       |                         |                 |                       |       |  |  |  |  |  |  |  |

| bit 2-0       | -                                                                            | :0>: SPI2 Error Int      |       | itv bits                |                 |                       |       |  |  |  |  |  |  |  |

|               |                                                                              | rupt is priority 7 (h    | -     | -                       |                 |                       |       |  |  |  |  |  |  |  |

|               | •                                                                            |                          | - ' ' |                         |                 |                       |       |  |  |  |  |  |  |  |

|               | •                                                                            |                          |       |                         |                 |                       |       |  |  |  |  |  |  |  |

|               | •                                                                            |                          |       |                         |                 |                       |       |  |  |  |  |  |  |  |

|               | 001 - Intor                                                                  | rupt is priority 1       |       |                         |                 |                       |       |  |  |  |  |  |  |  |

#### DECISTED 7 22

# 9.4 Clock Switching Operation

Applications are free to switch among any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects of this flexibility, dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 devices have a safeguard lock built into the switch process.

Note: Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch among the different primary submodes without reprogramming the device.

# 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to '0'. (Refer to **Section 28.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

Performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit (OSCCON<0>) to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

1. The clock switching hardware compares the COSC status bits with the new value of the NOSC control bits. If they are the same, the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and the CF (OSCCON<3>) status bits are cleared.

- 3. The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred to the COSC status bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

Note 1: The processor continues to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to Section 39. "Oscillator (Part III)" (DS70216) in the "dsPIC33F/ PIC24H Family Reference Manual" for details.

# 9.5 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

<sup>© 2007-2012</sup> Microchip Technology Inc.

# 10.5 Power-Saving Resources

Many useful resources related to power-saving modes are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

#### 10.5.1 KEY RESOURCES

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

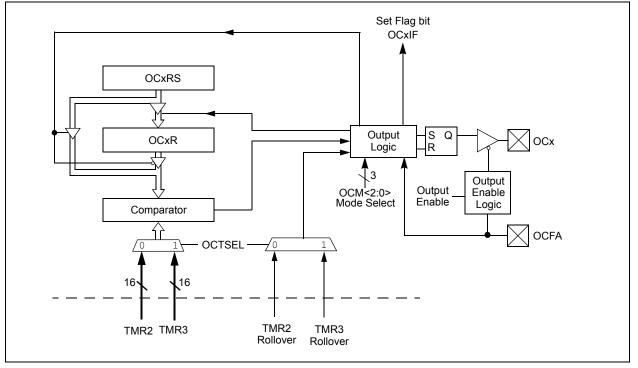

# 15.0 OUTPUT COMPARE

- This data sheet summarizes the features Note 1: of the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 of family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Output Compare" (DS70209) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Output Compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The Output Compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The Output Compare module can also generate interrupts on compare match events.

The Output Compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- · Delayed One-Shot mode

- · Continuous Pulse mode

- PWM mode without fault protection

- · PWM mode with fault protection

# FIGURE 15-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

| REGISTER 16     | 5-8: PXDTC    | ON2: DEAD         | -TIME CON   | TROL REGIS       | TER 2(")         |                 |       |

|-----------------|---------------|-------------------|-------------|------------------|------------------|-----------------|-------|

| U-0             | U-0           | U-0               | U-0         | U-0              | U-0              | U-0             | U-0   |

| —               | —             | _                 |             | —                |                  |                 | —     |

| bit 15          |               |                   |             |                  |                  |                 | bit 8 |

|                 |               |                   |             |                  |                  |                 |       |

| U-0             | U-0           | R/W-0             | R/W-0       | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| —               | —             | DTS3A             | DTS3I       | DTS2A            | DTS2I            | DTS1A           | DTS1I |

| bit 7           |               |                   |             |                  |                  |                 | bit 0 |

|                 |               |                   |             |                  |                  |                 |       |

| Legend:         |               |                   |             |                  |                  |                 |       |

| R = Readable    | bit           | W = Writable      | bit         | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value at P | OR            | '1' = Bit is set  |             | '0' = Bit is cle | ared             | x = Bit is unkr | lown  |

|                 |               |                   |             |                  |                  |                 |       |

| bit 15-6        | Unimplemen    | ted: Read as '    | 0'          |                  |                  |                 |       |

| bit 5           | DTS3A: Dead   | I-Time Select for | or PWMxH3 S | Signal Going A   | ctive bit        |                 |       |

|                 | 1 = Dead time | provided from     | n Unit B    |                  |                  |                 |       |

|                 | 0 = Dead time | e provided from   | n Unit A    |                  |                  |                 |       |

| bit 4           | DTS3I: Dead-  | Time Select fo    | r PWMxL3 Si | gnal Going Ina   | ctive bit        |                 |       |

|                 |               |                   |             |                  |                  |                 |       |

# REGISTER 16-8: PxDTCON2: DEAD-TIME CONTROL REGISTER 2<sup>(1)</sup>

|       | 0 = Dead time provided from Unit A                           |

|-------|--------------------------------------------------------------|

| bit 4 | DTS3I: Dead-Time Select for PWMxL3 Signal Going Inactive bit |

|       | 1 = Dead time provided from Unit B                           |

|       | 0 = Dead time provided from Unit A                           |

| bit 3 | DTS2A: Dead-Time Select for PWMxH2 Signal Going Active bit   |

|       | 1 = Dead time provided from Unit B                           |

|       | 0 = Dead time provided from Unit A                           |

| bit 2 | DTS2I: Dead-Time Select for PWMxL2 Signal Going Inactive bit |

|       | 1 = Dead time provided from Unit B                           |

|       | 0 = Dead time provided from Unit A                           |

| bit 1 | DTS1A: Dead-Time Select for PWMxH1 Signal Going Active bit   |

|       | 1 = Dead time provided from Unit B                           |

|       | 0 = Dead time provided from Unit A                           |

| bit 0 | DTS1I: Dead-Time Select for PWMxL1 Signal Going Inactive bit |

|       | 1 = Dead time provided from Unit B                           |

|       | 0 = Dead time provided from Unit A                           |

|       |                                                              |

Note 1: PWM2 supports only one PWM I/O pin pair.

| REGISTER 16-10: | PxOVDCON: OVERRIDE CONTROL REGISTER <sup>(1)</sup> |

|-----------------|----------------------------------------------------|

|-----------------|----------------------------------------------------|

| U-0             | U-0        | R/W-1            | R/W-1      | R/W-1            | R/W-1            | R/W-1           | R/W-1            |  |  |

|-----------------|------------|------------------|------------|------------------|------------------|-----------------|------------------|--|--|

| _               | _          | POVD3H           | POVD3L     | POVD2H           | POVD2L           | POVD1H          | POVD1L           |  |  |

| bit 15          |            |                  |            |                  |                  |                 | bit 8            |  |  |

|                 |            |                  |            |                  |                  |                 |                  |  |  |

| U-0             | U-0        | R/W-0            | R/W-0      | R/W-0            | R/W-0            | R/W-0           | R/W-0            |  |  |

| —               | —          | POUT3H           | POUT3L     | POUT2H           | POUT2L           | POUT1H          | POUT1L           |  |  |

| bit 7           |            | •                |            | ·                |                  | •               | bit 0            |  |  |

|                 |            |                  |            |                  |                  |                 |                  |  |  |

| Legend:         |            |                  |            |                  |                  |                 |                  |  |  |

| R = Readable    | bit        | W = Writable     | bit        | U = Unimpler     | nented bit, read | as '0'          |                  |  |  |

| -n = Value at F | POR        | '1' = Bit is set |            | '0' = Bit is cle | ared             | x = Bit is unkr | = Bit is unknown |  |  |

|                 |            |                  |            |                  |                  |                 |                  |  |  |

| bit 15-14       | Unimplemen | ted: Read as '   | )'         |                  |                  |                 |                  |  |  |

| bit 13-8        | POVDxH<3:1 | >:POVDxL<3:      | 1>: PWM Ou | tput Override b  | its              |                 |                  |  |  |

1 = Output on PWMx I/O pin is controlled by the PWM generator

0 = Output on PWMx I/O pin is controlled by the value in the corresponding POUTxH:POUTxL bit

bit 7-6

Unimplemented: Read as '0'

bit 5-0

POUTxH<3:1>:POUTxL<3:1>: PWM Manual Output bits

1 = PWMx I/O pin is driven active when the corresponding POVDxH:POVDxL bit is cleared

$_{0}$  = PWMx I/O pin is driven inactive when the corresponding POVDxH:POVDxL bit is cleared

Note 1: PWM2 supports only one PWM I/O pin pair.

# 21.5 ECAN Control Registers

| U-0          | U-0                                                       | R/W-0                                 | R/W-0        | r-0                    | R/W-1           | R/W-0           | R/W-0 |  |  |  |

|--------------|-----------------------------------------------------------|---------------------------------------|--------------|------------------------|-----------------|-----------------|-------|--|--|--|

|              | —                                                         | CSIDL                                 | ABAT         |                        |                 | REQOP<2:0>      |       |  |  |  |

| bit 15       |                                                           |                                       |              |                        |                 |                 | bit 8 |  |  |  |

| R-1          | R-0                                                       | R-0                                   | U-0          | R/W-0                  | U-0             | U-0             | R/W-0 |  |  |  |

|              | OPMODE<2:0>                                               | >                                     | _            | CANCAP                 | _               | _               | WIN   |  |  |  |

| bit 7        |                                                           |                                       |              |                        |                 |                 | bit C |  |  |  |

| Legend:      |                                                           | r = Bit is Res                        | erved        |                        |                 |                 |       |  |  |  |

| R = Readab   | ole bit                                                   | W = Writable                          | bit          | U = Unimpler           | mented bit, rea | d as '0'        |       |  |  |  |

| -n = Value a | it POR                                                    | '1' = Bit is set                      |              | '0' = Bit is cle       | ared            | x = Bit is unkr | nown  |  |  |  |

|              |                                                           |                                       |              |                        |                 |                 |       |  |  |  |

| bit 15-14    | Unimplemen                                                | ted: Read as '                        | 0'           |                        |                 |                 |       |  |  |  |

| bit 13       |                                                           | in Idle Mode b                        |              |                        |                 |                 |       |  |  |  |

|              |                                                           | ue module ope<br>module operat        |              | levice enters Id<br>de | lle mode        |                 |       |  |  |  |

| bit 12       |                                                           | All Pending Tra                       |              |                        |                 |                 |       |  |  |  |

|              |                                                           | transmit buffer                       |              |                        |                 |                 |       |  |  |  |

|              | •                                                         |                                       |              | smissions are a        | aborted         |                 |       |  |  |  |

| bit 11       | Reserved: D                                               | o not use                             |              |                        |                 |                 |       |  |  |  |

| bit 10-8     | 10-8 <b>REQOP&lt;2:0&gt;:</b> Request Operation Mode bits |                                       |              |                        |                 |                 |       |  |  |  |

|              | 111 = Set Lis                                             | ten All Messag                        | jes mode     |                        |                 |                 |       |  |  |  |

|              | 110 = Reserv                                              |                                       |              |                        |                 |                 |       |  |  |  |

|              | 101 = Reserv                                              | /ea<br>nfiguration mo                 | do           |                        |                 |                 |       |  |  |  |

|              |                                                           | ten Only Mode                         |              |                        |                 |                 |       |  |  |  |

|              | 010 = Set Lo                                              | -                                     |              |                        |                 |                 |       |  |  |  |

|              | 001 = Set Dis                                             |                                       |              |                        |                 |                 |       |  |  |  |

|              |                                                           | rmal Operation                        |              |                        |                 |                 |       |  |  |  |

| bit 7-5      |                                                           | 0>: Operation                         |              |                        |                 |                 |       |  |  |  |

|              | 111 = Module<br>110 = Reserv                              | e is in Listen Al                     | I Messages n | lode                   |                 |                 |       |  |  |  |

|              | 101 = Reserv                                              |                                       |              |                        |                 |                 |       |  |  |  |

|              |                                                           | 100 = Module is in Configuration mode |              |                        |                 |                 |       |  |  |  |

|              |                                                           | e is in Listen O                      | •            |                        |                 |                 |       |  |  |  |

|              |                                                           | e is in Loopbac                       |              |                        |                 |                 |       |  |  |  |

|              |                                                           | e is in Disable i<br>e is in Normal ( |              | 40                     |                 |                 |       |  |  |  |

| bit 4        |                                                           | ted: Read as '                        | •            | he                     |                 |                 |       |  |  |  |

| bit 3        | -                                                         |                                       |              | Capture Event          | Enable bit      |                 |       |  |  |  |

|              |                                                           | -                                     |              | nessage receiv         |                 |                 |       |  |  |  |

|              | 0 = Disable II                                            |                                       |              |                        | -               |                 |       |  |  |  |

| bit 2-1      | Unimplemen                                                | ted: Read as '                        | 0'           |                        |                 |                 |       |  |  |  |

| bit 0        | •                                                         | ap Window Sel                         |              |                        |                 |                 |       |  |  |  |

|              | 1 = Use filter                                            | window                                |              |                        |                 |                 |       |  |  |  |

|              | 0 = Use buffe                                             |                                       |              |                        |                 |                 |       |  |  |  |

# REGISTER 21-1: CICTRL1: ECAN™ CONTROL REGISTER 1

| REGISTER                          | 21-20: CiRXM<br>REGIS                                                                                                                                                                                                                                                                              | InSID: ECAN<br>TER n (n = 0                                 |             | ANCE FILTE                              | R MASK STA | NDARD IDE | NTIFIER |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------|-----------------------------------------|------------|-----------|---------|--|--|

| R/W-x                             | R/W-x                                                                                                                                                                                                                                                                                              | R/W-x                                                       | R/W-x       | R/W-x                                   | R/W-x      | R/W-x     | R/W-x   |  |  |

| SID10                             | SID9                                                                                                                                                                                                                                                                                               | SID8                                                        | SID7        | SID6                                    | SID5       | SID4      | SID3    |  |  |

| bit 15                            |                                                                                                                                                                                                                                                                                                    |                                                             |             |                                         |            |           | bit 8   |  |  |

| R/W-x                             | R/W-x                                                                                                                                                                                                                                                                                              | R/W-x                                                       | U-0         | R/W-x                                   | U-0        | R/W-x     | R/W-x   |  |  |

| SID2                              | SID1                                                                                                                                                                                                                                                                                               | SID0                                                        | _           | MIDE                                    |            | EID17     | EID16   |  |  |

| bit 7                             |                                                                                                                                                                                                                                                                                                    |                                                             |             |                                         |            |           | bit 0   |  |  |

| Legend:                           |                                                                                                                                                                                                                                                                                                    |                                                             |             |                                         |            |           |         |  |  |

| R = Readable bit W = Writable bit |                                                                                                                                                                                                                                                                                                    |                                                             | bit         | U = Unimplemented bit, read as '0'      |            |           |         |  |  |

| -n = Value at                     | POR                                                                                                                                                                                                                                                                                                | '1' = Bit is set                                            |             | '0' = Bit is cleared x = Bit is unknown |            |           |         |  |  |

| bit 15-5                          | 1 = Include bi                                                                                                                                                                                                                                                                                     | tandard Identifi<br>t SIDx in filter o<br>s don't care in f | comparison  | son                                     |            |           |         |  |  |

| bit 4                             | Unimplemen                                                                                                                                                                                                                                                                                         | ted: Read as '                                              | )'          |                                         |            |           |         |  |  |

| bit 3                             | MIDE: Identifi                                                                                                                                                                                                                                                                                     | er Receive Mo                                               | de bit      |                                         |            |           |         |  |  |

|                                   | <ul> <li>1 = Match only message types (standard or extended address) that correspond to EXIDE bit in filter</li> <li>0 = Match either standard or extended address message if filters match</li> <li>(i.e., if (Filter SID) = (Message SID) or if (Filter SID/EID) = (Message SID/EID))</li> </ul> |                                                             |             |                                         |            |           |         |  |  |

| bit 2                             | Unimplemen                                                                                                                                                                                                                                                                                         | Unimplemented: Read as '0'                                  |             |                                         |            |           |         |  |  |

| bit 1-0                           | EID<17:16>:                                                                                                                                                                                                                                                                                        | Extended Iden                                               | tifier bits |                                         |            |           |         |  |  |

|                                   |                                                                                                                                                                                                                                                                                                    | t EIDx in filter o<br>s don't care in f                     | •           | son                                     |            |           |         |  |  |

#### REGISTER 21-21: CIRXMnEID: ECAN<sup>™</sup> ACCEPTANCE FILTER MASK EXTENDED IDENTIFIER REGISTER n (n = 0-2)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| EID7   | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7  |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Include bit EIDx in filter comparison

0 = Bit EIDx is don't care in filter comparison

# 22.6 ADC Control Registers

| R/W-0  | U-0       | R/W-0  | R/W-0   | U-0    | R/W-0 | R/W-0  | R/W-0  |

|--------|-----------|--------|---------|--------|-------|--------|--------|

| ADON   | —         | ADSIDL | ADDMABM | -      | AD12B | FORM   | 1<1:0> |

| bit 15 |           |        |         |        |       |        | bit 8  |

| -      |           |        |         |        |       |        |        |

| R/W-0  | R/W-0     | R/W-0  | U-0     | R/W-0  | R/W-0 | R/W-0  | R/C-0  |

|        |           |        |         |        |       | HC, HS | HC, HS |

|        | SSRC<2:0> |        |         | SIMSAM | ASAM  | SAMP   | DONE   |

| bit 7  |           |        |         |        |       |        | bit 0  |

| REGISTER 22-1: AD1CON1: ADC1 CONTROL REG |

|------------------------------------------|

|------------------------------------------|

| Legend: HC = Cleared by hardware HS = Set by hardware |                  |                                    |                    |

|-------------------------------------------------------|------------------|------------------------------------|--------------------|

| R = Readable bit                                      | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR                                     | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 15  | ADON: ADC Operating Mode bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = ADC module is operating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | 0 = ADC is off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 13  | ADSIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul><li>1 = Discontinue module operation when device enters Idle mode</li><li>0 = Continue module operation in Idle mode</li></ul>                                                                                                                                                                                                                                                                                                                                                                           |

| bit 12  | ADDMABM: DMA Buffer Build Mode bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = DMA buffers are written in the order of conversion. The module provides an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer</li> <li>0 = DMA buffers are written in Scatter/Gather mode. The module provides a scatter/gather address</li> </ul>                                                                                                                                                                                              |

|         | to the DMA channel, based on the index of the analog input and the size of the DMA buffer                                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 11  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 10  | AD12B: 10-bit or 12-bit Operation Mode bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = 12-bit, 1-channel ADC operation</li> <li>0 = 10-bit, 4-channel ADC operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                         |

| bit 9-8 | FORM<1:0>: Data Output Format bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         | For 10-bit operation:<br>11 = Signed fractional (Dout = sddd dddd dd00 0000, where s =.NOT.d<9>)<br>10 = Fractional (Dout = dddd dddd dd00 0000)<br>01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NOT.d<9>)<br>00 = Integer (Dout = 0000 00dd dddd dddd)                                                                                                                                                                                                                                       |

|         | For 12-bit operation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | 11 = Signed fractional (Dout = sddd dddd dddd 0000, where s = .NOT.d<11>)                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | 10 = Fractional (Dout = dddd dddd dddd 0000)                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 01 = Signed Integer (Dout = ssss sddd dddd dddd, where s = .NOT.d<11>)<br>00 = Integer (Dout = 0000 dddd dddd dddd)                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |