Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc304-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents

| dsPIC | C33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 Product Families | 2   |

|-------|-----------------------------------------------------------------------------------|-----|

| 1.0   | Device Overview                                                                   |     |

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers             |     |

| 3.0   | CPU                                                                               |     |

| 4.0   | Memory Organization                                                               |     |

| 5.0   | Flash Program Memory                                                              | 73  |

| 6.0   | Resets                                                                            |     |

| 7.0   | Interrupt Controller                                                              |     |

| 8.0   | Direct Memory Access (DMA)                                                        | 131 |

| 9.0   | Oscillator Configuration                                                          | 143 |

| 10.0  | Power-Saving Features                                                             | 155 |

| 11.0  | I/O Ports                                                                         | 163 |

|       | Timer1                                                                            |     |

| 13.0  | Timer2/3 And TImer4/5                                                             | 199 |

| 14.0  | Input Capture                                                                     | 205 |

| 15.0  | Output Compare                                                                    | 209 |

|       | Motor Control PWM Module                                                          |     |

|       | Quadrature Encoder Interface (QEI) Module                                         |     |

|       | Serial Peripheral Interface (SPI)                                                 |     |

|       | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                     |     |

| 20.0  | Universal Asynchronous Receiver Transmitter (UART)                                |     |

|       | Enhanced CAN (ECAN™) Module                                                       |     |

|       | 10-bit/12-bit Analog-to-Digital Converter (ADC1)                                  |     |

| 23.0  | Audio Digital-to-Analog Converter (DAC)                                           |     |

|       | Comparator Module                                                                 |     |

|       | Real-Time Clock and Calendar (RTCC)                                               |     |

|       | Programmable Cyclic Redundancy Check (CRC) Generator                              |     |

|       | Parallel Master Port (PMP)                                                        |     |

| 28.0  | Special Features                                                                  | 335 |

|       | Instruction Set Summary                                                           |     |

|       | Development Support                                                               |     |

|       | Electrical Characteristics                                                        |     |

|       | High Temperature Electrical Characteristics                                       |     |

|       | DC and AC Device Characteristics Graphs                                           |     |

|       | Packaging Information                                                             |     |

| Appe  | ndix A: Revision History                                                          | 439 |

|       | <                                                                                 |     |

|       | Nicrochip Web Site                                                                |     |

|       | omer Change Notification Service                                                  |     |

| Custo | omer Support                                                                      | 455 |

|       | ler Response                                                                      |     |

| Produ | uct Identification System                                                         | 457 |

| TABLE 1-1: | PINOU       | T I/O DES       | CRIPT       | IONS (CONTINUED)                                                             |

|------------|-------------|-----------------|-------------|------------------------------------------------------------------------------|

| Pin Name   | Pin<br>Type | Buffer<br>Type  | PPS         | Description                                                                  |

| FLTA1      | I           | ST              | Yes         | PWM1 Fault A input.                                                          |

| PWM1L1     | 0           |                 | No          | PWM1 Low output 1                                                            |

| PWM1H1     | 0           | —               | No          | PWM1 High output 1                                                           |

| PWM1L2     | 0           | —               | No          | PWM1 Low output 2                                                            |

| PWM1H2     | 0           |                 | No          | PWM1 High output 2                                                           |

| PWM1L3     | 0           |                 | No          | PWM1 Low output 3                                                            |

| PWM1H3     | 0           |                 | No          | PWM1 High output 3                                                           |

| FLTA2      | I           | ST              | Yes         | PWM2 Fault A input.                                                          |

| PWM2L1     | 0           |                 | No          | PWM2 Low output 1                                                            |

| PWM2H1     | 0           |                 | No          | PWM2 High output 1                                                           |

| PGED1      | I/O         | ST              | No          | Data I/O pin for programming/debugging communication channel 1.              |

| PGEC1      | I           | ST              | No          | Clock input pin for programming/debugging communication channel 1.           |

| PGED2      | I/O         | ST              | No          | Data I/O pin for programming/debugging communication channel 2.              |

| PGEC2      | I           | ST              | No          | Clock input pin for programming/debugging communication channel 2.           |

| PGED3      | I/O         | ST              | No          | Data I/O pin for programming/debugging communication channel 3.              |

| PGEC3      | I           | ST              | No          | Clock input pin for programming/debugging communication channel 3.           |

| MCLR       | I/P         | ST              | No          | Master Clear (Reset) input. This pin is an active-low Reset to the device.   |

| AVDD       | Р           | Р               | No          | Positive supply for analog modules. This pin must be connected at all times. |

| AVss       | Р           | Р               | No          | Ground reference for analog modules.                                         |

| Vdd        | Р           | —               | No          | Positive supply for peripheral logic and I/O pins.                           |

| VCAP       | Р           | _               | No          | CPU logic filter capacitor connection.                                       |

| Vss        | Р           | —               | No          | Ground reference for logic and I/O pins.                                     |

| VREF+      | I           | Analog          | No          | Analog voltage reference (high) input.                                       |

| VREF-      | I           | Analog          | No          | Analog voltage reference (low) input.                                        |

|            | c = c M c   | C as man a tile | La liana de | or output Applog = Applog input P = Power                                    |

| TABLE 1-1: | <b>PINOUT I/O DESCRIPTIONS</b> | (CONTINUED) |

|------------|--------------------------------|-------------|

|            |                                |             |

**Legend:** CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select

Analog = Analog input P = Power O = Output TTL = TTL input buffer

I = Input

## TABLE 4-9: 2-OUTPUT PWM2 REGISTER MAP

| SFR Name  | Addr | Bit 15     | Bit 14 | Bit 13                         | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8      | Bit 7               | Bit 6      | Bit 5  | Bit 4 | Bit 3 | Bit 2   | Bit 1  | Bit 0  | Reset State |

|-----------|------|------------|--------|--------------------------------|--------|--------|--------|---------|------------|---------------------|------------|--------|-------|-------|---------|--------|--------|-------------|

| P2TCON    | 05C0 | PTEN       | -      | PTSIDL                         | _      | —      | —      | -       | —          |                     | PTOPS      | 6<3:0> |       | PTCKP | 'S<1:0> | PTMO   | D<1:0> | 0000        |

| P2TMR     | 05C2 | PTDIR      |        | PWM Timer Count Value Register |        |        |        |         |            |                     |            |        | 0000  |       |         |        |        |             |

| P2TPER    | 05C4 | _          |        |                                |        |        |        |         | PWM Time   | Base Perio          | d Register |        |       |       |         |        |        | 0000        |

| P2SECMP   | 05C6 | SEVTDIR    |        |                                |        |        |        | PW      | /M Special | Event Com           | pare Regis | ter    |       |       |         |        |        | 0000        |

| PWM2CON1  | 05C8 | _          | _      | _                              | _      | _      | _      | _       | PMOD1      | _                   | _          | _      | PEN1H | _     | _       | -      | PEN1L  | OOFF        |

| PWM2CON2  | 05CA | _          | _      | _                              | _      |        | SEVO   | PS<3:0> |            | _                   | _          | _      | _     | _     | IUE     | OSYNC  | UDIS   | 0000        |

| P2DTCON1  | 05CC | DTBPS      | <1:0>  |                                |        | DTB    | <5:0>  |         |            | DTAPS<1:0> DTA<5:0> |            |        |       |       |         |        | 0000   |             |

| P2DTCON2  | 05CE | _          | _      | _                              | _      | _      | _      | _       | _          | _                   | _          | _      | _     | _     | _       | DTS1A  | DTS1I  | 0000        |

| P2FLTACON | 05D0 | _          | _      | _                              | _      | _      | _      | FAOV1H  | FAOV1L     | FLTAM               | _          | _      | _     | _     | _       | -      | FAEN1  | 0000        |

| P2OVDCON  | 05D4 | _          | _      | —                              | _      | _      | —      | POVD1H  | POVD1L     | —                   | _          | —      | _     | _     | _       | POUT1H | POUT1L | FF00        |

| P2DC1     | 05D6 |            |        |                                |        |        |        | PWN     | / Duty Cyc | le #1 Regist        | ter        |        |       |       |         |        |        | 0000        |

| Lagandi   | ·    | monted rea |        |                                |        |        |        |         |            |                     |            |        |       |       |         |        |        |             |

Legend: — = unimplemented, read as '0'

## TABLE 4-10: QEI1 REGISTER MAP

| SFR<br>Name | Addr | Bit 15 | Bit 14                 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8 | Bit 7 | Bit 6  | Bit 5     | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0    | Reset State |

|-------------|------|--------|------------------------|---------|--------|--------|--------|---------|-------|-------|--------|-----------|-------|--------|--------|-------|----------|-------------|

| QEI1CON     | 01E0 | CNTERR | _                      | QEISIDL | INDX   | UPDN   | Q      | EIM<2:0 | >     | SWPAB | PCDOUT | TQGATE    | TQCKP | S<1:0> | POSRES | TQCS  | UPDN_SRC | 0000        |

| DFLT1CON    | 01E2 | _      | _                      | _       |        | _      | IMV<   | <1:0>   | CEID  | QEOUT |        | QECK<2:0> |       | _      | _      | _     | _        | 0000        |

| POS1CNT     | 01E4 |        | Position Counter<15:0> |         |        |        |        |         |       |       | 0000   |           |       |        |        |       |          |             |

| MAX1CNT     | 01E6 |        | Maximum Count<15:0>    |         |        |        |        |         |       |       |        |           |       | FFFF   |        |       |          |             |

Legend: — = unimplemented, read as '0'

## TABLE 4-11: QEI2 REGISTER MAP

| SFR<br>Name | Addr | Bit 15                 | Bit 14              | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8 | Bit 7 | Bit 6  | Bit 5     | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0    | Reset State |

|-------------|------|------------------------|---------------------|---------|--------|--------|--------|---------|-------|-------|--------|-----------|-------|--------|--------|-------|----------|-------------|

| QEI2CON     | 01F0 | CNTERR                 | _                   | QEISIDL | INDX   | UPDN   | Q      | EIM<2:0 | >     | SWPAB | PCDOUT | TQGATE    | TQCKP | S<1:0> | POSRES | TQCS  | UPDN_SRC | 0000        |

| DFLT2CON    | 01F2 | _                      |                     | _       | —      | _      | IMV<   | <1:0>   | CEID  | QEOUT |        | QECK<2:0> |       | _      | _      | _     | _        | 0000        |

| POS2CNT     | 01F4 | Position Counter<15:0> |                     |         |        |        |        |         | 0000  |       |        |           |       |        |        |       |          |             |

| MAX2CNT     | 01F6 |                        | Maximum Count<15:0> |         |        |        |        |         |       |       |        |           | FFFF  |        |        |       |          |             |

**Legend:** — = unimplemented, read as '0'

© 2007-2012 Microchip Technology Inc.

| File Name  | Addr          | Bit 15       | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10     | Bit 9  | Bit 8      | Bit 7                                                         | Bit 6    | Bit 5              | Bit 4  | Bit 3     | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|--------------|-----------|--------|--------|--------|------------|--------|------------|---------------------------------------------------------------|----------|--------------------|--------|-----------|--------|--------|--------|---------------|

|            | 0400-<br>041E |              |           | -      |        |        |            |        | See defini | tion when V                                                   | VIN = x  | •                  |        |           |        | -      |        |               |

| C1BUFPNT1  | 0420          |              | F3BF      | P<3:0> |        |        | F2BF       | P<3:0> |            |                                                               | F1BP     | <3:0>              |        |           | F0BP   | <3:0>  |        | 0000          |

| C1BUFPNT2  | 0422          |              | F7BF      | P<3:0> |        |        | F6BF       | P<3:0> |            |                                                               | F5BP     | <3:0>              |        |           | F4BP   | <3:0>  |        | 0000          |

| C1BUFPNT3  | 0424          |              | F11B      | P<3:0> |        |        | F10B       | P<3:0> |            | F9BP<3:0>                                                     |          |                    |        | F8BP<3:0> |        |        |        | 0000          |

| C1BUFPNT4  | 0426          |              | F15BI     | P<3:0> |        |        | F14B       | P<3:0> |            | F13BP<3:0>                                                    |          |                    |        |           | F12BF  | °<3:0> |        | 0000          |

| C1RXM0SID  | 0430          |              | SID<10:3> |        |        |        | SID<2:0> — |        |            |                                                               | MIDE     | —                  | EID<   | 17:16>    | XXXX   |        |        |               |

| C1RXM0EID  | 0432          |              | EID<15:8> |        |        |        |            |        | EID<7:0>   |                                                               |          |                    |        |           |        |        | XXXX   |               |

| C1RXM1SID  | 0434          |              |           |        | SID<   | 10:3>  |            |        |            |                                                               | SID<2:0> |                    | —      | MIDE      |        | EID<   | 17:16> | XXXX          |

| C1RXM1EID  | 0436          |              |           |        | EID<   | 15:8>  |            |        |            |                                                               |          |                    | EID<   | 7:0>      |        |        |        | XXXX          |

| C1RXM2SID  | 0438          |              |           |        | SID<   | 10:3>  |            |        |            |                                                               | SID<2:0> |                    | _      | MIDE      |        | EID<   | 17:16> | XXXX          |

| C1RXM2EID  | 043A          |              |           |        | EID<   | 15:8>  |            |        |            |                                                               |          |                    | EID<   | 7:0>      |        |        |        | XXXX          |

| C1RXF0SID  | 0440          |              |           |        | SID<   | 10:3>  |            |        |            |                                                               | SID<2:0> |                    | _      | EXIDE     |        | EID<   | 17:16> | XXXX          |

| C1RXF0EID  | 0442          |              |           |        | EID<   | 15:8>  |            |        |            |                                                               |          |                    | EID<   | 7:0>      |        |        |        | XXXX          |

| C1RXF1SID  | 0444          |              | SID<10:3> |        |        |        |            |        | SID<2:0>   |                                                               | —        | EXIDE              | —      | EID<      | 17:16> | XXXX   |        |               |

| C1RXF1EID  | 0446          |              | EID<15:8> |        |        |        |            |        |            |                                                               | EID<     | 7:0>               |        |           |        | XXXX   |        |               |

| C1RXF2SID  | 0448          | SID<10:3>    |           |        |        |        | SID<2:0>   |        | —          | EXIDE                                                         |          | EID<               | 17:16> | xxxx      |        |        |        |               |

| C1RXF2EID  | 044A          |              | EID<15:8> |        |        |        |            |        |            |                                                               |          | EID<               | 7:0>   |           |        |        | xxxx   |               |

| C1RXF3SID  | 044C          |              |           |        | SID<   | 10:3>  |            |        |            | SID<2:0> — EXIDE — EID<17:16>                                 |          |                    |        |           |        | 17:16> | xxxx   |               |

| C1RXF3EID  | 044E          |              |           |        | EID<   | 15:8>  |            |        |            | EID<7:0>                                                      |          |                    |        |           |        |        | xxxx   |               |

| C1RXF4SID  | 0450          |              |           |        | SID<   | 10:3>  |            |        |            |                                                               | SID<2:0> | EXIDE — EID<17:16> |        |           |        | xxxx   |        |               |

| C1RXF4EID  | 0452          |              |           |        | EID<   | 15:8>  |            |        |            | EID<7:0>                                                      |          |                    |        |           |        |        |        | xxxx          |

| C1RXF5SID  | 0454          |              |           |        | SID<   | 10:3>  |            |        |            | SID<2:0>         —         EXIDE         —         EID<17:16> |          |                    |        |           |        |        | 17:16> | xxxx          |

| C1RXF5EID  | 0456          |              |           |        | EID<   | 15:8>  |            |        |            |                                                               |          |                    | EID<   | 7:0>      |        |        |        | xxxx          |

| C1RXF6SID  | 0458          |              |           |        | SID<   | 10:3>  |            |        |            |                                                               | SID<2:0> |                    | —      | EXIDE     | _      | EID<   | 17:16> | XXXX          |

| C1RXF6EID  | 045A          |              |           |        | EID<   | 15:8>  |            |        |            |                                                               |          |                    | EID<   | 7:0>      |        | •      |        | XXXX          |

| C1RXF7SID  | 045C          |              |           |        | SID<   | 10:3>  |            |        |            |                                                               | SID<2:0> |                    | —      | EXIDE     | —      | EID<   | 17:16> | XXXX          |

| C1RXF7EID  | 045E          |              |           |        | EID<   | 15:8>  |            |        |            |                                                               |          |                    | EID<   | 7:0>      |        | •      |        | XXXX          |

| C1RXF8SID  | 0460          |              |           |        | SID<   | 10:3>  |            |        |            |                                                               | SID<2:0> |                    | —      | EXIDE     | _      | EID<   | 17:16> | XXXX          |

| C1RXF8EID  | 0462          | 52 EID<15:8> |           |        |        |        |            |        |            | EID<                                                          | 7:0>     |                    |        |           | XXXX   |        |        |               |

| C1RXF9SID  | 0464          |              |           |        | SID<   | 10:3>  |            |        |            |                                                               | SID<2:0> |                    | —      | EXIDE     | _      | EID<   | 17:16> | XXXX          |

| C1RXF9EID  | 0466          |              |           |        | EID<   | 15:8>  |            |        |            |                                                               |          |                    | EID<   | 7:0>      |        | -      |        | XXXX          |

| C1RXF10SID | 0468          |              |           |        | SID<   | 10:3>  |            |        |            |                                                               | SID<2:0> |                    | —      | EXIDE     | —      | EID<   | 17:16> | XXXX          |

| C1RXF10EID | 046A          |              |           |        | EID<   | 15:8>  |            |        |            |                                                               |          |                    | EID<   | 7:0>      |        |        |        | XXXX          |

| C1RXF11SID | 046C          |              |           |        | SID<   | 10:3>  |            |        |            |                                                               | SID<2:0> |                    | _      | EXIDE     | —      | EID<   | 17:16> | XXXX          |

#### ~~ AOTOLA MAIN AND -I- DIOOOF IO (BLOOOO/00 /)

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

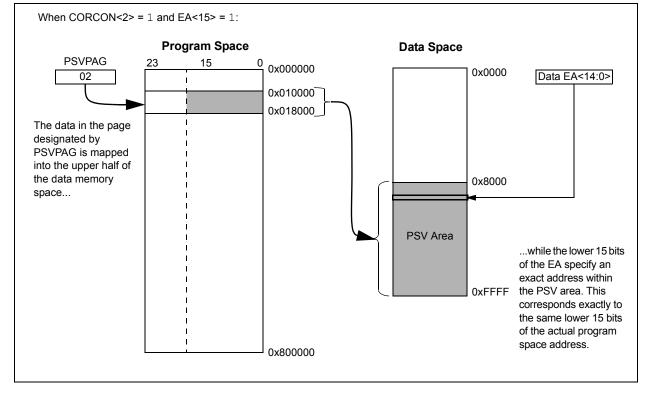

#### 4.8.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDH).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address 0x8000 and higher maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop allows the instruction using PSV to access data, to execute in a single cycle.

## FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

| R/W-0            | R/W-0                                                                                                       | R/W-0                                                                                                                                                | U-0                                                                  | U-0              | R/W-0           | R/W-0            | U-0   |

|------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------|-----------------|------------------|-------|

| FLTA1IF          | RTCIF                                                                                                       | DMA5IF                                                                                                                                               |                                                                      | _                | QEI1IF          | PWM1IF           | _     |

| bit 15           |                                                                                                             |                                                                                                                                                      |                                                                      | ÷                |                 |                  | bit 8 |

|                  |                                                                                                             |                                                                                                                                                      |                                                                      |                  |                 |                  |       |

| U-0              | U-0                                                                                                         | U-0                                                                                                                                                  | U-0                                                                  | U-0              | U-0             | U-0              | U-0   |

|                  | <u> </u>                                                                                                    | —                                                                                                                                                    | _                                                                    |                  |                 | —                | _     |

| bit 7            |                                                                                                             |                                                                                                                                                      |                                                                      |                  |                 |                  | bit ( |

|                  |                                                                                                             |                                                                                                                                                      |                                                                      |                  |                 |                  |       |

| Legend:          |                                                                                                             |                                                                                                                                                      |                                                                      |                  |                 |                  |       |

| R = Readable     | e bit                                                                                                       | W = Writable b                                                                                                                                       | oit                                                                  | U = Unimple      | mented bit, rea | d as '0'         |       |

| -n = Value at    | POR                                                                                                         | '1' = Bit is set                                                                                                                                     |                                                                      | '0' = Bit is cle | eared           | x = Bit is unkno | own   |

| bit 14<br>bit 13 | 0 = Interrupt<br><b>RTCIF:</b> Real<br>1 = Interrupt<br>0 = Interrupt<br><b>DMA5IF:</b> DM<br>1 = Interrupt | request has occ<br>request has not<br>-Time Clock and<br>request has occ<br>request has not<br>IA Channel 5 Da<br>request has occ<br>request has not | occurred<br>Calendar Ir<br>urred<br>occurred<br>ta Transfer<br>urred |                  |                 | s bit            |       |

| bit 12-11        | Unimpleme                                                                                                   | nted: Read as '0                                                                                                                                     | ,                                                                    |                  |                 |                  |       |

| bit 10           | 1 = Interrupt                                                                                               | 1 Event Interrupt<br>request has occ<br>request has not                                                                                              | urred                                                                | s bit            |                 |                  |       |

| bit 9            | PWM1IF: PV                                                                                                  | VM1 Event Interr                                                                                                                                     | upt Flag Sta                                                         | atus bit         |                 |                  |       |

|                  |                                                                                                             | request has occ<br>request has not                                                                                                                   |                                                                      |                  |                 |                  |       |

## REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

Unimplemented: Read as '0'

bit 8-0

| R/W-0        | R/W-0         | R/W-0                              | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0   |

|--------------|---------------|------------------------------------|----------------|------------------|-----------------|-----------------|---------|

| U2TXIE       | U2RXIE        | INT2IE                             | T5IE           | T4IE             | OC4IE           | OC3IE           | DMA2IE  |

| bit 15       | ·             | ·                                  | ·              | •                |                 |                 | bit 8   |

|              |               |                                    |                |                  |                 |                 |         |

| R/W-0        | R/W-0         | U-0                                | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0   |

| IC8IE        | IC7IE         |                                    | INT1IE         | CNIE             | CMIE            | MI2C1IE         | SI2C1IE |

| bit 7        |               |                                    |                |                  |                 |                 | bit 0   |

|              |               |                                    |                |                  |                 |                 |         |

| Legend:      | I I.:.        |                                    | L :4           |                  |                 | -l (0)          |         |

| R = Readab   |               | W = Writable                       |                |                  | nented bit, rea |                 |         |

| -n = Value a | t POR         | '1' = Bit is set                   | t              | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |

| bit 15       |               | RT2 Transmitte                     | r Intorrunt En | abla hit         |                 |                 |         |

| DIL 15       |               | request enable                     | -              |                  |                 |                 |         |

|              |               | request not en                     |                |                  |                 |                 |         |

| bit 14       | U2RXIE: UA    | RT2 Receiver I                     | nterrupt Enab  | le bit           |                 |                 |         |

|              | 1 = Interrupt | request enable                     | d              |                  |                 |                 |         |

|              | 0 = Interrupt | request not ena                    | abled          |                  |                 |                 |         |

| bit 13       |               | rnal Interrupt 2                   |                |                  |                 |                 |         |

|              |               | request enable                     |                |                  |                 |                 |         |

| bit 12       | -             | request not ena                    |                |                  |                 |                 |         |

| DIL 12       |               | i Interrupt Enab<br>request enable |                |                  |                 |                 |         |

|              |               | request not enable                 |                |                  |                 |                 |         |

| bit 11       | T4IE: Timer4  | Interrupt Enab                     | le bit         |                  |                 |                 |         |

|              | 1 = Interrupt | request enable                     | d              |                  |                 |                 |         |

|              | 0 = Interrupt | request not ena                    | abled          |                  |                 |                 |         |

| bit 10       | -             | out Compare Ch                     |                | upt Enable bit   |                 |                 |         |

|              |               | request enable                     |                |                  |                 |                 |         |

| hit 0        | •             | request not ena                    |                | unt Enchlo hit   |                 |                 |         |

| bit 9        | •             | out Compare Ch<br>request enable   |                | upt Enable bit   |                 |                 |         |

|              |               | request not enable                 |                |                  |                 |                 |         |

| bit 8        | -             | IA Channel 2 D                     |                | Complete Interr  | upt Enable bit  |                 |         |

|              |               | request enable                     |                | ·                |                 |                 |         |

|              | 0 = Interrupt | request not ena                    | abled          |                  |                 |                 |         |

| bit 7        | IC8IE: Input  | Capture Chann                      | el 8 Interrupt | Enable bit       |                 |                 |         |

|              |               | request enable                     |                |                  |                 |                 |         |

|              | •             | request not en                     |                |                  |                 |                 |         |

| bit 6        | -             | Capture Chann                      | -              | Enable bit       |                 |                 |         |

|              |               | request enable<br>request not ena  |                |                  |                 |                 |         |

| hit 5        |               | ntequest not only                  |                |                  |                 |                 |         |

bit 5Unimplemented: Read as '0'bit 4INT1IE: External Interrupt 1 Enable

#### bit 4 INT1IE: External Interrupt 1 Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled

## bit 3 CNIE: Input Change Notification Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| REGISTER     | 7-21: IPC6                                                   |                                           | PRIORITY        | CONTROL R         | EGISTER 6      |                 |       |  |  |  |  |  |  |

|--------------|--------------------------------------------------------------|-------------------------------------------|-----------------|-------------------|----------------|-----------------|-------|--|--|--|--|--|--|

| U-0          | R/W-1                                                        | R/W-0                                     | R/W-0           | U-0               | R/W-1          | R/W-0           | R/W-0 |  |  |  |  |  |  |

| _            |                                                              | T4IP<2:0>                                 |                 | —                 |                | OC4IP<2:0>      |       |  |  |  |  |  |  |

| bit 15       |                                                              |                                           |                 |                   |                |                 | bit   |  |  |  |  |  |  |

| U-0          | R/W-1                                                        | R/W-0                                     | R/W-0           | U-0               | R/W-1          | R/W-0           | R/W-0 |  |  |  |  |  |  |

| _            |                                                              | OC3IP<2:0>                                |                 | _                 |                | DMA2IP<2:0>     |       |  |  |  |  |  |  |

| bit 7        |                                                              |                                           |                 |                   |                |                 | bit   |  |  |  |  |  |  |

| Legend:      |                                                              |                                           |                 |                   |                |                 |       |  |  |  |  |  |  |

| R = Readab   | le bit                                                       | W = Writable I                            | oit             | U = Unimple       | mented bit, re | ad as '0'       |       |  |  |  |  |  |  |

| -n = Value a | t POR                                                        | '1' = Bit is set                          |                 | '0' = Bit is cle  | eared          | x = Bit is unkn | own   |  |  |  |  |  |  |

|              |                                                              |                                           |                 |                   |                |                 |       |  |  |  |  |  |  |

| bit 15       | Unimpleme                                                    | ented: Read as 'o                         | )'              |                   |                |                 |       |  |  |  |  |  |  |

| bit 14-12    | T4IP<2:0>:                                                   | Timer4 Interrupt                          | Priority bits   |                   |                |                 |       |  |  |  |  |  |  |

|              | 111 = Inter                                                  | rupt is priority 7 (ł                     | nighest priori  | ity interrupt)    |                |                 |       |  |  |  |  |  |  |

|              | •                                                            |                                           |                 |                   |                |                 |       |  |  |  |  |  |  |

|              | •                                                            |                                           |                 |                   |                |                 |       |  |  |  |  |  |  |

|              | 001 <b>= Inter</b>                                           | rupt is priority 1                        |                 |                   |                |                 |       |  |  |  |  |  |  |

|              |                                                              | rupt source is disa                       | abled           |                   |                |                 |       |  |  |  |  |  |  |

| bit 11       | Unimplemented: Read as '0'                                   |                                           |                 |                   |                |                 |       |  |  |  |  |  |  |

| bit 10-8     | OC4IP<2:0>: Output Compare Channel 4 Interrupt Priority bits |                                           |                 |                   |                |                 |       |  |  |  |  |  |  |

|              | 111 = Inter                                                  | rupt is priority 7 (ł                     | nighest priori  | ity interrupt)    |                |                 |       |  |  |  |  |  |  |

|              | •                                                            |                                           |                 |                   |                |                 |       |  |  |  |  |  |  |

|              | •                                                            |                                           |                 |                   |                |                 |       |  |  |  |  |  |  |

|              | 001 = Inter                                                  | rupt is priority 1                        |                 |                   |                |                 |       |  |  |  |  |  |  |

|              |                                                              | rupt source is disa                       | abled           |                   |                |                 |       |  |  |  |  |  |  |

| bit 7        | Unimpleme                                                    | ented: Read as 'o                         | )'              |                   |                |                 |       |  |  |  |  |  |  |

| bit 6-4      | OC3IP<2:0                                                    | >: Output Compa                           | re Channel      | 3 Interrupt Prior | rity bits      |                 |       |  |  |  |  |  |  |

|              | 111 = Inter                                                  | rupt is priority 7 (ł                     | nighest priori  | ity interrupt)    |                |                 |       |  |  |  |  |  |  |

|              | •                                                            |                                           |                 |                   |                |                 |       |  |  |  |  |  |  |

|              | •                                                            |                                           |                 |                   |                |                 |       |  |  |  |  |  |  |

|              |                                                              | rupt is priority 1<br>rupt source is disa | ahled           |                   |                |                 |       |  |  |  |  |  |  |

| bit 3        |                                                              | ented: Read as '0                         |                 |                   |                |                 |       |  |  |  |  |  |  |

| bit 2-0      | -                                                            | :0>: DMA Channe                           |                 | ansfer Complete   | Interrunt Prid | ority bits      |       |  |  |  |  |  |  |

|              |                                                              | rupt is priority 7 (h                     |                 |                   | - menupi Phi   | Jity Dita       |       |  |  |  |  |  |  |

|              | •                                                            |                                           | ingricor priori |                   |                |                 |       |  |  |  |  |  |  |

|              | •                                                            |                                           |                 |                   |                |                 |       |  |  |  |  |  |  |

|              | •                                                            | and the methods of the state              |                 |                   |                |                 |       |  |  |  |  |  |  |

|              |                                                              | rupt is priority 1<br>rupt source is disa | abled           |                   |                |                 |       |  |  |  |  |  |  |

|              |                                                              |                                           |                 |                   |                |                 |       |  |  |  |  |  |  |

# REGISTER 7-21: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

| REGISTER 9-5: | ACLKCON: AUXILIARY CLOCK DIVISOR CONTROL REGISTER <sup>(1)</sup> |

|---------------|------------------------------------------------------------------|

|---------------|------------------------------------------------------------------|

| U-0                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                         | R/W-0                                                                         | R/W-0                                | R/W-0            | R/W-0 |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------|------------------|-------|

| _                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                | SELACLK                                                                                                                                                                                                                                                                                                              | AOSCI                                                                                                         | MD<1:0>                                                                       | A                                    | PSTSCLR<2:0>     |       |

| bit 15                |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                      |                                                                                                               |                                                                               |                                      |                  | bit   |

| <b>D</b> #44 0        |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                      |                                                                                                               |                                                                               |                                      |                  |       |

| R/W-0                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                                                                                                                                  | U-0                                                                                                           | U-0                                                                           | U-0                                  | U-0              | U-0   |

| ASRCSEL<br>bit 7      |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                      | _                                                                                                             | _                                                                             | _                                    | _                | bit   |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                      |                                                                                                               |                                                                               |                                      |                  | DIL   |

| Legend:               |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                      |                                                                                                               |                                                                               |                                      |                  |       |

| R = Readabl           | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                            | W = Writable b                                                                                                                                                                                                                                                                                                       | oit                                                                                                           | U = Unimpler                                                                  | mented bit, rea                      | d as '0'         |       |

| -n = Value at         | POR                                                                                                                                                                                                                                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                     |                                                                                                               | '0' = Bit is cle                                                              | ared                                 | x = Bit is unkno | own   |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                      |                                                                                                               |                                                                               |                                      |                  |       |

| bit 15-14             | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                       | ted: Read as '0                                                                                                                                                                                                                                                                                                      | )'                                                                                                            |                                                                               |                                      |                  |       |

| bit 13                | SELACLK: Select Auxiliary Clock Source for Auxiliary Clock Divider                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                      |                                                                                                               |                                                                               |                                      |                  |       |

| -                     | SELACER. S                                                                                                                                                                                                                                                                                                                                                                                                                                       | elect Auxiliary C                                                                                                                                                                                                                                                                                                    |                                                                                                               |                                                                               | Dent Britael                         |                  |       |

| -                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Oscillators prov                                                                                                                                                                                                                                                                                                     |                                                                                                               | -                                                                             |                                      | ivider           |       |

| -                     | 1 = Auxiliary (                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                      | ides the sour                                                                                                 | ce clock for Au                                                               | ixiliary Clock Di                    |                  |       |

| bit 12-11             | 1 = Auxiliary (<br>0 = PLL outpu                                                                                                                                                                                                                                                                                                                                                                                                                 | Oscillators prov                                                                                                                                                                                                                                                                                                     | ides the sour<br>les the sourc                                                                                | ce clock for Au<br>e clock for the                                            | ixiliary Clock Di                    |                  |       |

| bit 12-11             | 1 = Auxiliary (<br>0 = PLL outpu<br>AOSCMD<1:                                                                                                                                                                                                                                                                                                                                                                                                    | Oscillators prov<br>ut (Fosc) provid                                                                                                                                                                                                                                                                                 | ides the sour<br>les the sourc<br>scillator Mode                                                              | ce clock for Au<br>e clock for the                                            | ixiliary Clock Di                    |                  |       |

| bit 12-11             | 1 = Auxiliary (<br>0 = PLL outpu<br><b>AOSCMD&lt;1:</b><br>11 = EC Exte                                                                                                                                                                                                                                                                                                                                                                          | Oscillators prov<br>ut (Fosc) provid<br><b>0&gt;:</b> Auxiliary Os                                                                                                                                                                                                                                                   | ides the sour<br>les the sourc<br>scillator Mode<br>e Select                                                  | ce clock for Au<br>e clock for the                                            | ixiliary Clock Di                    |                  |       |

| bit 12-11             | 1 = Auxiliary (<br>0 = PLL outpu<br>AOSCMD<1:<br>11 = EC Exte<br>10 = XT Oscil                                                                                                                                                                                                                                                                                                                                                                   | Oscillators prov<br>ut (Fosc) provid<br><b>0&gt;:</b> Auxiliary Os<br>mal Clock Mod                                                                                                                                                                                                                                  | ides the sour<br>les the sourc<br>scillator Mode<br>e Select<br>ect                                           | ce clock for Au<br>e clock for the                                            | ixiliary Clock Di                    |                  |       |

| bit 12-11             | 1 = Auxiliary (<br>0 = PLL outpu<br><b>AOSCMD&lt;1:</b><br>11 = EC Exte<br>10 = XT Oscii<br>01 = HS Osci                                                                                                                                                                                                                                                                                                                                         | Oscillators prov<br>ut (Fosc) provid<br><b>0&gt;:</b> Auxiliary Os<br>rnal Clock Mod<br>llator Mode Sele                                                                                                                                                                                                             | ides the sour<br>les the sourc<br>scillator Mode<br>e Select<br>ect<br>ect                                    | ce clock for Au<br>e clock for the<br>e                                       | ixiliary Clock Di                    |                  |       |

| bit 12-11<br>bit 10-8 | 1 = Auxiliary (<br>0 = PLL outpu<br><b>AOSCMD&lt;1:</b><br>11 = EC Exte<br>10 = XT Oscil<br>01 = HS Osci<br>00 = Auxiliary                                                                                                                                                                                                                                                                                                                       | Oscillators prov<br>ut (Fosc) provid<br><b>0&gt;:</b> Auxiliary Os<br>mal Clock Mod<br>llator Mode Sele<br>llator Mode Sele                                                                                                                                                                                          | ides the sour<br>les the sourc<br>scillator Mode<br>e Select<br>ect<br>ect<br>ect<br>ibled (default           | ce clock for Au<br>e clock for the<br>e                                       | ixiliary Clock Di                    |                  |       |