Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

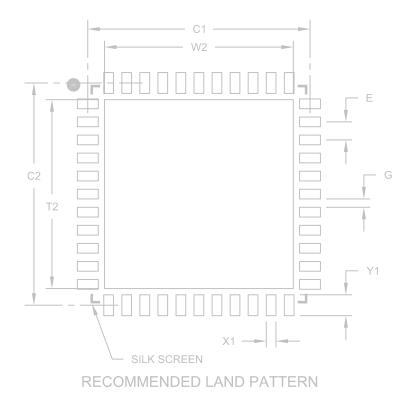

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc304-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup><br>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | RA: REPEAT Loop Active bit<br>1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | N: MCU ALU Negative bit<br>1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 2   | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (two's complement). It indicates an overflow of a magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                  |

| bit 1   | <ul> <li>Z: MCU ALU Zero bit</li> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                       |

| bit 0   | <b>C</b> : MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                      |

- Note 1: This bit can be read or cleared (not set).

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: This bit can be read or cleared (not set). Clearing this bit clears SA and SB.

## TABLE 4-1: CPU CORE REGISTERS MAP (CONTINUED)

|          |      |        |               |        |        |        | ,      |        |          |              |           |         |       |       |       |       |       |               |

|----------|------|--------|---------------|--------|--------|--------|--------|--------|----------|--------------|-----------|---------|-------|-------|-------|-------|-------|---------------|

| SFR Name | Addr | Bit 15 | Bit 14        | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8    | Bit 7        | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| MODCON   | 0046 | XMODEN | YMODEN        | -      | —      |        | BWN    | /<3:0> |          |              | YWM       | <3:0>   |       |       | XWM   | <3:0> |       | 0000          |

| XMODSRT  | 0048 |        |               |        |        |        |        | >      | (S<15:1> |              |           |         |       |       |       |       | 0     | XXXX          |

| XMODEND  | 004A |        | XE<15:1>      |        |        |        |        |        |          |              | 1         | XXXX    |       |       |       |       |       |               |

| YMODSRT  | 004C |        | YS<15:1>      |        |        |        |        |        |          |              | 0         | XXXX    |       |       |       |       |       |               |

| YMODEND  | 004E |        | YE<15:1>      |        |        |        |        |        |          |              | 1         | XXXX    |       |       |       |       |       |               |

| XBREV    | 0050 | BREN   | BREN XB<14:0> |        |        |        |        |        |          |              |           | XXXX    |       |       |       |       |       |               |

| DISICNT  | 0052 | —      | _             |        |        |        |        |        | Disabl   | e Interrupts | Counter R | egister |       |       |       |       |       | XXXX          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

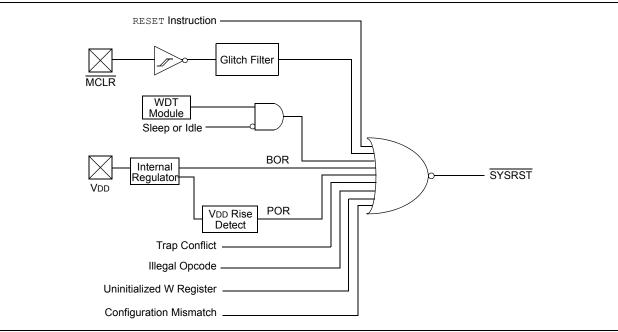

## 6.0 RESETS

- **Note 1:** This data sheet summarizes the features the dsPIC33FJ32MC302/304, of dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all reset <u>sources</u> and controls the device Master Reset Signal, <u>SYSRST</u>. The following is a list of device Reset sources:

- POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

#### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" in this data sheet for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR bit (RCON<0>), that are set. The user application can set or clear any bit at any time during the code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

## 6.3 System Reset

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices have two types of Reset:

- Cold Reset

- Warm Reset

A cold Reset is the result of a Power-on Reset (POR) or a Brown-out Reset (BOR). On a cold Reset, the FNOSC Configuration bits in the FOSC device Configuration register selects the device clock source. A warm Reset is the result of all other reset sources, including the RESET instruction. On warm Reset, the device will continue to operate from the current clock source as indicated by the Current Oscillator Selection bits (COSC<2:0>) in the Oscillator Control register (OSCCON<14:12>).

The device is kept in a Reset state until the system power supplies have stabilized at appropriate levels and the oscillator clock is ready. The description of the sequence in which this occurs is shown in Figure 6-2.

| Oscillator Mode        | Oscillator<br>Startup Delay | Oscillator<br>Startup Timer | PLL Lock Time | Total Delay             |

|------------------------|-----------------------------|-----------------------------|---------------|-------------------------|

| FRC, FRCDIV16, FRCDIVN | Toscd                       | _                           | —             | Toscd                   |

| FRCPLL                 | Toscd                       | —                           | TLOCK         | TOSCD + TLOCK           |

| XT                     | Toscd                       | Tost                        | —             | Toscd + Tost            |

| HS                     | Toscd                       | Tost                        | —             | Toscd + Tost            |

| EC                     | —                           | —                           | —             | —                       |

| XTPLL                  | Toscd                       | Тоят                        | Тьоск         | Toscd + Tost +<br>Tlock |

| HSPLL                  | Toscd                       | Тоѕт                        | Тьоск         | Toscd + Tost +<br>Tlock |

| ECPLL                  | —                           | —                           | Тьоск         | Тьоск                   |

| Sosc                   | Toscd                       | Tost                        | —             | Toscd + Tost            |

| LPRC                   | Toscd                       | —                           | —             | Toscd                   |

#### TABLE 6-1: OSCILLATOR DELAY

**Note 1:** ToscD = Oscillator Start-up Delay (1.1 μs max for FRC, 70 μs max for LPRC). Crystal Oscillator start-up times vary with crystal characteristics, load capacitance, etc.

**2:** TOST = Oscillator Start-up Timer Delay (1024 oscillator clock period). For example, TOST = 102.4 μs for a 10 MHz crystal and TOST = 32 ms for a 32 kHz crystal.

**3:** TLOCK = PLL lock time (1.5 ms nominal), if PLL is enabled.

| Symbol | Parameter                        | Value            |

|--------|----------------------------------|------------------|

| VPOR   | POR threshold                    | 1.8V nominal     |

| TPOR   | POR extension time               | 30 μs maximum    |

| VBOR   | BOR threshold                    | 2.5V nominal     |

| TBOR   | BOR extension time               | 100 μs maximum   |

| TPWRT  | Programmable power-up time delay | 0-128 ms nominal |

| TFSCM  | Fail-Safe Clock Monitor Delay    | 900 μs maximum   |

| IABLE 6-2: USCILLATUR PARAMETERS | <b>TABLE 6-2:</b> | <b>OSCILLATOR PARAMETERS</b> |

|----------------------------------|-------------------|------------------------------|

|----------------------------------|-------------------|------------------------------|

Note: When the device exits the Reset condition (begins normal operation), the device operating parameters (voltage, frequency, temperature, etc.) must be within their operating ranges, otherwise, the device may not function correctly. The user application must ensure that the delay between the time power is first applied, and the time SYSRST becomes inactive, is long enough to get operating parameters all within specification.

## 6.4 Power-on Reset (POR)

A Power-on Reset (POR) circuit ensures the device is reset from power-on. The POR circuit is active until VDD crosses the VPOR threshold and the delay TPOR has elapsed. The delay TPOR ensures the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to Section 31.0 "Electrical Characteristics" for details.

The POR status bit (POR) in the Reset Control register (RCON<0>) is set to indicate the Power-on Reset.

# 6.4.1 Brown-out Reset (BOR) and Power-up Timer (PWRT)

The on-chip regulator has a Brown-out Reset (BOR) circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses VBOR threshold and the delay TBOR has elapsed. The delay TBOR ensures the voltage regulator output becomes stable.

The BOR status bit (BOR) in the Reset Control register (RCON<1>) is set to indicate the Brown-out Reset.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The PWRT provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

The power-up timer delay (TPWRT) is programmed by the Power-on Reset Timer Value Select bits (FPWRT<2:0>) in the POR Configuration register (FPOR<2:0>), which provides eight settings (from 0 ms to 128 ms). Refer to **Section 28.0 "Special Features"** for further details.

Figure 6-3 shows the typical brown-out scenarios. The reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| REGISTER /-      | 4: INTCO         | DNZ: IN LERR                         | UPICONI     | KOL REGIST       | ER Z             |                 |        |

|------------------|------------------|--------------------------------------|-------------|------------------|------------------|-----------------|--------|

| R/W-0            | R-0              | U-0                                  | U-0         | U-0              | U-0              | U-0             | U-0    |

| ALTIVT           | DISI             | —                                    | _           | —                | —                | —               | —      |

| bit 15           |                  |                                      |             |                  |                  |                 | bit 8  |

|                  |                  |                                      |             |                  |                  |                 |        |

| U-0              | U-0              | U-0                                  | U-0         | U-0              | R/W-0            | R/W-0           | R/W-0  |

| —                |                  | _                                    | —           | —                | INT2EP           | INT1EP          | INT0EP |

| bit 7            |                  |                                      |             |                  |                  |                 | bit 0  |

|                  |                  |                                      |             |                  |                  |                 |        |

| Legend:          |                  |                                      |             |                  |                  |                 |        |

| R = Readable b   | bit              | W = Writable                         | bit         | U = Unimpler     | mented bit, read | as '0'          |        |

| -n = Value at Po | OR               | '1' = Bit is set                     |             | '0' = Bit is cle | eared            | x = Bit is unkr | nown   |

|                  |                  |                                      |             |                  |                  |                 |        |

| bit 15           |                  | ole Alternate In                     | •           | Table bit        |                  |                 |        |

|                  |                  | nate vector tabl<br>dard (default) v | -           |                  |                  |                 |        |

| bit 14           |                  | struction Statu                      |             |                  |                  |                 |        |

|                  | 1 = DISI inst    | ruction is active                    | e           |                  |                  |                 |        |

|                  | 0 = DISI inst    | ruction is not a                     | ctive       |                  |                  |                 |        |

| bit 13-3         | Unimplemen       | ted: Read as '                       | 0'          |                  |                  |                 |        |

| bit 2            | INT2EP: Exte     | ernal Interrupt 2                    | Edge Detect | Polarity Selec   | t bit            |                 |        |

|                  |                  | on negative ede                      | <i>,</i>    |                  |                  |                 |        |

|                  | •                | on positive edg                      |             |                  |                  |                 |        |

| bit 1            |                  | ernal Interrupt 1                    | 0           | Polarity Selec   | t bit            |                 |        |

|                  | 1 = Interrupt of | on negative ede                      | ge          |                  |                  |                 |        |

## REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

0 = Interrupt on positive edge

1 = Interrupt on negative edge 0 = Interrupt on positive edge

INTOEP: External Interrupt 0 Edge Detect Polarity Select bit

bit 0

| REGISTER 7      | -5: IFS0:     | INTERRUPT                            | FLAG STAT        | US REGIST        | =R 0            |                 |        |

|-----------------|---------------|--------------------------------------|------------------|------------------|-----------------|-----------------|--------|

| U-0             | R/W-0         | R/W-0                                | R/W-0            | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|                 | DMA1IF        | AD1IF                                | U1TXIF           | U1RXIF           | SPI1IF          | SPI1EIF         | T3IF   |

| bit 15          |               |                                      |                  |                  |                 |                 | bit 8  |

| R/W-0           | R/W-0         | R/W-0                                | R/W-0            | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

| T2IF            | OC2IF         | IC2IF                                | DMA0IF           | T1IF             | OC1IF           | IC1IF           | INTOIF |

| bit 7           | 00211         | 10211                                |                  |                  | 0011            |                 | bit C  |

| Legend:         |               |                                      |                  |                  |                 |                 |        |

| R = Readable    | bit           | W = Writable                         | bit              | U = Unimpler     | mented bit, rea | d as '0'        |        |

| -n = Value at F | POR           | '1' = Bit is se                      | t                | '0' = Bit is cle | ared            | x = Bit is unkn | own    |

|                 |               |                                      |                  |                  |                 |                 |        |

| bit 15          | Unimpleme     | nted: Read as                        | '0'              |                  |                 |                 |        |

| bit 14          |               | MA Channel 1 E                       |                  | omplete Interr   | upt Flag Status | s bit           |        |

|                 |               | t request has oc<br>t request has no |                  |                  |                 |                 |        |

| bit 13          | -             | C1 Conversion (                      |                  | unt Eloa Statu   | o hit           |                 |        |

| DIL 13          |               | t request has oc                     | •                | upi riay Sialu   | SDI             |                 |        |

|                 |               | t request has no                     |                  |                  |                 |                 |        |

| bit 12          | U1TXIF: UA    | RT1 Transmitte                       | r Interrupt Flag | g Status bit     |                 |                 |        |

|                 |               | t request has oc                     |                  |                  |                 |                 |        |

|                 | 0 = Interrupt | t request has no                     | ot occurred      |                  |                 |                 |        |

| bit 11          |               | RT1 Receiver I                       |                  | status bit       |                 |                 |        |

|                 |               | t request has oc                     |                  |                  |                 |                 |        |

| hit 10          | •             | t request has no                     |                  | .:.              |                 |                 |        |

| bit 10          |               | 1 Event Interrup                     | -                | DIT              |                 |                 |        |

|                 |               | t request has oc<br>t request has no |                  |                  |                 |                 |        |

| bit 9           | •             | PI1 Error Interru                    |                  | bit              |                 |                 |        |

|                 | 1 = Interrupt | t request has oc<br>t request has no | curred           |                  |                 |                 |        |

| bit 8           | -             | 3 Interrupt Flag                     |                  |                  |                 |                 |        |

|                 | 1 = Interrupt | t request has oc<br>t request has no | curred           |                  |                 |                 |        |

| bit 7           | -             | 2 Interrupt Flag                     |                  |                  |                 |                 |        |

|                 |               | t request has oc                     |                  |                  |                 |                 |        |

|                 | 0 = Interrupt | t request has no                     | ot occurred      |                  |                 |                 |        |

| bit 6           | OC2IF: Outp   | out Compare Cl                       | nannel 2 Interru | upt Flag Status  | s bit           |                 |        |

|                 |               | t request has oo<br>t request has no |                  |                  |                 |                 |        |

| bit 5           | IC2IF: Input  | Capture Chanr                        | el 2 Interrupt F | lag Status bit   |                 |                 |        |

|                 |               | t request has oc<br>t request has no |                  |                  |                 |                 |        |

| bit 4           | -             | VIA Channel 0 E                      |                  | omplete Interr   | upt Flag Status | s bit           |        |

|                 |               | t request has oc                     |                  |                  |                 |                 |        |

|                 | 0 = Interrupt |                                      |                  |                  |                 |                 |        |

|                 |               | request has he                       |                  |                  |                 |                 |        |

| bit 3           | T1IF: Timer   | 1 Interrupt Flag                     |                  |                  |                 |                 |        |

# REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| bit 10 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Jnimplement<br>CMPMD: Con<br>= Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                       | R/W-0<br>QEI2MD<br>W = Writable<br>'1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is di<br>or module is en<br>CC Module Di<br>dule is disable<br>dule is enabled | <sup>0'</sup><br>le Disable bit<br>isabled<br>nabled<br>sable bit       | U-0<br>—<br>U = Unimple<br>'0' = Bit is cle | U-0<br>U-0       | U-0<br>U-0<br>d as '0'<br>x = Bit is unkn | PMPMD<br>bit 8<br>U-0<br>bit 0 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------|------------------|-------------------------------------------|--------------------------------|

| R/W-0         CRCMD         bit 7         Legend:         R = Readable b         -n = Value at PC         bit 15-11       L         bit 15-11       L         bit 15-11       L         bit 10       C         Dit 15       L         bit 10       C         bit 3       F         bit 4       1         Dit 7       C         Dit 7       C                                                                                                                                                                | DAC1MD<br>it<br>DR<br>Jnimplement<br>CMPMD: Con<br>= Comparate<br>= Comparate<br>= Comparate<br>CMPMD: RT<br>= RTCC mo<br>= RTCC mo | QEI2MD<br>W = Writable<br>'1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                                                | PWM2MD<br>bit<br>0'<br>le Disable bit<br>isabled<br>nabled<br>sable bit | U = Unimple                                 | mented bit, read | d as '0'                                  | U-0<br>—<br>bit 0              |

| CRCMD           bit 7           Legend:           R = Readable b           -n = Value at PC           bit 15-11         L           bit 10         C           bit 10         L           0         1           0         1           0         0           bit 8         F           1         0           bit 7         C           bit 7         1 | DAC1MD<br>it<br>DR<br>Jnimplement<br>CMPMD: Con<br>= Comparate<br>= Comparate<br>= Comparate<br>CMPMD: RT<br>= RTCC mo<br>= RTCC mo | QEI2MD<br>W = Writable<br>'1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                                                | PWM2MD<br>bit<br>0'<br>le Disable bit<br>isabled<br>nabled<br>sable bit | U = Unimple                                 | mented bit, read | d as '0'                                  | bit 0                          |

| CRCMD           bit 7           Legend:           R = Readable b           -n = Value at PC           bit 15-11         L           bit 10         C           bit 10         L           0         1           0         1           0         0           bit 8         F           1         0           bit 7         C           bit 7         1 | DAC1MD<br>it<br>DR<br>Jnimplement<br>CMPMD: Con<br>= Comparate<br>= Comparate<br>= Comparate<br>CMPMD: RT<br>= RTCC mo<br>= RTCC mo | QEI2MD<br>W = Writable<br>'1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                                                | PWM2MD<br>bit<br>0'<br>le Disable bit<br>isabled<br>nabled<br>sable bit | U = Unimple                                 | mented bit, read | d as '0'                                  | bit 0                          |

| bit 7<br>Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15-11 L<br>bit 10 C<br>bit 9 F<br>1<br>0<br>bit 8 F<br>1<br>0<br>bit 8 F<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                                                                                                                                                                                                                                                                                | it<br>DR<br>Jnimplement<br>CMPMD: Con<br>= Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                           | W = Writable<br>'1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                                                          | bit<br>0'<br>le Disable bit<br>isabled<br>nabled<br>sable bit           | -                                           |                  |                                           |                                |

| Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15-11 L<br>bit 10 C<br>1<br>0<br>bit 9 F<br>1<br>0<br>bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                     | Jnimplement<br>CMPMD: Con<br>= Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                       | '1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                                                                          | <sup>0'</sup><br>le Disable bit<br>isabled<br>nabled<br>sable bit       | -                                           |                  |                                           |                                |

| R = Readable b<br>-n = Value at PC<br>bit 15-11 L<br>bit 10 C<br>bit 9 F<br>bit 8 F<br>bit 8 F<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                   | Jnimplement<br>CMPMD: Con<br>= Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                       | '1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                                                                          | <sup>0'</sup><br>le Disable bit<br>isabled<br>nabled<br>sable bit       | -                                           |                  |                                           | own                            |

| R = Readable b<br>-n = Value at PC<br>bit 15-11 L<br>bit 10 C<br>bit 9 F<br>bit 8 F<br>bit 8 F<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                   | Jnimplement<br>CMPMD: Con<br>= Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                       | '1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                                                                          | <sup>0'</sup><br>le Disable bit<br>isabled<br>nabled<br>sable bit       | -                                           |                  |                                           | own                            |

| bit 15-11 L<br>bit 10 C<br>bit 9 F<br>bit 8 F<br>bit 8 F<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                         | Jnimplement<br>CMPMD: Con<br>= Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                       | ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>CC Module Di<br>dule is disable                                                                                               | <sup>0'</sup><br>le Disable bit<br>isabled<br>nabled<br>sable bit       | -                                           |                  |                                           | own                            |

| bit 10 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CMPMD: Con<br>= Comparate<br>= Comparate<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                                    | nparator Modu<br>or module is di<br>or module is e<br>CC Module Di<br>dule is disable                                                                                                                 | le Disable bit<br>isabled<br>nabled<br>sable bit                        |                                             |                  |                                           |                                |

| bit 10 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CMPMD: Con<br>= Comparate<br>= Comparate<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                                    | nparator Modu<br>or module is di<br>or module is e<br>CC Module Di<br>dule is disable                                                                                                                 | le Disable bit<br>isabled<br>nabled<br>sable bit                        |                                             |                  |                                           |                                |

| bit 9 F<br>1<br>0<br>bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                           | = Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                                                    | or module is d<br>or module is e<br>CC Module Di<br>dule is disable                                                                                                                                   | isabled<br>nabled<br>sable bit                                          |                                             |                  |                                           |                                |

| bit 9 F<br>1<br>0<br>bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                           | = Comparat<br><b>RTCCMD:</b> RT<br>= RTCC mo<br>= RTCC mo                                                                           | or module is e<br>CC Module Di<br>dule is disable                                                                                                                                                     | nabled<br>sable bit                                                     |                                             |                  |                                           |                                |

| bit 9 F<br>1<br>0<br>bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                                                                                | CC Module Di<br>dule is disable                                                                                                                                                                       | sable bit                                                               |                                             |                  |                                           |                                |

| 1<br>0<br>bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | = RTCC mo<br>= RTCC mo                                                                                                              | dule is disable                                                                                                                                                                                       |                                                                         |                                             |                  |                                           |                                |

| 0<br>bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | = RTCC mo                                                                                                                           |                                                                                                                                                                                                       | d                                                                       |                                             |                  |                                           |                                |

| bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |                                                                                                                                                                                                       | h                                                                       |                                             |                  |                                           |                                |

| 1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                     | P Module Disal                                                                                                                                                                                        |                                                                         |                                             |                  |                                           |                                |

| bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | = PMP mod                                                                                                                           | ule is disabled                                                                                                                                                                                       |                                                                         |                                             |                  |                                           |                                |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | = PMP mod                                                                                                                           | ule is enabled                                                                                                                                                                                        |                                                                         |                                             |                  |                                           |                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CRCMD: CRC                                                                                                                          | C Module Disal                                                                                                                                                                                        | ble bit                                                                 |                                             |                  |                                           |                                |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                     | ule is disabled                                                                                                                                                                                       |                                                                         |                                             |                  |                                           |                                |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                     | ule is enabled                                                                                                                                                                                        |                                                                         |                                             |                  |                                           |                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                     | C1 Module Dis                                                                                                                                                                                         |                                                                         |                                             |                  |                                           |                                |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                     | dule is disable<br>dule is enableo                                                                                                                                                                    |                                                                         |                                             |                  |                                           |                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                     | 2 Module Disa                                                                                                                                                                                         |                                                                         |                                             |                  |                                           |                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                     | lule is disabled                                                                                                                                                                                      |                                                                         |                                             |                  |                                           |                                |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | = QEI2 mod                                                                                                                          | lule is enabled                                                                                                                                                                                       |                                                                         |                                             |                  |                                           |                                |

| bit 4 F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PWM2MD: PV                                                                                                                          | VM2 Module D                                                                                                                                                                                          | Disable bit                                                             |                                             |                  |                                           |                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                     | odule is disable<br>odule is enable                                                                                                                                                                   |                                                                         |                                             |                  |                                           |                                |

| bit 3-0 L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                     |                                                                                                                                                                                                       |                                                                         |                                             |                  |                                           |                                |

## 11.7 I/O Helpful Tips

- In some cases, certain pins as defined in TABLE 1. 31-9: "DC Characteristics: I/O Pin Input Specifications" under "Injection Current", have internal protection diodes to VDD and VSS. The term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- I/O pins that are shared with any analog input pin, 2. (i.e., ANx), are always analog pins by default after any reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the analog pin configuration registers in the ADC module, (i.e., ADxPCFGL, AD1PCFGH), by setting the appropriate bit that corresponds to that I/O port pin to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-toright. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each CN pin has a configurable internal weak pull-up resistor. The pull-ups act as a current source connected to the pin, and eliminates the need for external resistors in certain applications. The internal pull-up is to ~(VDD-0.8) not VDD. This is still above the minimum VIH of CMOS and TTL devices.

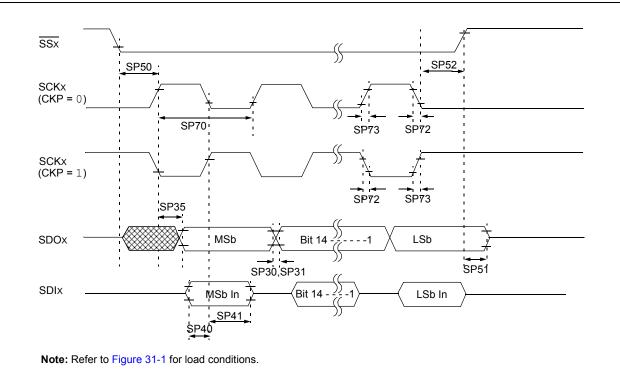

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 31.0 "Electrical Characteristics" for additional information.

# 11.8 I/O Resources

Many useful resources related to Resets are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the<br>product page using the link above, enter<br>this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/                                                                                |

|       | Devices.aspx?dDocName=en532315                                                                                       |

#### 11.8.1 KEY RESOURCES

- Section 10. "I/O Ports" (DS70193)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### 11.9 Peripheral Pin Select Registers

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 family of devices implement 33 registers for remappable peripheral configuration:

- 20 Input Remappable Peripheral Registers:

- RPINR0-RPINR1, RPINR3-RPINR4, RPINR7, RPINR10-RPINR21, PRINR23, and PRINR26

- 13 Output Remappable Peripheral Registers:

- RPOR0-RPOR12

| Note: | Inpu | t and output  | t reg | gister v | /alue | es can | only  |

|-------|------|---------------|-------|----------|-------|--------|-------|

|       | be   | changed       | if    | the      | IOI   | OCK    | bit   |

|       | (OS  | CCON<6>)      | is    | set      | to    | '0'.   | See   |

|       | Sec  | tion 11.6.3.1 | I     | "Cont    | rol   | Reg    | ister |

|       | Loc  | k" for a spec | cific | comm     | and   | seque  | ence. |

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | —   | —   |       |       | INT1R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

|        |     |     |       |       |            |       |       |

| U-0    | U-0 | U-0 | U-0   | U-0   | U-0        | U-0   | U-0   |

| —      | —   |     |       | —     | —          |       | —     |

| bit 7  |     |     |       |       |            |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

| bit 12-8 | <b>INT1R&lt;4:0&gt;:</b> Assign External Interrupt 1 (INTR1) to the corresponding RPn pin |

|----------|-------------------------------------------------------------------------------------------|

|          | 11111 = Input tied to Vss                                                                 |

|          | 11001 = Input tied to RP25                                                                |

|          | •                                                                                         |

|          | •                                                                                         |

|          | •                                                                                         |

|          | 00001 = Input tied to RP1                                                                 |

|          | 00000 = Input tied to RP0                                                                 |

| bit 7-0  | Unimplemented: Read as '0'                                                                |

### 17.1 QEI Resources

Many useful resources related to QEI are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532315              |

#### 17.1.1 KEY RESOURCES

- Section 15. "Quadature Encoder Interface (QEI)" (DS70208)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

NOTES:

## 21.6 ECAN Message Buffers

ECAN Message Buffers are part of DMA RAM memory. They are not ECAN special function registers. The user application must directly write into the DMA RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

## BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0    | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-------|-------|-------|-------|-------|

| —      | —   | _   | SID10 | SID9  | SID8  | SID7  | SID6  |

| bit 15 |     |     |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID5  | SID4  | SID3  | SID2  | SID1  | SID0  | SRR   | IDE   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                    |

|-----------|-----------------------------------------------|

| bit 12-2  | SID<10:0>: Standard Identifier bits           |

| bit 1     | SRR: Substitute Remote Request bit            |

|           | 1 = Message will request remote transmission  |

|           | 0 = Normal message                            |

| bit 0     | IDE: Extended Identifier bit                  |

|           | 1 = Message will transmit extended identifier |

|           | 0 = Message will transmit standard identifier |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0    | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-------|-------|-------|-------|

| —      | —   | _   | —   | EID17 | EID16 | EID15 | EID14 |

| bit 15 |     |     |     |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID13 | EID12 | EID11 | EID10 | EID9  | EID8  | EID7  | EID6  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

# REGISTER 27-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

| bit 2 | BEP: Byte Enable Polarity bit                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Byte enable active-high (PMBE)</li> <li>0 = Byte enable active-low (PMBE)</li> </ul>                                        |

| bit 1 | WRSP: Write Strobe Polarity bit                                                                                                          |

|       | For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):<br>1 = Write strobe active-high (PMWR)<br>0 = Write strobe active-low (PMWR) |

|       | For Master mode 1 (PMMODE<9:8> = 11):<br>1 = Enable strobe active-high (PMENB)<br>0 = Enable strobe active-low (PMENB)                   |

| bit 0 | RDSP: Read Strobe Polarity bit                                                                                                           |

|       | For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):<br>1 = Read strobe active-high (PMRD)<br>0 = Read strobe active-low (PMRD)   |

|       | For Master mode 1 (PMMODE<9:8> = 11):<br>1 = Read/write strobe active-high (PMRD/PMWR)<br>0 = Read/write strobe active-low (PMRD/PMWR)   |

- Note 1: 28-pin devices do not have PMA<10:2>.

- 2: These bits have no effect when their corresponding pins are used as address lines.

| Base<br>Instr<br># | Assembly<br>Mnemonic |       | Assembly Syntax | Description                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-------|-----------------|------------------------------------------|---------------|----------------|--------------------------|

| 1                  | ADD                  | ADD   | Acc             | Add Accumulators                         | 1             | 1              | OA,OB,SA,SB              |

|                    |                      | ADD   | f               | f = f + WREG                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | f,WREG          | WREG = f + WREG                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | #lit10,Wn       | Wd = lit10 + Wd                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,Ws,Wd        | Wd = Wb + Ws                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,#lit5,Wd     | Wd = Wb + lit5                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wso,#Slit4,Acc  | 16-bit Signed Add to Accumulator         | 1             | 1              | OA,OB,SA,SE              |

| 2                  | ADDC                 | ADDC  | f               | f = f + WREG + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | f,WREG          | WREG = $f + WREG + (C)$                  | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | #lit10,Wn       | Wd = lit10 + Wd + (C)                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,Ws,Wd        | Wd = Wb + Ws + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,#lit5,Wd     | Wd = Wb + lit5 + (C)                     | 1             | 1              | C,DC,N,OV,Z              |

| 3                  | AND                  | AND   | f               | f = f .AND. WREG                         | 1             | 1              | N,Z                      |

|                    |                      | AND   | f,WREG          | WREG = f .AND. WREG                      | 1             | 1              | N,Z                      |

|                    |                      | AND   | #lit10,Wn       | Wd = lit10 .AND. Wd                      | 1             | 1              | N,Z                      |

|                    |                      | AND   | Wb,Ws,Wd        | Wd = Wb .AND. Ws                         | 1             | 1              | N,Z                      |

|                    |                      | AND   | Wb,#lit5,Wd     | Wd = Wb .AND. lit5                       | 1             | 1              | N,Z                      |