Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc304t-i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended with a value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS51765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS51764)

- *"MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide"* (DS51616)

- *"Using MPLAB<sup>®</sup> REAL ICE™"* (poster) (DS51749)

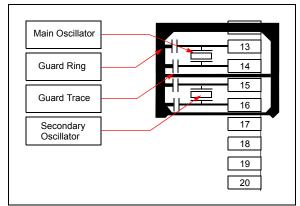

# 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A sugaested lavout is shown in Figure 2-3. Recommendations for crystals and ceramic resonators are provided in Table 2-1 and Table 2-2, respectively.

# FIGURE 2-3:

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| Part<br>Number       | Vendor   | Freq.  | Load<br>Cap. | Package<br>Case | Frequency<br>Tolerance | Mounting<br>Type | Operating<br>Temperature |

|----------------------|----------|--------|--------------|-----------------|------------------------|------------------|--------------------------|

| ECS-40-20-4DN        | ECS Inc. | 4 MHz  | 20 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-80-18-4DN        | ECS Inc. | 8 MHz  | 18 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-100-18-4-DN      | ECS Inc. | 10 MHz | 18 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-200-20-4DN       | ECS Inc. | 20 MHz | 20 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-40-20-5G3XDS-TR  | ECS Inc. | 4 MHz  | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |

| ECS-80-20-5G3XDS-TR  | ECS Inc. | 8 MHz  | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |

| ECS-100-20-5G3XDS-TR | ECS Inc. | 10 MHz | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |

| ECS-200-20-5G3XDS-TR | ECS Inc. | 20 MHz | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to 125°C           |

| NX3225SA 20MHZ AT-W  | NDK      | 20 MHz | 8 pF         | 3.2 mm x 2.5 mm | ±50 ppm                | SM               | -40°C to 125°C           |

# TABLE 2-1: CRYSTAL RECOMMENDATIONS

Legend: TH = Through Hole

SM = Surface Mount

# 3.5 CPU Resources

Many useful resources related to the CPU are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

# 3.5.1 KEY RESOURCES

- Section 2. "CPU" (DS70204)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| File Name                                                                                                                                                  | Addr                                                                                                     | r Bit 15                                                                               | Bit 14                                                                                                                   | Bit 13                                                                                              | Bit 12                                                                            | Bit 11                                                                            | Bit 10                                                                                                  | Bit 9                                                                                                 | Bit 8                                                                                                                                                  | Bit 7                                                                                                      | Bit 6                                                                                          | Bit 5                                                                                      | Bit 4                                                                                   | Bit 3                                                                                    | Bit 2                                                                         | Bit 1                                                                                 | Bit 0                                                                            | All<br>Reset                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------|

| C1CTRL1                                                                                                                                                    | 0400                                                                                                     | )                                                                                      | -                                                                                                                        | CSIDL                                                                                               | ABAT                                                                              | —                                                                                 |                                                                                                         | REQOP<2                                                                                               | :0>                                                                                                                                                    |                                                                                                            | OPMODE<2                                                                                       | 2:0>                                                                                       | —                                                                                       | CANCAF                                                                                   | ° —                                                                           | -                                                                                     | WIN                                                                              | 0480                                                        |

| C1CTRL2                                                                                                                                                    | 0402                                                                                                     | 2 —                                                                                    | _                                                                                                                        | _                                                                                                   | _                                                                                 | -                                                                                 | _                                                                                                       | _                                                                                                     | -                                                                                                                                                      | -                                                                                                          | _                                                                                              | _                                                                                          |                                                                                         | I                                                                                        | DNCNT<4:                                                                      | 0>                                                                                    |                                                                                  | 0000                                                        |

| C1VEC                                                                                                                                                      | 0404                                                                                                     |                                                                                        | _                                                                                                                        | _                                                                                                   |                                                                                   |                                                                                   | FILHIT<4:                                                                                               | 0>                                                                                                    |                                                                                                                                                        | —                                                                                                          |                                                                                                |                                                                                            |                                                                                         | ICODE<6:                                                                                 | 0>                                                                            |                                                                                       |                                                                                  | 0000                                                        |

| C1FCTRL                                                                                                                                                    | 0406                                                                                                     | 5                                                                                      | DMABS<2                                                                                                                  | :0>                                                                                                 |                                                                                   | -                                                                                 | _                                                                                                       | _                                                                                                     | -                                                                                                                                                      | -                                                                                                          | _                                                                                              | _                                                                                          |                                                                                         |                                                                                          | FSA<4:0>                                                                      | >                                                                                     |                                                                                  | 0000                                                        |

| C1FIFO                                                                                                                                                     | 0408                                                                                                     | 3 —                                                                                    | _                                                                                                                        |                                                                                                     |                                                                                   | FBF                                                                               | P<5:0>                                                                                                  |                                                                                                       |                                                                                                                                                        | —                                                                                                          | _                                                                                              |                                                                                            |                                                                                         | FNR                                                                                      | B<5:0>                                                                        |                                                                                       |                                                                                  | 0000                                                        |

| C1INTF                                                                                                                                                     | 040A                                                                                                     | · —                                                                                    | _                                                                                                                        | ТХВО                                                                                                | TXBP                                                                              | RXBP                                                                              | TXWA                                                                                                    | R RXWAR                                                                                               | R EWARN                                                                                                                                                | IVRIF                                                                                                      | WAKI                                                                                           | F ERRII                                                                                    |                                                                                         | FIFOIF                                                                                   | RBOVIE                                                                        | RBIF                                                                                  | TBIF                                                                             | 0000                                                        |

| C1INTE                                                                                                                                                     | 040C                                                                                                     | ; _                                                                                    | _                                                                                                                        | _                                                                                                   | _                                                                                 | _                                                                                 | _                                                                                                       | _                                                                                                     | _                                                                                                                                                      | IVRIE                                                                                                      | WAKI                                                                                           | E ERRIE                                                                                    | E —                                                                                     | FIFOIE                                                                                   | RBOVIE                                                                        | RBIE                                                                                  | TBIE                                                                             | 0000                                                        |

| C1EC                                                                                                                                                       | 040E                                                                                                     |                                                                                        |                                                                                                                          |                                                                                                     | TERRO                                                                             | CNT<7:0>                                                                          |                                                                                                         |                                                                                                       |                                                                                                                                                        |                                                                                                            |                                                                                                |                                                                                            | RERRC                                                                                   | NT<7:0>                                                                                  |                                                                               |                                                                                       |                                                                                  | 0000                                                        |

| C1CFG1                                                                                                                                                     | 0410                                                                                                     | ) _                                                                                    | -                                                                                                                        | _                                                                                                   | _                                                                                 | _                                                                                 | -                                                                                                       | _                                                                                                     | -                                                                                                                                                      | SJ                                                                                                         | W<1:0>                                                                                         |                                                                                            |                                                                                         | BRF                                                                                      | P<5:0>                                                                        |                                                                                       |                                                                                  | 0000                                                        |

| C1CFG2                                                                                                                                                     | 0412                                                                                                     | 2 —                                                                                    | WAKFIL                                                                                                                   | . —                                                                                                 | _                                                                                 | -                                                                                 |                                                                                                         | SEG2PH<2                                                                                              | 2:0>                                                                                                                                                   | SEG2PH                                                                                                     | ITS SAM                                                                                        | I                                                                                          | SEG1PH<                                                                                 | 2:0>                                                                                     |                                                                               | PRSEG<2:0                                                                             | )>                                                                               | 0000                                                        |

| C1FEN1                                                                                                                                                     | 0414                                                                                                     | FLTEN1                                                                                 | 5 FLTEN1                                                                                                                 | FLTEN1                                                                                              | 3 FLTEN12                                                                         | 2 FLTEN1                                                                          | 1 FLTEN1                                                                                                | 10 FLTENS                                                                                             | 9 FLTEN8                                                                                                                                               | FLTEN                                                                                                      | 7 FLTEN                                                                                        | 6 FLTEN                                                                                    | 5 FLTEN4                                                                                | FLTEN3                                                                                   | FLTEN2                                                                        | FLTEN1                                                                                | FLTEN0                                                                           | FFFF                                                        |

| C1FMSKSEL1                                                                                                                                                 | 0418                                                                                                     | F7N                                                                                    | ISK<1:0>                                                                                                                 | F6M                                                                                                 | ISK<1:0>                                                                          | F5M                                                                               | ISK<1:0>                                                                                                | F4M                                                                                                   | ISK<1:0>                                                                                                                                               | F3M                                                                                                        | ISK<1:0>                                                                                       | F2M                                                                                        | ISK<1:0>                                                                                | F1MS                                                                                     | SK<1:0>                                                                       | F0MS                                                                                  | K<1:0>                                                                           | 0000                                                        |

|                                                                                                                                                            |                                                                                                          |                                                                                        |                                                                                                                          |                                                                                                     |                                                                                   |                                                                                   |                                                                                                         |                                                                                                       |                                                                                                                                                        |                                                                                                            |                                                                                                |                                                                                            |                                                                                         |                                                                                          |                                                                               |                                                                                       |                                                                                  |                                                             |

| 0                                                                                                                                                          | — = unir                                                                                                 | mplemente                                                                              | ,                                                                                                                        | '. Reset va                                                                                         | INSK<1:0>                                                                         | wn in hexa                                                                        |                                                                                                         | F12N                                                                                                  | /ISK<1:0>                                                                                                                                              |                                                                                                            | //SK<1:0>                                                                                      |                                                                                            | //SK<1:0>                                                                               |                                                                                          | SK<1:0>                                                                       |                                                                                       | K<1:0>                                                                           |                                                             |

| Legend: -                                                                                                                                                  | — = unir                                                                                                 | mplemente                                                                              | d, read as '(                                                                                                            | '. Reset va                                                                                         |                                                                                   | wn in hexa                                                                        | decimal.                                                                                                | F12N                                                                                                  | /ISK<1:0>                                                                                                                                              |                                                                                                            |                                                                                                |                                                                                            |                                                                                         |                                                                                          |                                                                               |                                                                                       | K<1:0><br>Bit 0                                                                  | 0000<br>All                                                 |

| Legend: -<br>TABLE 4-2<br>File Name                                                                                                                        | — = unir<br>2 <b>2:</b>                                                                                  | mplemente                                                                              | d, read as 'd<br><b>REGIS</b>                                                                                            | . Reset va<br>Γ <b>ER MA</b>                                                                        | lues are sho                                                                      | N C1CTI                                                                           | decimal.                                                                                                | F12N<br>N = 0 (F<br>Bit 9                                                                             | ISK<1:0><br>OR dsP<br>Bit 8                                                                                                                            | PIC33FJ                                                                                                    | 128MC8<br>Bit 6                                                                                | 02/804                                                                                     | AND ds                                                                                  | PIC33FJ                                                                                  | J64MC8                                                                        | 02/804)                                                                               | ,                                                                                | 0000<br>All                                                 |

| Legend: -<br>TABLE 4-2<br>File Name                                                                                                                        | — = unir<br>22:<br>Addr<br>0400-<br>041E                                                                 | ECAN1<br>Bit 15                                                                        | d, read as '(<br>REGIS<br>Bit 14                                                                                         | <sup>7</sup> . Reset va                                                                             | lues are sho                                                                      | N C1CTI<br>Bit 11                                                                 | decimal.<br>RL1.WII<br>Bit 10                                                                           | F12N<br>N = 0 (F<br>Bit 9                                                                             | ISK<1:0><br>OR dsP<br>Bit 8                                                                                                                            | PIC33FJ                                                                                                    | 128MC8<br>Bit 6                                                                                | 02/804                                                                                     | AND ds                                                                                  | PIC33FJ                                                                                  | J64MC8                                                                        | 02/804)                                                                               | ,                                                                                | All                                                         |

| Legend: -<br>TABLE 4-2<br>File Name ( C1RXFUL1                                                                                                             | = unir<br>22:<br>Addr<br>0400-<br>041E<br>0420                                                           | ECAN1<br>Bit 15                                                                        | d, read as '(<br>REGIS<br>Bit 14                                                                                         | <sup>7</sup> . Reset va<br><b>FER MA</b><br><b>Bit 13</b><br>RXFUL13                                | Iues are sho<br>P WHEI<br>Bit 12<br>RXFUL12                                       | N C1CTI<br>Bit 11                                                                 | decimal.<br>RL1.WII<br>Bit 10                                                                           | F12N<br>N = 0 (F<br>Bit 9<br>See<br>RXFUL9                                                            | /ISK<1:0><br>FOR dsF<br>Bit 8<br>e definition                                                                                                          | PIC33FJ<br>Bit 7<br>when WIN<br>RXFUL7                                                                     | 128MC8<br>Bit 6<br>= x                                                                         | 02/804 /<br>Bit 5                                                                          | AND ds<br>Bit 4                                                                         | PIC33FJ<br>Bit 3                                                                         | Bit 2<br>RXFUL2                                                               | 02/804)<br>Bit 1                                                                      | Bit 0                                                                            | All<br>Reset                                                |

| Legend: -<br>TABLE 4-2<br>File Name<br>C1RXFUL1<br>C1RXFUL2                                                                                                | — = unir<br>22:<br>Addr<br>0400-<br>041E<br>0420<br>0422                                                 | Bit 15<br>RXFUL15<br>RXFUL31                                                           | d, read as '(<br><b>REGIS</b><br><b>Bit 14</b><br>RXFUL14<br>RXFUL30                                                     | <sup>1</sup> . Reset va<br><b>FER MA</b><br><b>Bit 13</b><br>RXFUL13<br>RXFUL29                     | RXFUL12<br>RXFUL28                                                                | N C1CTI<br>Bit 11<br>RXFUL11<br>RXFUL27                                           | decimal.<br>RL1.WII<br>Bit 10<br>RXFUL10                                                                | F12N<br>N = 0 (F<br>Bit 9<br>See<br>RXFUL9                                                            | ISK<1:0><br>FOR dsF<br>Bit 8<br>e definition<br>RXFUL8                                                                                                 | PIC33FJ<br>Bit 7<br>when WIN<br>RXFUL7                                                                     | 128MC8<br>Bit 6<br>= x<br>RXFUL6                                                               | 02/804 /<br>Bit 5<br>RXFUL5                                                                | AND ds<br>Bit 4<br>RXFUL4                                                               | PIC33FJ<br>Bit 3<br>RXFUL3                                                               | Bit 2<br>RXFUL2                                                               | 02/804)<br>Bit 1<br>RXFUL1                                                            | Bit 0                                                                            | All<br>Reset                                                |

| Legend: -<br>TABLE 4-2<br>File Name (<br>C1RXFUL1<br>C1RXFUL2<br>C1RXOVF1                                                                                  | - = unir<br>22:<br>Addr<br>0400-<br>041E<br>0420<br>0422<br>0428                                         | RXFUL15<br>RXFUL31<br>RXOVF15                                                          | d, read as '(<br><b>REGIS</b><br><b>Bit 14</b><br>RXFUL14<br>RXFUL30<br>RXOVF14                                          | '. Reset va           FER MA           Bit 13           RXFUL13           RXFUL29           RXOVF13 | RXFUL12<br>RXFUL28<br>RXOVF12                                                     | N C1CTI<br>Bit 11<br>RXFUL11<br>RXFUL27<br>RXOVF11                                | decimal.<br>RL1.WII<br>Bit 10<br>RXFUL10<br>RXFUL26<br>RXOVF10                                          | F12N<br>N = 0 (F<br>Bit 9<br>See<br>RXFUL9<br>RXFUL25<br>RXOVF9                                       | ASK<1:0><br>FOR dsF<br>Bit 8<br>e definition<br>RXFUL8<br>RXFUL24<br>RXOVF8                                                                            | Bit 7<br>Bit 7<br>When WIN<br>RXFUL7<br>RXFUL23<br>RXOVF7                                                  | 128MC8<br>Bit 6<br>= x<br>RXFUL6<br>RXFUL22<br>RXOVF6                                          | 02/804 /<br>Bit 5<br>RXFUL5<br>RXFUL21                                                     | AND ds<br>Bit 4<br>RXFUL4<br>RXFUL20                                                    | PIC33FJ<br>Bit 3<br>RXFUL3<br>RXFUL19<br>RXOVF3                                          | Bit 2<br>RXFUL2<br>RXFUL18<br>RXOVF2                                          | 02/804)<br>Bit 1<br>RXFUL1<br>RXFUL17                                                 | Bit 0<br>RXFUL0<br>RXFUL16<br>RXOVF0                                             | All<br>Reset                                                |

| Legend: -<br>TABLE 4-2<br>File Name (<br>C1RXFUL1<br>C1RXFUL2<br>C1RXOVF1<br>C1RXOVF2 (                                                                    | - = unir<br>22:<br>Addr<br>0400-<br>041E<br>0420<br>0422<br>0428                                         | RXFUL15<br>RXFUL31<br>RXOVF15                                                          | d, read as '(<br><b>REGIS</b><br><b>Bit 14</b><br>RXFUL14<br>RXFUL30<br>RXOVF14                                          | '. Reset va           FER MA           Bit 13           RXFUL13           RXFUL29           RXOVF13 | RXFUL12<br>RXFUL28<br>RXOVF12                                                     | N C1CTI<br>Bit 11<br>RXFUL11<br>RXFUL27<br>RXOVF11                                | decimal.<br>RL1.WII<br>Bit 10<br>RXFUL10<br>RXFUL26<br>RXOVF10                                          | F12N<br>N = 0 (F<br>Bit 9<br>See<br>RXFUL9<br>RXFUL25<br>RXOVF9<br>RXOVF25                            | ASK<1:0><br>FOR dsF<br>Bit 8<br>e definition<br>RXFUL8<br>RXFUL24<br>RXOVF8                                                                            | Bit 7<br>Bit 7<br>When WIN<br>RXFUL7<br>RXFUL23<br>RXOVF7                                                  | 128MC8<br>Bit 6<br>= x<br>RXFUL6<br>RXFUL22<br>RXOVF6                                          | 02/804 /<br>Bit 5<br>RXFUL5<br>RXFUL21<br>RXOVF5                                           | AND ds<br>Bit 4<br>RXFUL4<br>RXFUL20<br>RXOVF4                                          | PIC33FJ<br>Bit 3<br>RXFUL3<br>RXFUL19<br>RXOVF3                                          | Bit 2<br>RXFUL2<br>RXFUL18<br>RXOVF2                                          | 02/804)<br>Bit 1<br>RXFUL1<br>RXFUL17<br>RXOVF1<br>RXOVF17                            | Bit 0<br>RXFUL0<br>RXFUL16<br>RXOVF0                                             | All<br>Reset                                                |

| Legend: -<br>TABLE 4-2<br>File Name (<br>C1RXFUL1<br>C1RXFUL2<br>C1RXOVF1<br>C1RXOVF2<br>C1RXOVF2<br>C1TR01CON                                             | - = unir<br>22:<br>Addr<br>0400-<br>041E<br>0420<br>0422<br>0428<br>0428                                 | ECAN1<br>Bit 15<br>RXFUL15<br>RXFUL31<br>RXOVF15<br>RXOVF31                            | d, read as '(<br><b>REGIS</b><br><b>Bit 14</b><br>RXFUL14<br>RXFUL30<br>RXOVF14<br>RXOVF30                               | RXFUL13<br>RXFUL29<br>RXOVF13<br>RXOVF29                                                            | RXFUL12<br>RXFUL28<br>RXOVF12<br>RXOVF28                                          | N C1CT<br>Bit 11<br>RXFUL11<br>RXFUL27<br>RXOVF11<br>RXOVF27                      | decimal.<br>RL1.WII<br>Bit 10<br>RXFUL10<br>RXFUL26<br>RXOVF10<br>RXOVF26                               | F12N<br>N = 0 (F<br>Bit 9<br>RXFUL9<br>RXFUL25<br>RXOVF9<br>RXOVF25<br>TX1PF                          | ASK<1:0><br>FOR dsF<br>Bit 8<br>e definition<br>RXFUL8<br>RXFUL24<br>RXOVF8<br>RXOVF24                                                                 | PIC33FJ<br>Bit 7<br>when WIN<br>RXFUL7<br>RXFUL23<br>RXOVF7<br>RXOVF23                                     | 128MC8<br>Bit 6<br>= x<br>RXFUL6<br>RXFUL22<br>RXOVF6<br>RXOVF22                               | 02/804<br>Bit 5<br>RXFUL5<br>RXFUL21<br>RXOVF5<br>RXOVF21                                  | AND ds<br>Bit 4<br>RXFUL4<br>RXFUL20<br>RXOVF4<br>RXOVF20                               | RXFUL3<br>RXFUL3<br>RXFUL19<br>RXOVF3<br>RXOVF19                                         | RXFUL2<br>RXFUL18<br>RXOVF2<br>RXOVF18                                        | 02/804)<br>Bit 1<br>RXFUL1<br>RXFUL17<br>RXOVF1<br>RXOVF17<br>TX0PF                   | Bit 0<br>RXFUL0<br>RXFUL16<br>RXOVF0<br>RXOVF16                                  | All<br>Reset                                                |

| Legend: - TABLE 4-2 File Name C1RXFUL1 C1RXFUL2 C1RXOVF1 C1RXOVF2 C1RXOVF2 C1TR01CON C1TR23CON                                                             | - = unir<br>22:<br>Addr<br>0400-<br>041E<br>0420<br>0422<br>0428<br>0428<br>042A<br>0430                 | ECAN1<br>Bit 15<br>RXFUL15<br>RXFUL31<br>RXOVF15<br>RXOVF31<br>TXEN1                   | d, read as <sup>1</sup><br>REGIS<br>Bit 14<br>RXFUL14<br>RXFUL30<br>RXOVF14<br>RXOVF30<br>TXABT1                         | RXFUL13<br>RXFUL13<br>RXFUL29<br>RXOVF13<br>RXOVF29<br>TXLARB1                                      | RXFUL12<br>RXFUL12<br>RXFUL28<br>RXOVF12<br>RXOVF28<br>TXERR1                     | N C1CTI<br>Bit 11<br>RXFUL11<br>RXFUL27<br>RXOVF11<br>RXOVF27<br>TXREQ1           | decimal.<br>RL1.WII<br>Bit 10<br>RXFUL10<br>RXFUL26<br>RXOVF10<br>RXOVF26<br>RTREN1                     | F12N<br>N = 0 (F<br>Bit 9<br>RXFUL9<br>RXFUL25<br>RXOVF25<br>TX1PF<br>TX3PF                           | ASK<1:0><br>FOR dsF<br>Bit 8<br>e definition<br>RXFUL8<br>RXFUL24<br>RXOVF8<br>RXOVF24<br>RXOVF24<br>RXOVF24                                           | PIC33FJ<br>Bit 7<br>when WIN<br>RXFUL7<br>RXFUL23<br>RXOVF7<br>RXOVF23<br>TXEN0                            | 128MC8<br>Bit 6<br>= x<br>RXFUL6<br>RXFUL22<br>RXOVF6<br>RXOVF22<br>TXABT0                     | 02/804<br>Bit 5<br>RXFUL5<br>RXFUL21<br>RXOVF5<br>RXOVF21<br>TXLARB0                       | AND ds<br>Bit 4<br>RXFUL4<br>RXFUL20<br>RXOVF4<br>RXOVF20<br>TXERR0                     | PIC33FJ<br>Bit 3<br>RXFUL3<br>RXFUL19<br>RXOVF3<br>RXOVF19<br>TXREQ0                     | RXFUL2<br>RXFUL2<br>RXFUL18<br>RXOVF2<br>RXOVF18<br>RTREN0                    | 02/804)<br>Bit 1<br>RXFUL1<br>RXFUL17<br>RXOVF1<br>RXOVF17<br>TX0PF<br>TX2PF          | Bit 0<br>RXFUL0<br>RXFUL16<br>RXOVF0<br>RXOVF16<br>RXOVF16                       | All<br>Reset                                                |

| Legend: -<br>TABLE 4-2<br>File Name<br>C1RXFUL1<br>C1RXFUL2<br>C1RXOVF1<br>C1RXOVF2<br>C1TR01CON<br>C1TR23CON<br>C1TR45CON                                 | - = unir<br>22:<br>Addr<br>0400-<br>041E<br>0420<br>0422<br>0428<br>0428<br>0428<br>0423<br>0423         | Bit 15<br>Bit 15<br>RXFUL15<br>RXFUL31<br>RXOVF15<br>RXOVF31<br>TXEN1<br>TXEN3         | d, read as <sup>1</sup><br>REGIS<br>Bit 14<br>RXFUL14<br>RXFUL30<br>RXOVF14<br>RXOVF30<br>TXABT1<br>TXABT3               | RXFUL13<br>RXFUL13<br>RXFUL29<br>RXOVF13<br>RXOVF29<br>TXLARB1<br>TXLARB3                           | RXFUL12<br>RXFUL12<br>RXFUL28<br>RXOVF12<br>RXOVF28<br>TXERR1<br>TXERR3           | N C1CT<br>Bit 11<br>RXFUL11<br>RXFUL27<br>RXOVF11<br>RXOVF27<br>TXREQ1<br>TXREQ3  | decimal.<br>RL1.WII<br>Bit 10<br>RXFUL10<br>RXFUL26<br>RXOVF10<br>RXOVF26<br>RTREN1<br>RTREN3           | F12N<br>N = 0 (F<br>Bit 9<br>See<br>RXFUL9<br>RXFUL25<br>RXOVF9<br>RXOVF25<br>TX1PF<br>TX3PF<br>TX5PF | ASK<1:0><br>FOR dsF<br>Bit 8<br>e definition<br>RXFUL8<br>RXFUL24<br>RXOVF8<br>RXOVF24<br>RXOVF24<br>RXOVF24<br>RXOVF24<br>RXOVF24                     | PIC33FJ<br>Bit 7<br>when WIN<br>RXFUL7<br>RXFUL23<br>RXOVF7<br>RXOVF23<br>TXEN0<br>TXEN2                   | 128MC8<br>Bit 6<br>= x<br>RXFUL6<br>RXFUL22<br>RXOVF6<br>RXOVF22<br>TXABT0<br>TXABT2           | 02/804<br>Bit 5<br>RXFUL5<br>RXFUL21<br>RXOVF5<br>RXOVF21<br>TXLARB0<br>TXLARB2            | AND ds<br>Bit 4<br>RXFUL4<br>RXFUL20<br>RXOVF4<br>RXOVF20<br>TXERR0<br>TXERR2           | PIC33FJ<br>Bit 3<br>RXFUL3<br>RXFUL19<br>RXOVF3<br>RXOVF19<br>TXREQ0<br>TXREQ2           | RXFUL2<br>RXFUL2<br>RXFUL18<br>RXOVF18<br>RTREN0<br>RTREN2                    | 02/804)<br>Bit 1<br>RXFUL1<br>RXFUL17<br>RXOVF1<br>RXOVF17<br>TX0PF<br>TX2PF<br>TX4PF | Bit 0<br>RXFUL0<br>RXFUL16<br>RXOVF16<br>RXOVF16<br>RXOVF16<br>RX1:0>            | All<br>Reset                                                |

| Legend: -<br>TABLE 4-2<br>File Name (1)<br>C1RXFUL1 (2)<br>C1RXFUL2 (2)<br>C1RXOVF1 (2)<br>C1RXOVF2 (2)<br>C1TR01CON (2)<br>C1TR45CON (2)<br>C1TR67CON (2) | - = unir<br>22:<br>Addr<br>0400-<br>041E<br>0420<br>0422<br>0428<br>0428<br>0428<br>0430<br>0432<br>0434 | ECAN1<br>Bit 15<br>RXFUL15<br>RXFUL31<br>RXOVF15<br>RXOVF31<br>TXEN1<br>TXEN3<br>TXEN5 | d, read as '(<br><b>REGIS</b><br><b>Bit 14</b><br>RXFUL14<br>RXFUL30<br>RXOVF14<br>RXOVF30<br>TXABT1<br>TXABT3<br>TXABT5 | CER MA<br>Bit 13<br>RXFUL13<br>RXFUL29<br>RXOVF13<br>RXOVF29<br>TXLARB1<br>TXLARB3<br>TXLARB5       | RXFUL12<br>RXFUL12<br>RXFUL28<br>RXOVF12<br>RXOVF28<br>TXERR1<br>TXERR3<br>TXERR5 | RXFUL11<br>RXFUL11<br>RXFUL27<br>RXOVF11<br>RXOVF27<br>TXREQ1<br>TXREQ3<br>TXREQ5 | decimal.<br>RL1.WII<br>Bit 10<br>RXFUL10<br>RXFUL26<br>RXOVF10<br>RXOVF26<br>RTREN1<br>RTREN3<br>RTREN5 | F12N<br>N = 0 (F<br>Bit 9<br>See<br>RXFUL9<br>RXFUL25<br>RXOVF9<br>RXOVF25<br>TX1PF<br>TX3PF<br>TX5PF | ASK<1:0><br><b>FOR dsF</b><br><b>Bit 8</b><br><b>e definition</b><br>RXFUL8<br>RXFUL24<br>RXOVF8<br>RXOVF8<br>RXOVF24<br>RXOVF24<br>RI<1:0><br>RI<1:0> | PIC33FJ<br>Bit 7<br>when WIN<br>RXFUL7<br>RXFUL23<br>RXOVF7<br>RXOVF23<br>TXEN0<br>TXEN2<br>TXEN4<br>TXEN4 | 128MC8<br>Bit 6<br>= x<br>RXFUL6<br>RXFUL22<br>RXOVF6<br>RXOVF22<br>TXABT0<br>TXABT2<br>TXABT4 | 02/804<br>Bit 5<br>RXFUL5<br>RXFUL21<br>RXOVF5<br>RXOVF21<br>TXLARB0<br>TXLARB2<br>TXLARB4 | AND ds<br>Bit 4<br>RXFUL4<br>RXFUL20<br>RXOVF4<br>RXOVF20<br>TXERR0<br>TXERR2<br>TXERR4 | PIC33FJ<br>Bit 3<br>RXFUL3<br>RXFUL19<br>RXOVF3<br>RXOVF19<br>TXREQ0<br>TXREQ2<br>TXREQ4 | Bit 2<br>RXFUL2<br>RXFUL18<br>RXOVF2<br>RXOVF18<br>RTREN0<br>RTREN2<br>RTREN4 | 02/804)<br>Bit 1<br>RXFUL1<br>RXFUL17<br>RXOVF1<br>RXOVF17<br>TX0PF<br>TX2PF<br>TX4PF | Bit 0<br>RXFUL0<br>RXFUL16<br>RXOVF0<br>RXOVF16<br>RXOVF16<br>RI<1:0><br>RI<1:0> | All<br>Rese<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000 |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

| TABLE 4            | -37: | SECUF  |             | GISTER | MAP F       | OR dsF     | IC33FJ | 128MC | 204/804 | AND d | sPIC33F | J64MC2 | 04/804 | ONLY  |        |         |        |               |

|--------------------|------|--------|-------------|--------|-------------|------------|--------|-------|---------|-------|---------|--------|--------|-------|--------|---------|--------|---------------|

| File Name          | Addr | Bit 15 | Bit 14      | Bit 13 | Bit 12      | Bit 11     | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6   | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1   | Bit 0  | All<br>Resets |

| BSRAM              | 0750 | _      | —           | —      | _           | —          | _      | _     | _       | _     | _       | —      | —      |       | IW_BSR | IR_BSR  | RL_BSR | 0000          |

| SSRAM              | 0752 | _      | _           | _      | —           | _          | _      | _     | _       | _     | _       | _      | _      |       | IW_SSR | IR_SSR  | RL_SSR | 0000          |

| Legend:<br>TABLE 4 |      |        | on Reset, - | ·      | emented, re | ad as '0'. |        |       |         |       |         |        |        | -     |        |         |        |               |

| File Name          | Addr | Bit 15 | Bit 14      | Bit 13 | Bit 12      | Bit 11     | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6   | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1   | Bit 0  | All<br>Resets |

| NVMCON             | 0760 | WR     | WREN        | WRERR  | —           | —          | -      | —     | -       | —     | ERASE   | _      | —      |       | NVM    | OP<3:0> |        | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'.

# TABLE 4-39: PMD REGISTER MAP

0766

NVMKEY

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|--------|--------|--------|--------|-------|-------|-------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWM1MD | —     | I2C1MD | U2MD   | U1MD   | SPI2MD | SPI1MD | _     | C1MD  | AD1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | _      | _      | _      | _      | IC2MD  | IC1MD | _      | _      | _      | _      | OC4MD  | OC3MD | OC2MD | OC1MD | 0000          |

| PMD3      | 0774 | _      | _      | _      | _      | _      | CMPMD  | RTCCMD | PMPMD | CRCMD  | DAC1MD | QEI2MD | PWM2MD | _      |       | _     | _     | 0000          |

\_

NVMKEY<7:0>

Legend: x = unknown value on Reset, — = unimplemented, read as '0'.

0000

| U-0          | U-0                                    | U-0                                                                            | U-0                                     | U-0              | R/W-1            | R/W-0       | R/W-0 |  |

|--------------|----------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------|------------------|------------------|-------------|-------|--|

| _            | —                                      | —                                                                              | _                                       | —                |                  | DMA4IP<2:0> |       |  |

| bit 15       |                                        |                                                                                |                                         |                  |                  |             | bit   |  |

| U-0          | R/W-1                                  | R/W-0                                                                          | R/W-0                                   | U-0              | U-0              | U-0         | U-0   |  |

| 0-0          | R/W-1                                  | PMPIP<2:0>                                                                     | K/W-U                                   | 0-0              | 0-0              | 0-0         | 0-0   |  |

| <br>bit 7    |                                        | FINIFIF \2.0>                                                                  |                                         | _                | _                |             | bit   |  |

|              |                                        |                                                                                |                                         |                  |                  |             | DIL   |  |

| Legend:      |                                        |                                                                                |                                         |                  |                  |             |       |  |

| R = Readab   | le bit                                 | W = Writable                                                                   | bit                                     | U = Unimpler     | mented bit, read | d as '0'    |       |  |

| -n = Value a | t POR                                  | '1' = Bit is set                                                               | t i i i i i i i i i i i i i i i i i i i | '0' = Bit is cle |                  |             |       |  |

| bit 10-8     | 111 = Interr<br>•<br>•<br>001 = Interr | 0>: DMA Chanr<br>upt is priority 7 (<br>upt is priority 1<br>upt source is dis | highest priorit                         | •                | interrupt Priori | ty dits     |       |  |

| bit 7        | Unimpleme                              | nted: Read as                                                                  | 0'                                      |                  |                  |             |       |  |

| bit 6-4      | 111 = Interr<br>•<br>•                 | Parallel Master<br>upt is priority 7 (<br>upt is priority 1                    |                                         |                  |                  |             |       |  |

# REGISTER 7-25: IPC11: INTERRUPT PRIORITY CONTROL REGISTER 11

bit 3-0 Unimplemented: Read as '0'

| U-0                |                                                                                   | <b>B</b> / · · · ·                                                                                                                    | <b>B</b> 4                                          |                  | <b>-</b> <i>a</i> · · · · |                 |       |

|--------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------|---------------------------|-----------------|-------|

|                    | R/W-1                                                                             | R/W-0                                                                                                                                 | R/W-0                                               | U-0              | R/W-1                     | R/W-0           | R/W-0 |

|                    |                                                                                   | CRCIP<2:0>                                                                                                                            |                                                     |                  |                           | U2EIP<2:0>      |       |

| bit 15             |                                                                                   |                                                                                                                                       |                                                     |                  |                           |                 | bi    |

| U-0                | R/W-1                                                                             | R/W-0                                                                                                                                 | R/W-0                                               | U-0              | U-0                       | U-0             | U-0   |

| —                  |                                                                                   | U1EIP<2:0>                                                                                                                            |                                                     |                  | —                         | —               | —     |

| bit 7              |                                                                                   |                                                                                                                                       |                                                     |                  |                           |                 | bi    |

| Legend:            |                                                                                   |                                                                                                                                       |                                                     |                  |                           |                 |       |

| R = Readabl        | e bit                                                                             | W = Writable t                                                                                                                        | bit                                                 | U = Unimpler     | mented bit, rea           | d as '0'        |       |

| -n = Value at      | t POR                                                                             | '1' = Bit is set                                                                                                                      |                                                     | '0' = Bit is cle | ared                      | x = Bit is unkn | own   |

| bit 11<br>bit 10-8 | •<br>•<br>001 = Interr<br>000 = Interr<br>Unimpleme<br>U2EIP<2:0>                 | rupt is priority 7 (h<br>rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>>: UART2 Error Ir<br>rupt is priority 7 (h | abled<br>, <sup>,</sup>                             | ity bits         |                           |                 |       |

|                    | •                                                                                 |                                                                                                                                       |                                                     | ,                |                           |                 |       |

| hit 7              | 000 <b>= Interr</b>                                                               | upt is priority 1<br>upt source is disa                                                                                               |                                                     |                  |                           |                 |       |

| bit 7<br>bit 6-4   | 000 = Interr<br>Unimpleme<br>U1EIP<2:0><br>111 = Interr<br>•<br>•<br>001 = Interr |                                                                                                                                       | , <sup>,</sup><br>nterrupt Prior<br>nighest priorit | •                |                           |                 |       |

#### ....

# 7.6 Interrupt Setup Procedures

#### 7.6.1 INITIALIZATION

To configure an interrupt source at initialization:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level depends on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources can be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized such that all user interrupt sources are assigned to priority level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

# 7.6.2 INTERRUPT SERVICE ROUTINE

The method used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (C or assembler) and the language development tool suite used to develop the application.

In general, the user application must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the program re-enters the ISR immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

# 7.6.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.6.4 INTERRUPT DISABLE

All user interrupts can be disabled using this procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the  ${\tt POP}$  instruction can be used to restore the previous SR value.

| Note: | Only user interrupts with a priority level of |

|-------|-----------------------------------------------|

|       | 7 or lower can be disabled. Trap sources      |

|       | (level 8-level 15) cannot be disabled.        |

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

NOTES:

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| REGISTER          | 11-4: RPINF                                | R4: PERIPHEI                                                             | RAL PIN SE    | ELECT INPU                         | T REGISTER     | 4               |       |  |  |

|-------------------|--------------------------------------------|--------------------------------------------------------------------------|---------------|------------------------------------|----------------|-----------------|-------|--|--|

| U-0               | U-0                                        | U-0                                                                      | R/W-1         | R/W-1                              | R/W-1          | R/W-1           | R/W-1 |  |  |

| —                 | —                                          | _                                                                        |               |                                    | T5CKR<4:0      | >               |       |  |  |

| bit 15            |                                            | ·                                                                        |               |                                    |                |                 | bit   |  |  |

| U-0               | U-0                                        | U-0                                                                      | R/W-1         | R/W-1                              | R/W-1          | R/W-1           | R/W-1 |  |  |

| _                 | _                                          | _                                                                        |               |                                    | T4CKR<4:0      | >               |       |  |  |

| bit 7             |                                            |                                                                          |               |                                    |                |                 | bit ( |  |  |

| Legend:           |                                            |                                                                          |               |                                    |                |                 |       |  |  |

| R = Readabl       | le bit                                     | W = Writable                                                             | oit           | U = Unimplemented bit, read as '0' |                |                 |       |  |  |

| -n = Value at POR |                                            | '1' = Bit is set                                                         |               | '0' = Bit is cle                   | eared          | x = Bit is unki | nown  |  |  |

|                   | 11001 = Inpo<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to Vss<br>ut tied to RP25<br>ut tied to RP1<br>ut tied to RP0    |               |                                    |                |                 |       |  |  |

| bit 7-5           | Unimplemer                                 | nted: Read as '                                                          | )'            |                                    |                |                 |       |  |  |

| bit 4-0           | 11111 = Inpu<br>11001 = Inpu<br>•          | <ul> <li>Assign Timera<br/>ut tied to Vss<br/>ut tied to RP25</li> </ul> | t External Cl | ock (T4CK) to t                    | the correspond | ling RPn pin    |       |  |  |

|                   |                                            | ut tied to RP1                                                           |               |                                    |                |                 |       |  |  |

00000 = Input tied to RP0

| U-0                           | U-0                                                      | U-0                                                                          | R/W-1         | R/W-1             | R/W-1      | R/W-1           | R/W-1 |

|-------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------|---------------|-------------------|------------|-----------------|-------|

| —                             | _                                                        | _                                                                            |               |                   | QEB1R<4:0> |                 |       |