Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                            |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc304t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: | PINOU       | T I/O DES       | CRIPT       | IONS (CONTINUED)                                                             |

|------------|-------------|-----------------|-------------|------------------------------------------------------------------------------|

| Pin Name   | Pin<br>Type | Buffer<br>Type  | PPS         | Description                                                                  |

| FLTA1      | I           | ST              | Yes         | PWM1 Fault A input.                                                          |

| PWM1L1     | 0           |                 | No          | PWM1 Low output 1                                                            |

| PWM1H1     | 0           | —               | No          | PWM1 High output 1                                                           |

| PWM1L2     | 0           | —               | No          | PWM1 Low output 2                                                            |

| PWM1H2     | 0           |                 | No          | PWM1 High output 2                                                           |

| PWM1L3     | 0           |                 | No          | PWM1 Low output 3                                                            |

| PWM1H3     | 0           |                 | No          | PWM1 High output 3                                                           |

| FLTA2      | I           | ST              | Yes         | PWM2 Fault A input.                                                          |

| PWM2L1     | 0           |                 | No          | PWM2 Low output 1                                                            |

| PWM2H1     | 0           |                 | No          | PWM2 High output 1                                                           |

| PGED1      | I/O         | ST              | No          | Data I/O pin for programming/debugging communication channel 1.              |

| PGEC1      | I           | ST              | No          | Clock input pin for programming/debugging communication channel 1.           |

| PGED2      | I/O         | ST              | No          | Data I/O pin for programming/debugging communication channel 2.              |

| PGEC2      | I           | ST              | No          | Clock input pin for programming/debugging communication channel 2.           |

| PGED3      | I/O         | ST              | No          | Data I/O pin for programming/debugging communication channel 3.              |

| PGEC3      | I           | ST              | No          | Clock input pin for programming/debugging communication channel 3.           |

| MCLR       | I/P         | ST              | No          | Master Clear (Reset) input. This pin is an active-low Reset to the device.   |

| AVDD       | Р           | Р               | No          | Positive supply for analog modules. This pin must be connected at all times. |

| AVss       | Р           | Р               | No          | Ground reference for analog modules.                                         |

| Vdd        | Р           | —               | No          | Positive supply for peripheral logic and I/O pins.                           |

| VCAP       | Р           | _               | No          | CPU logic filter capacitor connection.                                       |

| Vss        | Р           | —               | No          | Ground reference for logic and I/O pins.                                     |

| VREF+      | I           | Analog          | No          | Analog voltage reference (high) input.                                       |

| VREF-      | I           | Analog          | No          | Analog voltage reference (low) input.                                        |

|            | c = c M c   | C as man a tile | La liana de | or output Applog = Applog input P = Power                                    |

| TABLE 1-1: | <b>PINOUT I/O DESCRIPTIONS</b> | (CONTINUED) |

|------------|--------------------------------|-------------|

|            |                                |             |

**Legend:** CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select

Analog = Analog input P = Power O = Output TTL = TTL input buffer

I = Input

#### **Special Function Register Maps** 4.4

#### TABLE 4-1: **CPU CORE REGISTERS MAP**

| DS7029  |  |

|---------|--|

| )1G-pag |  |

| je 42   |  |

| SFR Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7        | Bit 6 | Bit 5     | Bit 4           | Bit 3        | Bit 2        | Bit 1   | Bit 0 | All<br>Resets |

|----------|------|--------|--------|--------|--------|--------|--------|---------|---------------|--------------|-------|-----------|-----------------|--------------|--------------|---------|-------|---------------|

| WREG0    | 0000 |        |        |        |        |        |        |         | Working Re    | gister 0     |       |           |                 |              |              |         |       | 0000          |

| WREG1    | 0002 |        |        |        |        |        |        |         | Working Re    | gister 1     |       |           |                 |              |              |         |       | 0000          |

| WREG2    | 0004 |        |        |        |        |        |        |         | Working Re    | gister 2     |       |           |                 |              |              |         |       | 0000          |

| WREG3    | 0006 |        |        |        |        |        |        |         | Working Re    | gister 3     |       |           |                 |              |              |         |       | 0000          |

| WREG4    | 0008 |        |        |        |        |        |        |         | Working Re    | gister 4     |       |           |                 |              |              |         |       | 0000          |

| WREG5    | 000A |        |        |        |        |        |        |         | Working Re    | gister 5     |       |           |                 |              |              |         |       | 0000          |

| WREG6    | 000C |        |        |        |        |        |        |         | Working Re    | gister 6     |       |           |                 |              |              |         |       | 0000          |

| WREG7    | 000E |        |        |        |        |        |        |         | Working Re    | gister 7     |       |           |                 |              |              |         |       | 0000          |

| WREG8    | 0010 |        |        |        |        |        |        |         | Working Re    | gister 8     |       |           |                 |              |              |         |       | 0000          |

| WREG9    | 0012 |        |        |        |        |        |        |         | Working Re    | gister 9     |       |           |                 |              |              |         |       | 0000          |

| WREG10   | 0014 |        |        |        |        |        |        |         | Working Reg   | jister 10    |       |           |                 |              |              |         |       | 0000          |

| WREG11   | 0016 |        |        |        |        |        |        |         | Working Reg   | jister 11    |       |           |                 |              |              |         |       | 0000          |

| WREG12   | 0018 |        |        |        |        |        |        |         | Working Reg   | ister 12     |       |           |                 |              |              |         |       | 0000          |

| WREG13   | 001A |        |        |        |        |        |        |         | Working Reg   | jister 13    |       |           |                 |              |              |         |       | 0000          |

| WREG14   | 001C |        |        |        |        |        |        |         | Working Reg   | jister 14    |       |           |                 |              |              |         |       | 0000          |

| WREG15   | 001E |        |        |        |        |        |        |         | Working Reg   | jister 15    |       |           |                 |              |              |         |       | 0800          |

| SPLIM    | 0020 |        |        |        |        |        |        | Stac    | k Pointer Lir | nit Register |       |           |                 |              |              |         |       | XXXX          |

| ACCAL    | 0022 |        |        |        |        |        |        |         | ACCA          | L            |       |           |                 |              |              |         |       | XXXX          |

| ACCAH    | 0024 |        |        |        |        |        |        |         | ACCA          | Н            |       |           |                 |              |              |         |       | XXXX          |

| ACCAU    | 0026 |        |        |        | ACCA<  | 39>    |        |         |               |              |       |           | ACO             | CAU          |              |         |       | XXXX          |

| ACCBL    | 0028 |        |        |        |        |        |        |         | ACCB          | L            |       |           |                 |              |              |         |       | XXXX          |

| ACCBH    | 002A |        |        |        |        |        |        |         | ACCB          | Н            |       |           |                 |              |              |         |       | XXXX          |

| ACCBU    | 002C |        |        |        | ACCB<  | 39>    |        |         |               |              |       |           | ACO             | CBU          |              |         |       | XXXX          |

| PCL      | 002E |        |        |        |        |        |        | Program | Counter Lov   | w Word Reg   | ister |           |                 |              |              |         |       | XXXX          |

| PCH      | 0030 | _      |        | —      |        |        | —      |         | _             |              |       | Progra    | am Counter      | High Byte R  | Register     |         |       | 0000          |

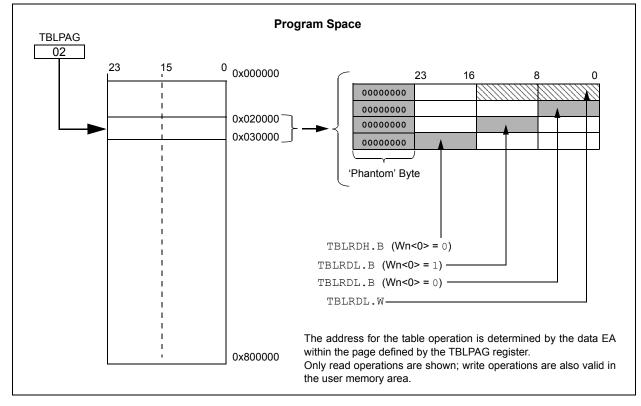

| TBLPAG   | 0032 | _      | —      | —      |        |        | _      |         |               |              |       | Table     | Page Addre      | ss Pointer F | Register     |         |       | 0000          |

| PSVPAG   | 0034 | _      |        | —      |        |        | —      |         | —             |              | Prog  | ram Memor | y Visibility Pa | age Addres   | s Pointer Re | egister |       | 0000          |

| RCOUNT   | 0036 |        |        |        |        |        |        | Repe    | at Loop Cou   | nter Registe | er    |           |                 |              |              |         |       | XXXX          |

| DCOUNT   | 0038 |        |        |        |        |        |        |         | DCOUNT<       |              |       |           |                 |              |              |         |       | XXXX          |

| DOSTARTL | 003A |        |        |        |        |        |        | DOST    | ARTL<15:1     | >            |       |           |                 |              |              |         | 0     | XXXX          |

| DOSTARTH | 003C | _      | —      | _      | —      | —      | —      | —       | —             | _            | _     |           |                 | DOSTAF       | RTH<5:0>     |         |       | 00xx          |

| DOENDL   | 003E |        |        |        |        |        |        | DOE     | NDL<15:1>     | •            |       | •         |                 |              |              |         | 0     | XXXX          |

| DOENDH   | 0040 | _      | —      | —      | —      | —      | —      | —       | —             | _            | —     |           |                 | DOEN         | DH<5:0>      |         |       | 00xx          |

| SR       | 0042 | OA     | OB     | SA     | SB     | OAB    | SAB    | DA      | DC            | IPL2         | IPL1  | IPL0      | RA              | N            | OV           | Z       | С     | 0000          |

| CORCON   | 0044 | —      | —      | _      | US     | EDT    |        | DL<2:0> |               | SATA         | SATB  | SATDW     | ACCSAT          | IPL3         | PSV          | RND     | IF    | 0020          |

| Bit 15  | Bit 14  |                                                                                |                                                                                                                               |                                                                                                                                                                   |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|---------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | DICIT   | Bit 13                                                                         | Bit 12                                                                                                                        | Bit 11                                                                                                                                                            | Bit 10                                                                                                                                                                                                           | Bit 9                                                                                                                                                                                                                                          | Bit 8                                                                                                                     | Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | All<br>Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CN15IE  | CN14IE  | CN13IE                                                                         | CN12IE                                                                                                                        | CN11IE                                                                                                                                                            | -                                                                                                                                                                                                                | —                                                                                                                                                                                                                                              | -                                                                                                                         | CN7IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CN6IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CN5IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CN4IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CN3IE                                                                                                                                                                                                                                                                                                                                                                                                                                               | CN2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CN1IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CN0IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| —       | CN30IE  | CN29IE                                                                         | -                                                                                                                             | CN27IE                                                                                                                                                            | -                                                                                                                                                                                                                | —                                                                                                                                                                                                                                              | CN24IE                                                                                                                    | CN23IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CN22IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CN21IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CN16IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CN15PUE | CN14PUE | CN13PUE                                                                        | CN12PUE                                                                                                                       | CN11PUE                                                                                                                                                           | -                                                                                                                                                                                                                | —                                                                                                                                                                                                                                              | —                                                                                                                         | CN7PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CN6PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CN5PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CN4PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CN3PUE                                                                                                                                                                                                                                                                                                                                                                                                                                              | CN2PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CN1PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CN0PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| —       | CN30PUE | CN29PUE                                                                        | —                                                                                                                             | CN27PUE                                                                                                                                                           | —                                                                                                                                                                                                                | _                                                                                                                                                                                                                                              | CN24PUE                                                                                                                   | CN23PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CN22PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CN21PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CN16PUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |