Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc202-e-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

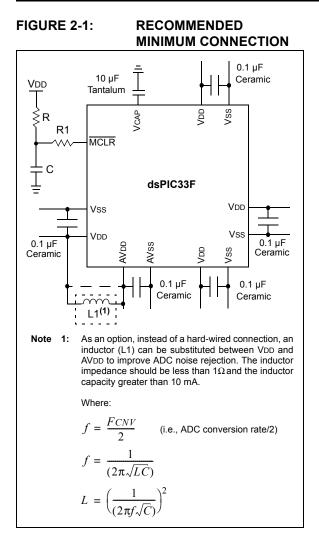

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, preferably surface mount connected within one-eights inch of the VCAP pin connected to ground. The type can be ceramic or tantalum. Refer to **Section 31.0** "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to Section 28.2 "On-Chip Voltage Regulator" for details.

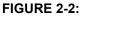

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides for two specific device functions:

- Device Reset

- Device programming and debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### EXAMPLE OF MCLR PIN CONNECTIONS

2:  $\underline{R1} \leq 470\Omega$  will limit any current flowing into MCLR from the external capacitor C, in the event of MCLR pin breakdown due to Electrostatic Discharge (ESD) or <u>Electrical</u> Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met.

#### 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All effective addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

#### 4.2.6 DMA RAM

Every dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 device contains up to 2 Kbytes of dual ported DMA RAM located at the end of Y data space, and is a part of Y data space. Memory locations in the DMA RAM space are accessible simultaneously by the CPU and the DMA controller module. The DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU.

When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

Note: The DMA RAM can be used for general purpose data storage if the DMA function is not required in an application.

# 4.3 Memory Resources

Many useful resources related to Memory Organization are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

#### 4.3.1 KEY RESOURCES

- Section 4. "Program Memory" (DS70203)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### **Special Function Register Maps** 4.4

#### TABLE 4-1: **CPU CORE REGISTERS MAP**

| DS7029  |  |

|---------|--|

| )1G-pag |  |

| je 42   |  |

| SFR Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7        | Bit 6 | Bit 5     | Bit 4           | Bit 3        | Bit 2        | Bit 1   | Bit 0 | All<br>Resets |

|----------|------|--------|--------|--------|--------|--------|--------|---------|---------------|--------------|-------|-----------|-----------------|--------------|--------------|---------|-------|---------------|

| WREG0    | 0000 |        |        |        |        |        |        |         | Working Re    | gister 0     |       |           |                 |              |              |         |       | 0000          |

| WREG1    | 0002 |        |        |        |        |        |        |         | Working Re    | gister 1     |       |           |                 |              |              |         |       | 0000          |

| WREG2    | 0004 |        |        |        |        |        |        |         | Working Re    | gister 2     |       |           |                 |              |              |         |       | 0000          |

| WREG3    | 0006 |        |        |        |        |        |        |         | Working Re    | gister 3     |       |           |                 |              |              |         |       | 0000          |

| WREG4    | 0008 |        |        |        |        |        |        |         | Working Re    | gister 4     |       |           |                 |              |              |         |       | 0000          |

| WREG5    | 000A |        |        |        |        |        |        |         | Working Re    | gister 5     |       |           |                 |              |              |         |       | 0000          |

| WREG6    | 000C |        |        |        |        |        |        |         | Working Re    | gister 6     |       |           |                 |              |              |         |       | 0000          |

| WREG7    | 000E |        |        |        |        |        |        |         | Working Re    | gister 7     |       |           |                 |              |              |         |       | 0000          |

| WREG8    | 0010 |        |        |        |        |        |        |         | Working Re    | gister 8     |       |           |                 |              |              |         |       | 0000          |

| WREG9    | 0012 |        |        |        |        |        |        |         | Working Re    | gister 9     |       |           |                 |              |              |         |       | 0000          |

| WREG10   | 0014 |        |        |        |        |        |        |         | Working Reg   | jister 10    |       |           |                 |              |              |         |       | 0000          |

| WREG11   | 0016 |        |        |        |        |        |        |         | Working Reg   | jister 11    |       |           |                 |              |              |         |       | 0000          |

| WREG12   | 0018 |        |        |        |        |        |        |         | Working Reg   | ister 12     |       |           |                 |              |              |         |       | 0000          |

| WREG13   | 001A |        |        |        |        |        |        |         | Working Reg   | jister 13    |       |           |                 |              |              |         |       | 0000          |

| WREG14   | 001C |        |        |        |        |        |        |         | Working Reg   | jister 14    |       |           |                 |              |              |         |       | 0000          |

| WREG15   | 001E |        |        |        |        |        |        |         | Working Reg   | jister 15    |       |           |                 |              |              |         |       | 0800          |

| SPLIM    | 0020 |        |        |        |        |        |        | Stac    | k Pointer Lir | nit Register |       |           |                 |              |              |         |       | XXXX          |

| ACCAL    | 0022 |        |        |        |        |        |        |         | ACCA          | L            |       |           |                 |              |              |         |       | XXXX          |

| ACCAH    | 0024 |        |        |        |        |        |        |         | ACCA          | Н            |       |           |                 |              |              |         |       | XXXX          |

| ACCAU    | 0026 |        |        |        | ACCA<  | 39>    |        |         |               |              |       |           | ACO             | CAU          |              |         |       | XXXX          |

| ACCBL    | 0028 |        |        |        |        |        |        |         | ACCB          | L            |       |           |                 |              |              |         |       | XXXX          |

| ACCBH    | 002A |        |        |        |        |        |        |         | ACCB          | Н            |       |           |                 |              |              |         |       | XXXX          |

| ACCBU    | 002C |        |        |        | ACCB<  | 39>    |        |         |               |              |       |           | ACO             | CBU          |              |         |       | XXXX          |

| PCL      | 002E |        |        |        |        |        |        | Program | Counter Lov   | w Word Reg   | ister |           |                 |              |              |         |       | XXXX          |

| PCH      | 0030 | _      |        | —      |        |        | —      |         | _             |              |       | Progra    | am Counter      | High Byte R  | Register     |         |       | 0000          |

| TBLPAG   | 0032 | _      | —      | —      |        |        | _      |         |               |              |       | Table     | Page Addre      | ss Pointer F | Register     |         |       | 0000          |

| PSVPAG   | 0034 | _      |        | —      |        |        | —      |         | —             |              | Prog  | ram Memor | y Visibility Pa | age Addres   | s Pointer Re | egister |       | 0000          |

| RCOUNT   | 0036 |        |        |        |        |        |        | Repe    | at Loop Cou   | nter Registe | er    |           |                 |              |              |         |       | XXXX          |

| DCOUNT   | 0038 |        |        |        |        |        |        |         | DCOUNT<       |              |       |           |                 |              |              |         |       | XXXX          |

| DOSTARTL | 003A |        |        |        |        |        |        | DOST    | ARTL<15:1     | >            |       |           |                 |              |              |         | 0     | XXXX          |

| DOSTARTH | 003C | _      | —      | _      | —      | —      | —      | —       | —             | _            | _     |           |                 | DOSTAF       | RTH<5:0>     |         |       | 00xx          |

| DOENDL   | 003E |        |        |        |        |        |        | DOE     | NDL<15:1>     | •            |       | •         |                 |              |              |         | 0     | XXXX          |

| DOENDH   | 0040 | _      | —      | —      | —      | —      | —      | —       | —             | _            | —     |           |                 | DOEN         | DH<5:0>      |         |       | 00xx          |

| SR       | 0042 | OA     | OB     | SA     | SB     | OAB    | SAB    | DA      | DC            | IPL2         | IPL1  | IPL0      | RA              | N            | OV           | Z       | С     | 0000          |

| CORCON   | 0044 | —      | —      | _      | US     | EDT    |        | DL<2:0> |               | SATA         | SATB  | SATDW     | ACCSAT          | IPL3         | PSV          | RND     | IF    | 0020          |

# TABLE 4-1: CPU CORE REGISTERS MAP (CONTINUED)

|          |      |        |        |        |        |        | ,      |        |          |              |           |         |       |       |       |       |       |               |

|----------|------|--------|--------|--------|--------|--------|--------|--------|----------|--------------|-----------|---------|-------|-------|-------|-------|-------|---------------|

| SFR Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8    | Bit 7        | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| MODCON   | 0046 | XMODEN | YMODEN | -      | —      |        | BWN    | /<3:0> |          |              | YWM       | <3:0>   |       |       | XWM   | <3:0> |       | 0000          |

| XMODSRT  | 0048 |        |        |        |        |        |        | >      | (S<15:1> |              |           |         |       |       |       |       | 0     | XXXX          |

| XMODEND  | 004A |        |        |        |        |        |        | >      | (E<15:1> |              |           |         |       |       |       |       | 1     | XXXX          |

| YMODSRT  | 004C |        |        |        |        |        |        | Y      | ′S<15:1> |              |           |         |       |       |       |       | 0     | XXXX          |

| YMODEND  | 004E |        |        |        |        |        |        | γ      | ′E<15:1> |              |           |         |       |       |       |       | 1     | XXXX          |

| XBREV    | 0050 | BREN   |        |        |        |        |        |        |          | XB<14:0>     |           |         |       |       |       |       |       | XXXX          |

| DISICNT  | 0052 | —      | _      |        |        |        |        |        | Disabl   | e Interrupts | Counter R | egister |       |       |       |       |       | XXXX          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-12: I2C1 REGISTER MAP

| SFR Name | Addr     | Bit 15       | Bit 14     | Bit 13     | Bit 12      | Bit 11       | Bit 10       | Bit 9        | Bit 8       | Bit 7 | Bit 6 | Bit 5      | Bit 4        | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|----------|--------------|------------|------------|-------------|--------------|--------------|--------------|-------------|-------|-------|------------|--------------|----------|-------|-------|-------|---------------|

| I2C1RCV  | 0200     | _            | -          |            | _           | _            |              | _            |             |       |       |            | Receive      | Register |       |       |       | 0000          |

| I2C1TRN  | 0202     | _            | _          |            | —           | —            |              | —            | _           |       |       |            | Transmit     | Register |       |       |       | OOFF          |

| I2C1BRG  | 0204     | _            | _          |            | —           | —            |              | —            |             |       |       | Baud Rat   | e Generato   | Register |       |       |       | 0000          |

| I2C1CON  | 0206     | I2CEN        |            | I2CSIDL    | SCLREL      | IPMIEN       | A10M         | DISSLW       | SMEN        | GCEN  | STREN | ACKDT      | ACKEN        | RCEN     | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208     | ACKSTAT      | TRSTAT     | _          | _           | _            | BCL          | GCSTAT       | ADD10       | IWCOL | I2COV | D_A        | Р            | S        | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A     | -            | _          | _          | _           | _            | _            |              |             |       |       | Address    | Register     |          |       |       |       | 0000          |

| I2C1MSK  | 020C     | -            | _          | _          | _           | _            | _            |              |             |       |       | Address Ma | isk Register |          |       |       |       | 0000          |

| Legend:  | x = unkr | nown value o | n Reset, — | = unimpler | nented, rea | d as '0'. Re | set values a | are shown ir | n hexadecir | nal.  |       |            |              |          |       |       |       |               |

## TABLE 4-13: UART1 REGISTER MAP

| SFR Name | Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7        | Bit 6   | Bit 5 | Bit 4       | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|------|----------|--------|----------|--------|--------|--------|-------|------------|--------------|---------|-------|-------------|--------------|-------|--------|-------|---------------|

| U1MODE   | 0220 | UARTEN   | —      | USIDL    | IREN   | RTSMD  |        | UEN1  | UEN0       | WAKE         | LPBACK  | ABAUD | URXINV      | BRGH         | PDSE  | _<1:0> | STSEL | 0000          |

| U1STA    | 0222 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT       | URXISI       | EL<1:0> | ADDEN | RIDLE       | PERR         | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224 | _        | _      | _        | _      | _      | _      | _     | UTX8       |              |         | U     | ART Transm  | nit Register |       |        |       | XXXX          |

| U1RXREG  | 0226 | _        | _      | _        | _      | _      | _      | _     | URX8       |              |         | U     | ART Receive | ed Register  |       |        |       | 0000          |

| U1BRG    | 0228 |          |        |          |        |        |        | Bau   | d Rate Ger | erator Presc | aler    |       |             |              |       |        |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-14: UART2 REGISTER MAP

| SFR Name | Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7        | Bit 6   | Bit 5 | Bit 4      | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|------|----------|--------|----------|--------|--------|--------|-------|------------|--------------|---------|-------|------------|--------------|-------|--------|-------|---------------|

| U2MODE   | 0230 | UARTEN   |        | USIDL    | IREN   | RTSMD  |        | UEN1  | UEN0       | WAKE         | LPBACK  | ABAUD | URXINV     | BRGH         | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA    | 0232 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT       | URXISE       | EL<1:0> | ADDEN | RIDLE      | PERR         | FERR  | OERR   | URXDA | 0110          |

| U2TXREG  | 0234 | —        |        | —        |        | —      |        |       | UTX8       |              |         | U     | ART Transm | nit Register |       |        |       | XXXX          |

| U2RXREG  | 0236 | —        |        | —        |        | —      |        |       | URX8       |              |         | U     | ART Receiv | e Register   |       |        |       | 0000          |

| U2BRG    | 0238 |          |        |          |        |        |        | Bau   | d Rate Ger | erator Presc | aler    |       |            |              |       |        |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER     | 7-16: IPC1              | : INTERRUPT                              | PRIORITY       | CONTROL R         | EGISTER 1        |                 |       |

|--------------|-------------------------|------------------------------------------|----------------|-------------------|------------------|-----------------|-------|

| U-0          | R/W-1                   | R/W-0                                    | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

| —            |                         | T2IP<2:0>                                |                | —                 |                  | OC2IP<2:0>      |       |

| bit 15       |                         |                                          |                |                   |                  |                 | bit   |

| U-0          | R/W-1                   | R/W-0                                    | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

|              |                         | IC2IP<2:0>                               |                | _                 |                  | DMA0IP<2:0>     |       |

| bit 7        |                         |                                          |                |                   |                  |                 | bit   |

| Legend:      |                         |                                          |                |                   |                  |                 |       |

| R = Readab   | le bit                  | W = Writable                             | bit            | U = Unimple       | mented bit, rea  | ad as '0'       |       |

| -n = Value a | t POR                   | '1' = Bit is set                         |                | '0' = Bit is cle  | eared            | x = Bit is unkn | own   |

|              |                         |                                          |                |                   |                  |                 |       |

| bit 15       | Unimpleme               | ented: Read as '                         | כי             |                   |                  |                 |       |

| bit 14-12    | T2IP<2:0>:              | Timer2 Interrupt                         | Priority bits  |                   |                  |                 |       |

|              |                         | rupt is priority 7 (I                    |                | ty interrupt)     |                  |                 |       |

|              | •                       |                                          |                |                   |                  |                 |       |

|              | •                       |                                          |                |                   |                  |                 |       |

|              | •<br>001 = Inter        | rupt is priority 1                       |                |                   |                  |                 |       |

|              |                         | rupt source is dis                       | abled          |                   |                  |                 |       |

| bit 11       | Unimpleme               | ented: Read as '                         | o'             |                   |                  |                 |       |

| bit 10-8     | OC2IP<2:0               | >: Output Compa                          | re Channel     | 2 Interrupt Prior | ity bits         |                 |       |

|              | 111 = Interi            | rupt is priority 7 (I                    | highest priori | ty interrupt)     |                  |                 |       |

|              | •                       |                                          |                |                   |                  |                 |       |

|              | •                       |                                          |                |                   |                  |                 |       |

|              |                         | rupt is priority 1<br>rupt source is dis | abled          |                   |                  |                 |       |

| bit 7        |                         | ented: Read as '                         |                |                   |                  |                 |       |

| bit 6-4      | -                       | : Input Capture C                        |                | errupt Prioritv b | its              |                 |       |

|              |                         | rupt is priority 7 (I                    |                |                   |                  |                 |       |

|              | •                       |                                          | •              |                   |                  |                 |       |

|              | •                       |                                          |                |                   |                  |                 |       |

|              | •<br>001 <b>– Inter</b> | rupt is priority 1                       |                |                   |                  |                 |       |

|              |                         | rupt source is dis                       | abled          |                   |                  |                 |       |

| bit 3        |                         | ented: Read as '                         |                |                   |                  |                 |       |

| bit 2-0      | -                       | :0>: DMA Chann                           |                | nsfer Complete    | e Interrupt Prio | ritv bits       |       |

|              |                         | rupt is priority 7 (I                    |                |                   |                  | .,              |       |

|              | •                       |                                          |                | - • • /           |                  |                 |       |

|              | •                       |                                          |                |                   |                  |                 |       |

|              | •<br>001 = Inter        | rupt is priority 1                       |                |                   |                  |                 |       |

|              |                         | rupt source is dis                       | abled          |                   |                  |                 |       |

|              |                         |                                          |                |                   |                  |                 |       |

NOTES:

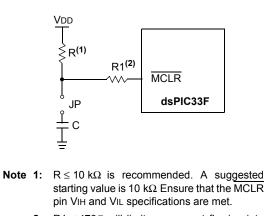

#### 11.6 Peripheral Pin Select

Peripheral pin select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral pin select is performed in software, and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

#### 11.6.1 AVAILABLE PINS

The peripheral pin select feature is used with a range of up to 26 pins. The number of available pins depends on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation RPn in their full pin designation, where RP designates a remappable peripheral and n is the remappable pin number.

#### 11.6.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of special function registers: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 11.6.2.1 Input Mapping

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it is mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-20). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of peripheral pin selections supported by the device.

Figure 11-2 Illustrates remappable pin selection for U1RX input.

| Note: | For input mapping only, the Peripheral Pin |

|-------|--------------------------------------------|

|       | Select (PPS) functionality does not have   |

|       | priority over the TRISx settings.          |

|       | Therefore, when configuring the RPx pin    |

|       | for input, the corresponding bit in the    |

|       | TRISx register must also be configured for |

|       | input (i.e., set to '1').                  |

#### FIGURE 11-2: REMAPPABLE MUX INPUT FOR U1RX

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

## REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0              | U-0 | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |

|------------------|-----|------------------|-------|------------------|------------------|-----------------|-------|

|                  | _   | —                | _     | —                | —                | _               | _     |

| bit 15           |     |                  |       |                  |                  |                 | bit 8 |

|                  |     |                  |       |                  |                  |                 |       |

| U-0              | U-0 | U-0              | R/W-1 | R/W-1            | R/W-1            | R/W-1           | R/W-1 |

| —                | _   | —                |       |                  | INTR2R<4:0>      | •               |       |

| bit 7            |     |                  |       |                  |                  |                 | bit 0 |

|                  |     |                  |       |                  |                  |                 |       |

| Legend:          |     |                  |       |                  |                  |                 |       |

| R = Readable b   | bit | W = Writable     | bit   | U = Unimpler     | mented bit, read | 1 as '0'        |       |

| -n = Value at Po | OR  | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkı | nown  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 INTR2R<4:0>: Assign External Interrupt 2 (INTR2) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25 •

00001 = Input tied to RP1 00000 = Input tied to RP0

| U-0                 | U-0                                                            | U-0                                                    | R/W-0                             | R/W-0                                  | R/W-0                                   | R/W-0           | R/W-0                |

|---------------------|----------------------------------------------------------------|--------------------------------------------------------|-----------------------------------|----------------------------------------|-----------------------------------------|-----------------|----------------------|

| _                   |                                                                | _                                                      | DISSCK                            | DISSDO                                 | MODE16                                  | SMP             | CKE <sup>(1)</sup>   |

| bit 15              |                                                                |                                                        | 2.000.0                           | 2.0020                                 |                                         |                 | bit                  |

|                     |                                                                |                                                        |                                   |                                        |                                         |                 |                      |

| R/W-0               | R/W-0                                                          | R/W-0                                                  | R/W-0                             | R/W-0                                  | R/W-0                                   | R/W-0           | R/W-0                |

| SSEN <sup>(3)</sup> | CKP                                                            | MSTEN                                                  |                                   | SPRE<2:0>(2                            | -)                                      | PPRE<           | <1:0> <sup>(2)</sup> |

| bit 7               |                                                                |                                                        |                                   |                                        |                                         |                 | bit                  |

| Legend:             |                                                                |                                                        |                                   |                                        |                                         |                 |                      |

| R = Readable        | e bit                                                          | W = Writable                                           | bit                               | U = Unimpler                           | nented bit, read                        | as '0'          |                      |

| -n = Value at       | POR                                                            | '1' = Bit is set                                       |                                   | '0' = Bit is cle                       | ared                                    | x = Bit is unkr | nown                 |

| bit 15-13           | Unimplemen                                                     | ted: Read as '                                         | 0'                                |                                        |                                         |                 |                      |

| bit 12              | DISSCK: Dis<br>1 = Internal S                                  |                                                        | bit (SPI Maste<br>abled, pin func | er modes only)<br>tions as I/O         |                                         |                 |                      |

| bit 11              | 1 = SDOx pir                                                   | able SDOx Pin<br>i is not used by<br>i is controlled b | , module; pin f                   | unctions as I/C                        | )                                       |                 |                      |

| bit 10              | 1 = Commun                                                     | ord/Byte Comm<br>ication is word-<br>ication is byte-  | wide (16 bits)                    |                                        |                                         |                 |                      |

| bit 9               | Master mode<br>1 = Input data<br>0 = Input data<br>Slave mode: | a sampled at en<br>a sampled at m                      | nd of data out<br>iddle of data o |                                        |                                         |                 |                      |

| bit 8               | 1 = Serial out                                                 |                                                        | ges on transitio                  |                                        | clock state to Idl<br>ck state to activ |                 |                      |

| bit 7               | <b>SSEN:</b> Slave<br>1 = <u>SSx</u> pin ι                     | Select Enable<br>ised for Slave i                      | bit (Slave mo<br>node             |                                        |                                         | ·               |                      |

| bit 6               | <b>CKP:</b> Clock F<br>1 = Idle state                          | Polarity Select I<br>for clock is a h                  | oit<br>igh level; activ           | /e state is a lov<br>e state is a higl | v level                                 |                 |                      |

| bit 5               |                                                                | ter Mode Enat                                          |                                   | U                                      |                                         |                 |                      |

# REGISTER 18-2: SPIxCON1: SPIx CONTROL REGISTER 1

- Note 1: This bit is not used in Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- **3:** This bit must be cleared when FRMEN = 1.

# 19.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32MC302/304. dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet. refer to Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit ( $I^2C$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

# 19.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The  $l^2C$  module can operate either as a slave or a master on an  $l^2C$  bus.

The following types of  $I^2C$  operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

For details about the communication sequence in each of these modes, refer to the "*dsPIC33F/PIC24H Family Reference Manual*". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual chapters.

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0              | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|-------|

| —               | —     | —                | _     | —                | —                | AMSK9           | AMSK8 |

| bit 15          |       | -                |       |                  |                  | -               | bit 8 |

|                 |       |                  |       |                  |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| AMSK7           | AMSK6 | AMSK5            | AMSK4 | AMSK3            | AMSK2            | AMSK1           | AMSK0 |

| bit 7           |       |                  |       |                  |                  | ·               | bit 0 |

|                 |       |                  |       |                  |                  |                 |       |

| Legend:         |       |                  |       |                  |                  |                 |       |

| R = Readable I  | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

# REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

bit 15-10 Unimplemented: Read as '0'

bit 9-0 AMSKx: Mask for Address bit x Select bit

1 = Enable masking for bit x of incoming message address; bit match not required in this position

0 = Disable masking for bit x; bit match required in this position

| R/W-0        | U-0                            | U-0              | R/W-0                   | R/W-0                  | R/W-0                | R/W-0     | R/W-0 |

|--------------|--------------------------------|------------------|-------------------------|------------------------|----------------------|-----------|-------|

| ADRC         | _                              | _                |                         |                        | SAMC<4:0>            | 1)        |       |

| bit 15       |                                |                  |                         |                        |                      |           | bit   |

|              |                                |                  |                         |                        |                      |           |       |

| R/W-0        | R/W-0                          | R/W-0            | R/W-0                   | R/W-0                  | R/W-0                | R/W-0     | R/W-0 |

|              |                                |                  | ADCS                    | <7:0> <sup>(2)</sup>   |                      |           |       |

| bit 7        |                                |                  |                         |                        |                      |           | bit   |

| Legend:      |                                |                  |                         |                        |                      |           |       |

| R = Readab   | le bit                         | W = Writable I   | oit                     | U = Unimpler           | nented bit, re       | ad as '0' |       |

| -n = Value a | t POR                          | '1' = Bit is set |                         |                        | '0' = Bit is cleared |           | nown  |

|              |                                |                  |                         |                        |                      |           |       |

| bit 15       |                                | Conversion Clo   | ck Source bit           |                        |                      |           |       |

|              |                                | rnal RC clock    |                         |                        |                      |           |       |

|              |                                | rived from syste |                         |                        |                      |           |       |

| bit 14-13    | -                              | nted: Read as '0 |                         |                        |                      |           |       |

| bit 12-8     |                                | : Auto Sample T  | ime bits <sup>(1)</sup> |                        |                      |           |       |

|              | 11111 <b>= 31</b> <sup>-</sup> | TAD              |                         |                        |                      |           |       |

|              | •                              |                  |                         |                        |                      |           |       |

|              | •                              |                  |                         |                        |                      |           |       |

|              | •                              |                  |                         |                        |                      |           |       |

|              | 00001 = 1 TA<br>00000 = 0 TA   |                  |                         |                        |                      |           |       |

| bit 7-0      | ADCS<7:0>:                     | ADC Conversion   | on Clock Sele           | ct bits <sup>(2)</sup> |                      |           |       |

|              | 11111111 =                     | Reserved         |                         |                        |                      |           |       |

|              | •                              |                  |                         |                        |                      |           |       |

|              | •                              |                  |                         |                        |                      |           |       |

|              | •                              |                  |                         |                        |                      |           |       |

|              | •                              |                  |                         |                        |                      |           |       |

|              | 01000000 =                     | Reserved         |                         |                        |                      |           |       |

|              | 00111111 =                     | TCY · (ADCS<7    | 7:0> + 1) = 64          | • TCY = TAD            |                      |           |       |

|              | •                              |                  |                         |                        |                      |           |       |

|              | •                              |                  |                         |                        |                      |           |       |

|              | •                              |                  |                         |                        |                      |           |       |

|              |                                | TCY · (ADCS<7    |                         |                        |                      |           |       |

|              |                                | TCY · (ADCS<7    |                         |                        |                      |           |       |

|              | 00000000 =                     |                  |                         |                        |                      |           |       |

####

2: This bit is not used if AD1CON3<15> (ADRC) = 1.

# 25.2 RTCC Resources

Many useful resources related to RTCC are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwprod-           |

|       | ucts/Devices.aspx?dDoc-                     |

|       | Name=en532315                               |

#### 25.2.1 KEY RESOURCES

- Section 37. "Real-Time Clock and Calendar (RTCC)" (DS70301)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| ALRMEN       CHIME       AMASK<3:0>       ALRMPTR<1:C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0        | R/W-0        | R/W-0             | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|-------------------|---------------|-------------------|-----------------|-----------------|----------------|

| RW-0       R       Readable bit       I       I = Dit is is set       '0' = Bit is cleared       x = Bit is unknown       CHIME       Chime Enable bit       I       = Chime is disabled; ARPT<7:0> bits stop once they reach 0x00       0x0FF       0       C = Chime is disabled; ARPT<7:0> bits stop once they reach 0x00       0x0FF       0       Dit is reserved – do not use       1011 = Once a veet (on ot use       1011 = Once a veet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LRMEN        | CHIME        |                   | AMA           | SK<3:0>           |                 | ALRMP           | TR<1:0>        |

| ARPT<7:0>         bit 7         Legend:         R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15           |              |                   |               |                   |                 |                 | bit            |

| bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 ALRMEN: Alarm Enable bit 1 = Alarm is enabled (cleared automatically after an alarm event whenever ARPT<7:0> = 0x CHIME = 0) 0 = Alarm is disabled bit 14 CHIME: Chime Enable bit 1 = Chime is enabled; ARPT<7:0> bits are allowed to roll over from 0x00 to 0xFF 0 = Chime is disabled; ARPT<7:0> bits stop once they reach 0x00 bit 13-10 AMASK<3:0>: Alarm Mask Configuration bits 1Lx = Reserved - do not use 101x = Reserved - do not use 1011 = Once a year (except when configured for February 29th, once every 4 years) 100 = Once a ayear (except when configured for February 29th, once every 4 years) 101 = Every nour 0100 = Every 10 minutes 011 = Every second 0100 = Every 10 minutes 011 = Every second 0100 = Every 10 adarm Value Register Window Pointer bits Points to the corresponding Alarm Value registers when reading ALRMVALH and ALRMVALL re the ALRMPTR<1:0>: Alarm Value Register Window Pointer bits Points to the corresponding Alarm Value registers when reading ALRMVALH and ALRMVALL re the ALRMPTR<1:0>: value decrements on every read or write of ALRMVALH until it reaches '00 ALRMVAL<15:8>: 11 = Unimplemented 10 = ALRMNTH 1 = ALRMMD 00 = ALRMMNTH 01 = ALRMMAT 01 = ALRMAR 01 = ALRMPR 01 = ALRMPR 01 = ALRMAR 01 = AL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0        | R/W-0        | R/W-0             | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0          |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ALRMEN: Alarm Enable bit       1 = Alarm is enabled (cleared automatically after an alarm event whenever ARPT<7:0> = 0x<br>CHIME = 0)         0 = Alarm is disabled       0 = Alarm is disabled         bit 14       CHIME: Chime Enable bit       1 = Chime is enabled; ARPT<7:0> bits are allowed to roll over from 0x00 to 0xFF         0 = Chime is disabled; ARPT<7:0> bits stop once they reach 0x00       bit 13.10         MMASK<3:0>: Alarm Mask Configuration bits         11xx = Reserved - do not use       101x = Reserved - do not use         101x = Reserved - do not use       101x = Reserved - do not use         101x = Reserved - do not use       101a = Once a year (except when configured for February 29th, once every 4 years)         100a = Once a month       0111 = Conce a year (except when configured for February 29th, once every 4 years)         100a = Once a day       0101 = Every four         0100 = Every 10 minutes       0111 = Every second         0011 = Every second       0001 = Every second         0010 = Every subte decrements on every read or write of ALRMVALH and ALRMVALL re         the ALRMPTR<1:0>: Alarm Value Register Window Pointer bits         Points to the correspo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |              |                   | ARP           | T<7:0>            |                 |                 |                |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ALRMEN: Alarm Enable bit       1 = Alarm is enabled (cleared automatically after an alarm event whenever ARPT<7:0> = 0x         CHIME = 0)       0 = Alarm is disabled       bit 14       CHIME: Chime Enable bit         1 = Chime is enabled; ARPT<7:0> bits are allowed to roll over from 0x00 to 0xFF       0 = Chime is disabled; ARPT<7:0> bits stop once they reach 0x00         bit 13-10       AMASK<3:0>: Alarm Mask Configuration bits       11xx = Reserved - do not use         1011 = Once a year (except when configured for February 29th, once every 4 years)       1000 = Once a month         0111 = Once a week       0101 = Once a week       0101 = Every nour         0101 = Every nour       0101 = Every nour       0101 = Every nour         0101 = Every nour       0101 = Every nour       011 = Every second         0000 = Every half second       0000 = Every half second       0000 = Every half second         bit 9-8       ALRMPTR<1:0: Alarm Value Register Window Pointer bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7            |              |                   |               |                   |                 |                 | bit            |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ALRMEN: Alarm Enable bit       1 = Alarm is enabled (cleared automatically after an alarm event whenever ARPT<7:0> = 0x<br>CHIME = 0)         0 = Alarm is disabled       0' = Bit is cleared       x = Bit is unknown         bit 14       CHIME: Chime Enable bit       1 = Chime is disabled; ARPT<7:0> bits are allowed to roll over from 0x00 to 0xFF         0 = Chime is disabled; ARPT<7:0> bits stop once they reach 0x00       00xFF         0 = Chime is disabled; ARPT<7:0> bits stop once they reach 0x00         bit 13-10       AMASK<3:0>: Alarm Mask Configuration bits         11x = Reserved - do not use       101 = Once a week (except when configured for February 29th, once every 4 years)         1001 = Once a week       0101 = Once a week         0101 = Once a week       0101 = Every nour         0100 = Every 10 minutes       0011 = Every nour         0100 = Every 10 seconds       0001 = Every half second         0000 = Every 10 seconds       0001 = Every half second         0011 = Every second       0000 = Chimplemented         101 = ALRMPTR<1:0> value decrements on every read or write of ALRMVALH and ALRMVALL referses '00         ALRMPTR<1:0> value decrements on every read or write of ALRMVALH until it reaches '00         ALRMVD       0 = ALRMINN         ALRMMIN       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | jend:        |              |                   |               |                   |                 |                 |                |

| bit 15 ALRMEN: Alarm Enable bit 1 = Alarm is enabled (cleared automatically after an alarm event whenever ARPT<7:0> = 0x CHIME = 0) 0 = Alarm is disabled bit 14 CHIME: Chime Enable bit 1 = Chime is enabled; ARPT<7:0> bits are allowed to roll over from 0x00 to 0xFF 0 = Chime is disabled; ARPT<7:0> bits stop once they reach 0x00 bit 13-10 AMASK<3:0>: Alarm Mask Configuration bits 11xx = Reserved – do not use 101x = Reserved – do not use 101x = Reserved – do not use 1011 = Once a week 0110 = Once a week 0110 = Once a week 0110 = Every 10 minutes 0010 = Every 10 minutes 0010 = Every 10 minutes 0010 = Every 10 seconds 0000 = Every half second bit 9-8 ALRMPTR<1:0>: Alarm Value Register Window Pointer bits Points to the corresponding Alarm Value registers when reading ALRMVALH and ALRMVALL re the ALRMPTR<1:0> value decrements on every read or write of ALRMVALH until it reaches '00 ALRMVAL<7:0>: 11 = Unimplemented 10 = ALRMMNN ALRMVAL<7:0>: 11 = Unimplemented 10 = ALRMMNN ALRMVAL<7:0>: 11 = Unimplemented 10 = ALRMANTH 01 = ALRMANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |              |                   |               | •                 |                 |                 |                |

| <pre>1 = Alarm is enabled (cleared automatically after an alarm event whenever ARPT&lt;7:0&gt; = 0x<br/>CHIME = 0)<br/>0 = Alarm is disabled<br/>bit 14 CHIME: Chime Enable bit<br/>1 = Chime is enabled; ARPT&lt;7:0&gt; bits are allowed to roll over from 0x00 to 0xFF<br/>0 = Chime is disabled; ARPT&lt;7:0&gt; bits stop once they reach 0x00<br/>bit 13-10 AMASK&lt;3:0&gt;: Alarm Mask Configuration bits<br/>11xx = Reserved – do not use<br/>101x = Reserved – do not use<br/>1001 = Once a year (except when configured for February 29th, once every 4 years)<br/>1000 = Once a week<br/>0110 = Once a week<br/>0110 = Every mour<br/>0100 = Every 10 minutes<br/>0011 = Every minute<br/>0010 = Every 10 minutes<br/>0011 = Every second<br/>0000 = Every 10 seconds<br/>0001 = Every half second<br/>bit 9-8 ALRMPTR&lt;1:0&gt;: Alarm Value Register Window Pointer bits<br/>Points to the corresponding Alarm Value registers when reading ALRMIVALH and ALRMIVALL re<br/>the ALRMPTR&lt;1:0&gt;: Alarm Value Register when reading ALRMIVALH until it reaches '00<br/>ALRMWAL&lt;15:8&gt;:<br/>11 = Unimplemented<br/>10 = ALRMINTH<br/>01 = ALRMINTH<br/>01 = ALRMINTH<br/>01 = ALRMINT<br/>01 = ALRMINTE<br/>01 = AL</pre> | · Value at P | OR           | '1' = Bit is set  |               | '0' = Bit is cle  | ared            | x = Bit is unkr | nown           |

| <pre>1 = Alarm is enabled (cleared automatically after an alarm event whenever ARPT&lt;7:0&gt; = 0x<br/>CHIME = 0)<br/>0 = Alarm is disabled<br/>bit 14 CHIME: Chime Enable bit<br/>1 = Chime is enabled; ARPT&lt;7:0&gt; bits are allowed to roll over from 0x00 to 0xFF<br/>0 = Chime is disabled; ARPT&lt;7:0&gt; bits stop once they reach 0x00<br/>bit 13-10 AMASK&lt;3:0&gt;: Alarm Mask Configuration bits<br/>11xx = Reserved – do not use<br/>101x = Reserved – do not use<br/>1001 = Once a year (except when configured for February 29th, once every 4 years)<br/>1000 = Once a week<br/>0110 = Once a week<br/>0110 = Every mour<br/>0100 = Every 10 minutes<br/>0011 = Every minute<br/>0010 = Every 10 minutes<br/>0011 = Every second<br/>0000 = Every 10 seconds<br/>0001 = Every half second<br/>bit 9-8 ALRMPTR&lt;1:0&gt;: Alarm Value Register Window Pointer bits<br/>Points to the corresponding Alarm Value registers when reading ALRMIVALH and ALRMIVALL re<br/>the ALRMPTR&lt;1:0&gt;: Alarm Value Register when reading ALRMIVALH until it reaches '00<br/>ALRMWAL&lt;15:8&gt;:<br/>11 = Unimplemented<br/>10 = ALRMINTH<br/>01 = ALRMINTH<br/>01 = ALRMINTH<br/>01 = ALRMINT<br/>01 = ALRMINTE<br/>01 = AL</pre> | 15           |              | Varm Enable bit   |               |                   |                 |                 |                |