Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc202-e-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1:          | 1: PINOUT I/O DESCRIPTIONS |                                |            |                                                                                                                                                                                                                                                                   |  |  |

|---------------------|----------------------------|--------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name            | Pin<br>Type                | Buffer<br>Type                 | PPS        | Description                                                                                                                                                                                                                                                       |  |  |

| AN0-AN8             | I                          | Analog                         | No         | Analog input channels.                                                                                                                                                                                                                                            |  |  |

| CLKI                | <br>  0                    | ST/CMOS                        | No<br>No   | External clock source input. Always associated with OSC1 pin functio<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally, functions as CLKO in RC and EC modes.<br>Always associated with OSC2 pin function. |  |  |

| OSC1                |                            | ST/CMOS                        | No         | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                                                                                                              |  |  |

| OSC2                | I/O                        | _                              | No         | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                         |  |  |

| SOSCI<br>SOSCO      | <br>  0                    | ST/CMOS                        | No<br>No   | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.<br>32.768 kHz low-power oscillator crystal output.                                                                                                                                                 |  |  |

| CN0-CN30            | I                          | ST                             | No         | Change notification inputs. Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                  |  |  |

| IC1-IC2<br>IC7-IC8  |                            | ST<br>ST                       | Yes<br>Yes | Capture inputs 1/2.<br>Capture inputs 7/8.                                                                                                                                                                                                                        |  |  |

| OCFA<br>OC1-OC4     | <br>  0                    | ST<br>—                        | Yes<br>Yes | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).<br>Compare outputs 1 through 4.                                                                                                                                                                       |  |  |

| INT0                | I                          | ST                             | No         | External interrupt 0.                                                                                                                                                                                                                                             |  |  |

| INT1                |                            | ST                             | Yes        | External interrupt 1.                                                                                                                                                                                                                                             |  |  |

| INT2<br>RA0-RA4     | 1                          | ST                             | Yes        | External interrupt 2.                                                                                                                                                                                                                                             |  |  |

| RA0-RA4<br>RA7-RA10 | 1/O<br>1/O                 | ST<br>ST                       | No<br>No   | PORTA is a bidirectional I/O port.<br>PORTA is a bidirectional I/O port.                                                                                                                                                                                          |  |  |

| RB0-RB15            | I/O                        | ST                             | No         | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                |  |  |

| RC0-RC9             | I/O                        | ST                             | No         | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                |  |  |

| T1CK                | I                          | ST                             | No         | Timer1 external clock input.                                                                                                                                                                                                                                      |  |  |

| T2CK                |                            | ST                             | Yes        | Timer2 external clock input.                                                                                                                                                                                                                                      |  |  |

| T3CK<br>T4CK        |                            | ST<br>ST                       | Yes<br>Yes | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                                                                                                      |  |  |

| T5CK                |                            | ST                             | Yes        | Timer5 external clock input.                                                                                                                                                                                                                                      |  |  |

| U1CTS               | 1                          | ST                             | Yes        | UART1 clear to send.                                                                                                                                                                                                                                              |  |  |

| U1RTS               | 0                          | _                              | Yes        | UART1 ready to send.                                                                                                                                                                                                                                              |  |  |

| U1RX                | I                          | ST                             | Yes        | UART1 receive.                                                                                                                                                                                                                                                    |  |  |

| U1TX                | 0                          | —                              | Yes        | UART1 transmit.                                                                                                                                                                                                                                                   |  |  |

| U2CTS               | I I                        | ST                             | Yes        | UART2 clear to send.                                                                                                                                                                                                                                              |  |  |

| U2RTS               | 0                          | -                              | Yes        | UART2 ready to send.                                                                                                                                                                                                                                              |  |  |

| U2RX<br>U2TX        |                            | ST<br>—                        | Yes<br>Yes | UART2 receive.<br>UART2 transmit.                                                                                                                                                                                                                                 |  |  |

|                     |                            |                                |            |                                                                                                                                                                                                                                                                   |  |  |

| SCK1<br>SDI1        | I/O                        | ST<br>ST                       | Yes<br>Yes | Synchronous serial clock input/output for SPI1.<br>SPI1 data in.                                                                                                                                                                                                  |  |  |

| SD01                | 0                          |                                | Yes        | SPI1 data out.                                                                                                                                                                                                                                                    |  |  |

| SS1                 | I/O                        | ST                             | Yes        | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                    |  |  |

| SCK2                | I/O                        | ST                             | Yes        | Synchronous serial clock input/output for SPI2.                                                                                                                                                                                                                   |  |  |

| SDI2                | I                          | ST                             | Yes        | SPI2 data in.                                                                                                                                                                                                                                                     |  |  |

| SDO2                | 0                          | —                              | Yes        | SPI2 data out.                                                                                                                                                                                                                                                    |  |  |

| SS2                 | I/O                        | ST                             | Yes        | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                    |  |  |

| SCL1                | I/O                        | ST                             | No         | Synchronous serial clock input/output for I2C1.                                                                                                                                                                                                                   |  |  |

| SDA1                | I/O                        | ST                             | No         | Synchronous serial data input/output for I2C1.                                                                                                                                                                                                                    |  |  |

| ASCL1               | I/O                        | ST                             | No         | Alternate synchronous serial clock input/output for I2C1.                                                                                                                                                                                                         |  |  |

| ASDA1               | I/O                        | ST                             | No         | Alternate synchronous serial data input/output for I2C1.                                                                                                                                                                                                          |  |  |

|                     |                            | S compatibl                    |            |                                                                                                                                                                                                                                                                   |  |  |

|                     |                            | Frigger input<br>eral Pin Sele |            | MOS levels O = Output I = Input<br>TTL = TTL input buffer                                                                                                                                                                                                         |  |  |

| сг                  |                            |                                |            |                                                                                                                                                                                                                                                                   |  |  |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS

| Pin Name     | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                                                |  |  |  |  |

|--------------|-------------|----------------|-----|------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TMS          | Ι           | ST             | No  | JTAG Test mode select pin.                                                                                 |  |  |  |  |

| ТСК          | Ι           | ST             | No  | JTAG test clock input pin.                                                                                 |  |  |  |  |

| TDI          | Ι           | ST             | No  | JTAG test data input pin.                                                                                  |  |  |  |  |

| TDO          | 0           | —              | No  | JTAG test data output pin.                                                                                 |  |  |  |  |

| INDX1        | Ι           | ST             | Yes | Quadrature Encoder Index1 Pulse input.                                                                     |  |  |  |  |

| QEA1         | I           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary Timer External Clock/Gate input in Timer mode.    |  |  |  |  |

| QEB1         | Ι           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary Timer External Clock/Gate input in Timer mode.    |  |  |  |  |

| UPDN1        | 0           | CMOS           | Yes | Position Up/Down Counter Direction State.                                                                  |  |  |  |  |

| INDX2        | Ι           | ST             | Yes | Quadrature Encoder Index2 Pulse input.                                                                     |  |  |  |  |

| QEA2         | Ι           | ST             | Yes | Quadrature Encoder Phase A input in QEI2 mode. Auxiliary Timer<br>External Clock/Gate input in Timer mode. |  |  |  |  |

| QEB2         | I           | ST             | Yes | Quadrature Encoder Phase A input in QEI2 mode. Auxiliary Timer External Clock/Gate input in Timer mode.    |  |  |  |  |

| UPDN2        | 0           | CMOS           | Yes | Position Up/Down Counter Direction State.                                                                  |  |  |  |  |

| C1RX         | I           | ST             | Yes | ECAN1 bus receive pin.                                                                                     |  |  |  |  |

| C1TX         | 0           | —              | Yes | ECAN1 bus transmit pin.                                                                                    |  |  |  |  |

| RTCC         | 0           | _              | No  | Real-Time Clock Alarm Output.                                                                              |  |  |  |  |

| CVREF        | 0           | ANA            | No  | Comparator Voltage Reference Output.                                                                       |  |  |  |  |

| C1IN-        | Ι           | ANA            | No  | Comparator 1 Negative Input.                                                                               |  |  |  |  |

| C1IN+        | I           | ANA            | No  | Comparator 1 Positive Input.                                                                               |  |  |  |  |

| C1OUT        | 0           | _              | Yes | Comparator 1 Output.                                                                                       |  |  |  |  |

| C2IN-        | Ι           | ANA            | No  | Comparator 2 Negative Input.                                                                               |  |  |  |  |

| C2IN+        | Ι           | ANA            | No  | Comparator 2 Positive Input.                                                                               |  |  |  |  |

| C2OUT        | 0           |                | Yes | Comparator 2 Output.                                                                                       |  |  |  |  |

| PMA0         | I/O         | TTL/ST         | No  | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes).                 |  |  |  |  |

| PMA1         | I/O         | TTL/ST         | No  | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes).                 |  |  |  |  |

| PMA2 -PMPA10 | 0           | _              | No  | Parallel Master Port Address (Demultiplexed Master modes).                                                 |  |  |  |  |

| PMBE         | Ō           |                | No  | Parallel Master Port Byte Enable Strobe.                                                                   |  |  |  |  |

| PMCS1        | 0           | _              | No  | Parallel Master Port Chip Select 1 Strobe.                                                                 |  |  |  |  |

| PMD0-PMPD7   | I/O         | TTL/ST         | No  | Parallel Master Port Data (Demultiplexed Master mode) or Address/<br>Data (Multiplexed Master modes).      |  |  |  |  |

| PMRD         | 0           | _              | No  | Parallel Master Port Read Strobe.                                                                          |  |  |  |  |

| PMWR         | Ō           | —              | No  | Parallel Master Port Write Strobe.                                                                         |  |  |  |  |

| DAC1RN       | 0           | _              | No  | DAC1 Negative Output.                                                                                      |  |  |  |  |

| DAC1RP       | 0           | —              | No  | DAC1 Positive Output.                                                                                      |  |  |  |  |

| DAC1RM       | 0           |                | No  | DAC1 Output indicating middle point value (typically 1.65V).                                               |  |  |  |  |

| DAC2RN       | 0           |                | No  | DAC2 Negative Output.                                                                                      |  |  |  |  |

| DAC2RP       | 0           | —              | No  | DAC2 Positive Output.                                                                                      |  |  |  |  |

| DAC2RM       | 0           | 1              | No  | DAC2 Output indicating middle point value (typically 1.65V).                                               |  |  |  |  |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog inputP = PoweO = OutputI = InputTTL = TTL input buffer

| Part<br>Number | Vendor    | Freq.  | Load<br>Cap. | Package<br>Case | Frequency<br>Tolerance | Mounting<br>Type | Operating<br>Temperature |

|----------------|-----------|--------|--------------|-----------------|------------------------|------------------|--------------------------|

| FCR4.0M5T      | TDK Corp. | 4 MHz  | N/A          | Radial          | ±0.5%                  | TH               | -40°C to +85°C           |

| FCR8.0M5       | TDK Corp. | 8 MHz  | N/A          | Radial          | ±0.5%                  | TH               | -40°C to +85°C           |

| HWZT-10.00MD   | TDK Corp. | 10 MHz | N/A          | Radial          | ±0.5%                  | TH               | -40°C to +85°C           |

| HWZT-20.00MD   | TDK Corp. | 20 MHz | N/A          | Radial          | ±0.5%                  | TH               | -40°C to +85°C           |

| TABLE 2-2: | RESONATOR | RECOMMENDATIONS |

|------------|-----------|-----------------|

|------------|-----------|-----------------|

Legend: TH = Through Hole

# 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to less than or equal to 8 MHz for start-up with PLL enabled to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

# 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the analog-to-digital input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in this register that correspond to the analog-to-digital pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain analog-to-digital pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all analog-to-digital pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

# 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor between Vss and the unused pin.

#### 4.4.1 SOFTWARE STACK

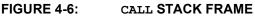

In addition to its use as a working register, the W15 register in the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

**Note:** A PC push during exception processing concatenates the SRL register to the MSb of the PC prior to the push.

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. The SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, the SPLIM<0> is forced to '0' because all stack operations must be word aligned.

Whenever an EA is generated using the W15 as a source or destination pointer, the resulting address is compared with the value in the SPLIM register. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap does not occur. The stack error trap occurs on a subsequent push operation. For example, to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### 4.4.2 DATA RAM PROTECTION FEATURE

The dsPIC33F product family supports Data RAM protection features that enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. The BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. The SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

# 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-40 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (near data space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

# 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where:

Operand 1 is always a working register (that is, the addressing mode can only be register direct), which is referred to as Wb.

Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

Note: Not all instructions support all the addressing modes listed above. Individual instructions can support different subsets of these addressing modes.

#### FIGURE 7-1: dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/ X04 INTERRUPT VECTOR TABLE

|                                   | Reset – GOTO Instruction          | 0x000000          |                                                        |

|-----------------------------------|-----------------------------------|-------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Address              | 0x000002          |                                                        |

|                                   | Reserved                          | 0x000004          |                                                        |

|                                   | Oscillator Fail Trap Vector       |                   |                                                        |

|                                   | Address Error Trap Vector         |                   |                                                        |

|                                   | Stack Error Trap Vector           |                   |                                                        |

|                                   | Math Error Trap Vector            |                   |                                                        |

|                                   | DMA Error Trap Vector             |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Interrupt Vector 0                | 0x000014          |                                                        |

|                                   | Interrupt Vector 1                |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | Interrupt Vector 52               | 0x00007C          | Interview Vector Table (IVT)(1)                        |

|                                   | Interrupt Vector 53               | 0x00007E          | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| ity                               | Interrupt Vector 54               | 0x000080          |                                                        |

| jo                                | ~                                 |                   |                                                        |

| Ē                                 | ~                                 |                   |                                                        |

| de                                | ~                                 |                   |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 116              | 0x0000FC          |                                                        |

| Iral                              | Interrupt Vector 117              | 0x0000FE          |                                                        |

| atr                               | Reserved                          | 0x000100          |                                                        |

| Z                                 | Reserved                          | 0x000102          |                                                        |

| sinç                              | Reserved                          |                   |                                                        |

| eas                               | Oscillator Fail Trap Vector       |                   |                                                        |

| ů –                               | Address Error Trap Vector         |                   |                                                        |

| ă                                 | Stack Error Trap Vector           |                   |                                                        |

|                                   | Math Error Trap Vector            |                   |                                                        |

|                                   | DMA Error Trap Vector             |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Interrupt Vector 0                | 0x000114          |                                                        |

|                                   | Interrupt Vector 1                |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 |                   | (4)                                                    |

|                                   | ~                                 |                   | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52               | 0x00017C          |                                                        |

|                                   | Interrupt Vector 53               | 0x00017E          |                                                        |

|                                   | Interrupt Vector 54               | 0x000180          |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 | _                 |                                                        |

|                                   |                                   |                   | 1                                                      |

|                                   | Interrupt Vector 116              |                   |                                                        |

| ₩                                 | Interrupt Vector 117              | 0x0001FE          |                                                        |

| ۲                                 | Start of Code                     | 0x000200          |                                                        |

|                                   |                                   |                   |                                                        |

|                                   |                                   |                   |                                                        |

| Note 1: See                       | Table 7-1 for the list of impleme | ented interrupt v | rectors                                                |

|                                   |                                   |                   |                                                        |

|                                   |                                   |                   |                                                        |

| R/W-0                         | R/W-0                                                                                        | R/W-0                                                                                        | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|---------|--|--|--|--|

| U2TXIE                        | U2RXIE                                                                                       | INT2IE                                                                                       | T5IE           | T4IE             | OC4IE           | OC3IE           | DMA2IE  |  |  |  |  |

| bit 15                        | ·                                                                                            | ·                                                                                            |                | •                |                 |                 | bit 8   |  |  |  |  |

|                               |                                                                                              |                                                                                              |                |                  |                 |                 |         |  |  |  |  |

| R/W-0                         | R/W-0                                                                                        | U-0                                                                                          | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |

| IC8IE                         | IC7IE                                                                                        |                                                                                              | INT1IE         | CNIE             | CMIE            | MI2C1IE         | SI2C1IE |  |  |  |  |

| bit 7                         |                                                                                              |                                                                                              |                |                  |                 |                 | bit 0   |  |  |  |  |

|                               |                                                                                              |                                                                                              |                |                  |                 |                 |         |  |  |  |  |

| Legend:                       | I I.:.                                                                                       |                                                                                              | L :4           |                  |                 |                 |         |  |  |  |  |

| R = Readab                    |                                                                                              | W = Writable                                                                                 |                |                  | nented bit, rea |                 |         |  |  |  |  |

| -n = Value a                  | t POR                                                                                        | '1' = Bit is set                                                                             | t              | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |  |  |  |  |

| bit 15                        |                                                                                              | RT2 Transmitte                                                                               | r Intorrunt En | abla hit         |                 |                 |         |  |  |  |  |

| DIL 15                        |                                                                                              | request enable                                                                               | -              |                  |                 |                 |         |  |  |  |  |

|                               |                                                                                              | request not en                                                                               |                |                  |                 |                 |         |  |  |  |  |

| bit 14                        | U2RXIE: UA                                                                                   | RT2 Receiver I                                                                               | nterrupt Enab  | le bit           |                 |                 |         |  |  |  |  |

|                               | 1 = Interrupt                                                                                | 1 = Interrupt request enabled                                                                |                |                  |                 |                 |         |  |  |  |  |

|                               | 0 = Interrupt                                                                                | request not ena                                                                              | abled          |                  |                 |                 |         |  |  |  |  |

| bit 13                        |                                                                                              | rnal Interrupt 2                                                                             |                |                  |                 |                 |         |  |  |  |  |

|                               | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul> |                                                                                              |                |                  |                 |                 |         |  |  |  |  |

| bit 12                        | -                                                                                            | -                                                                                            |                |                  |                 |                 |         |  |  |  |  |

| DIL 12                        |                                                                                              | i Interrupt Enab                                                                             |                |                  |                 |                 |         |  |  |  |  |

|                               | <ol> <li>I = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ol> |                                                                                              |                |                  |                 |                 |         |  |  |  |  |

| bit 11                        | T4IE: Timer4                                                                                 | Interrupt Enab                                                                               | le bit         |                  |                 |                 |         |  |  |  |  |

|                               | 1 = Interrupt                                                                                | 1 = Interrupt request enabled                                                                |                |                  |                 |                 |         |  |  |  |  |

|                               | 0 = Interrupt                                                                                | 0 = Interrupt request not enabled                                                            |                |                  |                 |                 |         |  |  |  |  |

| bit 10                        | -                                                                                            | out Compare Ch                                                                               |                | upt Enable bit   |                 |                 |         |  |  |  |  |

| 1 = Interrupt request enabled |                                                                                              |                                                                                              |                |                  |                 |                 |         |  |  |  |  |

| hit 0                         | •                                                                                            | 0 = Interrupt request not enabled                                                            |                |                  |                 |                 |         |  |  |  |  |

| bit 9                         | •                                                                                            | <b>DC3IE:</b> Output Compare Channel 3 Interrupt Enable bit                                  |                |                  |                 |                 |         |  |  |  |  |

|                               |                                                                                              | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul> |                |                  |                 |                 |         |  |  |  |  |

| bit 8                         | DMA2IE: DMA Channel 2 Data Transfer Complete Interrupt Enable bit                            |                                                                                              |                |                  |                 |                 |         |  |  |  |  |

|                               |                                                                                              | 1 = Interrupt request enabled                                                                |                |                  |                 |                 |         |  |  |  |  |

|                               | 0 = Interrupt                                                                                | 0 = Interrupt request not enabled                                                            |                |                  |                 |                 |         |  |  |  |  |

| bit 7                         | IC8IE: Input                                                                                 | Capture Chann                                                                                | el 8 Interrupt | Enable bit       |                 |                 |         |  |  |  |  |

|                               |                                                                                              | request enable                                                                               |                |                  |                 |                 |         |  |  |  |  |

|                               | •                                                                                            | request not en                                                                               |                |                  |                 |                 |         |  |  |  |  |

| bit 6                         | -                                                                                            | Capture Chann                                                                                | -              | Enable bit       |                 |                 |         |  |  |  |  |

|                               |                                                                                              | request enable                                                                               |                |                  |                 |                 |         |  |  |  |  |

| hit 5                         | 0 = Interrupt request not enabled                                                            |                                                                                              |                |                  |                 |                 |         |  |  |  |  |

bit 5Unimplemented: Read as '0'bit 4INT1IE: External Interrupt 1 Enable

#### bit 4 INT1IE: External Interrupt 1 Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled

# bit 3 CNIE: Input Change Notification Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| U-0            | U-0                                                                                              | U-0                                                                                              | U-0            | R-1               | R-1              | R-1             | R-1   |  |  |  |  |

|----------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| _              | _                                                                                                | _                                                                                                | _              |                   | LSTCH            |                 |       |  |  |  |  |

| bit 15         |                                                                                                  |                                                                                                  |                |                   |                  |                 | bit   |  |  |  |  |

|                |                                                                                                  |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

| R-0            | R-0                                                                                              | R-0                                                                                              | R-0            | R-0               | R-0              | R-0             | R-0   |  |  |  |  |

| PPST7          | PPST6                                                                                            | PPST5                                                                                            | PPST4          | PPST3             | PPST2            | PPST1           | PPST0 |  |  |  |  |

| bit 7          |                                                                                                  | •                                                                                                | •              |                   |                  | •               | bit   |  |  |  |  |

| Legend:        |                                                                                                  |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

| R = Readable   | e bit                                                                                            | W = Writable                                                                                     | bit            | U = Unimplem      | nented bit, read | as '0'          |       |  |  |  |  |

| -n = Value at  |                                                                                                  | '1' = Bit is set                                                                                 |                | '0' = Bit is clea |                  | x = Bit is unkr | nown  |  |  |  |  |

|                |                                                                                                  |                                                                                                  |                | 0 2000000         |                  |                 |       |  |  |  |  |

| bit 15-12      | Unimplemen                                                                                       | ted: Read as '                                                                                   | 0'             |                   |                  |                 |       |  |  |  |  |

| bit 11-8       | LSTCH<3:0>                                                                                       | : Last DMA Ch                                                                                    | annel Active I | oits              |                  |                 |       |  |  |  |  |

|                | 1111 <b>= No Di</b>                                                                              | MA transfer ha                                                                                   | s occurred sir | ice system Res    | et               |                 |       |  |  |  |  |

|                | 1110-1000 =                                                                                      |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

|                |                                                                                                  | lata transfer wa<br>lata transfer wa                                                             |                |                   |                  |                 |       |  |  |  |  |

|                |                                                                                                  | 0110 = Last data transfer was by DMA Channel 6<br>0101 = Last data transfer was by DMA Channel 5 |                |                   |                  |                 |       |  |  |  |  |

|                |                                                                                                  | lata transfer w                                                                                  |                |                   |                  |                 |       |  |  |  |  |

|                |                                                                                                  | 0011 = Last data transfer was by DMA Channel 3<br>0010 = Last data transfer was by DMA Channel 2 |                |                   |                  |                 |       |  |  |  |  |

|                |                                                                                                  |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

|                | 0001 = Last data transfer was by DMA Channel 1<br>0000 = Last data transfer was by DMA Channel 0 |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

| bit 7          | PPST7: Chan                                                                                      | nel 7 Ping-Por                                                                                   | ng Mode Statu  | ıs Flag bit       |                  |                 |       |  |  |  |  |

|                | 1 = DMA7STB register selected<br>0 = DMA7STA register selected                                   |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

| bit 6          |                                                                                                  | nel 6 Ping-Por                                                                                   |                | is Flag bit       |                  |                 |       |  |  |  |  |

|                |                                                                                                  | B register selec                                                                                 | -              | 3                 |                  |                 |       |  |  |  |  |

|                |                                                                                                  | A register selec                                                                                 |                |                   |                  |                 |       |  |  |  |  |

| bit 5          | PPST5: Chan                                                                                      | nel 5 Ping-Por                                                                                   | ng Mode Statu  | is Flag bit       |                  |                 |       |  |  |  |  |

|                | 1 = DMA5STB register selected                                                                    |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

|                |                                                                                                  | A register selec                                                                                 |                |                   |                  |                 |       |  |  |  |  |

| bit 4          |                                                                                                  | nel 4 Ping-Por                                                                                   | •              | is Flag bit       |                  |                 |       |  |  |  |  |

|                |                                                                                                  | 3 register seleo<br>A register seleo                                                             |                |                   |                  |                 |       |  |  |  |  |

| bit 3          |                                                                                                  | inel 3 Ping-Por                                                                                  |                | ıs Flag bit       |                  |                 |       |  |  |  |  |

|                | 1 = DMA3STB register selected                                                                    |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

|                |                                                                                                  | A register selec                                                                                 |                |                   |                  |                 |       |  |  |  |  |

| bit 2          |                                                                                                  | PPST2: Channel 2 Ping-Pong Mode Status Flag bit                                                  |                |                   |                  |                 |       |  |  |  |  |

|                | 1 = DMA2STB register selected<br>0 = DMA2STA register selected                                   |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

|                |                                                                                                  |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

| bit 1          | <b>PPST1:</b> Channel 1 Ping-Pong Mode Status Flag bit<br>1 = DMA1STB register selected          |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

| bit 1          | 1 = DMA1STE                                                                                      | 3 register seled                                                                                 | cted           |                   |                  |                 |       |  |  |  |  |

| bit 1          |                                                                                                  | B register seled<br>A register seled                                                             |                |                   |                  |                 |       |  |  |  |  |

| bit 1<br>bit 0 | 0 = DMA1STA                                                                                      | -                                                                                                | ted            | ıs Flag bit       |                  |                 |       |  |  |  |  |

| Oscillator Mode                                    | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Note |

|----------------------------------------------------|-------------------|-------------|------------|-------------|

| Fast RC Oscillator with Divide-by-N<br>(FRCDIVN)   | Internal          | XX          | 111        | 1, 2        |

| Fast RC Oscillator with Divide-by-16<br>(FRCDIV16) | Internal          | XX          | 110        | 1           |

| Low-Power RC Oscillator (LPRC)                     | Internal          | XX          | 101        | 1           |

| Secondary (Timer1) Oscillator (Sosc)               | Secondary         | XX          | 100        | 1           |

| Primary Oscillator (HS) with PLL<br>(HSPLL)        | Primary           | 10          | 011        | -           |

| Primary Oscillator (XT) with PLL<br>(XTPLL)        | Primary           | 01          | 011        | -           |

| Primary Oscillator (EC) with PLL<br>(ECPLL)        | Primary           | 00          | 011        | 1           |

| Primary Oscillator (HS)                            | Primary           | 10          | 010        | _           |

| Primary Oscillator (XT)                            | Primary           | 01          | 010        | -           |

| Primary Oscillator (EC)                            | Primary           | 00          | 010        | 1           |

| Fast RC Oscillator with PLL (FRCPLL)               | Internal          | XX          | 001        | 1           |

| Fast RC Oscillator (FRC)                           | Internal          | XX          | 000        | 1           |

**Note 1:** OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

# 9.2 Oscillator Resources

Many useful resources related to Oscillator Configuration are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532315              |

#### 9.2.1 KEY RESOURCES

- Section 39. "Oscillator (Part III)" (DS70216)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

NOTES:

#### **REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)**

- bit 2 Unimplemented: Read as '0'

- bit 1 C1MD: ECAN1 Module Disable bit

- 1 = ECAN1 module is disabled

- 0 = ECAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit

- 1 = ADC1 module is disabled 0 = ADC1 module is enabled

# 11.7 I/O Helpful Tips

- In some cases, certain pins as defined in TABLE 1. 31-9: "DC Characteristics: I/O Pin Input Specifications" under "Injection Current", have internal protection diodes to VDD and VSS. The term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- I/O pins that are shared with any analog input pin, 2. (i.e., ANx), are always analog pins by default after any reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the analog pin configuration registers in the ADC module, (i.e., ADxPCFGL, AD1PCFGH), by setting the appropriate bit that corresponds to that I/O port pin to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-toright. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each CN pin has a configurable internal weak pull-up resistor. The pull-ups act as a current source connected to the pin, and eliminates the need for external resistors in certain applications. The internal pull-up is to ~(VDD-0.8) not VDD. This is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 31.0 "Electrical Characteristics" for additional information.

# 11.8 I/O Resources

Many useful resources related to Resets are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the<br>product page using the link above, enter<br>this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/                                                                                |

|       | Devices.aspx?dDocName=en532315                                                                                       |

#### 11.8.1 KEY RESOURCES

- Section 10. "I/O Ports" (DS70193)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

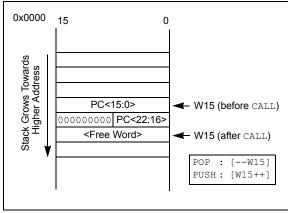

# 15.0 OUTPUT COMPARE

- This data sheet summarizes the features Note 1: of the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 of family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Output Compare" (DS70209) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Output Compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The Output Compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The Output Compare module can also generate interrupts on compare match events.

The Output Compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- · Delayed One-Shot mode

- · Continuous Pulse mode

- PWM mode without fault protection

- · PWM mode with fault protection

### FIGURE 15-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| REGISTER 1                                                                                                                                                                          | 6-8: PXDIC                                                          | ON2: DEAD        | -TIME CON | IROL REGIS       | IER 2(") |                    |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------|-----------|------------------|----------|--------------------|-------|

| U-0                                                                                                                                                                                 | U-0                                                                 | U-0              | U-0       | U-0              | U-0      | U-0                | U-0   |