Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc202-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04 PRODUCT FAMILIES

The device names, pin counts, memory sizes, and peripheral availability of each device are listed in Table 1. The pages that follow show their pinout diagrams.

# TABLE 1:dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04CONTROLLER FAMILIES

|                   |      |                                 |                            |                 |                             |               | Remap                          | pable F                                        | Periphe                         | ral  |     |                    |                                    |      |                   |                      |                                 |                  | Ĵ.                                                  |                                               |          |                        |

|-------------------|------|---------------------------------|----------------------------|-----------------|-----------------------------|---------------|--------------------------------|------------------------------------------------|---------------------------------|------|-----|--------------------|------------------------------------|------|-------------------|----------------------|---------------------------------|------------------|-----------------------------------------------------|-----------------------------------------------|----------|------------------------|

| Device            | Pins | Program Flash Memory<br>(Kbyte) | RAM (Kbyte) <sup>(1)</sup> | Remappable Pins | 16-bit Timer <sup>(2)</sup> | Input Capture | Output Compare<br>Standard PWM | Motor Control PWM<br>(Channels) <sup>(3)</sup> | Quadrature Encoder<br>Interface | UART | SPI | ECAN <sup>TM</sup> | External Interrupts <sup>(4)</sup> | RTCC | I <sup>2</sup> C™ | <b>CRC Generator</b> | 10-bit/12-bit ADC<br>(Channels) | 6-pin 16-bit DAC | Analog Comparator<br>(2 Channels/Voltage Regulator) | 8-bit Parallel Master<br>Port (Address Lines) | I/O Pins | Packages               |

| dsPIC33FJ128MC804 | 44   | 128                             | 16                         | 26              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 1                  | 3                                  | 1    | 1                 | 1                    | 9                               | 1                | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ128MC802 | 28   | 128                             | 16                         | 16              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 1                  | 3                                  | 1    | 1                 | 1                    | 6                               | 0                | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ128MC204 | 44   | 128                             | 8                          | 26              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 0                  | 3                                  | 1    | 1                 | 1                    | 9                               | 0                | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ128MC202 | 28   | 128                             | 8                          | 16              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 0                  | 3                                  | 1    | 1                 | 1                    | 6                               | 0                | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ64MC804  | 44   | 64                              | 16                         | 26              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 1                  | 3                                  | 1    | 1                 | 1                    | 9                               | 1                | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ64MC802  | 28   | 64                              | 16                         | 16              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 1                  | 3                                  | 1    | 1                 | 1                    | 6                               | 0                | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ64MC204  | 44   | 64                              | 8                          | 26              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 0                  | 3                                  | 1    | 1                 | 1                    | 9                               | 0                | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ64MC202  | 28   | 64                              | 8                          | 16              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 0                  | 3                                  | 1    | 1                 | 1                    | 6                               | 0                | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ32MC304  | 44   | 32                              | 4                          | 26              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 0                  | 3                                  | 1    | 1                 | 1                    | 9                               | 0                | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ32MC302  | 28   | 32                              | 4                          | 16              | 5                           | 4             | 4                              | 6, 2                                           | 2                               | 2    | 2   | 0                  | 3                                  | 1    | 1                 | 1                    | 6                               | 0                | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

Note 1: RAM size is inclusive of 2 Kbytes of DMA RAM for all devices except dsPIC33FJ32MC302/304, which include 1 Kbyte of DMA RAM.

2: Only four out of five timers are remappable.

**3:** Only PWM fault pins are remappable.

4: Only two out of three interrupts are remappable.

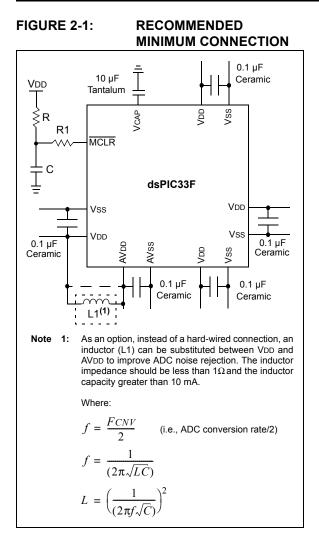

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

#### 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, preferably surface mount connected within one-eights inch of the VCAP pin connected to ground. The type can be ceramic or tantalum. Refer to **Section 31.0** "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to Section 28.2 "On-Chip Voltage Regulator" for details.

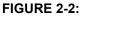

## 2.4 Master Clear (MCLR) Pin

The MCLR pin provides for two specific device functions:

- Device Reset

- Device programming and debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### EXAMPLE OF MCLR PIN CONNECTIONS

2:  $\underline{R1} \leq 470\Omega$  will limit any current flowing into MCLR from the external capacitor C, in the event of MCLR pin breakdown due to Electrostatic Discharge (ESD) or <u>Electrical</u> Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met.

#### 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All effective addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

#### 4.2.6 DMA RAM

Every dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 device contains up to 2 Kbytes of dual ported DMA RAM located at the end of Y data space, and is a part of Y data space. Memory locations in the DMA RAM space are accessible simultaneously by the CPU and the DMA controller module. The DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU.

When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

Note: The DMA RAM can be used for general purpose data storage if the DMA function is not required in an application.

## 4.3 Memory Resources

Many useful resources related to Memory Organization are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

#### 4.3.1 KEY RESOURCES

- Section 4. "Program Memory" (DS70203)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

## dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| <b>REGISTER 5-2</b> | 2: NVMI | KEY: NONVOLA     | ATILE ME | MORY KEY RI       | EGISTER         |                 |       |

|---------------------|---------|------------------|----------|-------------------|-----------------|-----------------|-------|

| U-0                 | U-0     | U-0              | U-0      | U-0               | U-0             | U-0             | U-0   |

| —                   | _       | —                | —        | —                 | —               | —               | —     |

| bit 15              |         |                  |          |                   |                 |                 | bit 8 |

| W-0                 | W-0     | W-0              | W-0      | W-0               | W-0             | W-0             | W-0   |

|                     |         |                  | NVM      | (EY<7:0>          |                 |                 |       |

| bit 7               |         |                  |          |                   |                 |                 | bit 0 |

| Legend:             |         |                  |          |                   |                 |                 |       |

| -                   |         |                  |          |                   |                 |                 |       |

| R = Readable b      | It      | W = Writable b   | It       | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at PC    | )R      | '1' = Bit is set |          | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

| REGISTER 7      | -5: IFS0:     | INTERRUPT                            | FLAG STAT        | US REGIST        | =R 0            |                 |        |

|-----------------|---------------|--------------------------------------|------------------|------------------|-----------------|-----------------|--------|

| U-0             | R/W-0         | R/W-0                                | R/W-0            | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|                 | DMA1IF        | AD1IF                                | U1TXIF           | U1RXIF           | SPI1IF          | SPI1EIF         | T3IF   |

| bit 15          |               |                                      |                  |                  |                 |                 | bit 8  |

| R/W-0           | R/W-0         | R/W-0                                | R/W-0            | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

| T2IF            | OC2IF         | IC2IF                                | DMA0IF           | T1IF             | OC1IF           | IC1IF           | INTOIF |

| bit 7           | 00211         | 10211                                |                  |                  | 00111           |                 | bit C  |

| Legend:         |               |                                      |                  |                  |                 |                 |        |

| R = Readable    | bit           | W = Writable                         | bit              | U = Unimpler     | mented bit, rea | d as '0'        |        |

| -n = Value at F | POR           | '1' = Bit is se                      | t                | '0' = Bit is cle | ared            | x = Bit is unkn | own    |

|                 |               |                                      |                  |                  |                 |                 |        |

| bit 15          | Unimpleme     | nted: Read as                        | '0'              |                  |                 |                 |        |

| bit 14          |               | MA Channel 1 E                       |                  | omplete Interr   | upt Flag Status | s bit           |        |

|                 |               | t request has oc<br>t request has no |                  |                  |                 |                 |        |

| bit 13          | -             | C1 Conversion (                      |                  | unt Eloa Statu   | o hit           |                 |        |

| DIL 13          |               | t request has oc                     | •                | upi riay Sialu   | S DIL           |                 |        |

|                 |               | t request has no                     |                  |                  |                 |                 |        |

| bit 12          | U1TXIF: UA    | RT1 Transmitte                       | r Interrupt Flag | g Status bit     |                 |                 |        |

|                 |               | t request has oc                     |                  |                  |                 |                 |        |

|                 | 0 = Interrupt | t request has no                     | ot occurred      |                  |                 |                 |        |

| bit 11          |               | RT1 Receiver I                       |                  | status bit       |                 |                 |        |

|                 |               | t request has oc                     |                  |                  |                 |                 |        |

| hit 10          | •             | t request has no                     |                  | .:.              |                 |                 |        |

| bit 10          |               | 1 Event Interrup                     | -                | DIT              |                 |                 |        |

|                 |               | t request has oc<br>t request has no |                  |                  |                 |                 |        |

| bit 9           | •             | PI1 Error Interru                    |                  | bit              |                 |                 |        |

|                 | 1 = Interrupt | t request has oc<br>t request has no | curred           |                  |                 |                 |        |

| bit 8           | -             | 3 Interrupt Flag                     |                  |                  |                 |                 |        |

|                 | 1 = Interrupt | t request has oc<br>t request has no | curred           |                  |                 |                 |        |

| bit 7           | -             | 2 Interrupt Flag                     |                  |                  |                 |                 |        |

|                 |               | t request has oc                     |                  |                  |                 |                 |        |

|                 | 0 = Interrupt | t request has no                     | ot occurred      |                  |                 |                 |        |

| bit 6           | OC2IF: Outp   | out Compare Cl                       | nannel 2 Interru | upt Flag Status  | s bit           |                 |        |

|                 |               | t request has oc<br>t request has no |                  |                  |                 |                 |        |

| bit 5           | IC2IF: Input  | Capture Chanr                        | el 2 Interrupt F | lag Status bit   |                 |                 |        |

|                 |               | t request has oc<br>t request has no |                  |                  |                 |                 |        |

| bit 4           | -             | VIA Channel 0 E                      |                  | omplete Interr   | upt Flag Status | s bit           |        |

|                 |               | t request has oc                     |                  |                  |                 |                 |        |

|                 | 0 = Interrupt |                                      |                  |                  |                 |                 |        |

|                 |               | request has he                       |                  |                  |                 |                 |        |

| bit 3           | T1IF: Timer   | 1 Interrupt Flag                     |                  |                  |                 |                 |        |

## REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

#### 10.5 Power-Saving Resources

Many useful resources related to power-saving modes are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

#### 10.5.1 KEY RESOURCES

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| U-0                | U-0                                                      | U-0                                                                          | R/W-1         | R/W-1             | R/W-1            | R/W-1           | R/W-1 |

|--------------------|----------------------------------------------------------|------------------------------------------------------------------------------|---------------|-------------------|------------------|-----------------|-------|

| —                  | _                                                        | _                                                                            |               |                   | QEB1R<4:0>       |                 |       |

| bit 15             | •                                                        |                                                                              |               |                   |                  |                 | bit 8 |

|                    |                                                          |                                                                              |               |                   |                  |                 |       |

| U-0                | U-0                                                      | U-0                                                                          | R/W-1         | R/W-1             | R/W-1            | R/W-1           | R/W-1 |

|                    | —                                                        | —                                                                            |               |                   | QEA1R<4:0>       |                 |       |

| bit 7              |                                                          |                                                                              |               |                   |                  |                 | bit 0 |

|                    |                                                          |                                                                              |               |                   |                  |                 |       |

| Legend:            |                                                          |                                                                              |               |                   |                  |                 |       |

| R = Readabl        | le bit                                                   | W = Writable I                                                               | oit           | U = Unimplen      | nented bit, read | l as '0'        |       |

| -n = Value at      | t POR                                                    | '1' = Bit is set                                                             |               | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|                    |                                                          |                                                                              |               |                   |                  |                 |       |

| bit 15-13          | Unimplemen                                               | ted: Read as '                                                               | )'            |                   |                  |                 |       |

| bit 12-8           | QEB1R<4:0>                                               | : Assign B (QE                                                               | B1) to the co | rresponding pir   | I                |                 |       |

|                    | 11111 <b>= Inp</b> u                                     |                                                                              |               |                   |                  |                 |       |

|                    | 11001 <b>= Inpu</b>                                      | ut tied to RP25                                                              |               |                   |                  |                 |       |

|                    | •                                                        |                                                                              |               |                   |                  |                 |       |

|                    | •                                                        |                                                                              |               |                   |                  |                 |       |

|                    |                                                          |                                                                              |               |                   |                  |                 |       |

|                    | •                                                        |                                                                              |               |                   |                  |                 |       |

|                    | •<br>00001 = Inpu                                        |                                                                              |               |                   |                  |                 |       |

| hit 7 E            | 00000 <b>= Inp</b> u                                     | ut tied to RP0                                                               | \ <b>`</b>    |                   |                  |                 |       |

|                    | 00000 = Inpu<br>Unimplemen                               | ut tied to RP0<br>Ited: Read as '0                                           |               |                   |                  |                 |       |

| bit 7-5<br>bit 4-0 | 00000 = Inpu<br>Unimplemen<br>QEA1R<4:0>                 | ut tied to RP0<br>Ited: Read as '(<br>-: Assign A (QE                        |               | rresponding pir   | 1                |                 |       |

|                    | 00000 = Inpu<br>Unimplemen<br>QEA1R<4:0><br>11111 = Inpu | ut tied to RP0<br><b>Ited:</b> Read as '(<br>Assign A (QE)<br>It tied to Vss |               | rresponding pir   | I                |                 |       |

| bit 7-5<br>bit 4-0 | 00000 = Inpu<br>Unimplemen<br>QEA1R<4:0><br>11111 = Inpu | ut tied to RP0<br>Ited: Read as '(<br>-: Assign A (QE                        |               | rresponding pir   | I                |                 |       |

00001 = Input tied to RP1

00000 = Input tied to RP0

| REGISTER 11-29: | <b>RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8<sup>(1)</sup></b> |

|-----------------|---------------------------------------------------------------------|

|-----------------|---------------------------------------------------------------------|

| bit 7      |     |     |       |       |                    |       | bit ( |

|------------|-----|-----|-------|-------|--------------------|-------|-------|

|            | _   | —   |       |       | RP16R<4:0>         | >     |       |

| U-0        | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0              | R/W-0 | R/W-0 |

| bit 15     |     |     |       |       |                    |       | bit t |

| <br>bit 15 |     |     |       |       | KF17K54.02         | -     | bit 8 |

| U-0        | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0<br>RP17R<4:0 | R/W-0 | R/W-0 |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP17R<4:0>:** Peripheral Output Function is Assigned to RP17 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP16R<4:0>:** Peripheral Output Function is Assigned to RP16 Output Pin bits (see Table 11-2 for peripheral function numbers)

Note 1: This register is implemented in 44-pin devices only.

#### REGISTER 11-30: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9<sup>(1)</sup>

| U-0           | U-0        | U-0                            | R/W-0          | R/W-0                             | R/W-0            | R/W-0             | R/W-0          |

|---------------|------------|--------------------------------|----------------|-----------------------------------|------------------|-------------------|----------------|

| _             | —          | —                              |                |                                   | RP19R<4:0>       |                   |                |

| bit 15        |            |                                |                |                                   |                  |                   | bit 8          |

|               |            |                                | <b>D</b> 444 0 | <b>D</b> 444.0                    | DANA             | <b>DMU</b> O      | <b>D</b> 444.0 |

| U-0           | U-0        | U-0                            | R/W-0          | R/W-0                             | R/W-0            | R/W-0             | R/W-0          |

| —             | —          | —                              |                |                                   | RP18R<4:0>       | 1                 |                |

| bit 7         |            |                                |                |                                   |                  |                   | bit 0          |

|               |            |                                |                |                                   |                  |                   |                |

| Legend:       |            |                                |                |                                   |                  |                   |                |

| R = Readabl   | le bit     | W = Writable                   | bit            | U = Unimpler                      | nented bit, read | d as '0'          |                |

| -n = Value at | POR        | '1' = Bit is set               |                | '0' = Bit is cleared x = Bit is u |                  |                   | nown           |

|               |            |                                |                |                                   |                  |                   |                |

| bit 15-13     | Unimplemen | ted: Read as '                 | 0'             |                                   |                  |                   |                |

| bit 12-8      |            | Peripheral Ou<br>ction numbers | •              | is Assigned to                    | RP19 Output F    | Pin bits (see Tal | ole 11-2 for   |

| bit 7-5       | Unimplemen | ted: Read as '                 | 0'             |                                   |                  |                   |                |

| bit 4-0       |            | Peripheral Ou                  | •              | is Assigned to                    | RP18 Output F    | Pin bits (see Tal | ole 11-2 for   |

Note 1: This register is implemented in 44-pin devices only.

## 12.2 Timer1 Control Register

| R/W-0         | U-0                                       | R/W-0                              | U-0            | U-0              | U-0              | U-0             | U-0 |

|---------------|-------------------------------------------|------------------------------------|----------------|------------------|------------------|-----------------|-----|

| TON           | _                                         | TSIDL                              | _              |                  |                  |                 | —   |

| bit 15        |                                           |                                    |                |                  |                  | 1               | bit |

|               |                                           |                                    |                |                  |                  |                 |     |

| U-0           | R/W-0                                     | R/W-0                              | R/W-0          | U-0              | R/W-0            | R/W-0           | U-0 |

| —             | TGATE                                     | TCKPS                              | S<1:0>         | —                | TSYNC            | TCS             |     |

| bit 7         |                                           |                                    |                |                  |                  |                 | bit |

| Legend:       |                                           |                                    |                |                  |                  |                 |     |

| R = Readable  | e bit                                     | W = Writable                       | bit            | U = Unimple      | mented bit, read | as '0'          |     |

| -n = Value at | POR                                       | '1' = Bit is set                   |                | '0' = Bit is cle | ared             | x = Bit is unkn | own |

|               |                                           |                                    |                |                  |                  |                 |     |

| bit 15        | TON: Timer1                               | On bit                             |                |                  |                  |                 |     |

|               | 1 = Starts 16-                            | bit Timer1                         |                |                  |                  |                 |     |

|               | 0 = Stops 16-                             |                                    |                |                  |                  |                 |     |

| bit 14        | Unimplemen                                | ted: Read as '                     | 0'             |                  |                  |                 |     |

| bit 13        |                                           | n Idle Mode bit                    |                |                  |                  |                 |     |

|               |                                           | ue module ope<br>module operat     |                |                  | lle mode         |                 |     |

| bit 12-7      |                                           | ted: Read as '                     |                | ue               |                  |                 |     |

| bit 6         | -                                         | r1 Gated Time                      |                | a Enabla bit     |                  |                 |     |

|               | When TCS =                                |                                    | Accumulation   |                  |                  |                 |     |

|               | This bit is igno                          |                                    |                |                  |                  |                 |     |

|               | When TCS =                                | 0:                                 |                |                  |                  |                 |     |

|               |                                           | e accumulation                     |                |                  |                  |                 |     |

|               |                                           | e accumulation                     |                | <b>.</b>         |                  |                 |     |

| bit 5-4       |                                           | Timer1 Input (                     | Clock Prescale | e Select bits    |                  |                 |     |

|               | 11 = 1:256<br>10 = 1:64                   |                                    |                |                  |                  |                 |     |

|               | 01 = 1:8                                  |                                    |                |                  |                  |                 |     |

|               | 00 = 1:1                                  |                                    |                |                  |                  |                 |     |

| bit 3         | Unimplemen                                | ted: Read as '                     | 0'             |                  |                  |                 |     |

| bit 2         | TSYNC: Time                               | er1 External Clo                   | ock Input Syn  | chronization S   | elect bit        |                 |     |

|               | $\frac{\text{When TCS}}{1} = \frac{1}{2}$ |                                    |                |                  |                  |                 |     |

|               |                                           | ize external clo<br>nchronize exte |                | ut               |                  |                 |     |

|               | When TCS =                                |                                    |                | at               |                  |                 |     |

|               | This bit is igno                          |                                    |                |                  |                  |                 |     |

| bit 1         | -                                         | Clock Source S                     | Select bit     |                  |                  |                 |     |

|               | 1 = External c<br>0 = Internal cl         | clock from pin T                   | T1CK (on the   | rising edge)     |                  |                 |     |

|               |                                           |                                    |                |                  |                  |                 |     |

## REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

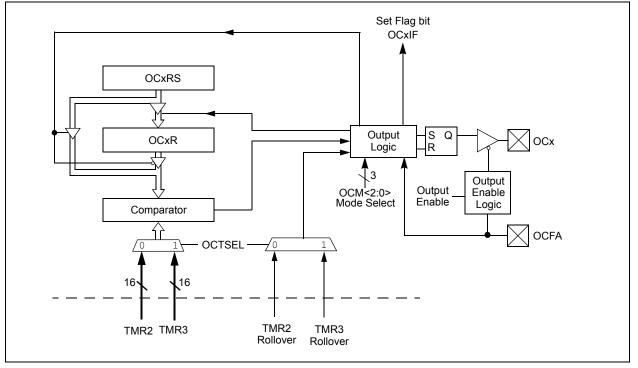

## 15.0 OUTPUT COMPARE

- This data sheet summarizes the features Note 1: of the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 of family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Output Compare" (DS70209) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Output Compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The Output Compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The Output Compare module can also generate interrupts on compare match events.

The Output Compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- · Delayed One-Shot mode

- · Continuous Pulse mode

- PWM mode without fault protection

- · PWM mode with fault protection

#### FIGURE 15-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

## dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| R/W-0                  | R/W-0 | R/W-0            | R/W-0 | R/W-0                  | R/W-0               | R/W-0           | R/W-0 |

|------------------------|-------|------------------|-------|------------------------|---------------------|-----------------|-------|

| SEVTDIR <sup>(1)</sup> |       |                  | 5     | SEVTCMP<14:8           | <sub>&gt;</sub> (2) |                 |       |

| bit 15                 |       |                  |       |                        |                     |                 | bit 8 |

| R/W-0                  | R/W-0 | R/W-0            | R/W-0 | R/W-0                  | R/W-0               | R/W-0           | R/W-0 |

|                        |       |                  | SEVTC | MP<7:0> <sup>(2)</sup> |                     |                 |       |

| bit 7                  |       |                  |       |                        |                     |                 | bit 0 |

| Legend:                |       |                  |       |                        |                     |                 |       |

| R = Readable b         | oit   | W = Writable     | bit   | U = Unimplen           | nented bit, rea     | ad as '0'       |       |

| -n = Value at Po       | OR    | '1' = Bit is set |       | '0' = Bit is cle       | ared                | x = Bit is unkr | nown  |

bit 15SEVTDIR: Special Event Trigger Time Base Direction bit<sup>(1)</sup>1 = A Special Event Trigger occurs when the PWM time base is counting downward0 = A Special Event Trigger occurs when the PWM time base is counting upwardbit 14-0SEVTCMP<14:0>: Special Event Compare Value bits<sup>(2)</sup>

Note 1: This bit is compared with the PTDIR bit (PxTMR<15>) to generate the Special Event Trigger.

2: The PxSECMP<14:0> bits are compared with the PxTMR<14:0> bits to generate the Special Event Trigger.

| U-0                                | U-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                               | R/W-0                                                                                                                               | R/W-0                                                                                                 | R/W-0           | R/W-0    |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------|----------|

| _                                  | _                                                                                                                                                                                                                                                                                                                                      | FAOV3H                                                                                                                                                                                                             | FAOV3L                                                                                                                                                                                                              | FAOV2H                                                                                                                              | FAOV2L                                                                                                | FAOV1H          | FAOV1L   |

| bit 15                             |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                                                                                                                                                                                                     | 1                                                                                                                                   |                                                                                                       |                 | bit 8    |

|                                    |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                                                                                                                                                                                                     |                                                                                                                                     |                                                                                                       |                 |          |

| R/W-0                              | U-0                                                                                                                                                                                                                                                                                                                                    | U-0                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                 | U-0                                                                                                                                 | R/W-0                                                                                                 | R/W-0           | R/W-0    |

| FLTAM                              | —                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                  | —                                                                                                                                                                                                                   | —                                                                                                                                   | FAEN3                                                                                                 | FAEN2           | FAEN1    |

| bit 7                              |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                                                                                                                                                                                                     |                                                                                                                                     |                                                                                                       |                 | bit      |

| Legend:                            |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                                                                                                                                                                                                     |                                                                                                                                     |                                                                                                       |                 |          |

| R = Readab                         | le bit                                                                                                                                                                                                                                                                                                                                 | W = Writable                                                                                                                                                                                                       | bit                                                                                                                                                                                                                 | U = Unimpler                                                                                                                        | nented bit, rea                                                                                       | d as '0'        |          |

| -n = Value a                       | t POR                                                                                                                                                                                                                                                                                                                                  | '1' = Bit is set                                                                                                                                                                                                   |                                                                                                                                                                                                                     | '0' = Bit is cle                                                                                                                    | ared                                                                                                  | x = Bit is unkr | iown     |

|                                    |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                                                                                                                                                                                                     |                                                                                                                                     |                                                                                                       |                 |          |

| bit 15-14                          | Unimplemen                                                                                                                                                                                                                                                                                                                             | ted: Read as '                                                                                                                                                                                                     | 0'                                                                                                                                                                                                                  |                                                                                                                                     |                                                                                                       |                 |          |

| bit 13-8                           | EA OV/vUz214                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                    |                                                                                                                                                                                                                     |                                                                                                                                     |                                                                                                       |                 |          |

|                                    |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                                                                                                                                                                                                     | t A PWM Over                                                                                                                        |                                                                                                       |                 |          |

| 2.0 0                              | 1 = The PWN                                                                                                                                                                                                                                                                                                                            | l output pin is c                                                                                                                                                                                                  | lriven active c                                                                                                                                                                                                     | it A PWM Over<br>on an external F<br>on an external                                                                                 | ault input eve                                                                                        |                 |          |

| bit 7                              | 1 = The PWN                                                                                                                                                                                                                                                                                                                            | l output pin is c<br>l output pin is c                                                                                                                                                                             | lriven active c                                                                                                                                                                                                     | on an external F                                                                                                                    | ault input eve                                                                                        |                 |          |

|                                    | 1 = The PWN<br>0 = The PWM<br><b>FLTAM:</b> Fault<br>1 = The Fault                                                                                                                                                                                                                                                                     | l output pin is c<br>l output pin is c<br>: A Mode bit<br>A input pin fur                                                                                                                                          | driven active of<br>driven inactive<br>actions in the o                                                                                                                                                             | on an external F<br>on an external<br>Cycle-by-Cycle                                                                                | Fault input eve<br>I Fault input ev<br>mode                                                           |                 | ON<13:8> |

| bit 7                              | 1 = The PWN<br>0 = The PWM<br><b>FLTAM:</b> Fault<br>1 = The Fault<br>0 = The Fault                                                                                                                                                                                                                                                    | l output pin is c<br>l output pin is c<br>: A Mode bit<br>A input pin fur                                                                                                                                          | Iriven active of<br>Iriven inactive<br>Inctions in the of<br>Iches all contro                                                                                                                                       | on an external F<br>on an external<br>Cycle-by-Cycle                                                                                | Fault input eve<br>I Fault input ev<br>mode                                                           | rent            | ON<13:8> |

|                                    | 1 = The PWM<br>0 = The PWM<br><b>FLTAM:</b> Fault<br>1 = The Fault<br>0 = The Fault<br><b>Unimplemen</b>                                                                                                                                                                                                                               | l output pin is c<br>l output pin is c<br>A Mode bit<br>A input pin fur<br>A input pin late                                                                                                                        | driven active of<br>driven inactive<br>actions in the of<br>ches all contro                                                                                                                                         | on an external F<br>on an external<br>Cycle-by-Cycle                                                                                | Fault input eve<br>I Fault input ev<br>mode                                                           | rent            | ON<13:8> |

| bit 7<br>bit 6-3                   | 1 = The PWM<br>0 = The PWM<br>FLTAM: Fault<br>1 = The Fault<br>0 = The Fault<br>Unimplemen<br>FAEN3: Fault                                                                                                                                                                                                                             | l output pin is c<br>l output pin is c<br>A Mode bit<br>A input pin fur<br>A input pin lato<br>ted: Read as f<br>Input A Enable                                                                                    | driven active of<br>driven inactive<br>notions in the of<br>ches all contro<br>0'<br>e bit                                                                                                                          | on an external F<br>on an external<br>Cycle-by-Cycle                                                                                | ault input eve<br>I Fault input ev<br>mode<br>ogrammed sta                                            | rent            | ON<13:8> |

| bit 7<br>bit 6-3                   | <ol> <li>1 = The PWM</li> <li>0 = The PWM</li> <li>FLTAM: Fault</li> <li>1 = The Fault</li> <li>0 = The Fault</li> <li>Unimplemen</li> <li>FAEN3: Fault</li> <li>1 = PWMxH3</li> </ol>                                                                                                                                                 | l output pin is c<br>l output pin is c<br>A Mode bit<br>A input pin fur<br>A input pin late<br><b>ted:</b> Read as '<br>Input A Enable<br>/PWMxL3 pin p                                                            | driven active of<br>driven inactive<br>notions in the<br>ches all contro<br>0'<br>e bit<br>pair is controllo                                                                                                        | on an external F<br>on an external<br>Cycle-by-Cycle<br>ol pins to the pr                                                           | ault input eve<br>I Fault input ev<br>mode<br>ogrammed sta<br>ut A                                    | rent            | ON<13:8> |

| bit 7<br>bit 6-3<br>bit 2          | 1 = The PWM<br>0 = The PWM<br><b>FLTAM:</b> Fault<br>1 = The Fault<br>0 = The Fault<br><b>Unimplemen</b><br><b>FAEN3:</b> Fault<br>1 = PWMxH3<br>0 = PWMxH3<br>FAEN2: Fault                                                                                                                                                            | l output pin is c<br>l output pin is c<br>A Mode bit<br>A input pin fur<br>A input pin lat<br><b>ted:</b> Read as f<br>Input A Enable<br>/PWMxL3 pin p<br>Input A Enable                                           | driven active of<br>driven inactive<br>octions in the o<br>ches all contro<br>o'<br>e bit<br>pair is controllo<br>pair is not con<br>e bit                                                                          | on an external F<br>on an external<br>Cycle-by-Cycle<br>of pins to the pr<br>ed by Fault Inp<br>trolled by Fault                    | Fault input eve<br>I Fault input ev<br>mode<br>ogrammed sta<br>ut A<br>Input A                        | rent            | ON<13:8> |

| bit 7<br>bit 6-3<br>bit 2          | <ul> <li>1 = The PWM</li> <li>0 = The PWM</li> <li>FLTAM: Fault</li> <li>1 = The Fault</li> <li>0 = The Fault</li> <li>Unimplemen</li> <li>FAEN3: Fault</li> <li>1 = PWMxH3</li> <li>0 = PWMxH3</li> <li>FAEN2: Fault</li> <li>1 = PWMxH2</li> </ul>                                                                                   | l output pin is c<br>l output pin is c<br>A Mode bit<br>A input pin fur<br>A input pin lat<br>ted: Read as<br>Input A Enable<br>/PWMxL3 pin p<br>Input A Enable<br>/PWMxL2 pin p                                   | driven active of<br>driven inactive<br>actions in the of<br>ches all contro<br>o'<br>e bit<br>pair is controllo<br>pair is not con<br>e bit<br>pair is controllo                                                    | on an external F<br>on an external<br>Cycle-by-Cycle<br>of pins to the pr<br>ed by Fault Inp                                        | Fault input eve<br>I Fault input ev<br>mode<br>ogrammed sta<br>ut A<br>Input A<br>ut A                | rent            | ON<13:8> |

| bit 7<br>bit 6-3<br>bit 2<br>bit 1 | <ol> <li>1 = The PWM</li> <li>0 = The PWM</li> <li>FLTAM: Fault</li> <li>1 = The Fault</li> <li>0 = The Fault</li> <li>Unimplemen</li> <li>FAEN3: Fault</li> <li>1 = PWMxH3</li> <li>0 = PWMxH3</li> <li>FAEN2: Fault</li> <li>1 = PWMxH2</li> <li>0 = PWMxH2</li> <li>0 = PWMxH2</li> </ol>                                           | l output pin is c<br>l output pin is c<br>A Mode bit<br>A input pin fur<br>A input pin lat<br>ted: Read as<br>Input A Enable<br>/PWMxL3 pin p<br>Input A Enable<br>/PWMxL2 pin p                                   | driven active of<br>driven inactive<br>octions in the<br>ches all contro<br>o'<br>e bit<br>pair is controllo<br>pair is controllo<br>pair is controllo<br>pair is not con                                           | on an external F<br>on an external<br>Cycle-by-Cycle<br>of pins to the pr<br>ed by Fault Inp<br>trolled by Fault<br>ed by Fault Inp | Fault input eve<br>I Fault input ev<br>mode<br>ogrammed sta<br>ut A<br>Input A<br>ut A                | rent            | ON<13:8> |

| bit 7<br>bit 6-3                   | <ul> <li>1 = The PWW</li> <li>0 = The PWW</li> <li>FLTAM: Fault</li> <li>1 = The Fault</li> <li>0 = The Fault</li> <li>Unimplemen</li> <li>FAEN3: Fault</li> <li>1 = PWMxH3</li> <li>0 = PWMxH3</li> <li>FAEN2: Fault</li> <li>1 = PWMxH2</li> <li>0 = PWMxH2</li> <li>0 = PWMxH2</li> <li>FAEN1: Fault</li> <li>1 = PWMxH1</li> </ul> | I output pin is o<br>output pin is o<br>A Mode bit<br>A input pin fur<br>A input pin lato<br>ted: Read as f<br>Input A Enable<br>/PWMxL3 pin p<br>/PWMxL2 pin p<br>/PWMxL2 pin p<br>/PWMxL2 pin p<br>/PWMxL2 pin p | driven active of<br>driven inactive<br>actions in the<br>ches all contro<br>o'<br>e bit<br>pair is controll<br>pair is not con<br>e bit<br>pair is controll<br>pair is not con<br>e bit<br>pair is not con<br>e bit | on an external F<br>on an external<br>Cycle-by-Cycle<br>of pins to the pr<br>ed by Fault Inp<br>trolled by Fault<br>ed by Fault Inp | Fault input eve<br>I Fault input eve<br>mode<br>ogrammed sta<br>ut A<br>Input A<br>Input A<br>Input A | rent            | ON<13:8> |

## REGISTER 16-9: PxFLTACON: FAULT A CONTROL REGISTER<sup>(1)</sup>

Note 1: PWM2 supports only one PWM I/O pin pair.

## 21.5 ECAN Control Registers

| U-0          | U-0                                                        | R/W-0                                                                                                                      | R/W-0      | r-0                    | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|--------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------|------------------------|-----------------|-----------------|-------|--|--|--|--|

|              | —                                                          | CSIDL                                                                                                                      | ABAT       |                        |                 | REQOP<2:0>      |       |  |  |  |  |

| bit 15       |                                                            |                                                                                                                            |            |                        |                 |                 | bit 8 |  |  |  |  |

| R-1          | R-0                                                        | R-0                                                                                                                        | U-0        | R/W-0                  | U-0             | U-0             | R/W-0 |  |  |  |  |

|              | OPMODE<2:0>                                                | •                                                                                                                          | _          | CANCAP                 | _               | _               | WIN   |  |  |  |  |

| bit 7        |                                                            |                                                                                                                            |            |                        |                 |                 | bit C |  |  |  |  |

| Legend:      |                                                            | r = Bit is Res                                                                                                             | erved      |                        |                 |                 |       |  |  |  |  |

| R = Readab   | ole bit                                                    | W = Writable                                                                                                               | bit        | U = Unimpler           | mented bit, rea | d as '0'        |       |  |  |  |  |