Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

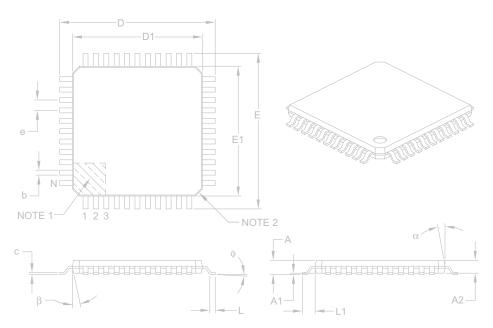

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc204-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33F/PIC24H Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

- Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33FJ64MC804 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory" (DS70202)

- Section 4. "Program Memory" (DS70202)

- Section 5. "Flash Programming" (DS70191)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer and Power-saving Modes" (DS70196)

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

- Section 14. "Motor Control PWM" (DS70187)

- Section 15. "Quadrature Encoder Interface (QEI)" (DS70208)

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Section 17. "UART" (DS70188)

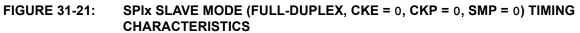

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

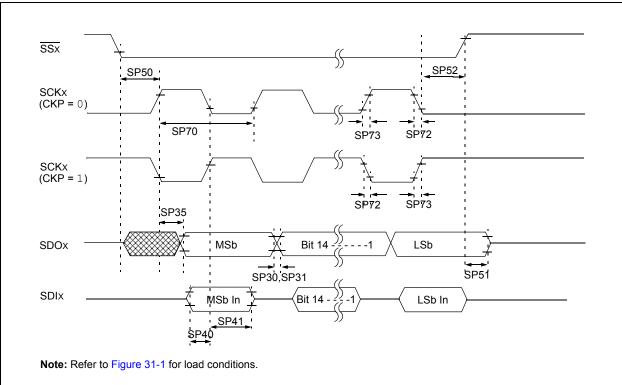

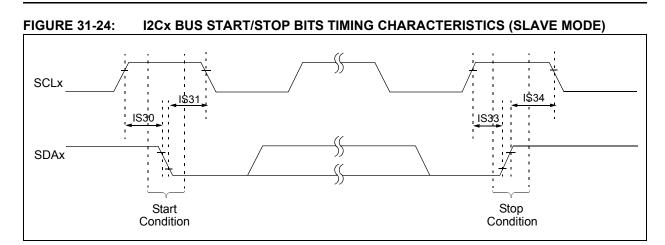

- Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- Section 20. "Data Converter Interface (DCI)" (DS70288)

- Section 23. "CodeGuard™ Security" (DS70199)

- Section 24. "Programming and Diagnostics" (DS70207)

- Section 25. "Device Configuration" (DS70194)

- Section 30. "I/O Ports with Peripheral Pin Select (PPS)" (DS70190)

- Section 32. "Interrupts (Part III)" (DS70214)

- Section 33. "Audio Digital-to-Analog Converter (DAC)" (DS70211)

- Section 34. "Comparator" (DS70212)

- Section 35. "Parallel Master Port (PMP)" (DS70299)

- Section 36. "Programmable Cyclic Redundancy Check (CRC)" (DS70298)

- Section 37. "Real-Time Clock and Calendar (RTCC)" (DS70301)

- Section 38. "Direct Memory Access" (DS70215)

- · Section 39. "Oscillator (Part III)" (DS70216)

# 3.6 CPU Control Registers

|                      | NO-1. OK. O                                                                                                                                                                                                                                                            |                                        |                   |                        |                   |                   |                |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------|------------------------|-------------------|-------------------|----------------|--|

| R-0                  | R-0                                                                                                                                                                                                                                                                    | R/C-0                                  | R/C-0             | R-0                    | R/C-0             | R -0              | R/W-0          |  |

| OA                   | OB                                                                                                                                                                                                                                                                     | SA <sup>(1)</sup>                      | SB <sup>(1)</sup> | OAB                    | SAB               | DA                | DC             |  |

| bit 15               |                                                                                                                                                                                                                                                                        |                                        |                   |                        |                   |                   | bit 8          |  |

| (0)                  | (0)                                                                                                                                                                                                                                                                    | (0)                                    |                   |                        |                   |                   |                |  |

| R/W-0 <sup>(3)</sup> |                                                                                                                                                                                                                                                                        | R/W-0 <sup>(3)</sup>                   | R-0               | R/W-0                  | R/W-0             | R/W-0             | R/W-0          |  |

|                      | IPL<2:0> <sup>(2)</sup>                                                                                                                                                                                                                                                |                                        | RA                | N                      | OV                | Z                 | С              |  |

| bit 7                |                                                                                                                                                                                                                                                                        |                                        |                   |                        |                   |                   | bit 0          |  |

| Legend:              |                                                                                                                                                                                                                                                                        |                                        |                   |                        |                   |                   |                |  |

| C = Clear o          | nly bit                                                                                                                                                                                                                                                                | R = Readable                           | e bit             | U = Unimplei           | mented bit, read  | l as '0'          |                |  |

| S = Set only         | y bit                                                                                                                                                                                                                                                                  | W = Writable                           | bit               | -n = Value at          | POR               |                   |                |  |

| '1' = Bit is s       | et                                                                                                                                                                                                                                                                     | '0' = Bit is clea                      | ared              | x = Bit is unk         | nown              |                   |                |  |

|                      |                                                                                                                                                                                                                                                                        |                                        |                   |                        |                   |                   |                |  |

| bit 15               | OA: Accumul                                                                                                                                                                                                                                                            | ator A Overflow                        | v Status bit      |                        |                   |                   |                |  |

|                      |                                                                                                                                                                                                                                                                        | ator A overflowe                       |                   |                        |                   |                   |                |  |

|                      |                                                                                                                                                                                                                                                                        | ator A has not c                       |                   |                        |                   |                   |                |  |

| bit 14               |                                                                                                                                                                                                                                                                        | ator B Overflow                        |                   |                        |                   |                   |                |  |

|                      |                                                                                                                                                                                                                                                                        | ator B overflowe<br>ator B has not c   |                   |                        |                   |                   |                |  |

| bit 13               |                                                                                                                                                                                                                                                                        | ator A Saturatio                       |                   | tus hit(1)             |                   |                   |                |  |

|                      |                                                                                                                                                                                                                                                                        | ator A is saturat                      |                   |                        | some time         |                   |                |  |

|                      | 0 = Accumula                                                                                                                                                                                                                                                           | ator A is not sat                      | turated           |                        |                   |                   |                |  |

| bit 12               | SB: Accumul                                                                                                                                                                                                                                                            | ator B Saturatio                       | on 'Sticky' Sta   | tus bit <sup>(1)</sup> |                   |                   |                |  |

|                      |                                                                                                                                                                                                                                                                        | ator B is saturat<br>ator B is not sat |                   | en saturated at        | some time         |                   |                |  |

| bit 11               | <b>0AB:</b> 0A    0                                                                                                                                                                                                                                                    | B Combined A                           | ccumulator C      | verflow Status         | bit               |                   |                |  |

|                      |                                                                                                                                                                                                                                                                        | ators A or B hav<br>ccumulators A      |                   |                        |                   |                   |                |  |

| bit 10               | <b>SAB:</b> SA    S                                                                                                                                                                                                                                                    | B Combined A                           | ccumulator (S     | ticky) Status bi       | t <sup>(4)</sup>  |                   |                |  |

|                      | 1 = Accumula                                                                                                                                                                                                                                                           |                                        | saturated or      | have been sat          | urated at some    | time in the past  | :              |  |

| bit 9                | DA: DO Loop                                                                                                                                                                                                                                                            | Active bit                             |                   |                        |                   |                   |                |  |

|                      | 1 = DO loop ir                                                                                                                                                                                                                                                         |                                        |                   |                        |                   |                   |                |  |

|                      | -                                                                                                                                                                                                                                                                      | ot in progress                         |                   |                        |                   |                   |                |  |

| bit 8                |                                                                                                                                                                                                                                                                        | U Half Carry/Bo                        |                   |                        |                   |                   |                |  |

|                      |                                                                                                                                                                                                                                                                        | out from the 4th sult occurred         | low-order bit (   | for byte-sized of      | data) or 8th low- | order bit (for wo | rd-sized data) |  |

|                      | 0 = No carry                                                                                                                                                                                                                                                           |                                        |                   | bit (for byte-siz      | ed data) or 8th   | low-order bit (f  | or word-sized  |  |

| Note 1:              | This bit can be rea                                                                                                                                                                                                                                                    | ad or cleared (n                       | ot set).          |                        |                   |                   |                |  |

| <b>2:</b> 1          | This bit can be read or cleared (not set).<br>The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority<br>evel. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when<br>PL<3> = 1. |                                        |                   |                        |                   |                   |                |  |

# REGISTER 3-1: SR: CPU STATUS REGISTER

3: The IPL<2:0> Status bits are read only when the NSTDIS bit (INTCON1<15>) = 1.

4: This bit can be read or cleared (not set). Clearing this bit clears SA and SB.

| REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2 |                                                                                                        |                                                   |                  |                     |                       |                |         |  |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------|---------------------|-----------------------|----------------|---------|--|--|--|--|

| U-0                                                  | R/W-0                                                                                                  | R/W-0                                             | U-0              | U-0                 | U-0                   | U-0            | U-0     |  |  |  |  |

|                                                      | DMA4IF                                                                                                 | PMPIF                                             |                  | —                   |                       | _              | _       |  |  |  |  |

| bit 15                                               |                                                                                                        |                                                   |                  |                     |                       |                | bit     |  |  |  |  |

| U-0                                                  | U-0                                                                                                    | U-0                                               | R/W-0            | R/W-0               | R/W-0                 | R/W-0          | R/W-0   |  |  |  |  |

|                                                      | _                                                                                                      | _                                                 | DMA3IF           | C1IF <sup>(1)</sup> | C1RXIF <sup>(1)</sup> | SPI2IF         | SPI2EIF |  |  |  |  |

| bit 7                                                |                                                                                                        |                                                   |                  |                     |                       |                | bit     |  |  |  |  |

| Legend:                                              |                                                                                                        |                                                   |                  |                     |                       |                |         |  |  |  |  |

| R = Readab                                           | le bit                                                                                                 | W = Writable                                      | bit              | U = Unimplei        | mented bit, read      | as '0'         |         |  |  |  |  |

| -n = Value a                                         | t POR                                                                                                  | '1' = Bit is se                                   | t                | '0' = Bit is cle    | eared                 | x = Bit is unk | nown    |  |  |  |  |

| bit 14                                               | 1 = Interrupt                                                                                          | A Channel 4 E<br>request has oc<br>request has no | curred           | Complete Interr     | rupt Flag Status I    | bit            |         |  |  |  |  |

|                                                      | •                                                                                                      | •                                                 |                  |                     |                       |                |         |  |  |  |  |

| bit 13                                               |                                                                                                        |                                                   | t Interrupt Flag | Status bit          |                       |                |         |  |  |  |  |

|                                                      |                                                                                                        | request has ou<br>request has no                  |                  |                     |                       |                |         |  |  |  |  |

| bit 12-5                                             | •                                                                                                      | ted: Read as                                      |                  |                     |                       |                |         |  |  |  |  |

| bit 4                                                | DMA3IF: DM                                                                                             | A Channel 3 E                                     | Data Transfer C  | Complete Interr     | rupt Flag Status I    | oit            |         |  |  |  |  |

|                                                      |                                                                                                        | request has or                                    |                  |                     |                       |                |         |  |  |  |  |

|                                                      | •                                                                                                      | request has no                                    |                  | (4)                 |                       |                |         |  |  |  |  |

| bit 3                                                |                                                                                                        |                                                   | pt Flag Status   | bit <sup>(1)</sup>  |                       |                |         |  |  |  |  |

|                                                      | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                                   |                  |                     |                       |                |         |  |  |  |  |

| bit 2                                                | •                                                                                                      | •                                                 | Data Ready Inte  | errupt Flag Sta     | itus bit(1)           |                |         |  |  |  |  |

| 5112                                                 |                                                                                                        | request has or                                    |                  | on up thing out     |                       |                |         |  |  |  |  |

|                                                      | 0 = Interrupt request has not occurred                                                                 |                                                   |                  |                     |                       |                |         |  |  |  |  |

| bit 1                                                | SPI2IF: SPI2                                                                                           | Event Interrup                                    | ot Flag Status b | pit                 |                       |                |         |  |  |  |  |

|                                                      |                                                                                                        | request has or                                    |                  |                     |                       |                |         |  |  |  |  |

| <b>h</b> # 0                                         | •                                                                                                      | request has no                                    |                  | L:4                 |                       |                |         |  |  |  |  |

| bit 0                                                |                                                                                                        | 2 Error Interru<br>request has or                 | pt Flag Status   | JIQ                 |                       |                |         |  |  |  |  |

|                                                      |                                                                                                        | request has our                                   |                  |                     |                       |                |         |  |  |  |  |

|                                                      |                                                                                                        |                                                   |                  |                     |                       |                |         |  |  |  |  |

# REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

Note 1: Interrupts are disabled on devices without an ECAN<sup>™</sup> module.

| U-0          | R/W-1                                                                                                                             | R/W-0                                  | R/W-0 | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------|------------------|-----------------|-----------------|-------|--|--|--|--|

| _            |                                                                                                                                   | U2TXIP<2:0>                            |       | —                |                 | U2RXIP<2:0>     |       |  |  |  |  |

| bit 15       |                                                                                                                                   |                                        |       |                  |                 |                 | bit 8 |  |  |  |  |

| U-0          | R/W-1                                                                                                                             | R/W-0                                  | R/W-0 | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

| _            |                                                                                                                                   | INT2IP<2:0>                            |       | _                |                 | T5IP<2:0>       |       |  |  |  |  |

| bit 7        |                                                                                                                                   |                                        |       |                  |                 |                 | bit C |  |  |  |  |

| Legend:      |                                                                                                                                   |                                        |       |                  |                 |                 |       |  |  |  |  |

| R = Readab   | le bit                                                                                                                            | W = Writable                           | bit   | U = Unimple      | mented bit, rea | d as '0'        |       |  |  |  |  |

| -n = Value a | It POR                                                                                                                            | '1' = Bit is set                       |       | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |  |  |  |  |

| hit 1E       | Unimplomo                                                                                                                         | nted: Dood oo '                        | o'    |                  |                 |                 |       |  |  |  |  |

| bit 15       | -                                                                                                                                 | nted: Read as '                        |       |                  |                 |                 |       |  |  |  |  |

| bit 14-12    | <b>U2TXIP&lt;2:0&gt;:</b> UART2 Transmitter Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                        |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                 |                                        |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                 |                                        |       |                  |                 |                 |       |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                                                                                                |                                        |       |                  |                 |                 |       |  |  |  |  |

|              |                                                                                                                                   | upt is priority if                     | abled |                  |                 |                 |       |  |  |  |  |

| bit 11       |                                                                                                                                   | nted: Read as '                        |       |                  |                 |                 |       |  |  |  |  |

| bit 10-8     | -                                                                                                                                 |                                        |       | Priority bits    |                 |                 |       |  |  |  |  |

|              | <b>U2RXIP&lt;2:0&gt;:</b> UART2 Receiver Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)    |                                        |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                 |                                        |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                 | •                                      |       |                  |                 |                 |       |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                                                                                                |                                        |       |                  |                 |                 |       |  |  |  |  |

|              |                                                                                                                                   | upt is priority if                     | abled |                  |                 |                 |       |  |  |  |  |

| bit 7        |                                                                                                                                   | nted: Read as '                        |       |                  |                 |                 |       |  |  |  |  |

| bit 6-4      | -                                                                                                                                 |                                        |       | hits             |                 |                 |       |  |  |  |  |

|              | INT2IP<2:0>: External Interrupt 2 Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                     |                                        |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                 | -prio piioiii) i (                     |       | .,               |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                 |                                        |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                 | unt in uniquity d                      |       |                  |                 |                 |       |  |  |  |  |

|              |                                                                                                                                   | upt is priority 1<br>upt source is dis | abled |                  |                 |                 |       |  |  |  |  |

| bit 3        |                                                                                                                                   | nted: Read as '                        |       |                  |                 |                 |       |  |  |  |  |

| bit 2-0      | -                                                                                                                                 | Timer5 Interrupt                       |       |                  |                 |                 |       |  |  |  |  |

|              |                                                                                                                                   |                                        | -     | ty interrunt)    |                 |                 |       |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                        |                                        |       |                  |                 |                 |       |  |  |  |  |

• • 001 = Interrupt is priority 1

000 = Interrupt source is disabled

© 2007-2012 Microchip Technology Inc.

NOTES:

## 11.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See **"Pin Diagrams**" for the available pins and their functionality.

## 11.3 Configuring Analog Port Pins

The AD1PCFGL and TRIS registers control the operation of the analog-to-digital port pins. The port pins that are to function as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

The AD1PCFGL register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

### 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be an NOP, as shown in Example 11-1.

# 11.5 Input Change Notification

The input change notification function of the I/O ports allows the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/ X04 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 21 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a change-ofstate.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on change notification pins should always be disabled when the port pin is configured as a digital output.

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | OxFFOO, WO | ; | Configure PORTB<15:8> as inputs |

|------|------------|---|---------------------------------|

| MOV  | W0, TRISBB | ; | and PORTB<7:0> as outputs       |

| NOP  |            | ; | Delay 1 cycle                   |

| btss | PORTB, #13 | ; | Next Instruction                |

|      |            |   |                                 |

# 11.7 I/O Helpful Tips

- In some cases, certain pins as defined in TABLE 1. 31-9: "DC Characteristics: I/O Pin Input Specifications" under "Injection Current", have internal protection diodes to VDD and VSS. The term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- I/O pins that are shared with any analog input pin, 2. (i.e., ANx), are always analog pins by default after any reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the analog pin configuration registers in the ADC module, (i.e., ADxPCFGL, AD1PCFGH), by setting the appropriate bit that corresponds to that I/O port pin to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-toright. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each CN pin has a configurable internal weak pull-up resistor. The pull-ups act as a current source connected to the pin, and eliminates the need for external resistors in certain applications. The internal pull-up is to ~(VDD-0.8) not VDD. This is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 31.0 "Electrical Characteristics" for additional information.

# 11.8 I/O Resources

Many useful resources related to Resets are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the<br>product page using the link above, enter<br>this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/                                                                                |

|       | Devices.aspx?dDocName=en532315                                                                                       |

## 11.8.1 KEY RESOURCES

- Section 10. "I/O Ports" (DS70193)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# 17.2 **QEI Control Registers**

| R/W-0                 | U-0                            | R/W-0             | R-0                       | R/W-0               | R/W-0             | R/W-0           | R/W-0          |

|-----------------------|--------------------------------|-------------------|---------------------------|---------------------|-------------------|-----------------|----------------|

| CNTERR <sup>(1)</sup> | _                              | QEISIDL           | INDEX                     | UPDN <sup>(2)</sup> |                   | QEIM<2:0>       |                |

| bit 15                |                                |                   |                           |                     |                   |                 | bit            |

|                       |                                |                   |                           |                     |                   |                 |                |

| R/W-0                 | R/W-0                          | R/W-0             | R/W-0                     | R/W-0               | R/W-0             | R/W-0           | R/W-0          |

| SWPAB                 | PCDOUT                         | TQGATE            | TQCK                      | PS<1:0>             | POSRES            | TQCS            | UPDN_SR        |

| bit 7                 |                                |                   |                           |                     |                   |                 | bit            |

| Legend:               |                                |                   |                           |                     |                   |                 |                |

| R = Readable          | bit                            | W = Writable      | bit                       | U = Unimple         | mented bit, read  | l as '0'        |                |

| -n = Value at f       | POR                            | '1' = Bit is set  |                           | '0' = Bit is cle    |                   | x = Bit is unl  | known          |

|                       |                                |                   |                           | 0 Dicio dic         |                   | X Ditio uni     |                |

| bit 15                | CNTERR: Co                     | ount Error Statu  | s Flag bit <sup>(1)</sup> |                     |                   |                 |                |

|                       | 1 = Position of                | count error has   | occurred                  |                     |                   |                 |                |

|                       | 0 = No positio                 | on count error h  | nas occurred              |                     |                   |                 |                |

| bit 14                | Unimplemen                     | nted: Read as '   | 0'                        |                     |                   |                 |                |

| bit 13                |                                | op in Idle Mode   |                           |                     |                   |                 |                |

|                       |                                | ue module ope     |                           |                     | lle mode          |                 |                |

|                       |                                | module operat     |                           |                     |                   |                 |                |

| bit 12                |                                | k Pin State Stat  | us bit (read-o            | nly)                |                   |                 |                |

|                       | 1 = Index pin<br>0 = Index pin | U U               |                           |                     |                   |                 |                |

| bit 11                |                                | ion Counter Dir   | ection Status             | bit(2)              |                   |                 |                |

| 2                     |                                | Counter Direction |                           |                     |                   |                 |                |

|                       |                                | Counter Direction |                           |                     |                   |                 |                |

| bit 10-8              | QEIM<2:0>:                     | Quadrature En     | coder Interfac            | e Mode Select       | bits              |                 |                |

|                       |                                |                   | Interface enal            | oled (x4 mode)      | with position co  | ounter reset by | y match        |

|                       | (MAXx)                         | ,                 | Interface enal            | oled (v4 mode)      | with Index Puls   | e reset of nos  | sition counter |

|                       |                                |                   |                           |                     | with position co  |                 |                |

|                       | (MAXx                          |                   |                           | ,                   |                   |                 |                |

|                       |                                |                   |                           | oled (x2 mode)      | with Index Puls   | e reset of pos  | sition counter |

|                       |                                | d (Module disa    | ,                         |                     |                   |                 |                |

|                       | 010 = Onuse<br>001 = Starts    | d (Module disa    | bied)                     |                     |                   |                 |                |

|                       |                                | ature Encoder     | Interface/Time            | er off              |                   |                 |                |

| bit 7                 |                                | ase A and Phas    |                           |                     |                   |                 |                |

|                       |                                | and Phase B ir    | •                         | •                   |                   |                 |                |

|                       |                                | and Phase B ir    |                           |                     |                   |                 |                |

| bit 6                 |                                | sition Counter    |                           | •                   | le bit            |                 |                |

|                       |                                |                   |                           | -                   | El logic controls | state of I/O p  | in)            |

|                       |                                |                   |                           |                     | Normal I/O pin c  |                 | ,              |

| Note 1: Thi           | s bit only applie              | es when OFIM      | < <b>2·0&gt; =</b> '110'  | <b>or</b> '100'     |                   |                 |                |

|                       | • • • •                        |                   |                           |                     | QEIM<2:0> = '(    | 01'             |                |

|                       | escaler utilized f             |                   |                           |                     |                   |                 |                |

|                       | is bit applies on              |                   | -                         | <b>r</b> 110.       |                   |                 |                |

|                       | en configured f                | -                 |                           |                     | <b>`</b>          |                 |                |

| J. VVI                |                                |                   |                           |                     |                   |                 |                |

REGISTER 17-1: QEIxCON: QEIx CONTROL REGISTER (x = 1 or 2)

5: When configured for QEI mode, this control bit is a 'don't care'.

# 20.1 UART Helpful Tips

- 1. In multi-node direct-connect UART networks, UART receive inputs react the to complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

### 20.2 UART Resources

Many useful resources related to UART are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532315              |

### 20.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### REGISTER 22-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

```

bit 4-0 CH0SA<4:0>: Channel 0 Positive Input Select for Sample A bits

dsPIC33FJ32MC304, dsPIC33FJ64MC204/804 and dsPIC33FJ128MC204/804 devices only:

01000 = Channel 0 positive input is AN8

.

00010 = Channel 0 positive input is AN2

00001 = Channel 0 positive input is AN1

00000 = Channel 0 positive input is AN0

dsPIC33FJ32MC302, dsPIC33FJ64MC202/802 and dsPIC33FJ128MC202/802 devices only:

00101 = Channel 0 positive input is AN5

.

```

00010 = Channel 0 positive input is AN2 00001 = Channel 0 positive input is AN1 00000 = Channel 0 positive input is AN0

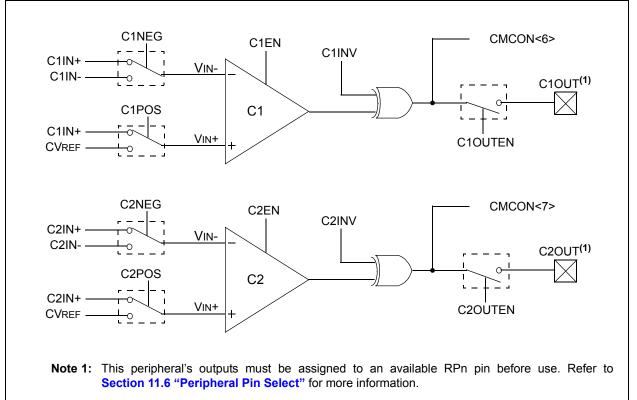

# 24.0 COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of dsPIC33FJ32MC302/304. the dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer Section to 34. "Comparator" (DS70212) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Comparator module provides a set of dual input comparators. The inputs to the comparator can be configured to use any one of the four pin inputs (C1IN+, C1IN-, C2IN+ and C2IN-) as well as the Comparator Voltage Reference Input (CVREF).

Note: This peripheral contains output functions that may need to be configured by the peripheral pin select feature. For more information, see Section 11.6 "Peripheral Pin Select".

| Register 27-2:   | PMM                                                                          | ODE: PARAL                                                                   | LEL PORT I                                         |                                             | STER                                                                                   |                                    |                      |

|------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------|----------------------|

| R-0              | R/W-0                                                                        | R/W-0                                                                        | R/W-0                                              | R/W-0                                       | R/W-0                                                                                  | R/W-0                              | R/W-0                |

| BUSY             | IRQ                                                                          | M<1:0>                                                                       | INC                                                | VI<1:0>                                     | MODE16                                                                                 | MODE                               | =<1:0>               |

| bit 15           |                                                                              |                                                                              |                                                    |                                             |                                                                                        |                                    | bit 8                |

| R/W-0            | R/W-0                                                                        | R/W-0                                                                        | R/W-0                                              | R/W-0                                       | R/W-0                                                                                  | R/W-0                              | R/W-0                |

| WAITB<1          | :0> <sup>(1)</sup>                                                           |                                                                              | WAI                                                | ГМ<3:0>                                     |                                                                                        | WAITE                              | <1:0> <sup>(1)</sup> |

| bit 7            |                                                                              |                                                                              |                                                    |                                             |                                                                                        |                                    | bit (                |

| Legend:          |                                                                              |                                                                              |                                                    |                                             |                                                                                        |                                    |                      |

| R = Readable bi  | t                                                                            | W = Writable                                                                 | bit                                                | U = Unimple                                 | mented bit, read                                                                       | as '0'                             |                      |

| -n = Value at PC | R                                                                            | '1' = Bit is se                                                              | t                                                  | ʻ0' = Bit is cle                            | eared                                                                                  | x = Bit is unkr                    | nown                 |

| bit 15           | BUSY: Busv                                                                   | v bit (Master mo                                                             | de onlv)                                           |                                             |                                                                                        |                                    |                      |

| :                | -                                                                            | usy (not useful                                                              | • ·                                                | cessor stall is a                           | ictive)                                                                                |                                    |                      |

| bit 14-13        | RQM<1:0>:                                                                    | Interrupt Requ                                                               | est Mode bits                                      |                                             |                                                                                        |                                    |                      |

|                  | or on a<br>10 = No inte<br>11 = Interrup                                     |                                                                              | peration when<br>l, processor si<br>the end of the | PMA<1:0> = :<br>all activated               | Write Buffer 3 is v<br>11 (Addressable<br>de                                           |                                    |                      |

| bit 12-11 I      | NCM<1:0>:                                                                    | Increment Mod                                                                | le bits                                            |                                             |                                                                                        |                                    |                      |

|                  | 10 = Decren                                                                  | ad and write bu<br>nent ADDR<10:<br>ent ADDR<10:0<br>rement or decre         | 0> by 1 every<br>)> by 1 every                     | read/write cyc<br>read/write cycl           |                                                                                        | ()                                 |                      |

| bit 10           | MODE16: 8/                                                                   | /16-bit Mode bit                                                             |                                                    |                                             |                                                                                        |                                    |                      |

|                  |                                                                              |                                                                              |                                                    |                                             | o the data registe<br>the data register                                                |                                    |                      |

| bit 9-8          | MODE<1:0>                                                                    | ·: Parallel Port                                                             | Mode Select b                                      | vits                                        | -                                                                                      |                                    |                      |

|                  | 10 = Master                                                                  | mode 2 (PMCS<br>ced PSP, contro                                              | 61, PMRD <u>, PN</u><br>I signals (PM              | <u>IWR, PMBE, F</u><br>RD, PM <u>WR, PI</u> | PMBE, PMA <x:0<br>PMA<x:0> and Pl<br/>MCS1, PMD&lt;7:0<br/>, PMWR, PMCS</x:0></x:0<br> | MD<7:0>)<br><u>&gt;</u> and PMA<1: | .0>)                 |

| bit 7-6          | NAITB<1:0                                                                    | >: Data Setup to                                                             | Read/Write                                         | Wait State Con                              | figuration bits <sup>(1)</sup>                                                         |                                    |                      |

|                  | 10 <b>= Data w</b><br>01 <b>= Data w</b>                                     | ait of 4 Tcy; mu<br>ait of 3 Tcy; mu<br>ait of 2 Tcy; mu<br>ait of 1 Tcy; mu | Itiplexed addr<br>Itiplexed addr                   | ess phase of 3<br>ess phase of 2            | TCY<br>TCY                                                                             |                                    |                      |

| bit 5-2          | NAITM<3:0                                                                    | >: Read to Byte                                                              | Enable Strob                                       | e Wait State C                              | onfiguration bits                                                                      |                                    |                      |

|                  | 1111 <b>= Wait</b>                                                           | of additional 1                                                              | 5 TCY                                              |                                             |                                                                                        |                                    |                      |

|                  | ,                                                                            |                                                                              |                                                    |                                             |                                                                                        |                                    |                      |

|                  |                                                                              | of additional 1<br>additional wait c                                         |                                                    | on forced into (                            | ane Tcv)                                                                               |                                    |                      |

|                  |                                                                              | <ul> <li>Data Hold Aft</li> </ul>                                            | • • • •                                            |                                             |                                                                                        |                                    |                      |

|                  | 11 = Wait of<br>10 = Wait of<br>11 = Wait of<br>10 = Wait of<br>10 = Wait of | 4 Tcy<br>3 Tcy<br>2 Tcy                                                      |                                                    |                                             |                                                                                        |                                    |                      |

# Register 27-2: PMMODE: PARALLEL PORT MODE REGISTER

**Note 1:** WAITB and WAITE bits are ignored whenever WAITM3:WAITM0 = 0000.

# TABLE 28-5: CODE FLASH SECURITY SEGMENT SIZES FOR 128 KB DEVICES

| CONFIG BITS           | BSS<2:0> = x11 0K                                                                                                                                                                                                                                                                                                                                                                                                                              | BSS<2:0> = x10 1K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BSS<2:0> = x01 4K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | BSS<2:0> = x00 8K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |