Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc204t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

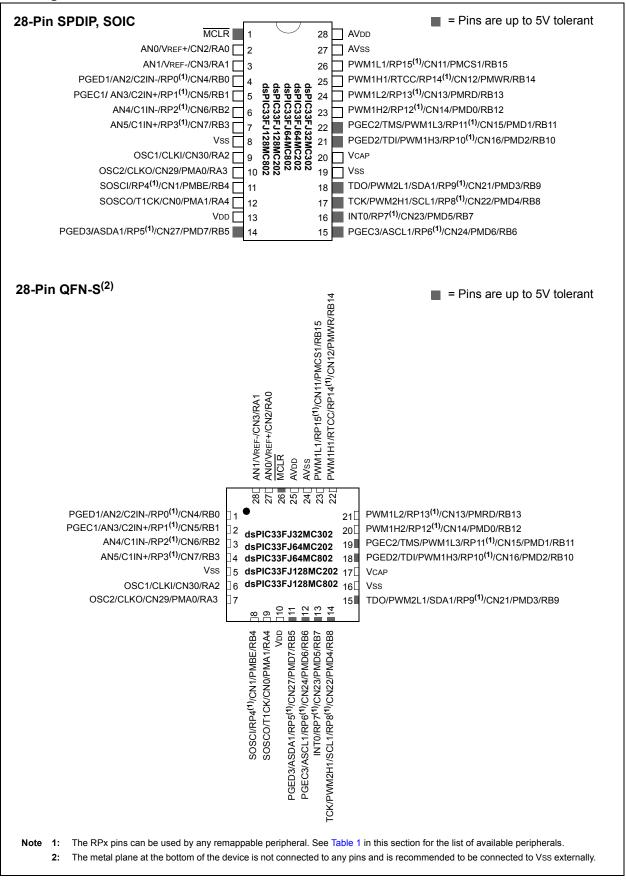

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

### Pin Diagrams

# Table of Contents

| dsPIC | C33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 Product Families | 2   |

|-------|-----------------------------------------------------------------------------------|-----|

| 1.0   | Device Overview                                                                   |     |

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers             |     |

| 3.0   | CPU                                                                               |     |

| 4.0   | Memory Organization                                                               |     |

| 5.0   | Flash Program Memory                                                              | 73  |

| 6.0   | Resets                                                                            |     |

| 7.0   | Interrupt Controller                                                              |     |

| 8.0   | Direct Memory Access (DMA)                                                        | 131 |

| 9.0   | Oscillator Configuration                                                          | 143 |

| 10.0  | Power-Saving Features                                                             | 155 |

| 11.0  | I/O Ports                                                                         | 163 |

|       | Timer1                                                                            |     |

| 13.0  | Timer2/3 And TImer4/5                                                             | 199 |

| 14.0  | Input Capture                                                                     | 205 |

| 15.0  | Output Compare                                                                    | 209 |

|       | Motor Control PWM Module                                                          |     |

|       | Quadrature Encoder Interface (QEI) Module                                         |     |

|       | Serial Peripheral Interface (SPI)                                                 |     |

|       | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                     |     |

| 20.0  | Universal Asynchronous Receiver Transmitter (UART)                                |     |

|       | Enhanced CAN (ECAN™) Module                                                       |     |

|       | 10-bit/12-bit Analog-to-Digital Converter (ADC1)                                  |     |

| 23.0  | Audio Digital-to-Analog Converter (DAC)                                           |     |

|       | Comparator Module                                                                 |     |

|       | Real-Time Clock and Calendar (RTCC)                                               |     |

|       | Programmable Cyclic Redundancy Check (CRC) Generator                              |     |

|       | Parallel Master Port (PMP)                                                        |     |

| 28.0  | Special Features                                                                  | 335 |

|       | Instruction Set Summary                                                           |     |

|       | Development Support                                                               |     |

|       | Electrical Characteristics                                                        |     |

|       | High Temperature Electrical Characteristics                                       |     |

|       | DC and AC Device Characteristics Graphs                                           |     |

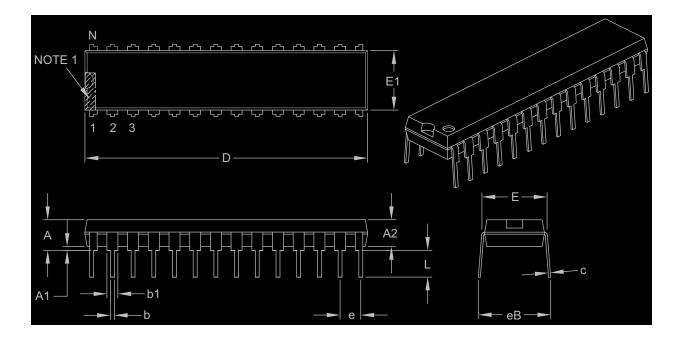

|       | Packaging Information                                                             |     |

| Appe  | ndix A: Revision History                                                          | 439 |

|       | <                                                                                 |     |

|       | Nicrochip Web Site                                                                |     |

|       | omer Change Notification Service                                                  |     |

| Custo | omer Support                                                                      | 455 |

|       | ler Response                                                                      |     |

| Produ | uct Identification System                                                         | 457 |

The Overflow and Saturation Status bits can optionally be viewed in the STATUS Register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). Programmers can check one bit in the STATUS register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This is useful for complex number arithmetic, which typically uses both accumulators.

The device supports three Saturation and Overflow modes:

- Bit 39 Overflow and Saturation:

- When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFF) or maximally negative 9.31 value (0x800000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user application. This condition is referred to as super saturation and provides protection against erroneous data or unexpected algorithm problems (such as gain calculations).

- Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFF) or maximally negative 1.31 value (0x0080000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user application. When this Saturation mode is in effect, the guard bits are not used, so the OA, OB or OAB bits are never set.

- Bit 39 Catastrophic Overflow: The bit 39 Overflow Status bit from the adder is used to set the SA or SB bit, which remains set until cleared by the user application. No saturation operation is performed, and the accumulator is allowed to overflow, destroying its sign. If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

# 3.8.3 ACCUMULATOR WRITE BACK

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

- W13, Register Direct: The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

- [W13] + = 2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

## 3.8.3.1 Round Logic

The round logic is a combinational block that performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value that is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored, and the least significant word is simply discarded.

Conventional rounding zero-extends bit 15 of the accumulator and adds it to the ACCxH word (bits 16 through 31 of the accumulator).

- If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented.

- If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged.

A consequence of this algorithm is that over a succession of random rounding operations, the value tends to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. In this case, the Least Significant bit (bit 16 of the accumulator) of ACCxH is examined:

- If it is '1', ACCxH is incremented.

- If it is '0', ACCxH is not modified.

Assuming that bit 16 is effectively random in nature, this scheme removes any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC), or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus, subject to data saturation (see **Section 3.8.3.2 "Data Space Write Saturation**"). For the MAC class of instructions, the accumulator write-back operation functions in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

#### **Special Function Register Maps** 4.4

#### TABLE 4-1: **CPU CORE REGISTERS MAP**

| DS7029  |  |

|---------|--|

| )1G-pag |  |

| je 42   |  |

| SFR Name | Addr | Bit 15 | Bit 14                       | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8       | Bit 7        | Bit 6 | Bit 5     | Bit 4           | Bit 3        | Bit 2        | Bit 1   | Bit 0 | All<br>Resets |

|----------|------|--------|------------------------------|--------|--------|--------|--------|---------|-------------|--------------|-------|-----------|-----------------|--------------|--------------|---------|-------|---------------|

| WREG0    | 0000 |        | Working Register 0           |        |        |        |        |         |             |              |       | 0000      |                 |              |              |         |       |               |

| WREG1    | 0002 |        | Working Register 1           |        |        |        |        |         |             |              | 0000  |           |                 |              |              |         |       |               |

| WREG2    | 0004 |        |                              |        |        |        |        |         | Working Re  | gister 2     |       |           |                 |              |              |         |       | 0000          |

| WREG3    | 0006 |        |                              |        |        |        |        |         | Working Re  | gister 3     |       |           |                 |              |              |         |       | 0000          |

| WREG4    | 0008 |        |                              |        |        |        |        |         | Working Re  | gister 4     |       |           |                 |              |              |         |       | 0000          |

| WREG5    | 000A |        |                              |        |        |        |        |         | Working Re  | gister 5     |       |           |                 |              |              |         |       | 0000          |

| WREG6    | 000C |        |                              |        |        |        |        |         | Working Re  | gister 6     |       |           |                 |              |              |         |       | 0000          |

| WREG7    | 000E |        |                              |        |        |        |        |         | Working Re  | gister 7     |       |           |                 |              |              |         |       | 0000          |

| WREG8    | 0010 |        |                              |        |        |        |        |         | Working Re  | gister 8     |       |           |                 |              |              |         |       | 0000          |

| WREG9    | 0012 |        |                              |        |        |        |        |         | Working Re  | gister 9     |       |           |                 |              |              |         |       | 0000          |

| WREG10   | 0014 |        |                              |        |        |        |        |         | Working Reg | jister 10    |       |           |                 |              |              |         |       | 0000          |

| WREG11   | 0016 |        |                              |        |        |        |        |         | Working Reg | jister 11    |       |           |                 |              |              |         |       | 0000          |

| WREG12   | 0018 |        |                              |        |        |        |        |         | Working Reg | ister 12     |       |           |                 |              |              |         |       | 0000          |

| WREG13   | 001A |        |                              |        |        |        |        |         | Working Reg | jister 13    |       |           |                 |              |              |         |       | 0000          |

| WREG14   | 001C |        |                              |        |        |        |        |         | Working Reg | jister 14    |       |           |                 |              |              |         |       | 0000          |

| WREG15   | 001E |        | Working Register 15          |        |        |        |        |         |             | 0800         |       |           |                 |              |              |         |       |               |

| SPLIM    | 0020 |        | Stack Pointer Limit Register |        |        |        |        |         |             | XXXX         |       |           |                 |              |              |         |       |               |

| ACCAL    | 0022 |        |                              |        |        |        |        |         | ACCA        | L            |       |           |                 |              |              |         |       | XXXX          |

| ACCAH    | 0024 |        |                              |        |        |        |        |         | ACCA        | Н            |       |           |                 |              |              |         |       | XXXX          |

| ACCAU    | 0026 |        |                              |        | ACCA<  | 39>    |        |         |             |              |       |           | ACO             | CAU          |              |         |       | XXXX          |

| ACCBL    | 0028 |        |                              |        |        |        |        |         | ACCB        | L            |       |           |                 |              |              |         |       | XXXX          |

| ACCBH    | 002A |        |                              |        |        |        |        |         | ACCB        | Н            |       |           |                 |              |              |         |       | XXXX          |

| ACCBU    | 002C |        |                              |        | ACCB<  | 39>    |        |         |             |              |       |           | ACO             | CBU          |              |         |       | XXXX          |

| PCL      | 002E |        |                              |        |        |        |        | Program | Counter Lov | w Word Reg   | ister |           |                 |              |              |         |       | XXXX          |

| PCH      | 0030 | _      |                              | —      |        |        | —      |         | _           |              |       | Progra    | am Counter      | High Byte R  | Register     |         |       | 0000          |

| TBLPAG   | 0032 | _      | —                            | —      |        |        | _      |         |             |              |       | Table     | Page Addre      | ss Pointer F | Register     |         |       | 0000          |

| PSVPAG   | 0034 | _      |                              | —      |        |        | —      |         | —           |              | Prog  | ram Memor | y Visibility Pa | age Addres   | s Pointer Re | egister |       | 0000          |

| RCOUNT   | 0036 |        |                              |        |        |        |        | Repe    | at Loop Cou | nter Registe | er    |           |                 |              |              |         |       | XXXX          |

| DCOUNT   | 0038 |        |                              |        |        |        |        |         | DCOUNT<     |              |       |           |                 |              |              |         |       | XXXX          |

| DOSTARTL | 003A |        |                              |        |        |        |        | DOST    | ARTL<15:1   | >            |       |           |                 |              |              |         | 0     | XXXX          |

| DOSTARTH | 003C | _      | —                            | _      | —      | —      | —      | —       | —           | _            | _     |           |                 | DOSTAF       | RTH<5:0>     |         |       | 00xx          |

| DOENDL   | 003E |        |                              |        |        |        |        | DOE     | NDL<15:1>   | •            |       | •         |                 |              |              |         | 0     | XXXX          |

| DOENDH   | 0040 | _      | —                            | —      | —      | —      | —      | —       | —           | _            | —     |           |                 | DOEN         | DH<5:0>      |         |       | 00xx          |

| SR       | 0042 | OA     | OB                           | SA     | SB     | OAB    | SAB    | DA      | DC          | IPL2         | IPL1  | IPL0      | RA              | N            | OV           | Z       | С     | 0000          |

| CORCON   | 0044 | —      | —                            | _      | US     | EDT    |        | DL<2:0> |             | SATA         | SATB  | SATDW     | ACCSAT          | IPL3         | PSV          | RND     | IF    | 0020          |

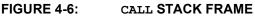

### 4.4.1 SOFTWARE STACK

In addition to its use as a working register, the W15 register in the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

**Note:** A PC push during exception processing concatenates the SRL register to the MSb of the PC prior to the push.

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. The SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, the SPLIM<0> is forced to '0' because all stack operations must be word aligned.

Whenever an EA is generated using the W15 as a source or destination pointer, the resulting address is compared with the value in the SPLIM register. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap does not occur. The stack error trap occurs on a subsequent push operation. For example, to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

# 4.4.2 DATA RAM PROTECTION FEATURE

The dsPIC33F product family supports Data RAM protection features that enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. The BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. The SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

# 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-40 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

# 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (near data space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

# 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where:

Operand 1 is always a working register (that is, the addressing mode can only be register direct), which is referred to as Wb.

Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

Note: Not all instructions support all the addressing modes listed above. Individual instructions can support different subsets of these addressing modes.

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

#### TABLE 4-40: FUNDAMENTAL ADDRESSING MODES SUPPORTED

#### 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than any other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing mode specified in the instruction can differ |

|-------|---------------------------------------------------------------------------------------|

|       | for the source and destination EA.                                                    |

|       | However, the 4-bit Wb (Register Offset)                                               |

|       | field is shared by both source and                                                    |

|       | destination (but typically only used by                                               |

|       | one).                                                                                 |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

Note: Not all instructions support all the addressing modes listed above. Individual instructions may support different subsets of these addressing modes.

## 4.5.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the data pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The effective addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

| Note: | Register                                 | Indirect | with | Register | Offset |  |

|-------|------------------------------------------|----------|------|----------|--------|--|

|       | Addressing mode is available only for W9 |          |      |          |        |  |

|       | (in X space) and W11 (in Y space).       |          |      |          |        |  |

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

# 4.5.5 OTHER INSTRUCTIONS

Apart from the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas, the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

# FIGURE 7-1: dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/ X04 INTERRUPT VECTOR TABLE

|                                   | Reset – GOTO Instruction          | 0x000000          |                                                        |

|-----------------------------------|-----------------------------------|-------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Address              | 0x000002          |                                                        |

|                                   | Reserved                          | 0x000004          |                                                        |

|                                   | Oscillator Fail Trap Vector       |                   |                                                        |

|                                   | Address Error Trap Vector         |                   |                                                        |

|                                   | Stack Error Trap Vector           |                   |                                                        |

|                                   | Math Error Trap Vector            |                   |                                                        |

|                                   | DMA Error Trap Vector             |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Interrupt Vector 0                | 0x000014          |                                                        |

|                                   | Interrupt Vector 1                |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | Interrupt Vector 52               | 0x00007C          | Interview Vector Table (IVT)(1)                        |

|                                   | Interrupt Vector 53               | 0x00007E          | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| ity                               | Interrupt Vector 54               | 0x000080          |                                                        |

| jo                                | ~                                 |                   |                                                        |

| Ē                                 | ~                                 |                   |                                                        |

| de                                | ~                                 |                   |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 116              | 0x0000FC          |                                                        |

| Iral                              | Interrupt Vector 117              | 0x0000FE          |                                                        |

| atr                               | Reserved                          | 0x000100          |                                                        |

| Z                                 | Reserved                          | 0x000102          |                                                        |

| sinç                              | Reserved                          |                   |                                                        |

| eas                               | Oscillator Fail Trap Vector       |                   |                                                        |

| ů –                               | Address Error Trap Vector         |                   |                                                        |

| ă                                 | Stack Error Trap Vector           |                   |                                                        |

|                                   | Math Error Trap Vector            |                   |                                                        |

|                                   | DMA Error Trap Vector             |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Interrupt Vector 0                | 0x000114          |                                                        |

|                                   | Interrupt Vector 1                |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 |                   | (4)                                                    |

|                                   | ~                                 |                   | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52               | 0x00017C          |                                                        |

|                                   | Interrupt Vector 53               | 0x00017E          |                                                        |

|                                   | Interrupt Vector 54               | 0x000180          |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 | _                 |                                                        |

|                                   |                                   |                   | 1                                                      |

|                                   | Interrupt Vector 116              |                   |                                                        |

| ₩                                 | Interrupt Vector 117              | 0x0001FE          |                                                        |

| ۲                                 | Start of Code                     | 0x000200          |                                                        |

|                                   |                                   |                   |                                                        |

|                                   |                                   |                   |                                                        |

| Note 1: See                       | Table 7-1 for the list of impleme | ented interrupt v | rectors                                                |

|                                   |                                   |                   |                                                        |

|                                   |                                   |                   |                                                        |

| U-0          | R/W-1                                                      | R/W-0                                                               | R/W-0         | U-0               | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|--------------|------------------------------------------------------------|---------------------------------------------------------------------|---------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| _            |                                                            | QEI2IP<2:0>                                                         |               | _                 |                  | FLTA2IP<2:0>    |       |  |  |  |  |

| bit 15       |                                                            |                                                                     |               |                   |                  |                 | bit   |  |  |  |  |

|              |                                                            |                                                                     |               |                   |                  |                 |       |  |  |  |  |

| U-0          | R/W-1                                                      | R/W-0                                                               | R/W-0         | U-0               | U-0              | U-0             | U-0   |  |  |  |  |

|              |                                                            | PWM2IP<2:0>                                                         |               | _                 |                  | _               |       |  |  |  |  |

| bit 7        |                                                            |                                                                     |               |                   |                  |                 | bit   |  |  |  |  |

| Legend:      |                                                            |                                                                     |               |                   |                  |                 |       |  |  |  |  |

| R = Readab   | ole bit                                                    | W = Writable                                                        | bit           | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value a | at POR                                                     | '1' = Bit is set                                                    |               | '0' = Bit is clea |                  | x = Bit is unkr | iown  |  |  |  |  |

|              |                                                            |                                                                     |               |                   |                  |                 |       |  |  |  |  |

| bit 15       | Unimpleme                                                  | nted: Read as '                                                     | )'            |                   |                  |                 |       |  |  |  |  |

| bit 14-12    | QEI2IP<2:0                                                 | CEI2IP<2:0>: QEI2 Interrupt Priority bits                           |               |                   |                  |                 |       |  |  |  |  |

|              | 111 = Interr                                               | 111 = Interrupt is priority 7 (highest priority interrupt)          |               |                   |                  |                 |       |  |  |  |  |

|              | •                                                          | •                                                                   |               |                   |                  |                 |       |  |  |  |  |

|              | •                                                          | •                                                                   |               |                   |                  |                 |       |  |  |  |  |

|              | •<br>001 = Interr                                          | •<br>001 = Interrupt is priority 1                                  |               |                   |                  |                 |       |  |  |  |  |

|              |                                                            | errupt source is disabled                                           |               |                   |                  |                 |       |  |  |  |  |

| bit 11       | Unimpleme                                                  | nted: Read as '                                                     | )'            |                   |                  |                 |       |  |  |  |  |

| bit 10-8     | FLTA2IP<2:                                                 | 0>: PWM2 Fault                                                      | A Interrupt F | Priority bits     |                  |                 |       |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt) |                                                                     |               |                   |                  |                 |       |  |  |  |  |

|              | •                                                          | •                                                                   |               |                   |                  |                 |       |  |  |  |  |

|              | •                                                          |                                                                     |               |                   |                  |                 |       |  |  |  |  |

|              | •                                                          |                                                                     |               |                   |                  |                 |       |  |  |  |  |

|              |                                                            | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled |               |                   |                  |                 |       |  |  |  |  |

| bit 7        |                                                            | nted: Read as '                                                     |               |                   |                  |                 |       |  |  |  |  |

| bit 6-4      | -                                                          | 0>: PWM2 Inter                                                      |               | oite              |                  |                 |       |  |  |  |  |

| DIL 0-4      |                                                            | upt is priority 7 (I                                                |               |                   |                  |                 |       |  |  |  |  |

|              | •                                                          |                                                                     | lightest phon | ty interrupt)     |                  |                 |       |  |  |  |  |

|              | •                                                          |                                                                     |               |                   |                  |                 |       |  |  |  |  |

|              | •                                                          |                                                                     |               |                   |                  |                 |       |  |  |  |  |

|              |                                                            | upt is priority 1                                                   |               |                   |                  |                 |       |  |  |  |  |

|              | 000 = Interr                                               | upt source is dis                                                   | abled         |                   |                  |                 |       |  |  |  |  |

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

## **REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)**

- bit 2 Unimplemented: Read as '0'

- bit 1 C1MD: ECAN1 Module Disable bit

- 1 = ECAN1 module is disabled

- 0 = ECAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit

- 1 = ADC1 module is disabled 0 = ADC1 module is enabled

# 15.2 Output Compare Resources

Many useful resources related to Output Compare are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

## 15.2.1 KEY RESOURCES

- Section 13. "Output Compare" (DS70209)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

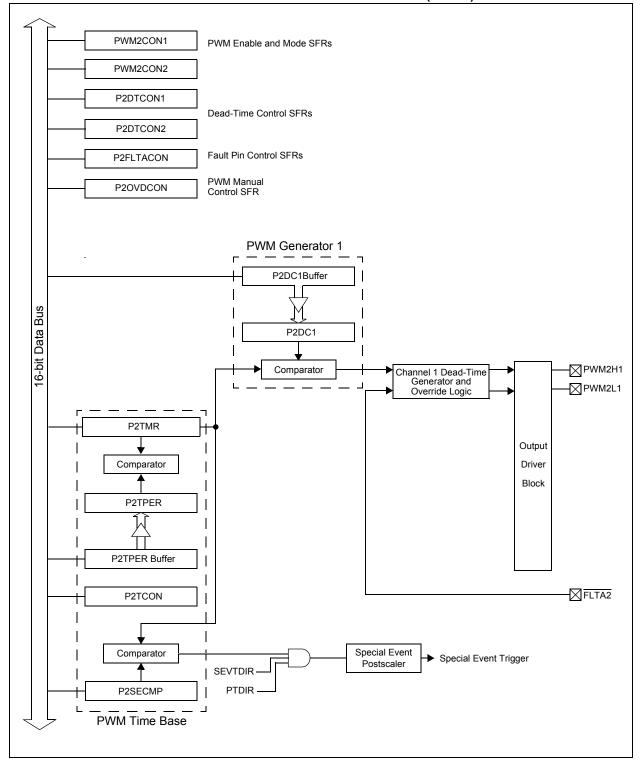

### FIGURE 16-2: 2-CHANNEL PWM MODULE BLOCK DIAGRAM (PWM2)

|                      |                                                                                                     | CONTINUE                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| U-0                  | U-0                                                                                                 | U-0                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| —                    | —                                                                                                   | _                                                                                                                                                                                                                                                                                                        | —                                                                                                                                                                                                                                                                                                                                                              | PMOD3                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PMOD2                                                                                                                                                                                                                                                                                        | PMOD1                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                      |                                                                                                     |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                              | bit 8                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                      |                                                                                                     |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| R/W-1                | R/W-1                                                                                               | R/W-1                                                                                                                                                                                                                                                                                                    | U-0                                                                                                                                                                                                                                                                                                                                                            | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-1                                                                                                                                                                                                                                                                                        | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| PEN3H <sup>(1)</sup> | PEN2H <sup>(1)</sup>                                                                                | PEN1H <sup>(1)</sup>                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                                              | PEN3L <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PEN2L <sup>(1)</sup>                                                                                                                                                                                                                                                                         | PEN1L <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                      |                                                                                                     |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                              | bit (                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                      |                                                                                                     |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                      |                                                                                                     |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| e bit                | W = Writable                                                                                        | bit                                                                                                                                                                                                                                                                                                      | U = Unimpler                                                                                                                                                                                                                                                                                                                                                   | mented bit, read                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | d as '0'                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| POR                  | '1' = Bit is set                                                                                    |                                                                                                                                                                                                                                                                                                          | '0' = Bit is cle                                                                                                                                                                                                                                                                                                                                               | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | x = Bit is unknown                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                      |                                                                                                     |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Unimplemen           | ted: Read as '                                                                                      | 0'                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |