#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc802-e-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1:     PINOUT I/O DESCRIPTIONS |             |                                |            |                                                                                                                                                                                                                                                                     |  |  |

|----------------------------------------|-------------|--------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                               | Pin<br>Type | Buffer<br>Type                 | PPS        | Description                                                                                                                                                                                                                                                         |  |  |

| AN0-AN8                                | I           | Analog                         | No         | Analog input channels.                                                                                                                                                                                                                                              |  |  |

| CLKI                                   | <br>  0     | ST/CMOS                        | No<br>No   | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally, functions as CLKO in RC and EC modes.<br>Always associated with OSC2 pin function. |  |  |

| OSC1                                   |             | ST/CMOS                        | No         | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                                                                                                                |  |  |

| OSC2                                   | I/O         | _                              | No         | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                           |  |  |

| SOSCI<br>SOSCO                         | <br>  0     | ST/CMOS                        | No<br>No   | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.<br>32.768 kHz low-power oscillator crystal output.                                                                                                                                                   |  |  |

| CN0-CN30                               | I           | ST                             | No         | Change notification inputs. Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                    |  |  |

| IC1-IC2<br>IC7-IC8                     |             | ST<br>ST                       | Yes<br>Yes | Capture inputs 1/2.<br>Capture inputs 7/8.                                                                                                                                                                                                                          |  |  |

| OCFA<br>OC1-OC4                        | <br>  0     | ST<br>—                        | Yes<br>Yes | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).<br>Compare outputs 1 through 4.                                                                                                                                                                         |  |  |

| INT0                                   | I           | ST                             | No         | External interrupt 0.                                                                                                                                                                                                                                               |  |  |

| INT1                                   |             | ST                             | Yes        | External interrupt 1.                                                                                                                                                                                                                                               |  |  |

| INT2<br>RA0-RA4                        | 1           | ST                             | Yes        | External interrupt 2.                                                                                                                                                                                                                                               |  |  |

| RA0-RA4<br>RA7-RA10                    | 1/O<br>1/O  | ST<br>ST                       | No<br>No   | PORTA is a bidirectional I/O port.<br>PORTA is a bidirectional I/O port.                                                                                                                                                                                            |  |  |

| RB0-RB15                               | I/O         | ST                             | No         | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                  |  |  |

| RC0-RC9                                | I/O         | ST                             | No         | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                  |  |  |

| T1CK                                   | I           | ST                             | No         | Timer1 external clock input.                                                                                                                                                                                                                                        |  |  |

| T2CK                                   |             | ST                             | Yes        | Timer2 external clock input.                                                                                                                                                                                                                                        |  |  |

| T3CK<br>T4CK                           |             | ST<br>ST                       | Yes<br>Yes | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                                                                                                        |  |  |

| T5CK                                   |             | ST                             | Yes        | Timer5 external clock input.                                                                                                                                                                                                                                        |  |  |

| U1CTS                                  | 1           | ST                             | Yes        | UART1 clear to send.                                                                                                                                                                                                                                                |  |  |

| U1RTS                                  | 0           | _                              | Yes        | UART1 ready to send.                                                                                                                                                                                                                                                |  |  |

| U1RX                                   | I           | ST                             | Yes        | UART1 receive.                                                                                                                                                                                                                                                      |  |  |

| U1TX                                   | 0           | —                              | Yes        | UART1 transmit.                                                                                                                                                                                                                                                     |  |  |

| U2CTS                                  | I           | ST                             | Yes        | UART2 clear to send.                                                                                                                                                                                                                                                |  |  |

| U2RTS                                  | 0           | -                              | Yes        | UART2 ready to send.                                                                                                                                                                                                                                                |  |  |

| U2RX<br>U2TX                           |             | ST<br>—                        | Yes<br>Yes | UART2 receive.<br>UART2 transmit.                                                                                                                                                                                                                                   |  |  |

|                                        |             |                                |            |                                                                                                                                                                                                                                                                     |  |  |

| SCK1<br>SDI1                           | I/O         | ST<br>ST                       | Yes<br>Yes | Synchronous serial clock input/output for SPI1.<br>SPI1 data in.                                                                                                                                                                                                    |  |  |

| SD01                                   | 0           |                                | Yes        | SPI1 data out.                                                                                                                                                                                                                                                      |  |  |

| SS1                                    | I/O         | ST                             | Yes        | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                      |  |  |

| SCK2                                   | I/O         | ST                             | Yes        | Synchronous serial clock input/output for SPI2.                                                                                                                                                                                                                     |  |  |

| SDI2                                   | I           | ST                             | Yes        | SPI2 data in.                                                                                                                                                                                                                                                       |  |  |

| SDO2                                   | 0           | _                              | Yes        | SPI2 data out.                                                                                                                                                                                                                                                      |  |  |

| SS2                                    | I/O         | ST                             | Yes        | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                      |  |  |

| SCL1                                   | I/O         | ST                             | No         | Synchronous serial clock input/output for I2C1.                                                                                                                                                                                                                     |  |  |

| SDA1                                   | I/O         | ST                             | No         | Synchronous serial data input/output for I2C1.                                                                                                                                                                                                                      |  |  |

| ASCL1                                  | I/O         | ST                             | No         | Alternate synchronous serial clock input/output for I2C1.                                                                                                                                                                                                           |  |  |

| ASDA1                                  | I/O         | ST                             | No         | Alternate synchronous serial data input/output for I2C1.                                                                                                                                                                                                            |  |  |

|                                        |             | S compatibl                    |            |                                                                                                                                                                                                                                                                     |  |  |

|                                        |             | Frigger input<br>eral Pin Sele |            | MOS levels O = Output I = Input<br>TTL = TTL input buffer                                                                                                                                                                                                           |  |  |

| сг                                     |             |                                |            |                                                                                                                                                                                                                                                                     |  |  |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS

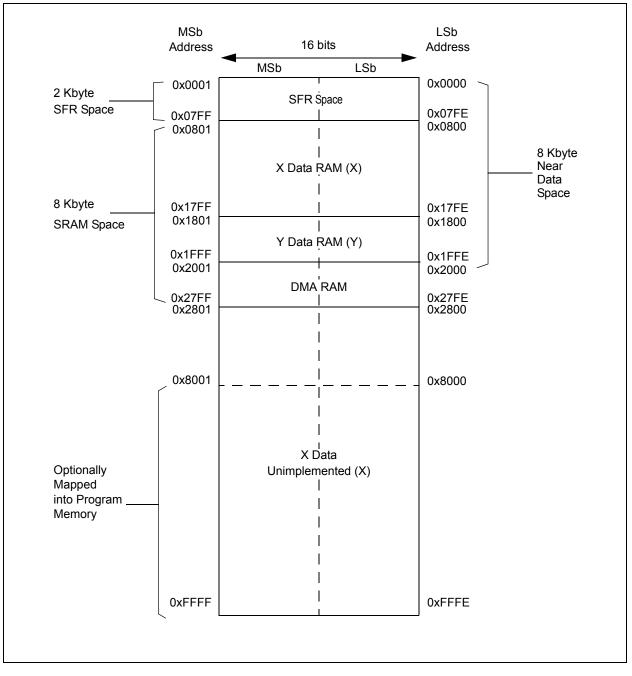

#### FIGURE 4-4: DATA MEMORY MAP FOR dsPIC33FJ128MC202/204 AND dsPIC33FJ64MC202/ 204 DEVICES WITH 8 KB RAM

# TABLE 4-1: CPU CORE REGISTERS MAP (CONTINUED)

|          |      |        |                                         |        |                            |        | ,      |       |          |          |       |       |       |       |       |       |       |               |

|----------|------|--------|-----------------------------------------|--------|----------------------------|--------|--------|-------|----------|----------|-------|-------|-------|-------|-------|-------|-------|---------------|

| SFR Name | Addr | Bit 15 | Bit 14                                  | Bit 13 | Bit 12                     | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| MODCON   | 0046 | XMODEN | YMODEN                                  | -      | BWM<3:0> YWM<3:0> XWM<3:0> |        |        |       |          |          |       |       |       | 0000  |       |       |       |               |

| XMODSRT  | 0048 |        | XS<15:1>                                |        |                            |        |        |       |          |          | 0     | XXXX  |       |       |       |       |       |               |

| XMODEND  | 004A |        | XE<15:1>                                |        |                            |        |        |       |          |          |       | 1     | XXXX  |       |       |       |       |               |

| YMODSRT  | 004C |        |                                         |        |                            |        |        | Y     | ′S<15:1> |          |       |       |       |       |       |       | 0     | XXXX          |

| YMODEND  | 004E |        |                                         |        |                            |        |        | Y     | ′E<15:1> |          |       |       |       |       |       |       | 1     | XXXX          |

| XBREV    | 0050 | BREN   |                                         |        |                            |        |        |       |          | XB<14:0> |       |       |       |       |       |       |       | XXXX          |

| DISICNT  | 0052 | —      | — — Disable Interrupts Counter Register |        |                            |        |        |       |          |          | XXXX  |       |       |       |       |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 2 | CMIE: Comparator Interrupt Enable bit                                                     |

|-------|-------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| bit 1 | MI2C1IE: I2C1 Master Events Interrupt Enable bit                                          |

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| bit 0 | SI2C1IE: I2C1 Slave Events Interrupt Enable bit                                           |

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

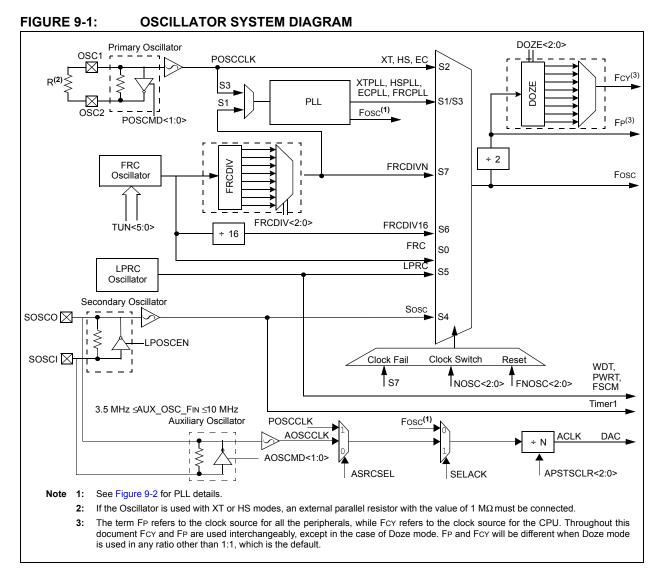

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features dsPIC33FJ32MC302/304, of the dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 39. "Oscillator (Part III)" (DS70216) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 oscillator system provides:

- External and internal oscillator options as clock sources

- An on-chip Phase-Locked Loop (PLL) to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- · Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Non-volatile Configuration bits for main oscillator selection

- · An auxiliary crystal oscillator for audio DAC

- A simplified diagram of the oscillator system is shown in Figure 9-1.

# 9.3 Oscillator Control Registers

| U-0        | R-0                                        | R-0                                                                                                 | R-0              | U-0               | R/W-y            | R/W-y                       | R/W-y      |  |  |  |  |

|------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------|-------------------|------------------|-----------------------------|------------|--|--|--|--|

|            |                                            | COSC<2:0>                                                                                           |                  |                   |                  | NOSC<2:0> <sup>(2)</sup>    |            |  |  |  |  |

| bit 15     |                                            |                                                                                                     |                  |                   |                  |                             | bit 8      |  |  |  |  |

| R/W-0      | ) R/W-0                                    | R-0                                                                                                 | U-0              | R/C-0             | U-0              | R/W-0                       | R/W-0      |  |  |  |  |

| CLKLO      |                                            | LOCK                                                                                                | 0-0              | CF                | 0-0              | LPOSCEN                     | OSWEN      |  |  |  |  |

| bit 7      |                                            | LOOK                                                                                                |                  |                   |                  |                             | bit 0      |  |  |  |  |

|            |                                            |                                                                                                     |                  |                   |                  |                             |            |  |  |  |  |

| Legend:    |                                            | C = Clear only                                                                                      | / bit            | y = Value set     | from Configura   | ation bits on POF           | २          |  |  |  |  |

| R = Read   | able bit                                   | W = Writable                                                                                        | oit              | U = Unimple       | mented bit, rea  | d as '0'                    |            |  |  |  |  |

| -n = Value | e at POR                                   | '1' = Bit is set                                                                                    |                  | '0' = Bit is cle  | ared             | x = Bit is unkno            | own        |  |  |  |  |

| bit 15     | Unimplomor                                 | ted: Dood oo '                                                                                      | `,               |                   |                  |                             |            |  |  |  |  |

| bit 14-12  | -                                          | nted: Read as '                                                                                     |                  | hite (road only   | )                |                             |            |  |  |  |  |

| DIL 14-12  |                                            | Current Oscilla<br>C (FRC) oscilla                                                                  |                  |                   | )                |                             |            |  |  |  |  |

|            |                                            | C (FRC) oscilla                                                                                     |                  |                   |                  |                             |            |  |  |  |  |

|            |                                            | ower RC (LPR                                                                                        |                  |                   |                  |                             |            |  |  |  |  |

|            |                                            | dary Oscillator                                                                                     |                  |                   |                  |                             |            |  |  |  |  |

|            |                                            | y oscillator (XT,                                                                                   |                  | PLL               |                  |                             |            |  |  |  |  |

|            |                                            | ry oscillator (XT,<br>C (FRC) oscilla                                                               |                  | -by-N and PL      | (FRCDIVN +       | PLL)                        |            |  |  |  |  |

|            |                                            | C (FRC) oscilla                                                                                     |                  |                   |                  |                             |            |  |  |  |  |

| bit 11     | Unimplemer                                 | ted: Read as '                                                                                      | )'               |                   |                  |                             |            |  |  |  |  |

| bit 10-8   | NOSC<2:0>:                                 | New Oscillator                                                                                      | Selection bits   | <sub>S</sub> (2)  |                  |                             |            |  |  |  |  |

|            |                                            | 111 = Fast RC (FRC) oscillator with Divide-by-n<br>110 = Fast RC (FRC) oscillator with Divide-by-16 |                  |                   |                  |                             |            |  |  |  |  |

|            |                                            |                                                                                                     |                  | e-by-16           |                  |                             |            |  |  |  |  |

|            |                                            | ower RC (LPRC<br>dary Oscillator                                                                    | ·                |                   |                  |                             |            |  |  |  |  |

|            |                                            | y oscillator (XT,                                                                                   |                  | PLL               |                  |                             |            |  |  |  |  |

|            |                                            | y oscillator (XT,                                                                                   |                  |                   |                  |                             |            |  |  |  |  |

|            |                                            | C (FRC) oscilla                                                                                     |                  | e-by-N and PL     | L (FRCDIVN +     | PLL)                        |            |  |  |  |  |

| bit 7      |                                            | C (FRC) oscilla<br>Clock Lock Enal                                                                  |                  |                   |                  |                             |            |  |  |  |  |

|            | -                                          |                                                                                                     |                  | disabled (FCI     | (SM<1:0> (FO     | SC<7:6>) = 0b0 <sup>-</sup> | 1)         |  |  |  |  |

|            |                                            | itching is disab                                                                                    |                  |                   |                  | 00 1.0 / 0.00               | <u>· /</u> |  |  |  |  |

|            | 0 = Clock sv                               | vitching is enabl                                                                                   | ed, system cl    | ock source ca     | n be modified b  | y clock switching           | 9          |  |  |  |  |

| bit 6      |                                            | ripheral Pin Sel                                                                                    |                  |                   |                  |                             |            |  |  |  |  |

|            | •                                          | ial pin select is                                                                                   |                  |                   | •                |                             |            |  |  |  |  |

| hit 5      | -                                          | ial pin select is<br>₋ock Status bit (                                                              |                  | nte to peripher   | ai pin select re | gisters allowed             |            |  |  |  |  |

| bit 5      |                                            | s that PLL is in I                                                                                  | • /              | tart-un timer is  | satisfied        |                             |            |  |  |  |  |

|            |                                            | s that PLL is out                                                                                   |                  |                   |                  | L is disabled               |            |  |  |  |  |

| bit 4      | Unimplemer                                 | nted: Read as '                                                                                     | )'               |                   |                  |                             |            |  |  |  |  |

| Note 1:    | Writes to this regis                       |                                                                                                     |                  |                   |                  |                             |            |  |  |  |  |

| •          | in the "dsPIC33F/                          | -                                                                                                   |                  |                   |                  |                             |            |  |  |  |  |

| 2:         | Direct clock switch<br>This applies to clo | ck switches in e                                                                                    | either direction | n. In these inst  | ances, the app   |                             |            |  |  |  |  |

| 3:         | mode as a transiti<br>This register is res |                                                                                                     |                  |                   | :5.              |                             |            |  |  |  |  |

| 5.         | THIS TEGISLET IS LES                       | ber only on a Po                                                                                    | wei-on Resel     | $(1^{\circ}OR)$ . |                  |                             |            |  |  |  |  |

**REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

© 2007-2012 Microchip Technology Inc.

### REGISTER 11-9: RPINR13: PERIPHERAL PIN SELECT INPUT REGISTER 13

| U-0                                | U-0 | U-0            | U-0                                     | U-0          | U-0              | U-0      | U-0   |  |

|------------------------------------|-----|----------------|-----------------------------------------|--------------|------------------|----------|-------|--|

| —                                  | —   | —              | —                                       | —            | —                | _        | —     |  |

| bit 15                             |     |                |                                         |              |                  |          | bit 8 |  |

|                                    |     |                |                                         |              |                  |          |       |  |

| U-0                                | U-0 | U-0            | R/W-1                                   | R/W-1        | R/W-1            | R/W-1    | R/W-1 |  |

| _                                  |     | _              | FLTA2R<4:0>                             |              |                  |          |       |  |

| bit 7                              |     |                |                                         |              |                  |          | bit 0 |  |

|                                    |     |                |                                         |              |                  |          |       |  |

| Legend:                            |     |                |                                         |              |                  |          |       |  |

| R = Readable I                     | oit | W = Writable I | bit                                     | U = Unimpler | mented bit, read | l as '0' |       |  |

| -n = Value at POR '1' = Bit is set |     |                | '0' = Bit is cleared x = Bit is unknown |              |                  |          |       |  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0

FLTA2R<4:0>: Assign PWM2 Fault (FLTA2) to the corresponding RPn pin 11111 = Input tied to Vss 11001 = Input tied to RP25 •

00001 = Input tied to RP1 00000 = Input tied to RP0

### REGISTER 11-19: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0                                           | U-0 | U-0 | U-0   | U-0                                     | U-0              | U-0    | U-0   |

|-----------------------------------------------|-----|-----|-------|-----------------------------------------|------------------|--------|-------|

| —                                             | —   | —   | _     | —                                       | —                | —      | —     |

| bit 15                                        |     |     |       |                                         |                  |        | bit 8 |

|                                               |     |     |       |                                         |                  |        |       |

| U-0                                           | U-0 | U-0 | R/W-1 | R/W-1                                   | R/W-1            | R/W-1  | R/W-1 |

| —                                             | —   | —   |       |                                         | SS2R<4:0>        |        |       |

| bit 7                                         |     | ·   |       |                                         |                  |        | bit 0 |

|                                               |     |     |       |                                         |                  |        |       |

| Legend:                                       |     |     |       |                                         |                  |        |       |

| R = Readable bit W = Writable bit U = Unimple |     |     |       | U = Unimpler                            | nented bit, read | as '0' |       |

| -n = Value at POR '1' = Bit is set            |     |     |       | '0' = Bit is cleared x = Bit is unknown |                  |        |       |

| -                                             |     |     |       |                                         |                  |        |       |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 SS2R<4:0>: Assign SPI2 Slave Select Input (SS2) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25 • • • • • • • • • •

00000 = Input tied to RP0

#### U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_ \_\_\_ \_\_\_\_ \_\_\_\_ bit 15 bit 8 U-0 U-0 U-0 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 C1RXR<4:0> bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' '1' = Bit is set -n = Value at POR '0' = Bit is cleared x = Bit is unknown

#### REGISTER 11-20: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26<sup>(1)</sup>

bit 15-5 Unimplemented: Read as '0'

**Note 1:** This register is disabled on devices without an ECAN<sup>™</sup> module.

| U-0                                | U-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                               | R/W-0                                                                                                                               | R/W-0                                                                                                 | R/W-0           | R/W-0    |  |  |  |  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------|----------|--|--|--|--|

| _                                  | _                                                                                                                                                                                                                                                                                                                                      | FAOV3H                                                                                                                                                                                                             | FAOV3L                                                                                                                                                                                                              | FAOV2H                                                                                                                              | FAOV2L                                                                                                | FAOV1H          | FAOV1L   |  |  |  |  |

| bit 15                             |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                                                                                                                                                                                                     | 1                                                                                                                                   |                                                                                                       |                 | bit 8    |  |  |  |  |

|                                    |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                                                                                                                                                                                                     |                                                                                                                                     |                                                                                                       |                 |          |  |  |  |  |

| R/W-0                              | U-0                                                                                                                                                                                                                                                                                                                                    | U-0                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                 | U-0                                                                                                                                 | R/W-0                                                                                                 | R/W-0           | R/W-0    |  |  |  |  |

| FLTAM                              | —                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                  | —                                                                                                                                                                                                                   | —                                                                                                                                   | FAEN3                                                                                                 | FAEN2           | FAEN1    |  |  |  |  |

| bit 7                              |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                                                                                                                                                                                                     |                                                                                                                                     |                                                                                                       |                 | bit      |  |  |  |  |

| Legend:                            |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                                                                                                                                                                                                     |                                                                                                                                     |                                                                                                       |                 |          |  |  |  |  |

| R = Readab                         | le bit                                                                                                                                                                                                                                                                                                                                 | W = Writable                                                                                                                                                                                                       | bit                                                                                                                                                                                                                 | U = Unimpler                                                                                                                        | nented bit, rea                                                                                       | d as '0'        |          |  |  |  |  |

| -n = Value a                       | t POR                                                                                                                                                                                                                                                                                                                                  | '1' = Bit is set                                                                                                                                                                                                   |                                                                                                                                                                                                                     | '0' = Bit is cle                                                                                                                    | ared                                                                                                  | x = Bit is unkr | iown     |  |  |  |  |

|                                    |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                                                                                                                                                                                                     |                                                                                                                                     |                                                                                                       |                 |          |  |  |  |  |

| bit 15-14                          | Unimplemen                                                                                                                                                                                                                                                                                                                             | ted: Read as '                                                                                                                                                                                                     | 0'                                                                                                                                                                                                                  |                                                                                                                                     |                                                                                                       |                 |          |  |  |  |  |

| bit 13-8                           | EA OV/vUZ214                                                                                                                                                                                                                                                                                                                           | FAOVxH<3:1>:FAOVxL<3:1>: Fault Input A PWM Override Value bits                                                                                                                                                     |                                                                                                                                                                                                                     |                                                                                                                                     |                                                                                                       |                 |          |  |  |  |  |

|                                    |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                                                                                                                                                                                                     |                                                                                                                                     |                                                                                                       |                 |          |  |  |  |  |

| 2.0 0                              | 1 = The PWN                                                                                                                                                                                                                                                                                                                            | l output pin is c                                                                                                                                                                                                  | lriven active c                                                                                                                                                                                                     | it A PWM Over<br>on an external F<br>on an external                                                                                 | ault input eve                                                                                        |                 |          |  |  |  |  |

| bit 7                              | 1 = The PWN                                                                                                                                                                                                                                                                                                                            | l output pin is c<br>l output pin is c                                                                                                                                                                             | lriven active c                                                                                                                                                                                                     | on an external F                                                                                                                    | ault input eve                                                                                        |                 |          |  |  |  |  |

|                                    | 1 = The PWN<br>0 = The PWM<br><b>FLTAM:</b> Fault<br>1 = The Fault                                                                                                                                                                                                                                                                     | l output pin is c<br>l output pin is c<br>: A Mode bit<br>A input pin fur                                                                                                                                          | driven active of<br>driven inactive<br>actions in the o                                                                                                                                                             | on an external F<br>on an external<br>Cycle-by-Cycle                                                                                | Fault input eve<br>I Fault input ev<br>mode                                                           |                 | ON<13:8> |  |  |  |  |

| bit 7                              | 1 = The PWN<br>0 = The PWM<br><b>FLTAM:</b> Fault<br>1 = The Fault<br>0 = The Fault                                                                                                                                                                                                                                                    | l output pin is c<br>l output pin is c<br>: A Mode bit<br>A input pin fur                                                                                                                                          | Iriven active of<br>Iriven inactive<br>Inctions in the of<br>Iches all contro                                                                                                                                       | on an external F<br>on an external<br>Cycle-by-Cycle                                                                                | Fault input eve<br>I Fault input ev<br>mode                                                           | rent            | ON<13:8> |  |  |  |  |

|                                    | 1 = The PWM<br>0 = The PWM<br><b>FLTAM:</b> Fault<br>1 = The Fault<br>0 = The Fault<br><b>Unimplemen</b>                                                                                                                                                                                                                               | l output pin is c<br>l output pin is c<br>A Mode bit<br>A input pin fur<br>A input pin late                                                                                                                        | driven active of<br>driven inactive<br>actions in the of<br>ches all contro                                                                                                                                         | on an external F<br>on an external<br>Cycle-by-Cycle                                                                                | Fault input eve<br>I Fault input ev<br>mode                                                           | rent            | ON<13:8> |  |  |  |  |

| bit 7<br>bit 6-3                   | 1 = The PWM<br>0 = The PWM<br>FLTAM: Fault<br>1 = The Fault<br>0 = The Fault<br>Unimplemen<br>FAEN3: Fault                                                                                                                                                                                                                             | l output pin is o<br>l output pin is o<br>A Mode bit<br>A input pin fur<br>A input pin lato<br><b>ted:</b> Read as f<br>Input A Enable                                                                             | driven active of<br>driven inactive<br>notions in the of<br>ches all contro<br>0'<br>e bit                                                                                                                          | on an external F<br>on an external<br>Cycle-by-Cycle                                                                                | ault input eve<br>I Fault input ev<br>mode<br>ogrammed sta                                            | rent            | ON<13:8> |  |  |  |  |

| bit 7<br>bit 6-3                   | <ol> <li>1 = The PWM</li> <li>0 = The PWM</li> <li>FLTAM: Fault</li> <li>1 = The Fault</li> <li>0 = The Fault</li> <li>Unimplemen</li> <li>FAEN3: Fault</li> <li>1 = PWMxH3</li> </ol>                                                                                                                                                 | l output pin is c<br>l output pin is c<br>A Mode bit<br>A input pin fur<br>A input pin late<br><b>ted:</b> Read as '<br>Input A Enable<br>/PWMxL3 pin p                                                            | driven active of<br>driven inactive<br>notions in the<br>ches all contro<br>0'<br>e bit<br>pair is controlle                                                                                                        | on an external F<br>on an external<br>Cycle-by-Cycle<br>ol pins to the pr                                                           | ault input eve<br>I Fault input ev<br>mode<br>ogrammed sta<br>ut A                                    | rent            | ON<13:8> |  |  |  |  |

| bit 7<br>bit 6-3<br>bit 2          | 1 = The PWM<br>0 = The PWM<br><b>FLTAM:</b> Fault<br>1 = The Fault<br>0 = The Fault<br><b>Unimplemen</b><br><b>FAEN3:</b> Fault<br>1 = PWMxH3<br>0 = PWMxH3<br>FAEN2: Fault                                                                                                                                                            | l output pin is c<br>l output pin is c<br>A Mode bit<br>A input pin fur<br>A input pin lat<br><b>ted:</b> Read as f<br>Input A Enable<br>/PWMxL3 pin p<br>Input A Enable                                           | driven active of<br>driven inactive<br>octions in the o<br>ches all contro<br>o'<br>e bit<br>pair is controllo<br>pair is not con<br>e bit                                                                          | on an external F<br>on an external<br>Cycle-by-Cycle<br>of pins to the pr<br>ed by Fault Inp<br>trolled by Fault                    | Fault input eve<br>I Fault input ev<br>mode<br>ogrammed sta<br>ut A<br>Input A                        | rent            | ON<13:8> |  |  |  |  |

| bit 7<br>bit 6-3<br>bit 2          | <ul> <li>1 = The PWM</li> <li>0 = The PWM</li> <li>FLTAM: Fault</li> <li>1 = The Fault</li> <li>0 = The Fault</li> <li>Unimplemen</li> <li>FAEN3: Fault</li> <li>1 = PWMxH3</li> <li>0 = PWMxH3</li> <li>FAEN2: Fault</li> <li>1 = PWMxH2</li> </ul>                                                                                   | l output pin is c<br>l output pin is c<br>A Mode bit<br>A input pin fur<br>A input pin lat<br>ted: Read as<br>Input A Enable<br>/PWMxL3 pin p<br>Input A Enable<br>/PWMxL2 pin p                                   | driven active of<br>driven inactive<br>actions in the of<br>ches all contro<br>o'<br>e bit<br>pair is controllo<br>pair is not con<br>e bit<br>pair is controllo                                                    | on an external F<br>on an external<br>Cycle-by-Cycle<br>of pins to the pr<br>ed by Fault Inp                                        | Fault input eve<br>I Fault input ev<br>mode<br>ogrammed sta<br>ut A<br>Input A<br>ut A                | rent            | ON<13:8> |  |  |  |  |

| bit 7<br>bit 6-3<br>bit 2<br>bit 1 | <ol> <li>1 = The PWM</li> <li>0 = The PWM</li> <li>FLTAM: Fault</li> <li>1 = The Fault</li> <li>0 = The Fault</li> <li>Unimplemen</li> <li>FAEN3: Fault</li> <li>1 = PWMxH3</li> <li>0 = PWMxH3</li> <li>FAEN2: Fault</li> <li>1 = PWMxH2</li> <li>0 = PWMxH2</li> <li>0 = PWMxH2</li> </ol>                                           | l output pin is c<br>l output pin is c<br>A Mode bit<br>A input pin fur<br>A input pin lat<br>ted: Read as<br>Input A Enable<br>/PWMxL3 pin p<br>Input A Enable<br>/PWMxL2 pin p                                   | driven active of<br>driven inactive<br>octions in the<br>ches all contro<br>o'<br>e bit<br>pair is controllo<br>pair is controllo<br>pair is controllo<br>pair is not con                                           | on an external F<br>on an external<br>Cycle-by-Cycle<br>of pins to the pr<br>ed by Fault Inp<br>trolled by Fault<br>ed by Fault Inp | Fault input eve<br>I Fault input ev<br>mode<br>ogrammed sta<br>ut A<br>Input A<br>ut A                | rent            | ON<13:8> |  |  |  |  |

| bit 7<br>bit 6-3                   | <ul> <li>1 = The PWW</li> <li>0 = The PWW</li> <li>FLTAM: Fault</li> <li>1 = The Fault</li> <li>0 = The Fault</li> <li>Unimplemen</li> <li>FAEN3: Fault</li> <li>1 = PWMxH3</li> <li>0 = PWMxH3</li> <li>FAEN2: Fault</li> <li>1 = PWMxH2</li> <li>0 = PWMxH2</li> <li>0 = PWMxH2</li> <li>FAEN1: Fault</li> <li>1 = PWMxH1</li> </ul> | I output pin is o<br>output pin is o<br>A Mode bit<br>A input pin fur<br>A input pin lato<br>ted: Read as f<br>Input A Enable<br>/PWMxL3 pin p<br>/PWMxL2 pin p<br>/PWMxL2 pin p<br>/PWMxL2 pin p<br>/PWMxL2 pin p | driven active of<br>driven inactive<br>actions in the<br>ches all contro<br>o'<br>e bit<br>pair is controll<br>pair is not con<br>e bit<br>pair is controll<br>pair is not con<br>e bit<br>pair is not con<br>e bit | on an external F<br>on an external<br>Cycle-by-Cycle<br>of pins to the pr<br>ed by Fault Inp<br>trolled by Fault<br>ed by Fault Inp | Fault input eve<br>I Fault input eve<br>mode<br>ogrammed sta<br>ut A<br>Input A<br>Input A<br>Input A | rent            | ON<13:8> |  |  |  |  |

# REGISTER 16-9: PxFLTACON: FAULT A CONTROL REGISTER<sup>(1)</sup>

Note 1: PWM2 supports only one PWM I/O pin pair.

| REGISTER      | 21-13: CIDU                  | JEPNIZ: ECA                                                                                                 |                                                | 4-1 DUFFER       |                                    | EGISTER       |       |  |  |  |

|---------------|------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------|------------------------------------|---------------|-------|--|--|--|

| R/W-0         | R/W-0                        | R/W-0                                                                                                       | R/W-0                                          | R/W-0            | R/W-0                              | R/W-0         | R/W-0 |  |  |  |

|               | F7B                          | P<3:0>                                                                                                      |                                                |                  | F6BF                               | P<3:0>        |       |  |  |  |

| bit 15        |                              |                                                                                                             |                                                |                  |                                    |               | bit 8 |  |  |  |

| R/W-0         | R/W-0                        | R/W-0                                                                                                       | R/W-0                                          | R/W-0            | R/W-0                              | R/W-0         | R/W-0 |  |  |  |

|               | F5B                          | P<3:0>                                                                                                      |                                                |                  | F4BF                               | P<3:0>        |       |  |  |  |

| bit 7         |                              |                                                                                                             |                                                |                  |                                    |               | bit 0 |  |  |  |

| Legend:       |                              |                                                                                                             |                                                |                  |                                    |               |       |  |  |  |

| R = Readabl   | le bit                       | W = Writable                                                                                                | bit                                            | U = Unimpler     | U = Unimplemented bit, read as '0' |               |       |  |  |  |

| -n = Value at | t POR                        | '1' = Bit is set                                                                                            |                                                | '0' = Bit is cle | x = Bit is unki                    | it is unknown |       |  |  |  |

| bit 15-12     | 1111 = Filte<br>1110 = Filte | : RX Buffer Mas<br>er hits received in<br>er hits received in<br>er hits received in<br>er hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | 4                |                                    |               |       |  |  |  |

| bit 11-8      | F6BP<3:0>                    | : RX Buffer Mas                                                                                             | k for Filter 6 (                               | same values as   | bit 15-12)                         |               |       |  |  |  |

| bit 7-4       | F5BP<3:0>                    | : RX Buffer Mas                                                                                             | k for Filter 5 (                               | same values as   | bit 15-12)                         |               |       |  |  |  |

|               |                              |                                                                                                             |                                                |                  |                                    |               |       |  |  |  |

# REGISTER 21-13: CIBUFPNT2: ECAN™ FILTER 4-7 BUFFER POINTER REGISTER

| bit 3-0 | F4BP<3:0>: RX Buffer Mask for Filter 4 | (same values as bit 15-12) |

|---------|----------------------------------------|----------------------------|

|         |                                        | · /                        |

### REGISTER 21-14: CIBUFPNT3: ECAN™ FILTER 8-11 BUFFER POINTER REGISTER

| R/W-0           | R/W-0                                    | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0           | R/W-0            |  |  |  |

|-----------------|------------------------------------------|------------------|-------------------|------------------|-----------------|-----------------|------------------|--|--|--|

|                 | F11BF                                    | P<3:0>           |                   | F10BP<3:0>       |                 |                 |                  |  |  |  |

| bit 15          |                                          |                  |                   | ·                |                 |                 | bit 8            |  |  |  |

|                 |                                          |                  |                   |                  |                 |                 |                  |  |  |  |

| R/W-0           | R/W-0                                    | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0           | R/W-0            |  |  |  |

|                 | F9BP                                     | <3:0>            |                   |                  | F8B             | P<3:0>          |                  |  |  |  |

| bit 7           |                                          |                  |                   |                  |                 |                 | bit 0            |  |  |  |

|                 |                                          |                  |                   |                  |                 |                 |                  |  |  |  |

| Legend:         |                                          |                  |                   |                  |                 |                 |                  |  |  |  |

| R = Readable    | bit                                      | W = Writable     | bit               | U = Unimpler     | nented bit, rea | id as '0'       |                  |  |  |  |

| -n = Value at P | OR                                       | '1' = Bit is set |                   | '0' = Bit is cle | ared            | x = Bit is unkr | = Bit is unknown |  |  |  |

|                 |                                          |                  |                   |                  |                 |                 |                  |  |  |  |

| bit 15-12       | F11BP<3:0>: RX Buffer Mask for Filter 11 |                  |                   |                  |                 |                 |                  |  |  |  |

|                 |                                          | hits received in |                   |                  |                 |                 |                  |  |  |  |

|                 | 1110 = Filter                            | hits received ir | n RX Buffer 14    | 1                |                 |                 |                  |  |  |  |

|                 | •                                        |                  |                   |                  |                 |                 |                  |  |  |  |

|                 | •                                        |                  |                   |                  |                 |                 |                  |  |  |  |

|                 | •                                        |                  |                   |                  |                 |                 |                  |  |  |  |

|                 |                                          | hits received ir |                   |                  |                 |                 |                  |  |  |  |

|                 | 0000 = Filter                            | hits received ir | n RX Buffer 0     |                  |                 |                 |                  |  |  |  |

| bit 11-8        | F10BP<3:0>                               | : RX Buffer Ma   | sk for Filter 10  | ) (same values   | as bit 15-12)   |                 |                  |  |  |  |

| bit 7-4         | F9BP<3:0>:                               | RX Buffer Masl   | k for Filter 9 (s | same values as   | bit 15-12)      |                 |                  |  |  |  |

|                 |                                          |                  |                   |                  |                 |                 |                  |  |  |  |