Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betuils                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20 MIPS                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc802-h-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

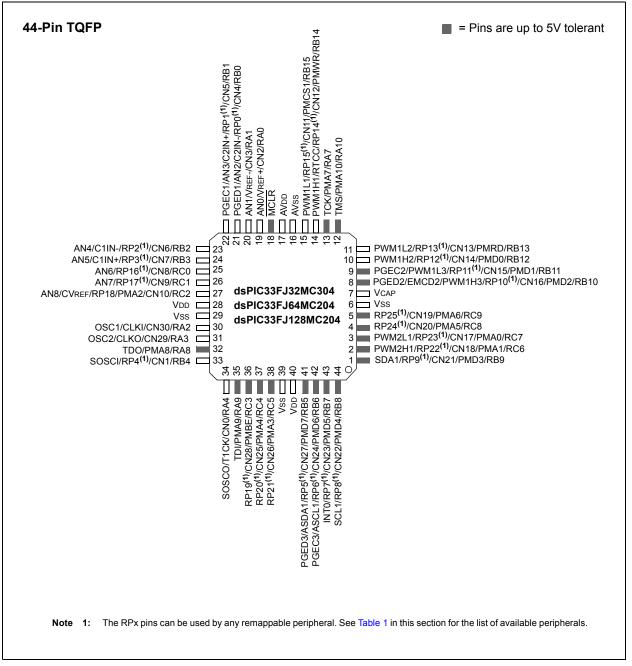

### Pin Diagrams (Continued)

| Pin Name     | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                                                |

|--------------|-------------|----------------|-----|------------------------------------------------------------------------------------------------------------|

| TMS          | Ι           | ST             | No  | JTAG Test mode select pin.                                                                                 |

| ТСК          | Ι           | ST             | No  | JTAG test clock input pin.                                                                                 |

| TDI          | Ι           | ST             | No  | JTAG test data input pin.                                                                                  |

| TDO          | 0           | —              | No  | JTAG test data output pin.                                                                                 |

| INDX1        | Ι           | ST             | Yes | Quadrature Encoder Index1 Pulse input.                                                                     |

| QEA1         | I           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary Timer External Clock/Gate input in Timer mode.    |

| QEB1         | Ι           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary Timer External Clock/Gate input in Timer mode.    |

| UPDN1        | 0           | CMOS           | Yes | Position Up/Down Counter Direction State.                                                                  |

| INDX2        | Ι           | ST             | Yes | Quadrature Encoder Index2 Pulse input.                                                                     |

| QEA2         | Ι           | ST             | Yes | Quadrature Encoder Phase A input in QEI2 mode. Auxiliary Timer<br>External Clock/Gate input in Timer mode. |

| QEB2         | I           | ST             | Yes | Quadrature Encoder Phase A input in QEI2 mode. Auxiliary Timer External Clock/Gate input in Timer mode.    |

| UPDN2        | 0           | CMOS           | Yes | Position Up/Down Counter Direction State.                                                                  |

| C1RX         | I           | ST             | Yes | ECAN1 bus receive pin.                                                                                     |

| C1TX         | 0           | —              | Yes | ECAN1 bus transmit pin.                                                                                    |

| RTCC         | 0           | _              | No  | Real-Time Clock Alarm Output.                                                                              |

| CVREF        | 0           | ANA            | No  | Comparator Voltage Reference Output.                                                                       |

| C1IN-        | Ι           | ANA            | No  | Comparator 1 Negative Input.                                                                               |

| C1IN+        | I           | ANA            | No  | Comparator 1 Positive Input.                                                                               |

| C1OUT        | 0           | _              | Yes | Comparator 1 Output.                                                                                       |

| C2IN-        | Ι           | ANA            | No  | Comparator 2 Negative Input.                                                                               |

| C2IN+        | Ι           | ANA            | No  | Comparator 2 Positive Input.                                                                               |

| C2OUT        | 0           |                | Yes | Comparator 2 Output.                                                                                       |

| PMA0         | I/O         | TTL/ST         | No  | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes).                 |

| PMA1         | I/O         | TTL/ST         | No  | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes).                 |

| PMA2 -PMPA10 | 0           | _              | No  | Parallel Master Port Address (Demultiplexed Master modes).                                                 |

| PMBE         | Ō           |                | No  | Parallel Master Port Byte Enable Strobe.                                                                   |

| PMCS1        | 0           | _              | No  | Parallel Master Port Chip Select 1 Strobe.                                                                 |

| PMD0-PMPD7   | I/O         | TTL/ST         | No  | Parallel Master Port Data (Demultiplexed Master mode) or Address/<br>Data (Multiplexed Master modes).      |

| PMRD         | 0           | _              | No  | Parallel Master Port Read Strobe.                                                                          |

| PMWR         | Ō           | —              | No  | Parallel Master Port Write Strobe.                                                                         |

| DAC1RN       | 0           | _              | No  | DAC1 Negative Output.                                                                                      |

| DAC1RP       | 0           | —              | No  | DAC1 Positive Output.                                                                                      |

| DAC1RM       | 0           |                | No  | DAC1 Output indicating middle point value (typically 1.65V).                                               |

| DAC2RN       | 0           |                | No  | DAC2 Negative Output.                                                                                      |

| DAC2RP       | 0           | —              | No  | DAC2 Positive Output.                                                                                      |

| DAC2RM       | 0           | 1              | No  | DAC2 Output indicating middle point value (typically 1.65V).                                               |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog inputP = PoweO = OutputI = InputTTL = TTL input buffer

| REGISTER     | 7-7: IFS2:                                                                                                             | NTERRUPT                          | FLAG STAT        | US REGISTI          | ER 2                  |                |         |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|---------------------|-----------------------|----------------|---------|--|--|--|

| U-0          | R/W-0                                                                                                                  | R/W-0                             | U-0              | U-0                 | U-0                   | U-0            | U-0     |  |  |  |

|              | DMA4IF                                                                                                                 | PMPIF                             |                  | —                   |                       | _              | _       |  |  |  |

| bit 15       |                                                                                                                        |                                   |                  |                     |                       |                | bit     |  |  |  |

| U-0          | U-0                                                                                                                    | U-0                               | R/W-0            | R/W-0               | R/W-0                 | R/W-0          | R/W-0   |  |  |  |

|              | _                                                                                                                      | _                                 | DMA3IF           | C1IF <sup>(1)</sup> | C1RXIF <sup>(1)</sup> | SPI2IF         | SPI2EIF |  |  |  |

| bit 7        |                                                                                                                        |                                   |                  |                     |                       |                | bit     |  |  |  |

| Legend:      |                                                                                                                        |                                   |                  |                     |                       |                |         |  |  |  |

| R = Readab   | le bit                                                                                                                 | W = Writable                      | bit              | U = Unimplei        | mented bit, read      | as '0'         |         |  |  |  |

| -n = Value a | t POR                                                                                                                  | '1' = Bit is se                   | t                | '0' = Bit is cle    | eared                 | x = Bit is unk | nown    |  |  |  |

| bit 14       | 1 = Interrupt                                                                                                          | request has or                    | curred           | Complete Interr     | rupt Flag Status I    | bit            |         |  |  |  |

|              | 0 = Interrupt request has not occurred                                                                                 |                                   |                  |                     |                       |                |         |  |  |  |

| bit 13       | <b>PMPIF:</b> Parallel Master Port Interrupt Flag Status bit<br>1 = Interrupt request has occurred                     |                                   |                  |                     |                       |                |         |  |  |  |

|              |                                                                                                                        | request has our                   |                  |                     |                       |                |         |  |  |  |

| bit 12-5     | •                                                                                                                      | ted: Read as                      |                  |                     |                       |                |         |  |  |  |

| bit 4        | DMA3IF: DM                                                                                                             | A Channel 3 E                     | Data Transfer C  | Complete Interr     | rupt Flag Status I    | oit            |         |  |  |  |

|              |                                                                                                                        | request has or                    |                  |                     |                       |                |         |  |  |  |

|              | •                                                                                                                      | request has no                    |                  | (4)                 |                       |                |         |  |  |  |

| bit 3        |                                                                                                                        |                                   | pt Flag Status   | bit <sup>(1)</sup>  |                       |                |         |  |  |  |

|              |                                                                                                                        | request has ou<br>request has no  |                  |                     |                       |                |         |  |  |  |

| bit 2        | •                                                                                                                      | •                                 |                  | errupt Flag Sta     | itus bit(1)           |                |         |  |  |  |

| 5112         | <b>C1RXIF:</b> ECAN1 Receive Data Ready Interrupt Flag Status bit <sup>(1)</sup><br>1 = Interrupt request has occurred |                                   |                  |                     |                       |                |         |  |  |  |

|              | 0 = Interrupt request has not occurred                                                                                 |                                   |                  |                     |                       |                |         |  |  |  |

| bit 1        | SPI2IF: SPI2                                                                                                           | Event Interrup                    | ot Flag Status b | pit                 |                       |                |         |  |  |  |

|              |                                                                                                                        | request has or                    |                  |                     |                       |                |         |  |  |  |

| <b>h</b> # 0 | •                                                                                                                      | request has no                    |                  | L:4                 |                       |                |         |  |  |  |

| bit 0        |                                                                                                                        | 2 Error Interru<br>request has or | pt Flag Status   | JIQ                 |                       |                |         |  |  |  |

|              |                                                                                                                        | request has oc                    |                  |                     |                       |                |         |  |  |  |

|              |                                                                                                                        |                                   |                  |                     |                       |                |         |  |  |  |

# REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

Note 1: Interrupts are disabled on devices without an ECAN<sup>™</sup> module.

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| bit 10 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Jnimplement<br>CMPMD: Con<br>= Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                              | R/W-0<br>QEI2MD<br>W = Writable<br>'1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is di<br>or module is enable<br>dule is enable | <sup>0'</sup><br>le Disable bit<br>isabled<br>nabled<br>sable bit       | U-0<br>—<br>U = Unimple<br>'0' = Bit is cle | U-0<br>U-0       | U-0<br>U-0<br>d as '0'<br>x = Bit is unkn | PMPMD<br>bit 8<br>U-0<br>bit 0 |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------|------------------|-------------------------------------------|--------------------------------|--|--|

| R/W-0         CRCMD         bit 7         Legend:         R = Readable b         -n = Value at PC         bit 15-11       L         bit 15-11       L         bit 15-11       L         bit 10       C         Dit 15       L         bit 10       C         bit 3       F         bit 4       1         Dit 7       C         Dit 7       C                                                                                                                                                                | DAC1MD<br>iit<br>DR<br>Jnimplement<br>CMPMD: Con<br>. = Comparate<br>. = Comparate<br>Comparate<br>CMPMD: RT<br>. = RTCC mo<br>. = RTCC mo | QEI2MD<br>W = Writable<br>'1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                | PWM2MD<br>bit<br>0'<br>le Disable bit<br>isabled<br>nabled<br>sable bit | U = Unimple                                 | mented bit, read | d as '0'                                  | U-0<br>—<br>bit 0              |  |  |

| CRCMD           bit 7           Legend:           R = Readable b           -n = Value at PC           bit 15-11         L           bit 10         C           bit 10         L           0         1           0         1           0         0           bit 8         F           1         0           bit 7         C           bit 7         1 | DAC1MD<br>iit<br>DR<br>Jnimplement<br>CMPMD: Con<br>. = Comparate<br>. = Comparate<br>Comparate<br>CMPMD: RT<br>. = RTCC mo<br>. = RTCC mo | QEI2MD<br>W = Writable<br>'1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                | PWM2MD<br>bit<br>0'<br>le Disable bit<br>isabled<br>nabled<br>sable bit | U = Unimple                                 | mented bit, read | d as '0'                                  | bit 0                          |  |  |

| CRCMD           bit 7           Legend:           R = Readable b           -n = Value at PC           bit 15-11         L           bit 10         C           bit 10         L           0         1           0         1           0         0           bit 8         F           1         0           bit 7         C           bit 7         1 | DAC1MD<br>iit<br>DR<br>Jnimplement<br>CMPMD: Con<br>. = Comparate<br>. = Comparate<br>Comparate<br>CMPMD: RT<br>. = RTCC mo<br>. = RTCC mo | QEI2MD<br>W = Writable<br>'1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                | PWM2MD<br>bit<br>0'<br>le Disable bit<br>isabled<br>nabled<br>sable bit | U = Unimple                                 | mented bit, read | d as '0'                                  | bit 0                          |  |  |

| bit 7<br>Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15-11 L<br>bit 10 C<br>bit 9 F<br>1<br>0<br>bit 8 F<br>1<br>0<br>bit 8 F<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                                                                                                                                                                                                                                                                                | it<br>DR<br>Jnimplement<br>CMPMD: Con<br>= Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                  | W = Writable<br>'1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                          | bit<br>0'<br>le Disable bit<br>isabled<br>nabled<br>sable bit           | -                                           |                  |                                           |                                |  |  |

| Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15-11 L<br>bit 10 C<br>1<br>0<br>bit 9 F<br>1<br>0<br>bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                     | Jnimplement<br>CMPMD: Con<br>= Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                              | '1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                                          | <sup>0'</sup><br>le Disable bit<br>isabled<br>nabled<br>sable bit       | -                                           |                  |                                           |                                |  |  |

| R = Readable b<br>-n = Value at PC<br>bit 15-11 L<br>bit 10 C<br>bit 9 F<br>bit 8 F<br>bit 8 F<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                   | Jnimplement<br>CMPMD: Con<br>= Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                              | '1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                                          | <sup>0'</sup><br>le Disable bit<br>isabled<br>nabled<br>sable bit       | -                                           |                  |                                           | own                            |  |  |

| R = Readable b<br>-n = Value at PC<br>bit 15-11 L<br>bit 10 C<br>bit 9 F<br>bit 8 F<br>bit 8 F<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                   | Jnimplement<br>CMPMD: Con<br>= Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                              | '1' = Bit is set<br>ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>'CC Module Di<br>dule is disable                                          | <sup>0'</sup><br>le Disable bit<br>isabled<br>nabled<br>sable bit       | -                                           |                  |                                           | own                            |  |  |

| bit 15-11 L<br>bit 10 C<br>bit 9 F<br>bit 8 F<br>bit 8 F<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                         | Jnimplement<br>CMPMD: Con<br>= Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                              | ted: Read as '<br>nparator Modu<br>or module is di<br>or module is e<br>CC Module Di<br>dule is disable                                                               | <sup>0'</sup><br>le Disable bit<br>isabled<br>nabled<br>sable bit       | -                                           |                  |                                           | own                            |  |  |

| bit 10 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CMPMD: Con<br>= Comparate<br>= Comparate<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                                           | nparator Modu<br>or module is di<br>or module is e<br>CC Module Di<br>dule is disable                                                                                 | le Disable bit<br>isabled<br>nabled<br>sable bit                        |                                             |                  |                                           |                                |  |  |

| bit 10 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CMPMD: Con<br>= Comparate<br>= Comparate<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                                           | nparator Modu<br>or module is di<br>or module is e<br>CC Module Di<br>dule is disable                                                                                 | le Disable bit<br>isabled<br>nabled<br>sable bit                        |                                             |                  |                                           |                                |  |  |

| bit 9 F<br>1<br>0<br>bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                           | = Comparat<br>= Comparat<br>RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                                                           | or module is d<br>or module is e<br>CC Module Di<br>dule is disable                                                                                                   | isabled<br>nabled<br>sable bit                                          |                                             |                  |                                           |                                |  |  |

| bit 9 F<br>1<br>0<br>bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                           | = Comparat<br><b>RTCCMD:</b> RT<br>= RTCC mo<br>= RTCC mo                                                                                  | or module is e<br>CC Module Di<br>dule is disable                                                                                                                     | nabled<br>sable bit                                                     |                                             |                  |                                           |                                |  |  |

| bit 9 F<br>1<br>0<br>bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RTCCMD: RT<br>= RTCC mo<br>= RTCC mo                                                                                                       | CC Module Di<br>dule is disable                                                                                                                                       | sable bit                                                               |                                             |                  |                                           |                                |  |  |

| 1<br>0<br>bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | = RTCC mo<br>= RTCC mo                                                                                                                     | dule is disable                                                                                                                                                       |                                                                         |                                             |                  |                                           |                                |  |  |

| 0<br>bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | = RTCC mo                                                                                                                                  |                                                                                                                                                                       | d                                                                       |                                             |                  |                                           |                                |  |  |

| bit 8 F<br>1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                            |                                                                                                                                                                       | h                                                                       |                                             |                  |                                           |                                |  |  |

| 1<br>0<br>bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                            | P Module Disal                                                                                                                                                        |                                                                         |                                             |                  |                                           |                                |  |  |

| bit 7 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | = PMP mod                                                                                                                                  | ule is disabled                                                                                                                                                       |                                                                         |                                             |                  |                                           |                                |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | = PMP mod                                                                                                                                  | ule is enabled                                                                                                                                                        |                                                                         |                                             |                  |                                           |                                |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CRCMD: CRC                                                                                                                                 | C Module Disal                                                                                                                                                        | ble bit                                                                 |                                             |                  |                                           |                                |  |  |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                            | ule is disabled                                                                                                                                                       |                                                                         |                                             |                  |                                           |                                |  |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                            | ule is enabled                                                                                                                                                        |                                                                         |                                             |                  |                                           |                                |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                            | C1 Module Dis                                                                                                                                                         |                                                                         |                                             |                  |                                           |                                |  |  |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                            | dule is disable<br>dule is enableo                                                                                                                                    |                                                                         |                                             |                  |                                           |                                |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                            | 2 Module Disa                                                                                                                                                         |                                                                         |                                             |                  |                                           |                                |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                            | lule is disabled                                                                                                                                                      |                                                                         |                                             |                  |                                           |                                |  |  |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | = QEI2 mod                                                                                                                                 | lule is enabled                                                                                                                                                       |                                                                         |                                             |                  |                                           |                                |  |  |

| bit 4 F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PWM2MD: PV                                                                                                                                 | VM2 Module D                                                                                                                                                          | Disable bit                                                             |                                             |                  |                                           |                                |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                            |                                                                                                                                                                       |                                                                         |                                             |                  |                                           |                                |  |  |

| bit 3-0 L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                            |                                                                                                                                                                       | 1 = PWM2 module is disabled<br>0 = PWM2 module is enabled               |                                             |                  |                                           |                                |  |  |

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| REGISTER      | 11-4: RPINF                                | R4: PERIPHEI                                                             | RAL PIN SE    | ELECT INPU       | T REGISTER      | 4               |       |

|---------------|--------------------------------------------|--------------------------------------------------------------------------|---------------|------------------|-----------------|-----------------|-------|

| U-0           | U-0                                        | U-0                                                                      | R/W-1         | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| —             | —                                          | _                                                                        |               |                  | T5CKR<4:0       | >               |       |

| bit 15        |                                            | ·                                                                        |               |                  |                 |                 | bit   |

| U-0           | U-0                                        | U-0                                                                      | R/W-1         | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| _             |                                            | _                                                                        |               |                  | T4CKR<4:0       | >               |       |

| bit 7         |                                            |                                                                          |               |                  |                 |                 | bit ( |

| Legend:       |                                            |                                                                          |               |                  |                 |                 |       |

| R = Readabl   | le bit                                     | W = Writable                                                             | oit           | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value at | t POR                                      | '1' = Bit is set                                                         |               | '0' = Bit is cle | eared           | x = Bit is unki | nown  |

|               | 11001 = Inpo<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to Vss<br>ut tied to RP25<br>ut tied to RP1<br>ut tied to RP0    |               |                  |                 |                 |       |

| bit 7-5       | Unimplemer                                 | nted: Read as '                                                          | )'            |                  |                 |                 |       |

| bit 4-0       | 11111 = Inpr<br>11001 = Inpr<br>•          | <ul> <li>Assign Timera<br/>ut tied to Vss<br/>ut tied to RP25</li> </ul> | t External Cl | ock (T4CK) to t  | the correspond  | ling RPn pin    |       |

|               |                                            | ut tied to RP1                                                           |               |                  |                 |                 |       |

00000 = Input tied to RP0

| U-0                | U-0                                                      | U-0                                                                          | R/W-1         | R/W-1                             | R/W-1      | R/W-1              | R/W-1 |  |  |  |  |  |  |

|--------------------|----------------------------------------------------------|------------------------------------------------------------------------------|---------------|-----------------------------------|------------|--------------------|-------|--|--|--|--|--|--|

| —                  | _                                                        | _                                                                            |               |                                   | QEB1R<4:0> |                    |       |  |  |  |  |  |  |

| bit 15             | •                                                        |                                                                              |               |                                   |            |                    | bit 8 |  |  |  |  |  |  |

|                    |                                                          |                                                                              |               |                                   |            |                    |       |  |  |  |  |  |  |

| U-0                | U-0                                                      | U-0                                                                          | R/W-1         | R/W-1                             | R/W-1      | R/W-1              | R/W-1 |  |  |  |  |  |  |

|                    | —                                                        | —                                                                            |               |                                   | QEA1R<4:0> |                    |       |  |  |  |  |  |  |

| bit 7              |                                                          |                                                                              |               |                                   |            |                    | bit 0 |  |  |  |  |  |  |

|                    |                                                          |                                                                              |               |                                   |            |                    |       |  |  |  |  |  |  |

| Legend:            |                                                          |                                                                              |               |                                   |            |                    |       |  |  |  |  |  |  |

| R = Readabl        | le bit                                                   | W = Writable I                                                               | oit           | U = Unimplemented bit, read as '0 |            | l as '0'           |       |  |  |  |  |  |  |

| -n = Value at      | t POR                                                    | '1' = Bit is set                                                             |               | '0' = Bit is cleared              |            | x = Bit is unknown |       |  |  |  |  |  |  |

|                    |                                                          |                                                                              |               |                                   |            |                    |       |  |  |  |  |  |  |

| bit 15-13          | Unimplemen                                               | ted: Read as '                                                               | )'            |                                   |            |                    |       |  |  |  |  |  |  |

| bit 12-8           | QEB1R<4:0>                                               | : Assign B (QE                                                               | B1) to the co | rresponding pir                   | I          |                    |       |  |  |  |  |  |  |

|                    | 11111 <b>= Inp</b> u                                     |                                                                              |               |                                   |            |                    |       |  |  |  |  |  |  |

|                    | 11001 <b>= Inpu</b>                                      | ut tied to RP25                                                              |               |                                   |            |                    |       |  |  |  |  |  |  |

|                    | •                                                        |                                                                              |               |                                   |            |                    |       |  |  |  |  |  |  |

|                    | •                                                        |                                                                              |               |                                   |            |                    |       |  |  |  |  |  |  |

|                    |                                                          |                                                                              |               |                                   |            | •                  |       |  |  |  |  |  |  |

|                    | •                                                        |                                                                              |               |                                   |            |                    |       |  |  |  |  |  |  |

|                    | •<br>00001 = Inpu                                        |                                                                              |               |                                   |            |                    |       |  |  |  |  |  |  |

| hit 7 E            | 00000 <b>= Inp</b> u                                     | ut tied to RP0                                                               | \ <b>`</b>    |                                   |            |                    |       |  |  |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen                               | ut tied to RP0<br>Ited: Read as '0                                           |               |                                   |            |                    |       |  |  |  |  |  |  |

| bit 7-5<br>bit 4-0 | 00000 = Inpu<br>Unimplemen<br>QEA1R<4:0>                 | ut tied to RP0<br>Ited: Read as '(<br>-: Assign A (QE                        |               | rresponding pir                   | 1          |                    |       |  |  |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>QEA1R<4:0><br>11111 = Inpu | ut tied to RP0<br><b>Ited:</b> Read as '(<br>Assign A (QE)<br>It tied to Vss |               | rresponding pir                   | I          |                    |       |  |  |  |  |  |  |

| bit 7-5<br>bit 4-0 | 00000 = Inpu<br>Unimplemen<br>QEA1R<4:0><br>11111 = Inpu | ut tied to RP0<br>Ited: Read as '(<br>-: Assign A (QE                        |               | rresponding pir                   | I          |                    |       |  |  |  |  |  |  |

00001 = Input tied to RP1

00000 = Input tied to RP0

| REGISTER           | 13-2: TyCON          | I: TIMER CO                                          | NTROL RE             | GISTER (y = 3                  | 3 or 5)         |                    |       |  |  |  |

|--------------------|----------------------|------------------------------------------------------|----------------------|--------------------------------|-----------------|--------------------|-------|--|--|--|

| R/W-0              | U-0                  | R/W-0                                                | U-0                  | U-0                            | U-0             | U-0                | U-0   |  |  |  |

| TON <sup>(2)</sup> | _                    | TSIDL <sup>(1)</sup>                                 |                      | —                              | _               | —                  | _     |  |  |  |

| bit 15             |                      |                                                      |                      |                                |                 |                    | bit 8 |  |  |  |

|                    |                      |                                                      |                      |                                |                 |                    |       |  |  |  |

| U-0                | R/W-0                | R/W-0                                                | R/W-0                | U-0                            | U-0             | R/W-0              | U-0   |  |  |  |

|                    | TGATE <sup>(2)</sup> | TCKPS<                                               | :1:0> <sup>(2)</sup> | —                              | _               | TCS <sup>(2)</sup> | _     |  |  |  |

| bit 7              |                      |                                                      |                      |                                |                 |                    | bit ( |  |  |  |

| Legend:            |                      |                                                      |                      |                                |                 |                    |       |  |  |  |

| R = Readabl        | e bit                | W = Writable k                                       | oit                  | U = Unimplem                   | nented bit. rea | d as '0'           |       |  |  |  |

| -n = Value at      |                      | '1' = Bit is set                                     | •                    |                                |                 |                    |       |  |  |  |

|                    |                      | 1 Bit io cot                                         |                      |                                |                 | X Bitle dillar     | ••••  |  |  |  |

| bit 15             | TON: Timery          | On bit <sup>(2)</sup>                                |                      |                                |                 |                    |       |  |  |  |

|                    | 1 = Starts 16-       |                                                      |                      |                                |                 |                    |       |  |  |  |

|                    | 0 = Stops 16-        | bit Timerx                                           |                      |                                |                 |                    |       |  |  |  |

| bit 14             | Unimplemen           | ted: Read as 'o                                      | )'                   |                                |                 |                    |       |  |  |  |

| bit 13             | TSIDL: Stop i        | n Idle Mode bit <sup>(</sup>                         | (1)                  |                                |                 |                    |       |  |  |  |

|                    |                      | ue timer operati<br>timer operation                  |                      | vice enters Idle i<br>e        | mode            |                    |       |  |  |  |

| bit 12-7           | Unimplemen           | ted: Read as '0                                      | )'                   |                                |                 |                    |       |  |  |  |

| bit 6              | TGATE: Time          | rx Gated Time                                        | Accumulatio          | n Enable bit <sup>(2)</sup>    |                 |                    |       |  |  |  |

|                    | When TCS =           | 1:                                                   |                      |                                |                 |                    |       |  |  |  |

|                    | •                    | nis bit is ignored.                                  |                      |                                |                 |                    |       |  |  |  |

|                    |                      | When TCS = 0:<br>1 = Gated time accumulation enabled |                      |                                |                 |                    |       |  |  |  |

|                    |                      | e accumulation                                       |                      |                                |                 |                    |       |  |  |  |

| bit 5-4            |                      |                                                      |                      | ale Select bits <sup>(2)</sup> |                 |                    |       |  |  |  |

|                    | 11 = 1:256 pr        | -                                                    |                      |                                |                 |                    |       |  |  |  |

|                    | 10 = 1:64 pre        |                                                      |                      |                                |                 |                    |       |  |  |  |

|                    |                      | 01 = 1:8 prescale value                              |                      |                                |                 |                    |       |  |  |  |

|                    | 00 = 1:1 pres        |                                                      |                      |                                |                 |                    |       |  |  |  |

| bit 3-2            | -                    | ted: Read as '0                                      |                      |                                |                 |                    |       |  |  |  |

| bit 1              |                      | Clock Source S                                       |                      |                                |                 |                    |       |  |  |  |

|                    |                      | clock from TxCk                                      | K pin                |                                |                 |                    |       |  |  |  |

| bit 0              | 0 = Internal cl      | ted: Read as '0                                      | ,,                   |                                |                 |                    |       |  |  |  |

| DILU               | Unimplemen           | ieu: Read as 10                                      | 1                    |                                |                 |                    |       |  |  |  |

# REGISTER 13-2: TyCON: TIMER CONTROL REGISTER (y = 3 or 5)

**Note 1:** When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), these bits have no effect.

### 14.1 Input Capture Resources

Many useful resources related to Input Capture are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532315              |

### 14.1.1 KEY RESOURCES

- Section 12. "Input Capture" (DS70198)

- Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| U-0             | U-0                                                                                                                                                                                                                                                  | U-0                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                                                                                                                        | U-0                                                                                                           | R/W-0                                                             | R/W-0                    | R/W-0      |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------|------------|--|

| _               | _                                                                                                                                                                                                                                                    | —                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                            | _                                                                                                             | IMV<                                                              | <1:0>                    | CEID       |  |

| bit 15          |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                            |                                                                                                               |                                                                   |                          | bit 8      |  |

|                 |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                            |                                                                                                               |                                                                   |                          |            |  |

| R/W-0           | R/W-0                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                      | U-0                                                                                                           | U-0                                                               | U-0                      | U-0        |  |

| QEOUT           |                                                                                                                                                                                                                                                      | QECK<2:0>                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                            | —                                                                                                             | —                                                                 | _                        |            |  |

| bit 7           |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                            |                                                                                                               |                                                                   |                          | bit (      |  |