Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                           |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc802-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Special Function Register Maps** 4.4

#### TABLE 4-1: **CPU CORE REGISTERS MAP**

| DS7029  |  |

|---------|--|

| )1G-pag |  |

| je 42   |  |

| SFR Name | Addr | Bit 15 | Bit 14             | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7        | Bit 6 | Bit 5     | Bit 4           | Bit 3        | Bit 2        | Bit 1   | Bit 0 | All<br>Resets |

|----------|------|--------|--------------------|--------|--------|--------|--------|---------|---------------|--------------|-------|-----------|-----------------|--------------|--------------|---------|-------|---------------|

| WREG0    | 0000 |        |                    |        |        |        |        |         | Working Re    | gister 0     |       |           |                 |              |              |         |       | 0000          |

| WREG1    | 0002 |        |                    |        |        |        |        |         | Working Re    | gister 1     |       |           |                 |              |              |         |       | 0000          |

| WREG2    | 0004 |        |                    |        |        |        |        |         | Working Re    | gister 2     |       |           |                 |              |              |         |       | 0000          |

| WREG3    | 0006 |        |                    |        |        |        |        |         | Working Re    | gister 3     |       |           |                 |              |              |         |       | 0000          |

| WREG4    | 0008 |        |                    |        |        |        |        |         | Working Re    | gister 4     |       |           |                 |              |              |         |       | 0000          |

| WREG5    | 000A |        | Working Register 5 |        |        |        |        |         |               |              |       | 0000      |                 |              |              |         |       |               |

| WREG6    | 000C |        |                    |        |        |        |        |         | Working Re    | gister 6     |       |           |                 |              |              |         |       | 0000          |

| WREG7    | 000E |        |                    |        |        |        |        |         | Working Re    | gister 7     |       |           |                 |              |              |         |       | 0000          |

| WREG8    | 0010 |        |                    |        |        |        |        |         | Working Re    | gister 8     |       |           |                 |              |              |         |       | 0000          |

| WREG9    | 0012 |        |                    |        |        |        |        |         | Working Re    | gister 9     |       |           |                 |              |              |         |       | 0000          |

| WREG10   | 0014 |        |                    |        |        |        |        |         | Working Reg   | jister 10    |       |           |                 |              |              |         |       | 0000          |

| WREG11   | 0016 |        |                    |        |        |        |        |         | Working Reg   | jister 11    |       |           |                 |              |              |         |       | 0000          |

| WREG12   | 0018 |        |                    |        |        |        |        |         | Working Reg   | ister 12     |       |           |                 |              |              |         |       | 0000          |

| WREG13   | 001A |        |                    |        |        |        |        |         | Working Reg   | jister 13    |       |           |                 |              |              |         |       | 0000          |

| WREG14   | 001C |        |                    |        |        |        |        |         | Working Reg   | jister 14    |       |           |                 |              |              |         |       | 0000          |

| WREG15   | 001E |        |                    |        |        |        |        |         | Working Reg   | jister 15    |       |           |                 |              |              |         |       | 0800          |

| SPLIM    | 0020 |        |                    |        |        |        |        | Stac    | k Pointer Lir | nit Register |       |           |                 |              |              |         |       | XXXX          |

| ACCAL    | 0022 |        |                    |        |        |        |        |         | ACCA          | L            |       |           |                 |              |              |         |       | XXXX          |

| ACCAH    | 0024 |        |                    |        |        |        |        |         | ACCA          | Н            |       |           |                 |              |              |         |       | XXXX          |

| ACCAU    | 0026 |        |                    |        | ACCA<  | 39>    |        |         |               |              |       |           | ACO             | CAU          |              |         |       | XXXX          |

| ACCBL    | 0028 |        |                    |        |        |        |        |         | ACCB          | L            |       |           |                 |              |              |         |       | XXXX          |

| ACCBH    | 002A |        |                    |        |        |        |        |         | ACCB          | Н            |       |           |                 |              |              |         |       | XXXX          |

| ACCBU    | 002C |        |                    |        | ACCB<  | 39>    |        |         |               |              |       |           | ACO             | CBU          |              |         |       | XXXX          |

| PCL      | 002E |        |                    |        |        |        |        | Program | Counter Lov   | w Word Reg   | ister |           |                 |              |              |         |       | XXXX          |

| PCH      | 0030 | _      |                    | —      |        |        | —      |         | _             |              |       | Progra    | am Counter      | High Byte R  | Register     |         |       | 0000          |

| TBLPAG   | 0032 | _      | —                  | —      |        |        | _      |         |               |              |       | Table     | Page Addre      | ss Pointer F | Register     |         |       | 0000          |

| PSVPAG   | 0034 | _      |                    | —      |        |        | —      |         | —             |              | Prog  | ram Memor | y Visibility Pa | age Addres   | s Pointer Re | egister |       | 0000          |

| RCOUNT   | 0036 |        |                    |        |        |        |        | Repe    | at Loop Cou   | nter Registe | er    |           |                 |              |              |         |       | XXXX          |

| DCOUNT   | 0038 |        |                    |        |        |        |        |         | DCOUNT<       |              |       |           |                 |              |              |         |       | XXXX          |

| DOSTARTL | 003A |        |                    |        |        |        |        | DOST    | ARTL<15:1     | >            |       |           |                 |              |              |         | 0     | XXXX          |

| DOSTARTH | 003C | _      | —                  | _      | —      | —      | —      | —       | —             | _            | _     |           |                 | DOSTAF       | RTH<5:0>     |         |       | 00xx          |

| DOENDL   | 003E |        |                    |        |        |        |        | DOE     | NDL<15:1>     | •            |       | •         |                 |              |              |         | 0     | XXXX          |

| DOENDH   | 0040 | _      | —                  | —      | —      | —      | —      | —       | —             | _            | —     |           |                 | DOEN         | DH<5:0>      |         |       | 00xx          |

| SR       | 0042 | OA     | OB                 | SA     | SB     | OAB    | SAB    | DA      | DC            | IPL2         | IPL1  | IPL0      | RA              | N            | OV           | Z       | С     | 0000          |

| CORCON   | 0044 | —      | —                  | _      | US     | EDT    |        | DL<2:0> |               | SATA         | SATB  | SATDW     | ACCSAT          | IPL3         | PSV          | RND     | IF    | 0020          |

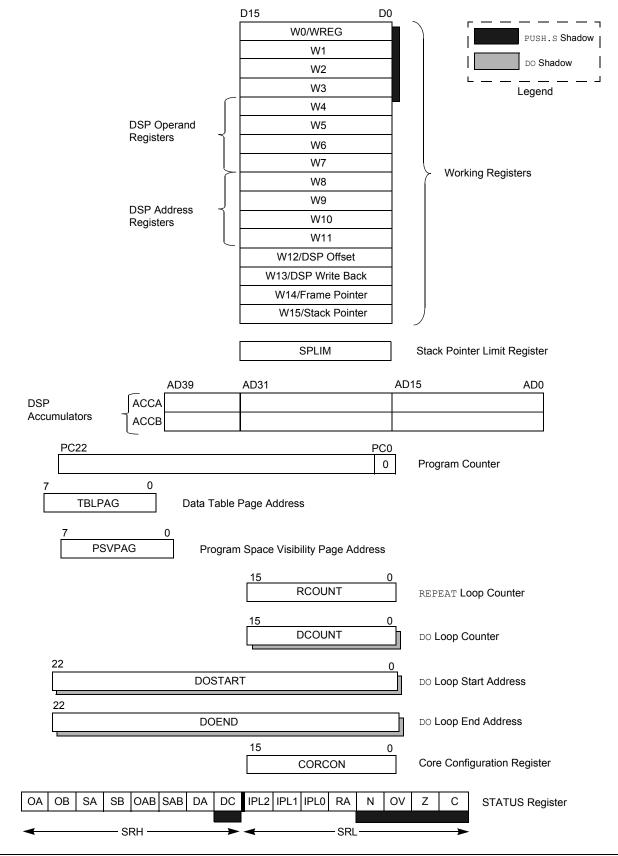

#### 4.8.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDH).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address 0x8000 and higher maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the  ${\tt REPEAT}$  loop allows the instruction using PSV to access data, to execute in a single cycle.

#### FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

#### 5.2 RTSP Operation

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 31-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers sequentially. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

## 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

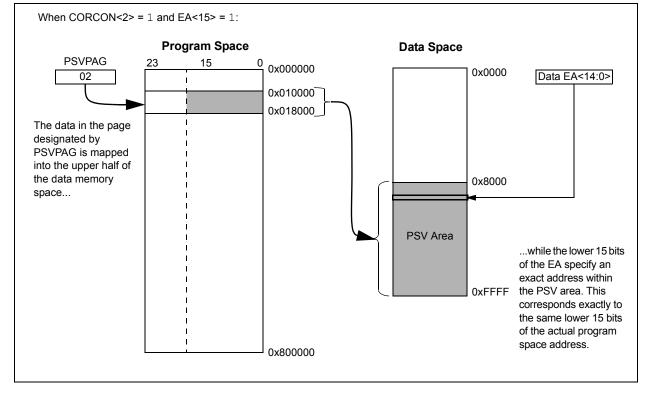

The programming time depends on the FRC accuracy (see Table 31-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time, and Word Write Cycle Time parameters (see Table 31-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm$ 5%. If the TUN<5:0> bits (see Register 9-4) are set to `b111111, the minimum row write time is equal to Equation 5-2.

# EQUATION 5-2: MINIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 1.435 ms$$

The maximum row write time is equal to Equation 5-3.

#### EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \text{ Cycles}}{7.37 \text{ MHz} \times (1 - 0.05) \times (1 - 0.00375)} = 1.586 \text{ms}$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

## 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory:

- NVMCON: The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

- NVMKEY: NVMKEY (Register 5-2) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to Section 5.3 "Programming Operations" for further details.

## 5.5 Flash Programming Resources

Many useful resources related to Flash programming are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532315              |

#### 5.5.1 KEY RESOURCES

- Section 5. "Flash Programming" (DS70191)

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

## 7.3 Interrupt Control and Status Registers

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 devices implement a total of 30 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFSx

- IECx

- IPCx

- INTTREG

#### 7.3.1 INTCON1 AND INTCON2

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS) as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table (AIVT).

#### 7.3.2 IFSx

The IFS registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

#### 7.3.3 IECx

The IEC registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.3.4 IPCx

The IPC registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 7.3.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into vector number bits (VECNUM<6:0>) and Interrupt level bits (ILR<3:0>) in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having vector number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0>, and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

#### 7.3.6 STATUS/CONTROL REGISTERS

Although they are not specifically part of the interrupt control hardware, two of the CPU control registers contain bits that control interrupt functionality.

- The CPU Status register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU interrupt priority level. The user software can change the current CPU priority level by writing to the IPL bits.

- The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU priority level. The IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-32.

## 7.4 Interrupts Resources

Many useful resources related to Interrupts are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the<br>product page using the link above, enter<br>this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en532315                                              |

#### 7.4.1 KEY RESOURCES

- Section 32. "Interrupts (Part III)" (DS70214)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| R/W-0            | R/W-0                                                                                                       | R/W-0                                                                                                                                                | U-0                                                                  | U-0              | R/W-0           | R/W-0            | U-0   |

|------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------|-----------------|------------------|-------|

| FLTA1IF          | RTCIF                                                                                                       | DMA5IF                                                                                                                                               |                                                                      | _                | QEI1IF          | PWM1IF           | _     |

| bit 15           |                                                                                                             |                                                                                                                                                      |                                                                      | ÷                |                 |                  | bit 8 |

|                  |                                                                                                             |                                                                                                                                                      |                                                                      |                  |                 |                  |       |

| U-0              | U-0                                                                                                         | U-0                                                                                                                                                  | U-0                                                                  | U-0              | U-0             | U-0              | U-0   |

|                  | <u> </u>                                                                                                    | —                                                                                                                                                    | _                                                                    |                  |                 | —                | _     |

| bit 7            |                                                                                                             |                                                                                                                                                      |                                                                      |                  |                 |                  | bit ( |

|                  |                                                                                                             |                                                                                                                                                      |                                                                      |                  |                 |                  |       |

| Legend:          |                                                                                                             |                                                                                                                                                      |                                                                      |                  |                 |                  |       |

| R = Readable     | e bit                                                                                                       | W = Writable b                                                                                                                                       | oit                                                                  | U = Unimple      | mented bit, rea | d as '0'         |       |

| -n = Value at    | POR                                                                                                         | '1' = Bit is set                                                                                                                                     |                                                                      | '0' = Bit is cle | eared           | x = Bit is unkno | own   |

| bit 14<br>bit 13 | 0 = Interrupt<br><b>RTCIF:</b> Real<br>1 = Interrupt<br>0 = Interrupt<br><b>DMA5IF:</b> DM<br>1 = Interrupt | request has occ<br>request has not<br>-Time Clock and<br>request has occ<br>request has not<br>IA Channel 5 Da<br>request has occ<br>request has not | occurred<br>Calendar Ir<br>urred<br>occurred<br>ta Transfer<br>urred |                  |                 | s bit            |       |

| bit 12-11        | Unimpleme                                                                                                   | nted: Read as '0                                                                                                                                     | ,                                                                    |                  |                 |                  |       |

| bit 10           | 1 = Interrupt                                                                                               | 1 Event Interrupt<br>request has occ<br>request has not                                                                                              | urred                                                                | s bit            |                 |                  |       |

| bit 9            | PWM1IF: PV                                                                                                  | VM1 Event Interr                                                                                                                                     | upt Flag Sta                                                         | atus bit         |                 |                  |       |

|                  |                                                                                                             | request has occ<br>request has not                                                                                                                   |                                                                      |                  |                 |                  |       |

#### REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

Unimplemented: Read as '0'

bit 8-0

## 8.0 DIRECT MEMORY ACCESS (DMA)

- **Note 1:** This data sheet summarizes the features the dsPIC33FJ32MC302/304, of dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 38. "Direct Memory Access (DMA) (Part III)" (DS70215) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Direct Memory Access (DMA) is a very efficient mechanism of copying data between peripheral SFRs (e.g., UART Receive register, Input Capture 1 buffer), and buffers or variables stored in RAM, with minimal CPU intervention. The DMA controller can automatically copy entire blocks of data without requiring the user software to read or write the peripheral Special Function Registers (SFRs) every time a peripheral interrupt occurs. The DMA controller uses a dedicated bus for data transfers and therefore, does not steal cycles from the code execution flow of the CPU. To exploit the DMA capability, the corresponding user buffers or variables must be located in DMA RAM.

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association         | DMAxREQ Register<br>IRQSEL<6:0> Bits | DMAxPAD Register<br>Values to Read From<br>Peripheral | DMAxPAD Register<br>Values to Write to<br>Peripheral |

|---------------------------------------|--------------------------------------|-------------------------------------------------------|------------------------------------------------------|

| INT0 – External Interrupt 0           | 0000000                              | —                                                     | —                                                    |

| IC1 – Input Capture 1                 | 0000001                              | 0x0140 (IC1BUF)                                       | —                                                    |

| OC1 – Output Compare 1 Data           | 0000010                              | —                                                     | 0x0182 (OC1R)                                        |

| OC1 – Output Compare 1 Secondary Data | 0000010                              | —                                                     | 0x0180 (OC1RS)                                       |

| IC2 – Input Capture 2                 | 0000101                              | 0x0144 (IC2BUF)                                       | —                                                    |

| OC2 – Output Compare 2 Data           | 0000110                              | —                                                     | 0x0188 (OC2R)                                        |

| OC2 – Output Compare 2 Secondary Data | 0000110                              | —                                                     | 0x0186 (OC2RS)                                       |

| TMR2 – Timer2                         | 0000111                              | —                                                     | —                                                    |

| TMR3 – Timer3                         | 0001000                              | —                                                     | —                                                    |

| SPI1 – Transfer Done                  | 0001010                              | 0x0248 (SPI1BUF)                                      | 0x0248 (SPI1BUF)                                     |

| UART1RX – UART1 Receiver              | 0001011                              | 0x0226 (U1RXREG)                                      | —                                                    |

| UART1TX – UART1 Transmitter           | 0001100                              | —                                                     | 0x0224 (U1TXREG)                                     |

| ADC1 – ADC1 Convert Done              | 0001101                              | 0x0300 (ADC1BUF0)                                     | —                                                    |

| UART2RX – UART2 Receiver              | 0011110                              | 0x0236 (U2RXREG)                                      | —                                                    |

| UART2TX – UART2 Transmitter           | 0011111                              | —                                                     | 0x0234 (U2TXREG)                                     |

| SPI2 – Transfer Done                  | 0100001                              | 0x0268 (SPI2BUF)                                      | 0x0268 (SPI2BUF)                                     |

| ECAN1 – RX Data Ready                 | 0100010                              | 0x0440 (C1RXD)                                        | —                                                    |

| PMP - Master Data Transfer            | 0101101                              | 0x0608 (PMDIN1)                                       | 0x0608 (PMDIN1)                                      |

| ECAN1 – TX Data Request               | 1000110                              | —                                                     | 0x0442 (C1TXD)                                       |

| DAC1 - Right Data Output              | 1001110                              | —                                                     | 0x3F6 (DAC1RDAT)                                     |

| DAC2 - Left Data Output               | 1001111                              | —                                                     | 0x03F8 (DAC1LDAT)                                    |

#### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

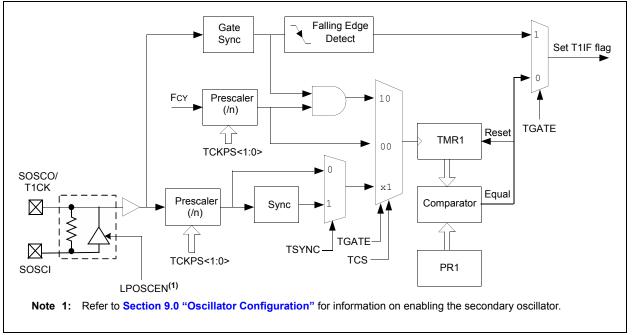

#### 12.0 TIMER1

- This data sheet summarizes the features Note 1: dsPIC33FJ32MC302/304, of the dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated from the low power 32 kHz crystal oscillator available on the device.

- Can be operated in Asynchronous Counter mode from an external clock source.

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler.

The unique features of Timer1 allow it to be used for Real-Time Clock (RTC) applications. A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

#### TABLE 12-1: TIMER MODE SETTINGS

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | Х     |

| Gated timer             | 0   | 1     | х     |

| Synchronous<br>Counter  | 1   | х     | 1     |

| Asynchronous<br>Counter | 1   | х     | 0     |

#### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

| REGISTER           | 13-2: TyCON          | I: TIMER CO                         | NTROL RE             | GISTER (y = 3                  | 3 or 5)         |                    |       |

|--------------------|----------------------|-------------------------------------|----------------------|--------------------------------|-----------------|--------------------|-------|

| R/W-0              | U-0                  | R/W-0                               | U-0                  | U-0                            | U-0             | U-0                | U-0   |

| TON <sup>(2)</sup> | _                    | TSIDL <sup>(1)</sup>                |                      | —                              | _               | —                  | _     |

| bit 15             |                      |                                     |                      |                                |                 |                    | bit 8 |

|                    |                      |                                     |                      |                                |                 |                    |       |

| U-0                | R/W-0                | R/W-0                               | R/W-0                | U-0                            | U-0             | R/W-0              | U-0   |

|                    | TGATE <sup>(2)</sup> | TCKPS<                              | :1:0> <sup>(2)</sup> | —                              | _               | TCS <sup>(2)</sup> | _     |

| bit 7              |                      |                                     |                      |                                |                 |                    | bit ( |

| Legend:            |                      |                                     |                      |                                |                 |                    |       |

| R = Readabl        | e bit                | W = Writable k                      | oit                  | U = Unimplen                   | nented bit. rea | d as '0'           |       |

| -n = Value at      |                      | '1' = Bit is set                    |                      | '0' = Bit is clea              |                 | x = Bit is unkn    | own   |

|                    |                      | 1 Bit io cot                        |                      |                                |                 | X Bitle dillar     | ••••  |

| bit 15             | TON: Timery          | On bit <sup>(2)</sup>               |                      |                                |                 |                    |       |

|                    | 1 = Starts 16-       |                                     |                      |                                |                 |                    |       |

|                    | 0 = Stops 16-        | bit Timerx                          |                      |                                |                 |                    |       |

| bit 14             | Unimplemen           | ted: Read as 'o                     | )'                   |                                |                 |                    |       |

| bit 13             | TSIDL: Stop i        | n Idle Mode bit <sup>(</sup>        | (1)                  |                                |                 |                    |       |

|                    |                      | ue timer operati<br>timer operation |                      | vice enters Idle i<br>e        | mode            |                    |       |

| bit 12-7           | Unimplemen           | ted: Read as '0                     | )'                   |                                |                 |                    |       |

| bit 6              | TGATE: Time          | rx Gated Time                       | Accumulatio          | n Enable bit <sup>(2)</sup>    |                 |                    |       |

|                    | When TCS =           | 1:                                  |                      |                                |                 |                    |       |

|                    | This bit is igno     |                                     |                      |                                |                 |                    |       |

|                    | When TCS =           |                                     | a a a la la al       |                                |                 |                    |       |

|                    |                      | e accumulation<br>e accumulation    |                      |                                |                 |                    |       |

| bit 5-4            |                      |                                     |                      | ale Select bits <sup>(2)</sup> |                 |                    |       |

|                    | 11 = 1:256 pr        | -                                   |                      |                                |                 |                    |       |

|                    | 10 = 1:64 pre        |                                     |                      |                                |                 |                    |       |

|                    | 01 = 1:8 pres        |                                     |                      |                                |                 |                    |       |

|                    | 00 = 1:1 pres        |                                     |                      |                                |                 |                    |       |

| bit 3-2            | -                    | ted: Read as '0                     |                      |                                |                 |                    |       |

| bit 1              |                      | Clock Source S                      |                      |                                |                 |                    |       |

|                    |                      | clock from TxCk                     | K pin                |                                |                 |                    |       |

| bit 0              | 0 = Internal cl      | ted: Read as '0                     | , ,                  |                                |                 |                    |       |

| DILU               | Unimplemen           | ieu: Read as 10                     | 1                    |                                |                 |                    |       |

# REGISTER 13-2: TyCON: TIMER CONTROL REGISTER (y = 3 or 5)

**Note 1:** When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), these bits have no effect.

#### 15.2 Output Compare Resources

Many useful resources related to Output Compare are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

#### 15.2.1 KEY RESOURCES

- Section 13. "Output Compare" (DS70209)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

NOTES:

| REGISTER 1      | 9-2: I2CxS                                           | TAT: I2Cx ST                                                                                            | ATUS REG                                        | STER                                  |                                                  |                                       |                |  |  |  |  |

|-----------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------|--------------------------------------------------|---------------------------------------|----------------|--|--|--|--|

| R-0, HSC        | R-0, HSC                                             | U-0                                                                                                     | U-0                                             | U-0                                   | R/C-0, HS                                        | R-0, HSC                              | R-0, HSC       |  |  |  |  |

| ACKSTAT         | TRSTAT                                               |                                                                                                         |                                                 | _                                     | BCL                                              | GCSTAT                                | ADD10          |  |  |  |  |

| bit 15          |                                                      |                                                                                                         |                                                 | ·                                     |                                                  | ·                                     | bit 8          |  |  |  |  |

| R/C-0, HS       | R/C-0, HS                                            | R-0, HSC                                                                                                | R/C-0, HSC                                      | R/C-0, HSC                            | R-0, HSC                                         | R-0, HSC                              | R-0, HSC       |  |  |  |  |

| IWCOL           | I2COV                                                | D_A                                                                                                     | Р                                               | S                                     | RW                                               | RBF                                   | TBF            |  |  |  |  |

| bit 7           | 1                                                    |                                                                                                         |                                                 | I                                     |                                                  |                                       | bit (          |  |  |  |  |

| Legend:         |                                                      | C = Clear on                                                                                            | ly bit                                          | U = Unimpler                          | nented bit, rea                                  | d as '0'                              |                |  |  |  |  |

| R = Readable    | bit                                                  | W = Writable                                                                                            | -                                               | HS = Set in h                         |                                                  | HSC = Hardw                           | are set/cleare |  |  |  |  |

| -n = Value at P | POR                                                  | '1' = Bit is se                                                                                         | t                                               | '0' = Bit is cle                      | ared                                             | x = Bit is unkr                       |                |  |  |  |  |

|                 | •                                                    |                                                                                                         | •                                               | 0 21010 010                           |                                                  |                                       |                |  |  |  |  |

| bit 15          | (when operat<br>1 = NACK re<br>0 = ACK rece          | cknowledge St<br>ting as I <sup>2</sup> C™ m<br>ceived from sla<br>eived from slav<br>t or clear at end | aster, applica<br>ave<br>e                      |                                       | ransmit operati                                  | on)                                   |                |  |  |  |  |

| bit 14          | <b>TRSTAT:</b> Tra<br>1 = Master tr<br>0 = Master tr | nsmit Status bi<br>ansmit is in pro<br>ansmit is not in                                                 | t (when opera<br>ogress (8 bits -<br>o progress | ting as I <sup>2</sup> C ma<br>+ ACK) |                                                  | e to master trans<br>and of slave Ack | ·              |  |  |  |  |

| bit 13-11       | Unimplemer                                           | nted: Read as                                                                                           | ʻ0 <b>'</b>                                     |                                       |                                                  |                                       |                |  |  |  |  |

| bit 10          | BCL: Master Bus Collision Detect bit                 |                                                                                                         |                                                 |                                       |                                                  |                                       |                |  |  |  |  |

|                 | 0 = No collisi                                       | llision has beer<br>on<br>t at detection o                                                              |                                                 |                                       | peration                                         |                                       |                |  |  |  |  |

| bit 9           | 1 = General (<br>0 = General (                       | neral Call Statu<br>call address wa<br>call address wa<br>t when address                                | as received<br>as not received                  |                                       | ess. Hardware o                                  | clear at Stop dei                     | ection.        |  |  |  |  |

| bit 8           | 1 = 10-bit ad<br>0 = 10-bit ad                       | bit Address Stat<br>dress was mate<br>dress was not i<br>t at match of 2r                               | ched<br>matched                                 | ched 10-bit ad                        | dress. Hardwa                                    | re clear at Stop                      | detection.     |  |  |  |  |

| bit 7           | IWCOL: Writ                                          | e Collision Det                                                                                         | ect bit                                         |                                       |                                                  |                                       |                |  |  |  |  |

|                 | 0 = No collisi                                       | on                                                                                                      | c                                               |                                       | ause the I <sup>2</sup> C mo<br>ousy (cleared by | -                                     |                |  |  |  |  |

| bit 6           |                                                      | vive Overflow F                                                                                         |                                                 |                                       |                                                  | · · · ·                               |                |  |  |  |  |

|                 | 1 = A byte wa<br>0 = No overfl                       | as received wh<br>ow                                                                                    | ile the I2CxR0                                  | -                                     | still holding the                                |                                       |                |  |  |  |  |

| bit 5           |                                                      | ddress bit (whe                                                                                         |                                                 |                                       |                                                  |                                       |                |  |  |  |  |

|                 | 1 = Indicates<br>0 = Indicates                       | that the last by that the last by                                                                       | yte received w<br>yte received w                | vas data<br>vas device add            | ress<br>by reception of                          | slave byte.                           |                |  |  |  |  |

| bit 4           | 0 = Stop bit v                                       | that a Stop bit<br>vas not detecte<br>t or clear when                                                   | ed last                                         |                                       | p detected.                                      |                                       |                |  |  |  |  |

# REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| 511 15  |         |         |         |         |         |        | DIL    |

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLTEN7 | FLTEN6 | FLTEN5 | FLTEN4 | FLTEN3 | FLTEN2 | FLTEN1 | FLTEN0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

FLTENn: Enable Filter n to Accept Messages bits

1 = Enable Filter n

0 = Disable Filter n

#### REGISTER 21-12: CIBUFPNT1: ECAN™ FILTER 0-3 BUFFER POINTER REGISTER

| REGISTER      | ZI-1Z. CIDU         | FFINIT. ECAN                                |                  | U-3 DUFFER                              |                 | EGISTER  |       |  |  |

|---------------|---------------------|---------------------------------------------|------------------|-----------------------------------------|-----------------|----------|-------|--|--|

| R/W-0         | R/W-0               | R/W-0                                       | R/W-0            | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |  |

|               | F3BF                | P<3:0>                                      |                  |                                         | F2BI            | ><3:0>   |       |  |  |

| bit 15        |                     |                                             |                  | -                                       |                 |          | bit 8 |  |  |

|               |                     |                                             |                  |                                         |                 |          |       |  |  |

| R/W-0         | R/W-0               | R/W-0                                       | R/W-0            | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |  |

|               | F1BF                | °<3:0>                                      |                  |                                         | F0BI            | ><3:0>   |       |  |  |

| bit 7         |                     |                                             |                  |                                         |                 |          | bit C |  |  |

| Legend:       |                     |                                             |                  |                                         |                 |          |       |  |  |

| R = Readabl   | le bit              | W = Writable                                | bit              | U = Unimplen                            | nented bit, rea | d as '0' |       |  |  |

| -n = Value at | t POR               | '1' = Bit is set                            |                  | '0' = Bit is cleared x = Bit is unknown |                 |          | nown  |  |  |

|               |                     |                                             |                  |                                         |                 |          |       |  |  |

| bit 15-12     |                     | RX Buffer mas                               |                  |                                         |                 |          |       |  |  |

|               |                     | r hits received ir                          |                  |                                         |                 |          |       |  |  |

|               | 1110 <b>= Filte</b> | 1110 = Filter hits received in RX Buffer 14 |                  |                                         |                 |          |       |  |  |

|               | •                   |                                             |                  |                                         |                 |          |       |  |  |

|               | •                   |                                             |                  |                                         |                 |          |       |  |  |

|               | •                   |                                             |                  |                                         |                 |          |       |  |  |

|               | 0001 = Filte        | r hits received ir                          | n RX Buffer 1    |                                         |                 |          |       |  |  |

|               | 0000 <b>= Filte</b> | r hits received ir                          | n RX Buffer 0    |                                         |                 |          |       |  |  |

| bit 11-8      | F2BP<3:0>:          | RX Buffer mas                               | k for Filter 2 ( | same values as                          | ; bit 15-12)    |          |       |  |  |

| bit 7-4       | F1BP<3:0>:          | RX Buffer mas                               | k for Filter 1 ( | same values as                          | bit 15-12)      |          |       |  |  |

| bit 3-0       |                     | RX Buffer mas                               |                  |                                         |                 |          |       |  |  |

|               |                     |                                             |                  |                                         | - /             |          |       |  |  |

| R/W-0        | U-0                            | U-0              | R/W-0                   | R/W-0                  | R/W-0           | R/W-0          | R/W-0 |

|--------------|--------------------------------|------------------|-------------------------|------------------------|-----------------|----------------|-------|

| ADRC         | _                              | _                |                         |                        | SAMC<4:0>       | 1)             |       |

| bit 15       |                                |                  |                         |                        |                 |                | bit   |

|              |                                |                  |                         |                        |                 |                |       |

| R/W-0        | R/W-0                          | R/W-0            | R/W-0                   | R/W-0                  | R/W-0           | R/W-0          | R/W-0 |

|              |                                |                  | ADCS                    | <7:0> <sup>(2)</sup>   |                 |                |       |

| bit 7        |                                |                  |                         |                        |                 |                | bit   |

| Legend:      |                                |                  |                         |                        |                 |                |       |

| R = Readab   | le bit                         | W = Writable I   | oit                     | U = Unimpler           | nented bit, rea | ad as '0'      |       |

| -n = Value a | t POR                          | '1' = Bit is set |                         | '0' = Bit is cle       |                 | x = Bit is unk | nown  |

|              |                                |                  |                         |                        |                 |                |       |

| bit 15       |                                | Conversion Clo   | ck Source bit           |                        |                 |                |       |

|              |                                | rnal RC clock    |                         |                        |                 |                |       |

|              |                                | rived from syste |                         |                        |                 |                |       |

| bit 14-13    | -                              | nted: Read as '0 |                         |                        |                 |                |       |

| bit 12-8     |                                | : Auto Sample T  | ime bits <sup>(1)</sup> |                        |                 |                |       |

|              | 11111 <b>= 31</b> <sup>-</sup> | Tad              |                         |                        |                 |                |       |

|              | •                              |                  |                         |                        |                 |                |       |

|              | •                              |                  |                         |                        |                 |                |       |

|              | •                              |                  |                         |                        |                 |                |       |

|              | 00001 = 1 TA<br>00000 = 0 TA   |                  |                         |                        |                 |                |       |

| bit 7-0      | ADCS<7:0>:                     | ADC Conversion   | on Clock Sele           | ct bits <sup>(2)</sup> |                 |                |       |

|              | 11111111 =                     | Reserved         |                         |                        |                 |                |       |

|              | •                              |                  |                         |                        |                 |                |       |

|              | •                              |                  |                         |                        |                 |                |       |

|              | •                              |                  |                         |                        |                 |                |       |

|              | •                              |                  |                         |                        |                 |                |       |

|              | 01000000 =                     | Reserved         |                         |                        |                 |                |       |

|              | 00111111 =                     | TCY · (ADCS<7    | 7:0> + 1) = 64          | • TCY = TAD            |                 |                |       |

|              | •                              |                  |                         |                        |                 |                |       |

|              | •                              |                  |                         |                        |                 |                |       |

|              | •                              |                  |                         |                        |                 |                |       |

|              |                                | TCY · (ADCS<7    |                         |                        |                 |                |       |

|              |                                | TCY · (ADCS<7    |                         |                        |                 |                |       |

|              | 00000000 =                     |                  |                         |                        |                 |                |       |

####

2: This bit is not used if AD1CON3<15> (ADRC) = 1.

| U-0           | U-0                                                                                                                                                                           | U-0              | U-0            | U-0                                     | U-0             | U-0       | U-0   |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|-----------------------------------------|-----------------|-----------|-------|--|

| _             | —                                                                                                                                                                             | —                | —              | —                                       | _               | —         | —     |  |

| bit 15        |                                                                                                                                                                               |                  |                |                                         |                 |           | bit 8 |  |

|               |                                                                                                                                                                               |                  |                |                                         |                 |           |       |  |

| R/W-0         | R/W-0                                                                                                                                                                         | R/W-0            | R/W-0          | R/W-0                                   | R/W-0           | R/W-0     | R/W-0 |  |

| CVREN         | CVROE                                                                                                                                                                         | CVRR             | CVRSS          |                                         | CVF             | २<3:0>    |       |  |

| bit 7         |                                                                                                                                                                               |                  |                |                                         |                 |           | bit C |  |

|               |                                                                                                                                                                               |                  |                |                                         |                 |           |       |  |

| Legend:       |                                                                                                                                                                               |                  |                |                                         |                 |           |       |  |

| R = Readable  | e bit                                                                                                                                                                         | W = Writable     | bit            | U = Unimplen                            | nented bit, rea | ıd as '0' |       |  |

| -n = Value at | POR                                                                                                                                                                           | '1' = Bit is set | t              | '0' = Bit is cleared x = Bit is unknown |                 |           |       |  |

|               |                                                                                                                                                                               |                  |                |                                         |                 |           |       |  |

| bit 15-8      | Unimplemen                                                                                                                                                                    | ted: Read as '   | 0'             |                                         |                 |           |       |  |

| bit 7         | CVREN: Comparator Voltage Reference Enable bit                                                                                                                                |                  |                |                                         |                 |           |       |  |

|               | <ul> <li>1 = CVREF circuit powered on</li> <li>0 = CVREF circuit powered down</li> </ul>                                                                                      |                  |                |                                         |                 |           |       |  |

|               |                                                                                                                                                                               |                  |                |                                         |                 |           |       |  |

| bit 6         | CVROE: Comparator VREF Output Enable bit                                                                                                                                      |                  |                |                                         |                 |           |       |  |

|               | <ol> <li>CVREF voltage level is output on CVREF pin</li> <li>CVREF voltage level is disconnected from CVREF pin</li> <li>CVRR: Comparator VREF Range Selection bit</li> </ol> |                  |                |                                         |                 |           |       |  |

| bit 5         |                                                                                                                                                                               |                  |                |                                         |                 |           |       |  |

|               | 1 = CVRSRC range should be 0 to 0.625 CVRSRC with CVRSRC/24 step size                                                                                                         |                  |                |                                         |                 |           |       |  |

|               |                                                                                                                                                                               |                  |                | 9 CVRSRC with                           |                 |           |       |  |

| bit 4         | CVRSS: Comparator VREF Source Selection bit                                                                                                                                   |                  |                |                                         |                 |           |       |  |

|               | 1 = Comparator reference source CVRSRC = VREF+ – VREF-                                                                                                                        |                  |                |                                         |                 |           |       |  |

|               | 0 = Comparator reference source CVRSRC = AVDD – AVSS                                                                                                                          |                  |                |                                         |                 |           |       |  |

| bit 3-0       |                                                                                                                                                                               | •                | EF Value Selec | ction 0 ⊴CVR<3                          | :0> ≤15 bits    |           |       |  |

|               | When CVRR                                                                                                                                                                     |                  |                |                                         |                 |           |       |  |

|               | CVREF = (CVR)                                                                                                                                                                 | <3:0>/ 24) ● (0  | _VRSRC)        |                                         |                 |           |       |  |

#### REGISTER 24-2: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

$\frac{VREF}{CVREF} = (CVRES.0) + (24) \bullet (CVRSRC)$   $\frac{When CVRR}{CVREF} = 1/4 \bullet (CVRSRC) + (CVR < 3:0 > /32) \bullet (CVRSRC)$

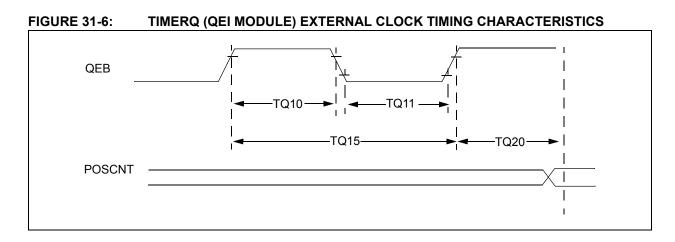

#### TABLE 31-25: QEI MODULE EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                             |                             | (unles | ard Operating<br>s otherwise s<br>ting temperatu | <b>tated)</b><br>ire -40 | °C≤Ta≤  | +85°C fo | /<br>or Industrial<br>for Extended |

|--------------------|-----------|---------------------------------------------|-----------------------------|--------|--------------------------------------------------|--------------------------|---------|----------|------------------------------------|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>               |                             |        | Min                                              | Тур                      | Max     | Units    | Conditions                         |

| TQ10               | TtQH      | TQCK High Time                              | Synchronous, with prescaler |        | Тсү + 20                                         |                          | _       | ns       | Must also meet parameter TQ15      |