Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b; D/A 6x16b                                                        |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc804-e-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-20: DMA REGISTER MAP

| IABLE 4   | +-20. |            | LOISI      |        | F      |        |        |       |       | -         | -     |       |        | -         |       | -     |        |               |

|-----------|-------|------------|------------|--------|--------|--------|--------|-------|-------|-----------|-------|-------|--------|-----------|-------|-------|--------|---------------|

| File Name | Addr  | Bit 15     | Bit 14     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

| DMA0CON   | 0380  | CHEN       | SIZE       | DIR    | HALF   | NULLW  | _      | —     | —     | —         | —     | AMOD  | E<1:0> | _         | _     | MODE  | =<1:0> | 0000          |

| DMA0REQ   | 0382  | FORCE      | _          | —      | _      | —      | —      | _     | _     | —         |       |       |        | RQSEL<6:0 | >     |       |        | 0000          |

| DMA0STA   | 0384  |            |            |        |        |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |        | 0000          |

| DMA0STB   | 0386  |            |            |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |        | 0000          |

| DMA0PAD   | 0388  |            |            |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |        | 0000          |

| DMA0CNT   | 038A  | _          |            | _      | _      | —      | _      |       |       |           |       | CN    | Г<9:0> |           |       |       |        | 0000          |

| DMA1CON   | 038C  | CHEN       | SIZE       | DIR    | HALF   | NULLW  | _      | _     | _     | —         | —     | AMOD  | E<1:0> | —         |       | MODE  | =<1:0> | 0000          |

| DMA1REQ   | 038E  | FORCE      |            | —      | _      | —      | _      | _     | _     | —         |       |       |        | RQSEL<6:0 | >     |       |        | 0000          |

| DMA1STA   | 0390  |            |            |        |        |        |        |       |       |           |       |       | 0000   |           |       |       |        |               |

| DMA1STB   | 0392  |            |            |        |        |        |        |       |       |           |       |       | 0000   |           |       |       |        |               |

| DMA1PAD   | 0394  |            |            |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |        | 0000          |

| DMA1CNT   | 0396  |            |            | —      | _      | —      | _      |       |       |           |       | CN    | Г<9:0> |           |       |       |        | 0000          |

| DMA2CON   | 0398  | CHEN       | SIZE       | DIR    | HALF   | NULLW  | _      | _     | _     | _         | _     | AMOD  | E<1:0> | _         | _     | MODE  | <1:0>  | 0000          |

| DMA2REQ   | 039A  | FORCE      | _          | _      | _      | _      | _      | _     | _     | _         |       |       |        | RQSEL<6:0 | >     |       |        | 0000          |

| DMA2STA   | 039C  |            |            |        |        |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |        | 0000          |

| DMA2STB   | 039E  |            |            |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |        | 0000          |

| DMA2PAD   | 03A0  |            |            |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |        | 0000          |

| DMA2CNT   | 03A2  | _          |            | _      | _      | —      | _      |       |       |           |       | CN    | Г<9:0> |           |       |       |        | 0000          |

| DMA3CON   | 03A4  | CHEN       | SIZE       | DIR    | HALF   | NULLW  | —      | —     | —     | —         | —     | AMOD  | E<1:0> | —         | -     | MODE  | =<1:0> | 0000          |

| DMA3REQ   | 03A6  | FORCE      |            | —      | _      | —      | _      | _     | _     | —         |       |       |        | RQSEL<6:0 | >     |       |        | 0000          |

| DMA3STA   | 03A8  |            |            |        |        |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |        | 0000          |

| DMA3STB   | 03AA  |            |            |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |        | 0000          |

| DMA3PAD   | 03AC  |            |            |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |        | 0000          |

| DMA3CNT   | 03AE  |            |            | —      | _      | —      | _      |       |       |           |       | CN    | Г<9:0> |           |       |       |        | 0000          |

| DMA4CON   | 03B0  | CHEN       | SIZE       | DIR    | HALF   | NULLW  | —      | —     | —     | —         | —     | AMOD  | E<1:0> | —         | -     | MODE  | =<1:0> | 0000          |

| DMA4REQ   | 03B2  | FORCE      | —          | —      | —      | —      | —      | —     | —     | —         |       |       |        | RQSEL<6:0 | >     |       |        | 0000          |

| DMA4STA   | 03B4  |            |            |        |        |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |        | 0000          |

| DMA4STB   | 03B6  |            |            |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |        | 0000          |

| DMA4PAD   | 03B8  |            |            |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |        | 0000          |

| DMA4CNT   | 03BA  |            |            | —      | _      | —      | _      |       |       |           |       | CN    | Г<9:0> |           |       |       |        | 0000          |

| DMA5CON   | 03BC  | CHEN       | SIZE       | DIR    | HALF   | NULLW  | —      | —     | —     | _         | —     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0>  | 0000          |

| DMA5REQ   | 03BE  | FORCE      |            | —      | _      | —      | —      | —     | —     | _         |       |       |        | RQSEL<6:0 | >     |       |        | 0000          |

| DMA5STA   | 03C0  |            |            |        |        |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |        | 0000          |

| DMA5STB   | 03C2  |            |            |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |        | 0000          |

| Legend:   | = 11r | nimplement | ed read as | s 'O'  |        |        |        |       |       |           |       |       |        |           |       |       |        |               |

dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

Legend: — = unimplemented, read as '0'.

#### 5.2 RTSP Operation

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 31-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers sequentially. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

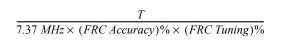

The programming time depends on the FRC accuracy (see Table 31-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time, and Word Write Cycle Time parameters (see Table 31-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm$ 5%. If the TUN<5:0> bits (see Register 9-4) are set to `b111111, the minimum row write time is equal to Equation 5-2.

# EQUATION 5-2: MINIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 1.435 ms$$

The maximum row write time is equal to Equation 5-3.

#### EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \text{ Cycles}}{7.37 \text{ MHz} \times (1 - 0.05) \times (1 - 0.00375)} = 1.586 \text{ms}$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

### 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory:

- NVMCON: The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

- NVMKEY: NVMKEY (Register 5-2) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to Section 5.3 "Programming Operations" for further details.

### 5.5 Flash Programming Resources

Many useful resources related to Flash programming are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532315              |

#### 5.5.1 KEY RESOURCES

- Section 5. "Flash Programming" (DS70191)

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| Symbol | Parameter                        | Value            |  |  |

|--------|----------------------------------|------------------|--|--|

| VPOR   | POR threshold                    | 1.8V nominal     |  |  |

| TPOR   | POR extension time               | 30 μs maximum    |  |  |

| VBOR   | BOR threshold                    | 2.5V nominal     |  |  |

| TBOR   | BOR extension time               | 100 μs maximum   |  |  |

| TPWRT  | Programmable power-up time delay | 0-128 ms nominal |  |  |

| TFSCM  | Fail-Safe Clock Monitor Delay    | 900 μs maximum   |  |  |

| IABLE 6-2: USCILLATUR PARAMETERS | TABLE 6-2: | <b>OSCILLATOR PARAMETERS</b> |

|----------------------------------|------------|------------------------------|

|----------------------------------|------------|------------------------------|

Note: When the device exits the Reset condition (begins normal operation), the device operating parameters (voltage, frequency, temperature, etc.) must be within their operating ranges, otherwise, the device may not function correctly. The user application must ensure that the delay between the time power is first applied, and the time SYSRST becomes inactive, is long enough to get operating parameters all within specification.

#### 6.4 Power-on Reset (POR)

A Power-on Reset (POR) circuit ensures the device is reset from power-on. The POR circuit is active until VDD crosses the VPOR threshold and the delay TPOR has elapsed. The delay TPOR ensures the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to Section 31.0 "Electrical Characteristics" for details.

The POR status bit (POR) in the Reset Control register (RCON<0>) is set to indicate the Power-on Reset.

## 6.4.1 Brown-out Reset (BOR) and Power-up Timer (PWRT)

The on-chip regulator has a Brown-out Reset (BOR) circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses VBOR threshold and the delay TBOR has elapsed. The delay TBOR ensures the voltage regulator output becomes stable.

The BOR status bit (BOR) in the Reset Control register (RCON<1>) is set to indicate the Brown-out Reset.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The PWRT provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

The power-up timer delay (TPWRT) is programmed by the Power-on Reset Timer Value Select bits (FPWRT<2:0>) in the POR Configuration register (FPOR<2:0>), which provides eight settings (from 0 ms to 128 ms). Refer to **Section 28.0 "Special Features"** for further details.

Figure 6-3 shows the typical brown-out scenarios. The reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point

| U-0                       | U-0                                                                                                                                                        | U-0                                                                                                                                                                                                                       | U-0                                                                             | U-0                                              | R/W-1                    | R/W-0           | R/W-0  |  |  |  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------|--------------------------|-----------------|--------|--|--|--|--|

| _                         | _                                                                                                                                                          | _                                                                                                                                                                                                                         |                                                                                 | _                                                |                          | C1TXIP<2:0>(1)  |        |  |  |  |  |

| bit 15                    |                                                                                                                                                            |                                                                                                                                                                                                                           |                                                                                 |                                                  |                          |                 | bit 8  |  |  |  |  |

|                           |                                                                                                                                                            |                                                                                                                                                                                                                           |                                                                                 |                                                  |                          |                 |        |  |  |  |  |

| U-0                       | R/W-1                                                                                                                                                      | R/W-0                                                                                                                                                                                                                     | R/W-0                                                                           | U-0                                              | R/W-1                    | R/W-0           | R/W-0  |  |  |  |  |

| _                         |                                                                                                                                                            | DMA7IP<2:0>                                                                                                                                                                                                               |                                                                                 | —                                                |                          | DMA6IP<2:0>     |        |  |  |  |  |

| bit 7                     |                                                                                                                                                            |                                                                                                                                                                                                                           |                                                                                 |                                                  |                          |                 | bit (  |  |  |  |  |

| Legend:                   |                                                                                                                                                            |                                                                                                                                                                                                                           |                                                                                 |                                                  |                          |                 |        |  |  |  |  |

| R = Readab                | alo hit                                                                                                                                                    | W = Writable                                                                                                                                                                                                              | oit                                                                             |                                                  | nented bit, rea          | nd as '0'       |        |  |  |  |  |

|                           |                                                                                                                                                            |                                                                                                                                                                                                                           | JIL                                                                             | •                                                |                          |                 | 0.11/2 |  |  |  |  |

| -n = Value a              | al POR                                                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                          |                                                                                 | '0' = Bit is cle                                 | ared                     | x = Bit is unkn | OWN    |  |  |  |  |

| bit 15 11                 | Unimplomo                                                                                                                                                  | nted: Read as '                                                                                                                                                                                                           | `,                                                                              |                                                  |                          |                 |        |  |  |  |  |

| bit 15-11                 | -                                                                                                                                                          |                                                                                                                                                                                                                           |                                                                                 |                                                  | <b>D</b> · · · · · · (1) |                 |        |  |  |  |  |

| bit 10-8                  | <b>C1TXIP&lt;2:0&gt;:</b> ECAN1 Transmit Data Request Interrupt Priority bits <sup>(1)</sup><br>111 = Interrupt is priority 7 (highest priority interrupt) |                                                                                                                                                                                                                           |                                                                                 |                                                  |                          |                 |        |  |  |  |  |

|                           |                                                                                                                                                            |                                                                                                                                                                                                                           |                                                                                 |                                                  |                          |                 |        |  |  |  |  |

|                           |                                                                                                                                                            |                                                                                                                                                                                                                           |                                                                                 |                                                  |                          |                 |        |  |  |  |  |

|                           |                                                                                                                                                            |                                                                                                                                                                                                                           |                                                                                 |                                                  |                          |                 |        |  |  |  |  |

|                           |                                                                                                                                                            |                                                                                                                                                                                                                           |                                                                                 |                                                  |                          |                 |        |  |  |  |  |

|                           | 111 = Intern<br>•<br>•<br>•<br>•<br>•                                                                                                                      | upt is priority 7 (I<br>upt is priority 1                                                                                                                                                                                 | nighest priori                                                                  |                                                  |                          |                 |        |  |  |  |  |

|                           | 111 = Intern<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis                                                                                                                                                            | nighest priorii<br>abled                                                        |                                                  |                          |                 |        |  |  |  |  |

| bit 7                     | 111 = Intern<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(                                                                                                                                | nighest priori<br>abled                                                         | ty interrupt)                                    | -                        | rity hits       |        |  |  |  |  |

|                           | 111 = Intern<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '0<br><b>0&gt;:</b> DMA Channe                                                                                                    | nighest priori<br>abled<br>o'<br>el 7 Data Tra                                  | ty interrupt)<br>nsfer Complete                  | -                        | rity bits       |        |  |  |  |  |

| bit 7                     | 111 = Intern<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(                                                                                                                                | nighest priori<br>abled<br>o'<br>el 7 Data Tra                                  | ty interrupt)<br>nsfer Complete                  | -                        | rity bits       |        |  |  |  |  |

| bit 7                     | 111 = Intern<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '0<br><b>0&gt;:</b> DMA Channe                                                                                                    | nighest priori<br>abled<br>o'<br>el 7 Data Tra                                  | ty interrupt)<br>nsfer Complete                  | -                        | rity bits       |        |  |  |  |  |

| bit 7                     | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0<br>111 = Intern                                                                    | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I                                                                             | nighest priori<br>abled<br>o'<br>el 7 Data Tra                                  | ty interrupt)<br>nsfer Complete                  | -                        | rity bits       |        |  |  |  |  |

| bit 7                     | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0<br>111 = Intern<br>001 = Intern                                                    | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt is priority 1                                                        | nighest priori<br>abled<br>o'<br>el 7 Data Tra<br>nighest priori                | ty interrupt)<br>nsfer Complete                  | -                        | rity bits       |        |  |  |  |  |

| bit 7<br>bit 6-4          | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>000 = Intern                                    | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt is priority 1<br>upt source is dis                                   | abled<br>oʻ<br>el 7 Data Tra<br>nighest priorit                                 | ty interrupt)<br>nsfer Complete                  | -                        | rity bits       |        |  |  |  |  |

| bit 7<br>bit 6-4<br>bit 3 | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme                       | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(      | abled<br>)'<br>el 7 Data Tra<br>highest priorit                                 | ty interrupt)<br>nsfer Complete<br>ty interrupt) | Interrupt Prio           |                 |        |  |  |  |  |

| bit 7<br>bit 6-4<br>bit 3 | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0<br>111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA6IP<2:0         | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe | abled<br>o'<br>el 7 Data Tra<br>highest priorit<br>abled<br>o'<br>el 6 Data Tra | ty interrupt)<br>nsfer Complete<br>ty interrupt) | Interrupt Prio           |                 |        |  |  |  |  |

| bit 7<br>bit 6-4<br>bit 3 | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0<br>111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA6IP<2:0         | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(      | abled<br>o'<br>el 7 Data Tra<br>highest priorit<br>abled<br>o'<br>el 6 Data Tra | ty interrupt)<br>nsfer Complete<br>ty interrupt) | Interrupt Prio           |                 |        |  |  |  |  |

| bit 7<br>bit 6-4<br>bit 3 | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0<br>111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA6IP<2:0         | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe | abled<br>o'<br>el 7 Data Tra<br>highest priorit<br>abled<br>o'<br>el 6 Data Tra | ty interrupt)<br>nsfer Complete<br>ty interrupt) | Interrupt Prio           |                 |        |  |  |  |  |

| bit 7<br>bit 6-4<br>bit 3 | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0<br>111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA6IP<2:0         | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe | abled<br>o'<br>el 7 Data Tra<br>highest priorit<br>abled<br>o'<br>el 6 Data Tra | ty interrupt)<br>nsfer Complete<br>ty interrupt) | Interrupt Prio           |                 |        |  |  |  |  |

| bit 7<br>bit 6-4          | <pre>111 = Intern</pre>                                                                                                                                    | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe | abled<br>o'<br>el 7 Data Tra<br>highest priorit<br>abled<br>o'<br>el 6 Data Tra | ty interrupt)<br>nsfer Complete<br>ty interrupt) | Interrupt Prio           |                 |        |  |  |  |  |

#### \_ \_ . \_ \_ \_ \_ \_ \_ \_ \_ .\_ ...

**Note 1:** Interrupts are disabled on devices without an ECAN<sup>™</sup> module.

#### 11.9 Peripheral Pin Select Registers

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 family of devices implement 33 registers for remappable peripheral configuration:

- 20 Input Remappable Peripheral Registers:

- RPINR0-RPINR1, RPINR3-RPINR4, RPINR7, RPINR10-RPINR21, PRINR23, and PRINR26

- 13 Output Remappable Peripheral Registers:

- RPOR0-RPOR12

| Note: | Input and output register values can only |               |       |       |     |       |       |  |

|-------|-------------------------------------------|---------------|-------|-------|-----|-------|-------|--|

|       | be changed if                             |               |       | the   | IOI | OCK   | bit   |  |

|       | (OSCCON<6>)                               |               |       | set   | to  | '0'.  | See   |  |

|       | Sec                                       | tion 11.6.3.1 | I     | "Cont | rol | Reg   | ister |  |

|       | Loc                                       | k" for a spec | cific | comm  | and | seque | ence. |  |

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | —   | —   |       |       | INT1R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

|        |     |     |       |       |            |       |       |

| U-0    | U-0 | U-0 | U-0   | U-0   | U-0        | U-0   | U-0   |

| —      | —   |     |       | —     | —          |       | —     |

| bit 7  |     |     |       |       |            |       | bit 0 |

| Legend:           |                  |                       |                                    |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

| bit 15-13 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

| bit 12-8 | <b>INT1R&lt;4:0&gt;:</b> Assign External Interrupt 1 (INTR1) to the corresponding RPn pin |

|----------|-------------------------------------------------------------------------------------------|

|          | 11111 = Input tied to Vss                                                                 |

|          | 11001 = Input tied to RP25                                                                |

|          | •                                                                                         |

|          | •                                                                                         |

|          | •                                                                                         |

|          | 00001 = Input tied to RP1                                                                 |

|          | 00000 = Input tied to RP0                                                                 |

| bit 7-0  | Unimplemented: Read as '0'                                                                |

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

#### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0                               | U-0 | U-0              | U-0   | U-0                                     | U-0         | U-0   | U-0   |  |

|-----------------------------------|-----|------------------|-------|-----------------------------------------|-------------|-------|-------|--|

|                                   | _   | —                | _     | —                                       | —           | _     | _     |  |

| bit 15                            |     |                  |       |                                         |             |       | bit 8 |  |

|                                   |     |                  |       |                                         |             |       |       |  |

| U-0                               | U-0 | U-0              | R/W-1 | R/W-1                                   | R/W-1       | R/W-1 | R/W-1 |  |

| —                                 | _   | —                |       |                                         | INTR2R<4:0> | •     |       |  |

| bit 7                             |     |                  |       |                                         |             |       | bit 0 |  |

|                                   |     |                  |       |                                         |             |       |       |  |

| Legend:                           |     |                  |       |                                         |             |       |       |  |

| R = Readable bit W = Writable bit |     |                  | bit   | U = Unimplemented bit, read as '0'      |             |       |       |  |

| -n = Value at Po                  | OR  | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |             |       | nown  |  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 INTR2R<4:0>: Assign External Interrupt 2 (INTR2) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25 •

00001 = Input tied to RP1 00000 = Input tied to RP0

| U-0                | U-0                                                                                                  | U-0                                                                    | R/W-1          | R/W-1                | R/W-1           | R/W-1           | R/W-1 |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------|----------------------|-----------------|-----------------|-------|--|--|--|

| _                  | _                                                                                                    |                                                                        |                |                      | SCK1R<4:0       | >               |       |  |  |  |

| bit 15             |                                                                                                      |                                                                        |                |                      |                 |                 | bit   |  |  |  |

| U-0                | U-0                                                                                                  | U-0                                                                    | R/W-1          | R/W-1                | R/W-1           | R/W-1           | R/W-1 |  |  |  |

| _                  | -                                                                                                    |                                                                        |                |                      | SDI1R<4:0>      |                 |       |  |  |  |

| bit 7              |                                                                                                      |                                                                        |                |                      |                 |                 | bit ( |  |  |  |

|                    |                                                                                                      |                                                                        |                |                      |                 |                 |       |  |  |  |

| Legend:            |                                                                                                      |                                                                        |                |                      |                 |                 |       |  |  |  |

| R = Readab         | le bit                                                                                               | W = Writable                                                           | bit            | U = Unimple          | mented bit, rea | ad as '0'       |       |  |  |  |

| -n = Value a       | t POR                                                                                                | '1' = Bit is se                                                        | t              | '0' = Bit is cleared |                 | x = Bit is unki | nown  |  |  |  |

| bit 15-13          | Unimpleme                                                                                            | nted: Read as                                                          | 0'             |                      |                 |                 |       |  |  |  |

|                    | -                                                                                                    |                                                                        |                |                      |                 |                 |       |  |  |  |

| bit 12-8           | SCK1R<4:0>: Assign SPI1 Clock Input (SCK1) to the corresponding RPn pin<br>11111 = Input tied to Vss |                                                                        |                |                      |                 |                 |       |  |  |  |

|                    |                                                                                                      | 11111 = Input tied to VSS<br>11001 = Input tied to RP25                |                |                      |                 |                 |       |  |  |  |

|                    | •                                                                                                    |                                                                        |                |                      |                 |                 |       |  |  |  |

|                    | •                                                                                                    |                                                                        |                |                      |                 |                 |       |  |  |  |

|                    | •                                                                                                    | •                                                                      |                |                      |                 |                 |       |  |  |  |

|                    | 00001 <b>= Inp</b>                                                                                   | 00001 = Input tied to RP1                                              |                |                      |                 |                 |       |  |  |  |

|                    | 00000 <b>= Inp</b>                                                                                   | out tied to RP0                                                        |                |                      |                 |                 |       |  |  |  |

|                    | Unimpleme                                                                                            | nted: Read as                                                          | 0'             |                      |                 |                 |       |  |  |  |

| bit 7-5            | •                                                                                                    | SDI1R<4:0>: Assign SPI1 Data Input (SDI1) to the corresponding RPn pin |                |                      |                 |                 |       |  |  |  |

| bit 7-5<br>bit 4-0 | -                                                                                                    | : Assign SPI1                                                          | Data Input (SD | (in) to the cone     | sponding RFT    | i pili          |       |  |  |  |

|                    | SDI1R<4:0><br>11111 = Inp                                                                            | out tied to Vss                                                        |                |                      |                 | i piri          |       |  |  |  |

|                    | SDI1R<4:0><br>11111 = Inp                                                                            | •                                                                      |                |                      |                 |                 |       |  |  |  |

|                    | SDI1R<4:0><br>11111 = Inp                                                                            | out tied to Vss                                                        |                |                      |                 | , bui           |       |  |  |  |

#### 40 ... DIN SELECT INDUT DECISTED 20

00001 = Input tied to RP1 00000 = Input tied to RP0

# dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

### REGISTER 11-31: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10<sup>(1)</sup>

| U-0                                                                  | U-0 | U-0              | R/W-0      | R/W-0                                   | R/W-0      | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-----|------------------|------------|-----------------------------------------|------------|-------|-------|

|                                                                      | —   | —                |            |                                         | RP21R<4:0> | •     |       |

| bit 15                                                               |     |                  |            |                                         |            |       | bit 8 |

|                                                                      |     |                  |            |                                         |            |       |       |

| U-0                                                                  | U-0 | U-0              | R/W-0      | R/W-0                                   | R/W-0      | R/W-0 | R/W-0 |

|                                                                      | —   | —                | RP20R<4:0> |                                         |            |       |       |

| bit 7                                                                |     |                  |            |                                         |            |       | bit 0 |

|                                                                      |     |                  |            |                                         |            |       |       |

| Legend:                                                              |     |                  |            |                                         |            |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |                  | d as '0'   |                                         |            |       |       |

| -n = Value at P                                                      | OR  | '1' = Bit is set |            | '0' = Bit is cleared x = Bit is unknown |            |       | nown  |

|                                                                      |     |                  |            |                                         |            |       |       |

| bit 15-13 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12-8  | <b>RP21R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP21 Output Pin bits (see Table 11-2 for peripheral function numbers) |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 RP20R<4:0>: Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-2 for peripheral function numbers)

Note 1: This register is implemented in 44-pin devices only.

#### REGISTER 11-32: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11<sup>(1)</sup>

| U-0                                | U-0        | U-0                  | R/W-0        | R/W-0            | R/W-0              | R/W-0             | R/W-0        |

|------------------------------------|------------|----------------------|--------------|------------------|--------------------|-------------------|--------------|

| _                                  |            | —                    |              |                  | RP23R<4:0          | >                 |              |

| bit 15                             |            |                      |              |                  |                    |                   | bit 8        |

|                                    |            |                      |              |                  |                    |                   |              |

| U-0                                | U-0        | U-0                  | R/W-0        | R/W-0            | R/W-0              | R/W-0             | R/W-0        |

| —                                  | —          | —                    |              |                  | RP22R<4:0          | >                 |              |

| bit 7                              |            |                      |              |                  |                    |                   | bit 0        |

|                                    |            |                      |              |                  |                    |                   |              |

| Legend:                            |            |                      |              |                  |                    |                   |              |

| R = Readable                       | bit        | W = Writable b       | oit          | U = Unimplen     | nented bit, rea    | ad as '0'         |              |

| -n = Value at POR '1' = Bit is set |            | '0' = Bit is cleared |              | ared             | x = Bit is unknown |                   |              |

|                                    |            |                      |              |                  |                    |                   |              |

| bit 15-13                          | Unimplemen | ted: Read as 'o      | )'           |                  |                    |                   |              |

| bit 12-8                           | RP23R<4:0> | Peripheral Out       | tput Functio | n is Assigned to | RP23 Output        | Pin bits (see Tal | ole 11-2 for |

peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

Note 1: This register is implemented in 44-pin devices only.

bit 4-0 RP22R<4:0>: Peripheral Output Function is Assigned to RP22 Output Pin bits (see Table 11-2 for peripheral function numbers)

|                      |                                                                                                     | CONTINUE                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U-0                  | U-0                                                                                                 | U-0                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                    |

| —                    | —                                                                                                   | _                                                                                                                                                                                                                                                                                                        | —                                                                                                                                                                                                                                                                                                                                                              | PMOD3                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PMOD2                                                                                                                                                                                                                                                                                        | PMOD1                                                                                                                                                                                                                                                                                                                                                                                                    |

|                      |                                                                                                     |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                              | bit 8                                                                                                                                                                                                                                                                                                                                                                                                    |

|                      |                                                                                                     |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |

| R/W-1                | R/W-1                                                                                               | R/W-1                                                                                                                                                                                                                                                                                                    | U-0                                                                                                                                                                                                                                                                                                                                                            | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-1                                                                                                                                                                                                                                                                                        | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                    |

| PEN3H <sup>(1)</sup> | PEN2H <sup>(1)</sup>                                                                                | PEN1H <sup>(1)</sup>                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                                              | PEN3L <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PEN2L <sup>(1)</sup>                                                                                                                                                                                                                                                                         | PEN1L <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                     |

|                      |                                                                                                     |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                              | bit (                                                                                                                                                                                                                                                                                                                                                                                                    |

|                      |                                                                                                     |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |