Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Betuils                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20 MIPS                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b; D/A 6x16b                                                        |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc804-h-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

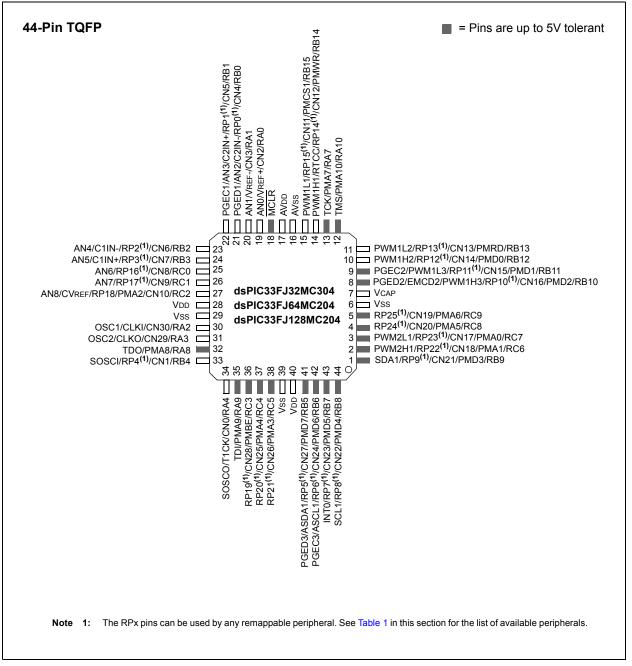

### Pin Diagrams (Continued)

### 3.5 CPU Resources

Many useful resources related to the CPU are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

### 3.5.1 KEY RESOURCES

- Section 2. "CPU" (DS70204)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

The Overflow and Saturation Status bits can optionally be viewed in the STATUS Register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). Programmers can check one bit in the STATUS register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This is useful for complex number arithmetic, which typically uses both accumulators.

The device supports three Saturation and Overflow modes:

- Bit 39 Overflow and Saturation:

- When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFF) or maximally negative 9.31 value (0x800000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user application. This condition is referred to as super saturation and provides protection against erroneous data or unexpected algorithm problems (such as gain calculations).

- Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFF) or maximally negative 1.31 value (0x0080000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user application. When this Saturation mode is in effect, the guard bits are not used, so the OA, OB or OAB bits are never set.

- Bit 39 Catastrophic Overflow: The bit 39 Overflow Status bit from the adder is used to set the SA or SB bit, which remains set until cleared by the user application. No saturation operation is performed, and the accumulator is allowed to overflow, destroying its sign. If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

### 3.8.3 ACCUMULATOR WRITE BACK

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

- W13, Register Direct: The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

- [W13] + = 2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

### 3.8.3.1 Round Logic

The round logic is a combinational block that performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value that is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored, and the least significant word is simply discarded.

Conventional rounding zero-extends bit 15 of the accumulator and adds it to the ACCxH word (bits 16 through 31 of the accumulator).

- If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented.

- If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged.

A consequence of this algorithm is that over a succession of random rounding operations, the value tends to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. In this case, the Least Significant bit (bit 16 of the accumulator) of ACCxH is examined:

- If it is '1', ACCxH is incremented.

- If it is '0', ACCxH is not modified.

Assuming that bit 16 is effectively random in nature, this scheme removes any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC), or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus, subject to data saturation (see **Section 3.8.3.2 "Data Space Write Saturation**"). For the MAC class of instructions, the accumulator write-back operation functions in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

### TABLE 4-29: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14                                         | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9                | Bit 8       | Bit 7     | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0  | All<br>Resets |

|-----------|------|--------|------------------------------------------------|---------|---------|---------|------------|----------------------|-------------|-----------|----------|-------|-------|-------|-------|----------|--------|---------------|

| ALRMVAL   | 0620 |        | Alarm Value Register Window based on APTR<1:0> |         |         |         |            |                      |             |           | XXXX     |       |       |       |       |          |        |               |

| ALCFGRPT  | 0622 | ALRMEN | CHIME                                          |         | AMASK   | <3:0>   |            | ALRMP                | TR<1:0>     | ARPT<7:0> |          |       |       |       |       |          |        | 0000          |

| RTCVAL    | 0624 |        |                                                |         |         |         | RTCC Value | Register W           | indow based | on RTCF   | PTR<1:0> |       |       |       |       |          |        | XXXX          |

| RCFGCAL   | 0626 | RTCEN  | _                                              | RTCWREN | RTCSYNC | HALFSEC | RTCOE      | RTCPTR<1:0> CAL<7:0> |             |           |          |       |       |       |       | 0000     |        |               |

| PADCFG1   | 02FC | _      | _                                              | —       | _       | _       | _          | _                    | —           | _         | —        | —     | _     | _     | —     | RTSECSEL | PMPTTL | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-30: CRC REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14              | Bit 13 | Bit 12 | it 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 |  |   |             |              |        |  | Bit 1 | Bit 0 | All<br>Resets |       |  |      |

|-----------|------|--------|---------------------|--------|--------|---------------------------------------------------------------------------|--|---|-------------|--------------|--------|--|-------|-------|---------------|-------|--|------|

| CRCCON    | 0640 | _      | _                   | CSIDL  |        | VWORD<4:0>                                                                |  |   |             |              | CRCMPT |  | CRCGO |       | PLEN          | <3:0> |  | 0000 |

| CRCXOR    | 0642 |        |                     |        |        |                                                                           |  |   | X<1         | 5:0>         |        |  |       |       |               |       |  | 0000 |

| CRCDAT    | 0644 |        |                     |        |        |                                                                           |  | C | CRC Data Ir | nput Registe | r      |  |       |       |               |       |  | 0000 |

| CRCWDAT   | 0646 |        | CRC Result Register |        |        |                                                                           |  |   |             |              |        |  |       |       | 0000          |       |  |      |

Legend: — = unimplemented, read as '0'.

### TABLE 4-31: DUAL COMPARATOR REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|---------|---------|-------|-------|-------|-------|----------|-------|-------|-------|---------------|

| CMCON     | 0630 | CMIDL  | —      | C2EVT  | C1EVT  | C2EN   | C1EN   | C2OUTEN | C10UTEN | C2OUT | C10UT | C2INV | C1INV | C2NEG    | C2POS | C1NEG | C1POS | 0000          |

| CVRCON    | 0632 | _      | _      | _      | _      | _      | _      | _       | _       | CVREN | CVROE | CVRR  | CVRSS | CVR<3:0> |       | 0000  |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-32: PORTA REGISTER MAP FOR dsPIC33FJ128MC202/802, dsPIC33FJ64MC202/802 AND dsPIC33FJ32MC302

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA     | 02C0 |        | —      | _      |        | —      | —      | —     | —     |       | —     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA     | 02C2 | _      | —      | _      | _      | —      | _      | _     | -     | _     | —     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | XXXX          |

| LATA      | 02C4 |        | _      |        | _      | _      | _      | _     | —     |       | _     | _     | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | XXXX          |

| ODCA      | 02C6 | -      | _      | -      |        | —      | _      | _     | —     | -     | _     | -     | _      | -      | —      | _      | -      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2007-2012 Microchip Technology Inc.

### 4.4.1 SOFTWARE STACK

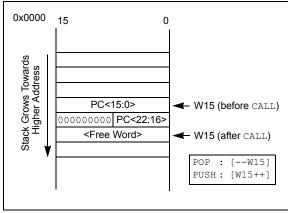

In addition to its use as a working register, the W15 register in the dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 and dsPIC33FJ128MCX02/X04 devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

**Note:** A PC push during exception processing concatenates the SRL register to the MSb of the PC prior to the push.

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. The SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, the SPLIM<0> is forced to '0' because all stack operations must be word aligned.

Whenever an EA is generated using the W15 as a source or destination pointer, the resulting address is compared with the value in the SPLIM register. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap does not occur. The stack error trap occurs on a subsequent push operation. For example, to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### 4.4.2 DATA RAM PROTECTION FEATURE

The dsPIC33F product family supports Data RAM protection features that enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. The BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. The SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-40 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (near data space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where:

Operand 1 is always a working register (that is, the addressing mode can only be register direct), which is referred to as Wb.

Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

Note: Not all instructions support all the addressing modes listed above. Individual instructions can support different subsets of these addressing modes.

### 6.1 Resets Resources

Many useful resources related to Resets are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en532315                                                       |

### 6.1.1 KEY RESOURCES

- Section 8. "Reset" (DS70192)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### 7.5 Interrupt Registers

| R-0    | R-0 | R/C-0 | R/C-0 | R-0 | R/C-0 | R -0 | R/W-0 |

|--------|-----|-------|-------|-----|-------|------|-------|

| OA     | OB  | SA    | SB    | OAB | SAB   | DA   | DC    |

| bit 15 |     |       |       |     |       |      | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | Ν     | OV    | Z     | C     |

| bit 7                |                      |                      |     |       |       |       | bit 0 |

### Legend:

| C = Clear only bit | R = Readable bit     | U = Unimplemented bit, read as '0' |  |

|--------------------|----------------------|------------------------------------|--|

| S = Set only bit   | W = Writable bit     | -n = Value at POR                  |  |

| '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |  |

bit 7-5

IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup>

111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

Note 1: For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

#### CORCON: CORE CONTROL REGISTER<sup>(1)</sup> **REGISTER 7-2:**

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R-0 | R-0     | R-0   |

|--------|-----|-----|-------|-------|-----|---------|-------|

| —      | —   | —   | US    | EDT   |     | DL<2:0> |       |

| bit 15 |     |     |       |       |     |         | bit 8 |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-------|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | PSV   | RND   | IF    |

| bit 7 |       |       |        |                     |       |       | bit 0 |

| Legend:             | C = Clear only bit  |                             |                  |

|---------------------|---------------------|-----------------------------|------------------|

| R = Readable bit    | W = Writable bit    | -n = Value at POR           | '1' = Bit is set |

| 0' = Bit is cleared | 'x = Bit is unknown | U = Unimplemented bit, read | l as '0'         |

**IPL3:** CPU Interrupt Priority Level Status bit 3<sup>(2)</sup> bit 3

- 1 = CPU interrupt priority level is greater than 7

- 0 = CPU interrupt priority level is 7 or less

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/X04 AND dsPIC33FJ128MCX02/X04

| REGISTER /-      | 4: INTCO         | DNZ: IN LERR                         | UPICONI     | KOL REGIST                              | ER Z             |        |        |  |

|------------------|------------------|--------------------------------------|-------------|-----------------------------------------|------------------|--------|--------|--|

| R/W-0            | R-0              | U-0                                  | U-0         | U-0                                     | U-0              | U-0    | U-0    |  |

| ALTIVT           | DISI             | —                                    | _           | —                                       | —                | —      | —      |  |

| bit 15           |                  |                                      |             |                                         |                  |        | bit 8  |  |

|                  |                  |                                      |             |                                         |                  |        |        |  |

| U-0              | U-0              | U-0                                  | U-0         | U-0                                     | R/W-0            | R/W-0  | R/W-0  |  |

| —                |                  | _                                    | —           | —                                       | INT2EP           | INT1EP | INT0EP |  |

| bit 7            |                  |                                      |             |                                         |                  |        | bit 0  |  |

|                  |                  |                                      |             |                                         |                  |        |        |  |

| Legend:          |                  |                                      |             |                                         |                  |        |        |  |

| R = Readable b   | bit              | W = Writable                         | bit         | U = Unimpler                            | mented bit, read | as '0' |        |  |

| -n = Value at Po | OR               | '1' = Bit is set                     |             | '0' = Bit is cleared x = Bit is unknown |                  |        |        |  |

|                  |                  |                                      |             |                                         |                  |        |        |  |

| bit 15           |                  | ole Alternate In                     | •           | Table bit                               |                  |        |        |  |

|                  |                  | nate vector tabl<br>dard (default) v | -           |                                         |                  |        |        |  |

| bit 14           |                  | struction Statu                      |             |                                         |                  |        |        |  |

|                  | 1 = DISI inst    | ruction is active                    | e           |                                         |                  |        |        |  |

|                  | 0 = DISI inst    | ruction is not a                     | ctive       |                                         |                  |        |        |  |

| bit 13-3         | Unimplemen       | ted: Read as '                       | 0'          |                                         |                  |        |        |  |

| bit 2            | INT2EP: Exte     | ernal Interrupt 2                    | Edge Detect | Polarity Selec                          | t bit            |        |        |  |

|                  |                  | on negative ede                      | <i>,</i>    |                                         |                  |        |        |  |

|                  | •                | on positive edg                      |             |                                         |                  |        |        |  |

| bit 1            |                  | ernal Interrupt 1                    | 0           | Polarity Selec                          | t bit            |        |        |  |

|                  | 1 = Interrupt of | on negative ede                      | ge          |                                         |                  |        |        |  |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

0 = Interrupt on positive edge

1 = Interrupt on negative edge 0 = Interrupt on positive edge

INTOEP: External Interrupt 0 Edge Detect Polarity Select bit

bit 0

## 10.6 Power-Saving Registers

| REGISTER     | -                       |                                     |         | E DISABLE C       |                 |                 |       |

|--------------|-------------------------|-------------------------------------|---------|-------------------|-----------------|-----------------|-------|

| R/W-0        | R/W-0                   | R/W-0                               | R/W-0   | R/W-0             | R/W-0           | R/W-0           | U-0   |

| T5MD         | T4MD                    | T3MD                                | T2MD    | T1MD              | QEI1MD          | PWM1MD          |       |

| bit 15       |                         |                                     |         |                   |                 |                 | bit 8 |

| R/W-0        | R/W-0                   | R/W-0                               | R/W-0   | R/W-0             | U-0             | R/W-0           | R/W-0 |

| I2C1MD       | U2MD                    | U1MD                                | SPI2MD  | SPI1MD            | _               | C1MD            | AD1MD |

| bit 7        |                         |                                     |         |                   |                 |                 | bit C |

| Legend:      |                         |                                     |         |                   |                 |                 |       |

| R = Readab   | le bit                  | W = Writable                        | bit     | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value a |                         | '1' = Bit is set                    |         | '0' = Bit is clea |                 | x = Bit is unkn | own   |

|              | <u> </u>                |                                     |         |                   |                 |                 | -     |

| bit 15       | T5MD: Timer             | 5 Module Disal                      | ole bit |                   |                 |                 |       |

|              | 1 = Timer5 m            | odule is disabl                     | ed      |                   |                 |                 |       |

|              | 0 = Timer5 m            | odule is enable                     | ed      |                   |                 |                 |       |

| bit 14       | -                       | 4 Module Disa                       |         |                   |                 |                 |       |

|              | -                       | odule is disable<br>odule is enable |         |                   |                 |                 |       |

| bit 13       | • • • • • • • • • • • • | 3 Module Disal                      |         |                   |                 |                 |       |

|              |                         | odule is disable                    |         |                   |                 |                 |       |

|              | 0 = Timer3 m            | odule is enable                     | ed      |                   |                 |                 |       |

| bit 12       | T2MD: Timer2            | 2 Module Disal                      | ole bit |                   |                 |                 |       |

|              | -                       | odule is disable                    |         |                   |                 |                 |       |

| L:1 44       |                         | odule is enable                     |         |                   |                 |                 |       |

| bit 11       | -                       | 1 Module Disal<br>odule is disabl   |         |                   |                 |                 |       |

|              | -                       | odule is enable                     |         |                   |                 |                 |       |

| bit 10       | QEI1MD: QE              | I1 Module Disa                      | ble bit |                   |                 |                 |       |

|              | 1 = QEI1 mod            | dule is disabled                    | l       |                   |                 |                 |       |

|              | 0 = QEI1 mod            | dule is enabled                     |         |                   |                 |                 |       |

| bit 9        |                         | WM1 Module [                        |         |                   |                 |                 |       |

|              |                         | odule is disable<br>odule is enable |         |                   |                 |                 |       |

| bit 8        |                         | ted: Read as '                      |         |                   |                 |                 |       |

| bit 7        |                         | 1 Module Disat                      |         |                   |                 |                 |       |

|              |                         | ule is disabled                     |         |                   |                 |                 |       |

|              |                         | ule is enabled                      |         |                   |                 |                 |       |

| bit 6        | U2MD: UART              | 2 Module Disa                       | ble bit |                   |                 |                 |       |

|              |                         | odule is disabl                     |         |                   |                 |                 |       |

|              |                         | odule is enable                     |         |                   |                 |                 |       |

| bit 5        |                         | 1 Module Disa                       |         |                   |                 |                 |       |

|              | -                       | odule is disabl<br>odule is enabl   |         |                   |                 |                 |       |

| bit 4        |                         | 2 Module Disa                       |         |                   |                 |                 |       |

| -            |                         | lule is disabled                    |         |                   |                 |                 |       |

|              | 0 = SPI2 mod            | lule is enabled                     |         |                   |                 |                 |       |

| bit 3        |                         | 1 Module Disa                       |         |                   |                 |                 |       |

|              |                         | lule is disabled                    |         |                   |                 |                 |       |

|              | 0 = SPI1 mod            | lule is enabled                     |         |                   |                 |                 |       |

### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

### 11.9 Peripheral Pin Select Registers

The dsPIC33FJ32MC302/304, dsPIC33FJ64MCX02/ X04 and dsPIC33FJ128MCX02/X04 family of devices implement 33 registers for remappable peripheral configuration:

- 20 Input Remappable Peripheral Registers:

- RPINR0-RPINR1, RPINR3-RPINR4, RPINR7, RPINR10-RPINR21, PRINR23, and PRINR26

- 13 Output Remappable Peripheral Registers:

- RPOR0-RPOR12

| Note: | Inpu        | t and output  | t reg | gister v          | /alue | es can | only  |

|-------|-------------|---------------|-------|-------------------|-------|--------|-------|

|       | be          | changed       | if    | the               | IOI   | OCK    | bit   |

|       | (OSCCON<6>) |               |       | set               | to    | '0'.   | See   |

|       | Sec         | tion 11.6.3.1 | I     | "Control Register |       |        |       |

|       | Loc         | k" for a spec | cific | comm              | and   | seque  | ence. |

### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | U-0 | R/W-1      | R/W-1 | R/W-1 | R/W-1 | R/W-1 |  |  |

|--------|-----|-----|------------|-------|-------|-------|-------|--|--|

| —      | —   | —   | INT1R<4:0> |       |       |       |       |  |  |

| bit 15 |     |     |            |       |       |       | bit 8 |  |  |

|        |     |     |            |       |       |       |       |  |  |

| U-0    | U-0 | U-0 | U-0        | U-0   | U-0   | U-0   | U-0   |  |  |

| —      | —   |     |            | —     | —     |       | —     |  |  |

| bit 7  |     |     |            |       |       |       | bit 0 |  |  |

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| bit 15-13 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

| bit 12-8 | <b>INT1R&lt;4:0&gt;:</b> Assign External Interrupt 1 (INTR1) to the corresponding RPn pin |

|----------|-------------------------------------------------------------------------------------------|

|          | 11111 = Input tied to Vss                                                                 |

|          | 11001 = Input tied to RP25                                                                |

|          | •                                                                                         |

|          | •                                                                                         |

|          | •                                                                                         |

|          | 00001 = Input tied to RP1                                                                 |

|          | 00000 = Input tied to RP0                                                                 |

| bit 7-0  | Unimplemented: Read as '0'                                                                |

### 15.2 Output Compare Resources

Many useful resources related to Output Compare are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

### 15.2.1 KEY RESOURCES

- Section 13. "Output Compare" (DS70209)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

NOTES:

### 24.3 Comparator Voltage Reference

# 24.3.1 CONFIGURING THE COMPARATOR VOLTAGE REFERENCE

The voltage reference module is controlled through the CVRCON register (Register 24-2). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR3:CVR0), with one range offering finer resolution.

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

### FIGURE 24-2: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

| REGISTER 25-4: | RTCVAL | (WHEN RTCPTR<1:0> = 11): YEAR VALUE REGISTER <sup>(1)</sup> |

|----------------|--------|-------------------------------------------------------------|

|----------------|--------|-------------------------------------------------------------|

|                 |       |                                                            |       | -                                  |       |       |       |  |

|-----------------|-------|------------------------------------------------------------|-------|------------------------------------|-------|-------|-------|--|

| U-0             | U-0   | U-0                                                        | U-0   | U-0                                | U-0   | U-0   | U-0   |  |

| —               | _     | —                                                          |       | —                                  | _     | _     | _     |  |

| bit 15          |       |                                                            |       |                                    |       |       | bit 8 |  |

|                 |       |                                                            |       |                                    |       |       |       |  |

| R/W-x           | R/W-x | R/W-x                                                      | R/W-x | R/W-x                              | R/W-x | R/W-x | R/W-x |  |

|                 | YRTE  | N<3:0>                                                     |       | YRONE<3:0>                         |       |       |       |  |

| bit 7           |       |                                                            |       |                                    |       |       | bit 0 |  |

|                 |       |                                                            |       |                                    |       |       |       |  |

| Legend:         |       |                                                            |       |                                    |       |       |       |  |

| R = Readable b  | bit   | W = Writable                                               | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at P | OR    | R '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |                                    |       | nown  |       |  |

bit 15-8 Unimplemented: Read as '0'

bit 7-4 YRTEN<3:0>: Binary Coded Decimal Value of Year's Tens Digit; contains a value from 0 to 9

bit 3-0 YRONE<3:0>: Binary Coded Decimal Value of Year's Ones Digit; contains a value from 0 to 9

**Note 1:** A write to the YEAR register is only allowed when RTCWREN = 1.

### REGISTER 25-5: RTCVAL (WHEN RTCPTR<1:0> = 10): MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R-x     | R-x         | R-x | R-x | R-x   |

|--------|-----|-----|---------|-------------|-----|-----|-------|

| —      | —   | —   | MTHTEN0 | MTHONE<3:0> |     |     |       |

| bit 15 |     |     |         |             |     |     | bit 8 |

| U-0   | U-0 | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|-------|-----|-------------|-------|-------|-------|---------|-------|

| —     | —   | DAYTEN<1:0> |       |       | DAYON | IE<3:0> |       |

| bit 7 |     |             |       |       |       |         | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12 MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit; contains a value of 0 or 1

bit 11-8MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit; contains a value from 0 to 9bit 7-6Unimplemented: Read as '0'

bit 5-4 DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit; contains a value from 0 to 3

bit 3-0 DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit; contains a value from 0 to 9

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### 30.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

### 30.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

# TABLE 31-21:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |                                      |     |       |                                                                                        |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------|-----|-------|----------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                         | Min  | Тур <sup>(2)</sup>                   | Мах | Units | Conditions                                                                             |

| SY10               | TMCL   | MCLR Pulse Width (low)                                                                                                                                                                                                                                                                | 2    | —                                    | _   | μs    | -40°C to +85°C                                                                         |

| SY11               | TPWRT  | Power-up Timer Period                                                                                                                                                                                                                                                                 | _    | 2<br>4<br>8<br>16<br>32<br>64<br>128 |     | ms    | -40°C to +85°C<br>User programmable                                                    |

| SY12               | TPOR   | Power-on Reset Delay                                                                                                                                                                                                                                                                  | 3    | 10                                   | 30  | μs    | -40°C to +85°C                                                                         |

| SY13               | Tioz   | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset                                                                                                                                                                                                                        | 0.68 | 0.72                                 | 1.2 | μs    | —                                                                                      |

| SY20               | Twdt1  | Watchdog Timer Time-out<br>Period                                                                                                                                                                                                                                                     | —    | —                                    | —   | _     | See Section 28.4 "Watchdog<br>Timer (WDT)" and LPRC<br>specification F21 (Table 31-19) |

| SY30               | Tost   | Oscillator Start-up Time                                                                                                                                                                                                                                                              | _    | 1024 Tosc                            |     |       | Tosc = OSC1 period                                                                     |

| SY35               | TFSCM  | Fail-Safe Clock Monitor<br>Delay                                                                                                                                                                                                                                                      | —    | 500                                  | 900 | μs    | -40°C to +85°C                                                                         |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

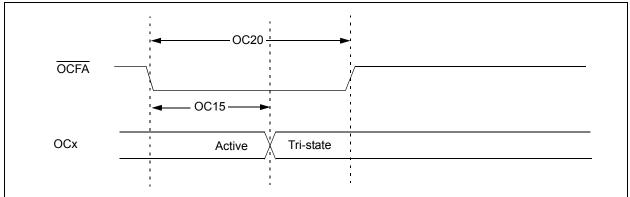

### FIGURE 31-9: OC/PWM MODULE TIMING CHARACTERISTICS

### TABLE 31-28: SIMPLE OC/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |          |     |          |       |            |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|----------|-------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                           | Min      | Тур | Max      | Units | Conditions |

| OC15               | Tfd    | Fault Input to PWM I/O<br>Change                                                                                                                                                                                                                                                        |          | _   | Tcy + 20 | ns    | _          |

| OC20               | TFLT   | Fault Input Pulse Width                                                                                                                                                                                                                                                                 | Tcy + 20 | _   | —        | ns    | —          |

**Note 1:** These parameters are characterized but not tested in manufacturing.

|              | AC<br>TERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+150°C for High Temperature |             |              |           |            |                                                  |

|--------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|-----------|------------|--------------------------------------------------|

| Param<br>No. | Symbol          | Characteristic                                                                                                                                   | Min Typ Max |              | Units     | Conditions |                                                  |

|              | AD              | C Accuracy (10-bit Mode)                                                                                                                         | – Measu     | rements      | with Ex   | ternal V   | REF+/VREF- <sup>(1)</sup>                        |

| HAD20b       | Nr              | Resolution <sup>(3)</sup>                                                                                                                        | 1           | 0 data bi    | ts        | bits       | —                                                |

| HAD21b       | INL             | Integral Nonlinearity                                                                                                                            | -3          | —            | 3         | LSb        | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| HAD22b       | DNL             | Differential Nonlinearity                                                                                                                        | > -1        | —            | < 1       | LSb        | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| HAD23b       | Gerr            | Gain Error                                                                                                                                       | -5          | _            | 6         | LSb        | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| HAD24b       | EOFF            | Offset Error                                                                                                                                     | -1          | —            | 5         | LSb        | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

|              | AD              | C Accuracy (10-bit Mode)                                                                                                                         | – Measu     | irements     | s with In | ernal V    | REF+/VREF- <sup>(1)</sup>                        |

| HAD20b       | Nr              | Resolution <sup>(3)</sup>                                                                                                                        |             | 10 data bits |           |            |                                                  |

| HAD21b       | INL             | Integral Nonlinearity                                                                                                                            | -2          |              | 2         | LSb        | VINL = AVSS = 0V, AVDD = 3.6V                    |

| HAD22b       | DNL             | Differential Nonlinearity                                                                                                                        | > -1        | _            | < 1       | LSb        | VINL = AVSS = 0V, AVDD = 3.6V                    |

| HAD23b       | Gerr            | Gain Error                                                                                                                                       | -5          |              | 15        | LSb        | VINL = AVSS = 0V, AVDD = 3.6V                    |

| HAD24b       | EOFF            | Offset Error                                                                                                                                     | -1.5        |              | 7         | LSb        | VINL = AVSS = 0V, AVDD = 3.6V                    |

|              |                 | Dynamic P                                                                                                                                        | erformar    | nce (10-b    | oit Mode  | (2)        |                                                  |

| HAD33b       | Fnyq            | Input Signal Bandwidth                                                                                                                           |             |              | 400       | kHz        | _                                                |

### TABLE 32-16: ADC MODULE SPECIFICATIONS (10-BIT MODE)

Note 1: These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

**3:** Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

| Section Name                              | Update Description                                                                                                                                          |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 31.0 "Electrical Characteristics" | Updated the maximum value for Extended Temperature Devices in the Thermal Operating Conditions (see Table 31-2).                                            |

|                                           | Removed Note 4 from the DC Temperature and Voltage Specifications (see Table 31-4).                                                                         |

|                                           | Updated all typical and maximum Operating Current (IDD) values (see Table 31-5).                                                                            |

|                                           | Updated all typical and maximum Idle Current (IIDLE) values (see Table 31-6).                                                                               |

|                                           | Updated the maximum Power-Down Current (IPD) values for parameters DC60d, DC60a, and DC60b (see Table 31-7).                                                |

|                                           | Updated all typical Doze Current (Idoze) values (see Table 31-8).                                                                                           |

|                                           | Updated the maximum value for parameter DI19 and added parameters DI28, DI29, DI60a, DI60b, and DI60c to the I/O Pin Input Specifications (see Table 31-9). |

|                                           | Added Note 2 to the PLL Clock Timing Specifications (see Table 31-17)                                                                                       |

|                                           | Removed Note 2 from the AC Characteristics: Internal RC Accuracy (see Table 31-18).                                                                         |

|                                           | Updated the Internal RC Accuracy minimum and maximum values for parameter F21b (see Table 31-19).                                                           |

|                                           | Updated the characteristic description for parameter DI35 in the I/O Timing Requirements (see Table 31-20).                                                 |

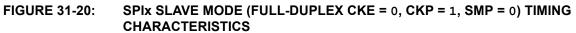

|                                           | Updated <i>all</i> SPI specifications (see Table 31-32 through Table 31-39 and Figure 31-14 through Figure 31-21)                                           |

|                                           | Updated the ADC Module Specification minimum values for parameters AD05 and AD07, and updated the maximum value for parameter AD06 (see Table 31-43).       |

|                                           | Updated the ADC Module Specifications (12-bit Mode) minimum and maximum values for parameter AD21a (see Table 31-44).                                       |

|                                           | Updated all ADC Module Specifications (10-bit Mode) values, with the exception of Dynamic Performance (see Table 31-45).                                    |

|                                           | Updated the minimum value for parameter PM6 and the maximum value for parameter PM7 in the Parallel Master Port Read Timing Requirements (see Table 31-54). |

|                                           | Added DMA Read/Write Timing Requirements (see Table 31-56).                                                                                                 |

### TABLE A-4: MAJOR SECTION UPDATES (CONTINUED)