# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 6                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 8-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18313-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.3 Master Clear (MCLR) Pin

The MCLR pin provides three specific device functions:

- Device Reset (when MCLRE = 1)

- Digital input pin (when MCLRE = 0)

- Device Programming and Debugging

If programming and debugging are not required in the end application then either set the MCLRE Configuration bit to '1' and use the pin as a digital input or clear the MCLRE Configuration bit and leave the pin open to use the internal weak pull-up. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{MCLR}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, the programmer  $\overline{MCLR}/VPP$  output should be connected directly to the pin so that R1 isolates the capacitor, C1 from the  $\overline{MCLR}$ pin during programming and debugging operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### 2.4 ICSP<sup>™</sup> Pins

The ICSPCLK and ICSPDAT pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the ICSPCLK and ICSPDAT pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be isolated from the programmer by resistors between the application and the device pins or removed from the circuit during programming. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., ICSPCLK/ICSPDAT pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/ emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 37.0 "Development Support**".

### 4.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- Revision ID

- User ID

- Program Flash Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

- Data EEPROM

#### 4.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing 32K x 14 program memory space. Table 4-1 shows the memory sizes implemented. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 4-1).

#### TABLE 4-1: DEVICE SIZES AND ADDRESSES

| Device               | Program Memory Size (Words) | Last Program Memory Address |

|----------------------|-----------------------------|-----------------------------|

| PIC16(L)F18313/18323 | 2048                        | 07FFh                       |

| TABLE 4 | -4: SPEC |                | FUN            | CTION RE | GISTER SU     | JMMARY B    | ANKS 0-31     | (CONTINU         | ED)      |         |        |                       |                              |

|---------|----------|----------------|----------------|----------|---------------|-------------|---------------|------------------|----------|---------|--------|-----------------------|------------------------------|

| Address | Name     | PIC16(L)F18313 | PIC16(L)F18323 | Bit 7    | Bit 6         | Bit 5       | Bit 4         | Bit 3            | Bit 2    | Bit 1   | Bit 0  | Value on:<br>POR, BOR | Value on all<br>other Resets |

| Bank 1  |          |                |                |          |               |             |               |                  |          |         |        |                       |                              |

|         |          |                |                |          |               | CPU CORE RI | EGISTERS; see | Table 4-2 for sp | pecifics |         |        |                       |                              |

| 08Ch    | TRISA    |                |                | _        | _             | TRISA5      | TRISA4        | _                | TRISA2   | TRISA1  | TRISA0 | 11 -111               | 11 -111                      |

| 08Dh    | _        | -              | _              |          | Unimplemented |             |               |                  |          |         | _      | _                     |                              |

| 08Eh    | TRISC    | Х              | —              |          | Unimplemented |             |               |                  |          | —       | —      |                       |                              |

|         |          | _              | х              | _        | —             | TRISC5      | TRISC4        | TRISC3           | TRISC2   | TRISC1  | TRISC0 | 11 1111               | 11 1111                      |

| 08Fh    | —        | -              | -              |          | Unimplemented |             |               |                  |          | —       | _      |                       |                              |

| 090h    | PIE0     |                |                | _        | _             | TMR0IE      | IOCIE         | _                | _        | _       | INTE   | 000                   | 000                          |

| 091h    | PIE1     |                |                | TMR1GIE  | ADIE          | RCIE        | TXIE          | SSP1IE           | BCL1IE   | TMR2IE  | TMR1IE | 0000 0000             | 0000 0000                    |

| 092h    | PIE2     | Х              | —              |          |               | C1IE        | NVMIE         | _                | _        |         | NCO1IE | 0000 0000             | 0000 0000                    |

|         |          | —              | Х              |          | C2IE          | C1IE        | NVMIE         | _                | _        |         | NCO1IE | 0000 0000             | 0000 0000                    |

| 093h    | PIE3     |                |                | OSFIE    | CSWIE         | _           | _             | _                | —        | CLC2IE  | CLC1IE | 0000 0000             | 0000 0000                    |

| 094h    | PIE4     |                |                |          | CWG1IE        | _           |               | _                | _        | CCP2IE  | CCP1IE | 0000 0000             | 0000 0000                    |

| 095h    | _        | -              | _              |          |               |             | Unimp         | lemented         |          |         |        | _                     | —                            |

| 096h    | —        | -              | -              |          |               |             | Unimp         | lemented         |          |         |        | —                     | —                            |

| 097h    | WDTCON   |                |                | _        | —             |             |               | WDTPS<4:0>       |          |         | SWDTEN | 01 0110               | 01 0110                      |

| 098h    | —        | -              | _              |          |               |             | Unimp         | lemented         |          |         |        | —                     | _                            |

| 099h    | —        |                | _              |          | Unimplemented |             |               |                  |          |         |        | —                     | _                            |

| 09Ah    | —        | -              | -              |          |               |             | Unimp         | lemented         |          |         |        | —                     | _                            |

| 09Bh    | ADRESL   |                |                |          |               |             | ADRE          | SL<7:0>          |          |         |        | xxxx xxxx             | uuuu uuuu                    |

| 09Ch    | ADRESH   |                |                |          |               |             | ADRE          | SH<7:0>          |          |         |        | xxxx xxxx             | uuuu uuuu                    |

| 09Dh    | ADCON0   |                |                |          |               | CHS         | <5:0>         |                  | 1        | GO/DONE | ADON   | 0000 0000             | 0000 0000                    |

|         |          |                |                |          |               |             |               |                  |          |         |        |                       |                              |

\_

ADNREF

ADACT<3:0>

\_

ADPREF<1:0>

ADCS<2:0>

\_

x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

#### OLIMANA A DV AA (OONTINUUED)

09Eh

09Fh

Legend:

Note 1:

ADCON1

Only on PIC16F18313/18323.

ADACT

ADFM

\_

\_

© 2015-2016 Microchip Technology Inc.

0000 -000

---- 0000

0000 -000

---- 0000

# PIC16(L)F18313/18323

| RE 4-5: ACCESSING | THE STA                                                                                                                      |                                                                                                          | 2                                                                                                                                                                                                                    |

|-------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |                                                                                                                              | [                                                                                                        | _                                                                                                                                                                                                                    |

|                   | 0x0F                                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

|                   | 0x0E                                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

|                   | 0x0D                                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

|                   | 0x0C                                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

|                   | 0x0B                                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

|                   | 0x0A                                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

|                   | 0x09                                                                                                                         |                                                                                                          | This figure shows the stack configuration                                                                                                                                                                            |

|                   | 0x08                                                                                                                         |                                                                                                          | after the first CALL or a single interrupt.<br>If a RETURN instruction is executed, the                                                                                                                              |

|                   | 0x07                                                                                                                         |                                                                                                          | return address will be placed in the<br>Program Counter and the Stack Pointer                                                                                                                                        |

|                   | 0x06                                                                                                                         |                                                                                                          | decremented to the empty state (0x1F).                                                                                                                                                                               |

|                   | 0x05                                                                                                                         |                                                                                                          | _                                                                                                                                                                                                                    |

|                   | 0x04                                                                                                                         |                                                                                                          | _                                                                                                                                                                                                                    |

|                   | 0x03                                                                                                                         |                                                                                                          | _                                                                                                                                                                                                                    |

|                   | 0x02                                                                                                                         |                                                                                                          | _                                                                                                                                                                                                                    |

|                   | 0x01                                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

| TOSH:TOSL         | 0x00                                                                                                                         | Return Address                                                                                           | STKPTR = 0x00                                                                                                                                                                                                        |

|                   | THE STA                                                                                                                      | CK EXAMPLE                                                                                               | 3                                                                                                                                                                                                                    |

|                   | ſ                                                                                                                            | CK EXAMPLE                                                                                               | <u>3</u>                                                                                                                                                                                                             |

|                   | 0x0F                                                                                                                         | CK EXAMPLE                                                                                               | <u>3</u>                                                                                                                                                                                                             |

|                   | 0x0F<br>0x0E                                                                                                                 | ACK EXAMPLE                                                                                              |                                                                                                                                                                                                                      |

|                   | 0x0F<br>0x0E<br>0x0D                                                                                                         | CK EXAMPLE                                                                                               | <u>3</u>                                                                                                                                                                                                             |

|                   | 0x0F<br>0x0E<br>0x0D<br>0x0C                                                                                                 | CK EXAMPLE                                                                                               | After seven CALLS or six CALLS and an                                                                                                                                                                                |

|                   | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B                                                                                         | ACK EXAMPLE                                                                                              | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions                                                                                        |

|                   | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A                                                                                 |                                                                                                          | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure                                                                                                                                     |

|                   | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x0A<br>0x09                                                                 |                                                                                                          | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses                                             |

|                   | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x09<br>0x08                                                                 |                                                                                                          | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses                                             |

| RE 4-6: ACCESSING | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07                                                         |                                                                                                          | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

|                   | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07<br>0x06                                                 | Return Address                                                                                           | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses                                             |

| RE 4-6: ACCESSING | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07<br>0x06<br>0x05                                         | Return Address<br>Return Address                                                                         | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

| RE 4-6: ACCESSING | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07<br>0x06<br>0x05<br>0x04                                 | Return Address<br>Return Address<br>Return Address                                                       | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

| RE 4-6: ACCESSING | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x08<br>0x07<br>0x08<br>0x07<br>0x06<br>0x05<br>0x04<br>0x03                 | Return Address<br>Return Address<br>Return Address<br>Return Address<br>Return Address                   | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

| RE 4-6: ACCESSING | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07<br>0x08<br>0x07<br>0x06<br>0x05<br>0x04<br>0x03<br>0x02 | Return Address<br>Return Address<br>Return Address<br>Return Address<br>Return Address<br>Return Address | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

| RE 4-6: ACCESSING | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x08<br>0x07<br>0x08<br>0x07<br>0x06<br>0x05<br>0x04<br>0x03                 | Return Address<br>Return Address<br>Return Address<br>Return Address<br>Return Address                   | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

# PIC16(L)F18313/18323

| REGISTER          | 5-3: CC                                                        | ONFIGURATIO                                    | ON WORD 3:                                  | MEMORY                                                  |                               |               |                    |

|-------------------|----------------------------------------------------------------|------------------------------------------------|---------------------------------------------|---------------------------------------------------------|-------------------------------|---------------|--------------------|

|                   |                                                                | R/P-1                                          | U-1                                         | U-1                                                     | U-1                           | U-1           | U-1                |

|                   |                                                                | LVP <sup>(1)</sup>                             |                                             | _                                                       |                               |               |                    |

|                   |                                                                | bit 13                                         |                                             |                                                         |                               |               | bit 8              |

| U-1               | U-1                                                            | U-1                                            | U-1                                         | U-1                                                     | U-1                           | R/P-1         | R/P-1              |

| _                 | —                                                              | _                                              | —                                           | _                                                       | —                             | WRT1          | WRT0               |

| bit 7             | 1                                                              |                                                | l .                                         | 1                                                       | I                             |               | bit 0              |

|                   |                                                                |                                                |                                             |                                                         |                               |               |                    |

| Legend:           |                                                                |                                                |                                             |                                                         |                               |               |                    |

| R = Readable      | e bit                                                          | P = Programma                                  | able bit                                    | U = Unimpleme                                           | nted bit, read as             | '1'           |                    |

| '0' = Bit is clea | ared                                                           | '1' = Bit is set                               |                                             | n = Value when                                          | blank or after Bu             | ulk Erase     |                    |

|                   |                                                                |                                                |                                             |                                                         |                               |               |                    |

| bit 13            | 1 = ON L                                                       | age Programming<br>ow-Voltage Progr<br>pnored. |                                             | led. MCLR/VPP p                                         | in function is $\overline{M}$ | CLR. MCLRE Co | nfiguration bit is |

|                   |                                                                | IV on MCLR/VPP I                               | must be used fo                             | r programming.                                          |                               |               |                    |

| bit 12-2          | Unimplement                                                    | ed: Read as '1'                                |                                             |                                                         |                               |               |                    |

| bit 1-0           | WRT<1:0>: Us<br>11 = OFF<br>10 = BOOT<br>01 = HALF<br>00 = ALL | 0000h to 03FFh                                 | off<br>write-protected,<br>write-protected, | 0200h to 07FFh i<br>0400h to 07FFh i<br>no addresses ma | may be modified               |               |                    |

Note 1: The LVP bit cannot be programmed to '0' when Programming mode is entered via LVP.

#### 7.2.2.3 Internal Oscillator Frequency Adjustment

The HFINTOSC and LFINTOSC internal oscillators are both factory-calibrated. This HFINTOSC oscillator can be adjusted in software by writing to the OSCTUNE register (Register 7-3). OSCTUNE does not affect the LFINTOSC frequency.

The default value of the OSCTUNE register is 00h. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the HFINTOSC oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

#### 7.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a factory calibrated 31 kHz internal clock source.

The LFINTOSC is the clock source for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM). The LFINTOSC can also be used as the system clock, or as a clock or input source to certain peripherals.

The LFINTOSC is selected as the clock source through one of the following methods:

- Programming the RSTOSC<2:0> bits of Configuration Word 1 to enable LFINTOSC.

- Write to the NOSC<2:0> bits of the OSCCON1 register.

#### 7.2.2.5 Oscillator Status and Manual Enable

The 'ready' status of each oscillator is displayed in the OSCSTAT1 register (Register 7-4). The oscillators can also be manually enabled through the OSCEN register (Register 7-6). Manual enables make it possible to verify the operation of the EXTOSC or SOSC crystal oscillators. This can be achieved by enabling the selected oscillator, then watching the corresponding 'ready' state of the oscillator in the OSCSTAT1 register.

### 7.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the New Oscillator Source (NOSC) and New Divider selection request (NDIV) bits of the OSCCON1 register. The following clock sources can be selected using the following:

- External Oscillator (EXTOSC)

- High-Frequency Internal Oscillator (HFINTOSC)

- Low-Frequency Internal Oscillator (LFINTOSC)

- Secondary Oscillator (SOSC)

- · EXTOSC with 4x PLL

- HFINTOSC with 2x PLL

#### 7.3.1 NEW OSCILLATOR SOURCE (NOSC) AND NEW DIVIDER SELECTION REQUEST (NDIV) BITS

The New Oscillator Source (NOSC) and New Divider selection request (NDIV) bits of the OSCCON1 register select the system clock source and frequencies that are used for the CPU and peripherals.

When new values of NOSC and NDIV are written to OSCCON1, the current oscillator selection will continue to operate while waiting for the new clock source to indicate that it is stable and ready. In some cases, the newly requested source may already be in use, and is ready immediately. In the case of a divider-only change, the new and old sources are the same and are ready immediately. The device may enter Sleep while waiting for the switch as described in **Section 7.3.3 "Clock Switch and Sleep"**.

When the new oscillator is ready, the New Oscillator is Ready (NOSCR) bit of OSCCON3 and the Clock Switch Interrupt Flag (CSWIF) bit of PIR3 become set (CSWIF = 1). If Clock Switch Interrupts are enabled (CSWIE = 1), an interrupt will be generated at that time. The Oscillator Ready (ORDY) bit of OSCCON3 can also be polled to determine when the oscillator is ready in lieu of an interrupt.

If the Clock Switch Hold (CSWHOLD) bit of OSCCON3 is clear, the oscillator switch will occur when the New Oscillator is Ready bit (NOSCR) is set, and the interrupt (if enabled) will be serviced at the new oscillator setting.

If CSWHOLD is set, the oscillator switch is suspended, while execution continues using the current (old) clock source. When the NOSCR bit is set, software should:

- set CSWHOLD = 0 so the switch can complete, or

- copy COSC into NOSC to abandon the switch.

If DOZE is in effect, the switch occurs on the next clock cycle, whether or not the CPU is operating during that cycle.

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|-------|-------|-------|-------|-----------|-------|-------|--------|---------------------|

| STATUS |       |       |       | TO    | PD        | Z     | DC    | С      | 24                  |

| WDTCON | —     | _     |       | ١     | WDTPS<4:0 | >     |       | SWDTEN | 110                 |

#### TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 | 13:8 |         | —       | DEBUG    | STVREN   | PPS1WAY  | —        | BORV    |         | 66                  |

| CONFIGZ | 7:0  | BOREN1  | BOREN0  | LPBOREN  | -        | WDTE1    | WDTE0    | PWRTE   | MCLRE   | 55                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

| W-0/0            | W-0/0    | W-0/0             | W-0/0 | W-0/0        | W-0/0            | W-0/0            | W-0/0       |

|------------------|----------|-------------------|-------|--------------|------------------|------------------|-------------|

|                  |          |                   | NVMC  | ON2<7:0>     |                  |                  |             |

| bit 7            |          |                   |       |              |                  |                  | bit 0       |

|                  |          |                   |       |              |                  |                  |             |

| Legend:          |          |                   |       |              |                  |                  |             |

| R = Readable     | bit      | W = Writable b    | oit   | U = Unimpler | mented bit, read | d as '0'         |             |

| S = Bit can onl  | y be set | x = Bit is unkno  | own   | -n/n = Value | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |          | '0' = Bit is clea | red   |              |                  |                  |             |

#### REGISTER 11-6: NVMCON2: NONVOLATILE MEMORY CONTROL 2 REGISTER

bit 7-0 **NVMCON2<7:0>:** Flash Memory Unlock Pattern bits To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the NVMCON1 register. The value written to this register is used to unlock the writes.

TABLE 11-5: SUMMARY OF REGISTERS ASSOCIATED WITH NONVOLATILE MEMORY (NVM)

| Name    | Bit 7 | Bit 6               | Bit 5                              | Bit 4 | Bit 3   | Bit 2   | Bit 1 | Bit 0  | Register<br>on Page |

|---------|-------|---------------------|------------------------------------|-------|---------|---------|-------|--------|---------------------|

| INTCON  | GIE   | PEIE                | —                                  | —     | —       | _       | —     | INTEDG | 90                  |

| PIR2    | _     | C2IF <sup>(1)</sup> | C1IF                               | NVMIF | _       | _       | —     | NCO1IF | 98                  |

| PIE2    | _     | C2IE <sup>(1)</sup> | C1IE                               | NVMIE | _       | _       | —     | NCO1IE | 93                  |

| NVMCON1 | _     | NVMREGS             | IVMREGS LWLO FREE WRERR WREN WR RD |       |         |         |       |        | 127                 |

| NVMCON2 |       | NVMCON2<7:0>        |                                    |       |         |         |       |        | 128                 |

| NVMADRL |       |                     |                                    | NVMAD | )R<7:0> |         |       |        | 126                 |

| NVMADRH | (2)   |                     | NVMADR<14:8>                       |       |         |         |       |        | 126                 |

| NVMDATL |       | NVMDAT<7:0>         |                                    |       |         |         |       | 126    |                     |

| NVMDATH | _     | _                   |                                    |       | NVMDA   | T<13:8> |       |        | 126                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by NVM.

Note 1: PIC16(L)F18323 only.

2: Unimplemented, read as '1'.

# PIC16(L)F18313/18323

| U-0                                   | R/W-0/0                                                             | R/W-0/0                                       | U-0                   | U-0             | R/W-0/0               | R/W-0/0             | U-0   |

|---------------------------------------|---------------------------------------------------------------------|-----------------------------------------------|-----------------------|-----------------|-----------------------|---------------------|-------|

| _                                     | DACMD                                                               | ADCMD                                         | _                     | _               | CMP2MD <sup>(1)</sup> | CMP1MD              | _     |

| bit 7                                 |                                                                     |                                               |                       |                 |                       |                     | bit ( |

| Legend:                               |                                                                     |                                               |                       |                 |                       |                     |       |

| R = Readable                          | bit                                                                 | W = Writable bit                              |                       | U = Unimplem    | ented bit, read as    | ʻ0'                 |       |

| u = Bit is unch                       | anged                                                               | x = Bit is unknow                             | vn                    | -n/n = Value at | POR and BOR/Va        | alue at all other R | esets |

| (1' = Bit is set (0' = Bit is cleared |                                                                     |                                               |                       | q = Value depe  | ends on condition     |                     |       |

| bit 5                                 | 0 = DAC more<br><b>ADCMD</b> : Disa<br>1 = ADC more<br>0 = ADC more | able ADC bit<br>dule disabled<br>dule enabled |                       |                 |                       |                     |       |

| bit 4-3                               | •                                                                   | ted: Read as '0'                              | (1)                   |                 |                       |                     |       |

| bit 2                                 | CMP2MD: Dis<br>1 = C2 modu<br>0 = C2 modu                           |                                               | C2 bit <sup>(1)</sup> |                 |                       |                     |       |

| bit 1                                 | 1 = C1 modu                                                         | sable Comparator (<br>ile disabled            | C1 bit                |                 |                       |                     |       |

|                                       | 0 = C1 modu                                                         | lle enabled                                   |                       |                 |                       |                     |       |

Note 1: PIC16(L)F18323 only.

#### REGISTER 14-4: PMD3: PMD CONTROL REGISTER 3

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-----|-----|---------|---------|

| _     | CWG1MD  | PWM6MD  | PWM5MD  | —   |     | CCP2MD  | CCP1MD  |

| bit 7 |         |         |         |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | Unimplemented: Read as '0'                                                             |

|---------|----------------------------------------------------------------------------------------|

| bit 6   | <b>CWG1MD:</b> Disable CWG1 bit<br>1 = CWG1 module disabled<br>0 = CWG1 module enabled |

| bit 5   | <b>PWM6MD:</b> Disable PWM6 bit<br>1 = PWM6 module disabled<br>0 = PWM6 module enabled |

| bit 4   | <b>PWM5MD:</b> Disable PWM5 bit<br>1 = PWM5 module disabled<br>0 = PWM5 module enabled |

| bit 3-2 | Unimplemented: Read as '0'                                                             |

| bit 1   | <b>CCP2MD:</b> Disable CCP2 bit<br>1 = CCP2 module disabled<br>0 = CCP2 module enabled |

| bit 0   | <b>CCP1MD:</b> Disable CCP1bit<br>1 = CCP1 module disabled<br>0 = CCP1 module enabled  |

## 16.3 Register Definitions: FVR Control

#### REGISTER 16-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 | R-q/q                 | R/W-0/0             | R/W-0/0              | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----------------------|---------------------|----------------------|-------------|---------|---------|---------|

| FVREN   | FVRRDY <sup>(1)</sup> | TSEN <sup>(3)</sup> | TSRNG <sup>(3)</sup> | CDAFVR<1:0> |         | ADFV    | R<1:0>  |

| bit 7   |                       |                     |                      |             |         |         | bit 0   |

| R = Reada    | able bit                         | W = Writable bit                                                                                                                                          | U = Unimplemented bit, read as '0'                         |  |  |  |  |  |

|--------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|--|--|

| u = Bit is u | inchanged                        | x = Bit is unknown                                                                                                                                        | -n/n = Value at POR and BOR/Value at all other Resets      |  |  |  |  |  |

| '1' = Bit is | set                              | '0' = Bit is cleared                                                                                                                                      | q = Value depends on condition                             |  |  |  |  |  |

| bit 7        | 1 = Fixed                        | Fixed Voltage Reference Ena<br>I Voltage Reference is enable<br>I Voltage Reference is disabl                                                             | ed                                                         |  |  |  |  |  |

| bit 6        | 1 = Fixed                        | Fixed Voltage Reference Re<br>Voltage Reference output is<br>Voltage Reference output is                                                                  | s ready for use                                            |  |  |  |  |  |

| bit 5        | 1 = Temp                         | <b>TSEN:</b> Temperature Indicator Enable bit <sup>(3)</sup><br>1 = Temperature Indicator is enabled<br>0 = Temperature Indicator is disabled             |                                                            |  |  |  |  |  |

| bit 4        | 1 = VOUT                         | Femperature Indicator Range<br>= VDD - 4V⊤ (High Range)<br>= VDD - 2V⊤ (Low Range)                                                                        | e Selection bit <sup>(3)</sup>                             |  |  |  |  |  |

| bit 3-2      | 11 = Com<br>10 = Com<br>01 = Com | <1:0>: Comparator FVR Buff<br>parator FVR Buffer Gain is 4<br>parator FVR Buffer Gain is 2<br>parator FVR Buffer Gain is 1<br>parator FVR Buffer is off   | lx, (4.096V) <sup>(2)</sup><br>2x, (2.048V) <sup>(2)</sup> |  |  |  |  |  |

| bit 1-0      | 11 = ADC<br>10 = ADC<br>01 = ADC | <b>:0&gt;:</b> ADC FVR Buffer Gain S<br>FVR Buffer Gain is 4x, (4.09<br>FVR Buffer Gain is 2x, (2.04<br>FVR Buffer Gain is 1x, (1.02<br>FVR Buffer is off | 96V) <sup>(2)</sup><br>48V) <sup>(2)</sup>                 |  |  |  |  |  |

- 2: Fixed Voltage Reference output cannot exceed VDD.

- 3: See Section 17.0 "Temperature Indicator Module" for additional information.

| Name                   | Bit 7  | Bit 6  | Bit 5     | Bit 4      | Bit 3  | Bit 2   | Bit 1      | Bit 0   | Register<br>on page |

|------------------------|--------|--------|-----------|------------|--------|---------|------------|---------|---------------------|

| FVRCON                 | FVREN  | FVRRDY | TSEN      | TSRNG      | CDAFV  | /R<1:0> | ADFV       | 157     |                     |

| ADCON0                 |        |        | CHS<      | <5:0>      |        |         | GO/DONE    | ADON    | 220                 |

| ADCON1                 | ADFM   |        | ADCS<2:0> |            | _      | ADNREF  | ADPRE      | 221     |                     |

| CM1CON1                | C1INTP | C1INTN | (         | C1PCH<2:0> | >      |         | C1NCH<2:0> |         | 167                 |

| CM2CON1 <sup>(1)</sup> | C2INTP | C2INTN | (         | C2PCH<2:0> |        |         |            |         | 167                 |

| DACCON0                | DAC1EN | _      | DAC10E    | _          | DAC1PS | SS<1:0> | _          | DAC1NSS | 239                 |

#### TABLE 16-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

Legend: Shaded cells are not used with the Fixed Voltage Reference.

**Note 1:** PIC16(L)F18323 only.

<sup>© 2015-2016</sup> Microchip Technology Inc.

## 22.4 Register Definitions: ADC Control

#### REGISTER 22-1: ADCON0: ADC CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0              | R/W-0/0                    | R/W-0/0               | R/W-0/0                    | R/W-0/0       | R/W-0/0           | R/W-0/0      |

|------------------|----------------------|----------------------------|-----------------------|----------------------------|---------------|-------------------|--------------|

|                  |                      | CHS<                       | :5:0>                 |                            |               | GO/DONE           | ADON         |

| bit 7            |                      |                            |                       |                            |               |                   | bit          |

|                  |                      |                            |                       |                            |               |                   |              |

| Legend:          |                      |                            |                       |                            |               |                   |              |

| R = Readable     |                      | W = Writable               |                       | U = Unimplen               |               |                   |              |

| u = Bit is unch  | •                    | x = Bit is unkr            |                       | -n/n = Value a             | at POR and BO | OR/Value at all o | other Resets |

| '1' = Bit is set |                      | '0' = Bit is cle           | ared                  |                            |               |                   |              |

| bit 7-2          | CHS<5:0>:            | Analog Channel             | Select bits           |                            |               |                   |              |

|                  |                      | FVR (Fixed Volta           |                       | e)(2)                      |               |                   |              |

|                  | 111110 =             | DAC1 output <sup>(1)</sup> |                       | ,                          |               |                   |              |

|                  |                      | Temperature Ind            | icator <sup>(3)</sup> |                            |               |                   |              |

|                  | 111100 =             |                            |                       |                            |               |                   |              |

|                  | 111011 =             | Reserved. No ch            | iannel connec         | ted.                       |               |                   |              |

|                  | •                    |                            |                       |                            |               |                   |              |

|                  | •                    |                            |                       |                            |               |                   |              |

|                  | 010101 =             | ANC5 <sup>(4)</sup>        |                       |                            |               |                   |              |

|                  | 010100 =             | ANC4 <sup>(4)</sup>        |                       |                            |               |                   |              |

|                  | 010011 =             | ANC3 <sup>(4)</sup>        |                       |                            |               |                   |              |

|                  | 010010 =             | ANC2 <sup>(4)</sup>        |                       |                            |               |                   |              |

|                  | 010001 =<br>010000 = | ANC1 <sup>(4)</sup>        |                       |                            |               |                   |              |

|                  |                      | Reserved. No c             | hannel conne          | rted                       |               |                   |              |

|                  | •                    |                            |                       |                            |               |                   |              |

|                  | •                    |                            |                       |                            |               |                   |              |

|                  | •                    |                            |                       |                            |               |                   |              |

|                  | 000101 =             | ANA5                       |                       |                            |               |                   |              |

|                  |                      | ANA4                       |                       |                            |               |                   |              |

|                  |                      | Reserved. No c<br>ANA2     | nannei conne          | cted.                      |               |                   |              |

|                  | 000010 =<br>000001 = | ANA2<br>ANA1               |                       |                            |               |                   |              |

|                  | 000000 =             | ANA0                       |                       |                            |               |                   |              |

| bit 1            | GO/DONE:             | ADC Conversion             | n Status bit          |                            |               |                   |              |

|                  |                      | nversion cycle ir          |                       |                            |               |                   |              |

|                  |                      | is automatically           |                       |                            | e ADC convers | sion has comple   | eted.        |

|                  |                      | nversion comple            | ted/not in proo       | gress                      |               |                   |              |

| bit 0            | ADON: ADO            |                            |                       |                            |               |                   |              |

|                  | 1 = ADC is           |                            |                       |                            |               |                   |              |

|                  | 0 = ADC IS           | disabled and cor           | isumes no op          | erating current            |               |                   |              |

| Note 1: Se       | e Section 24.        | 0 "5-Bit Digital-          | To-Analog Co          | onverter (DAC <sup>2</sup> | I) Module" fo | r more informati  | on.          |

|                  |                      | 0 "Fixed Voltag            | -                     | •                          | •             |                   |              |

| <b>3</b> : Se    | e Section 17.        | 0 "Temperature             | Indicator Mo          | dule" for more             | information.  |                   |              |

4: PIC16(L)F18323 only.

## 24.0 5-BIT DIGITAL-TO-ANALOG CONVERTER (DAC1) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- ADC input channel

- DAC1OUT pin

The Digital-to-Analog Converter (DAC) is enabled by setting the DAC1EN bit of the DACCON0 register.

#### EQUATION 24-1: DAC OUTPUT VOLTAGE

#### 24.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DAC1R<4:0> bits of the DACCON1 register.

The DAC output voltage is determined by Equation 24-1:

# $V_{OUT} = \left( (V_{SOURCE+} - V_{SOURCE-}) - \frac{DAC1R\langle 4:0 \rangle}{2^5} \right) + (V_{SOURCE-})$ $V_{SOURCE+} = V_{DD} \quad or \quad V_{REF+} \quad or \quad FVR$ $V_{SOURCE-} = V_{SS} \quad or \quad V_{REF-}$

#### 24.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Table 35-15.

#### 24.3 DAC Voltage Reference Output

The DAC voltage can be output to the DAC1OUT pin by setting the DAC1OE bit of the DACCON0 register. Selecting the DAC reference voltage for output on the DAC1OUT pin automatically overrides the digital output buffer and digital input threshold detector functions, disables the weak pull-up, and disables the constant-current drive function of that pin. Reading the DAC1OUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to the DAC1OUT pin. Figure 24-2 shows an example buffering technique.

### 25.5 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high source is enabled by setting the MDCHPOL bit of the MDCARH register. Inverting the signal for the carrier low source is enabled by setting the MDCLPOL bit of the MDCARL register.

#### 25.6 Programmable Modulator Data

The MDBIT of the MDCON register can be selected as the source for the modulator signal. This gives the user the ability to program the value used for modulation.

#### 25.7 Modulated Output Polarity

The modulated output signal provided on the DSM pin can also be inverted. Inverting the modulated output signal is enabled by setting the MDOPOL bit of the MDCON register.

#### 25.8 Slew Rate Control

The slew rate limitation on the output port pin can be disabled. The slew rate limitation can be removed by clearing the SLR bit of the SLRCON register associated with that pin. For example, clearing the slew rate limitation for pin RA5 would require clearing the SLRA5 bit of the SLRCONA register.

#### 25.9 Operation in Sleep Mode

The DSM module is not affected by Sleep mode. The DSM can still operate during Sleep, if the Carrier and Modulator input sources are also still operable during Sleep.

#### 25.10 Effects of a Reset

Upon any device Reset, the DSM module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

#### 28.1 Timer2 Operation

The clock input to the Timer2 modules is the system instruction clock (Fosc/4).

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, T2CKPS<1:0> of the T2CON register. The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output "Timer2 counter/postscaler (see Section 28.2 Interrupt").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, whereas the PR2 register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- Watchdog Timer (WDT) Reset

- Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

## Note: TMR2 is not cleared when T2CON is written.

#### 28.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2-to-PR2 match) provides the input for the 4-bit counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF of the PIR1 register. The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE, of the PIE1 register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0>, of the T2CON register.

## 28.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 30.0 "Master Synchronous Serial Port (MSSP) Module".

### 28.4 Timer2 Operation During Sleep

The Timer2 timers cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and PR2 registers will remain unchanged while the processor is in Sleep mode.

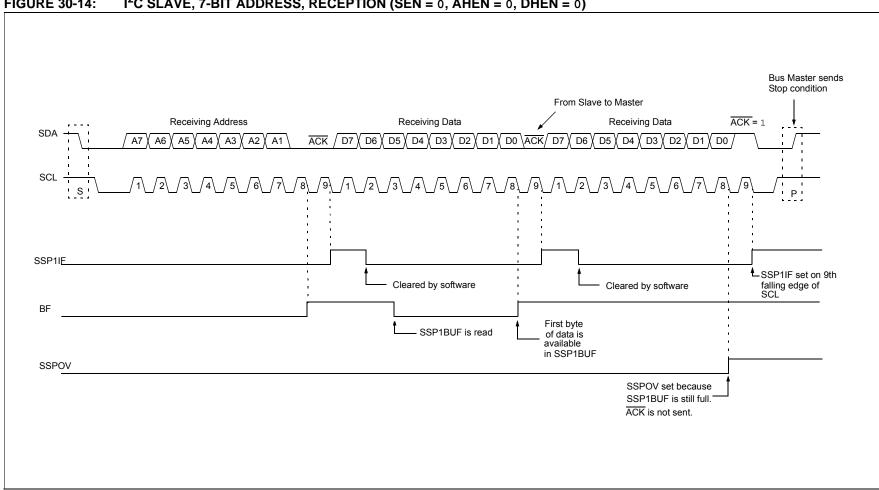

#### I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 0, DHEN = 0) FIGURE 30-14:

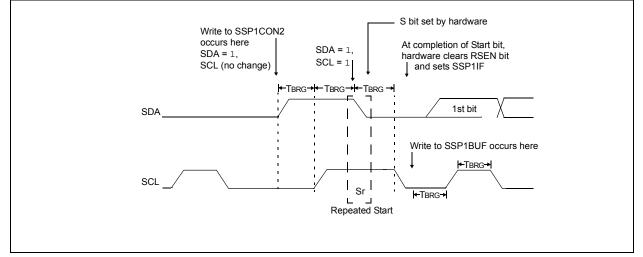

#### 30.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 30-27) occurs when the RSEN bit of the SSP1CON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSP1CON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSP1STAT register will be set. The SSP1IF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

### FIGURE 30-27: REPEATED START CONDITION WAVEFORM

| R-0/0           | R-1/1                       | U-0                            | R/W-0/0                              | R/W-0/0          | U-0              | R/W-0/0           | R/W-0/0       |

|-----------------|-----------------------------|--------------------------------|--------------------------------------|------------------|------------------|-------------------|---------------|

| ABDOVF          | RCIDL                       | —                              | SCKP                                 | BRG16            | _                | WUE               | ABDEN         |

| bit 7           |                             |                                |                                      |                  |                  |                   | bit 0         |

|                 |                             |                                |                                      |                  |                  |                   |               |

| Legend:         |                             |                                |                                      |                  |                  |                   |               |

| R = Readable    |                             | W = Writable                   |                                      | •                | mented bit, rea  |                   |               |

| u = Bit is und  | •                           | x = Bit is unk                 |                                      | -n/n = Value     | at POR and BC    | OR/Value at all o | other Resets  |

| '1' = Bit is se | t                           | '0' = Bit is cle               | eared                                |                  |                  |                   |               |

| bit 7           | ABDOVF: A                   | uto-Baud Dete                  | ct Overflow bit                      |                  |                  |                   |               |

|                 | Asynchronou                 |                                |                                      |                  |                  |                   |               |

|                 | -                           | d timer overflo                | wed                                  |                  |                  |                   |               |

|                 |                             | id timer did not               | overflow                             |                  |                  |                   |               |

|                 | Synchronous                 | <u>s mode</u> :                |                                      |                  |                  |                   |               |

| <b>h</b> # 0    | Don't care                  | sive Idle Flee b               |                                      |                  |                  |                   |               |

| bit 6           | Asynchronou                 | eive Idle Flag b<br>is mode:   | л                                    |                  |                  |                   |               |

|                 | 1 = Receiver                |                                |                                      |                  |                  |                   |               |

|                 |                             |                                | ved and the re                       | ceiver is receiv | /ing             |                   |               |

|                 | Synchronous                 | <u>s mode</u> :                |                                      |                  |                  |                   |               |

|                 | Don't care                  |                                |                                      |                  |                  |                   |               |

| bit 5           | -                           | nted: Read as                  |                                      |                  |                  |                   |               |

| bit 4           |                             | <pre></pre>                    | arity Select bit                     |                  |                  |                   |               |

|                 | Asynchronou                 |                                |                                      |                  |                  |                   |               |

|                 |                             |                                | 「X) is a low lev<br>「X) is a high le |                  |                  |                   |               |

|                 | Synchronous                 | -                              | , 0                                  |                  |                  |                   |               |

|                 | 1 = Idle state              | e for clock (CK)               | is a high level                      |                  |                  |                   |               |

|                 | 0 = Idle state              | e for clock (CK)               | is a low level                       |                  |                  |                   |               |

| bit 3           |                             | oit Baud Rate (                |                                      |                  |                  |                   |               |

|                 |                             | aud Rate Gene<br>ud Rate Gener |                                      |                  |                  |                   |               |

| bit 2           | Unimpleme                   | nted: Read as                  | ʻ0'                                  |                  |                  |                   |               |

| bit 1           | WUE: Wake-                  | -up Enable bit                 |                                      |                  |                  |                   |               |

|                 | <u>Asynchronou</u>          | <u>us mode</u> :               |                                      |                  |                  |                   |               |

|                 |                             |                                |                                      | Rx pin – interru | pt generated o   | n falling edge; b | it cleared in |

|                 |                             | e on following r               |                                      | -1 - 441         |                  |                   |               |

|                 | 0 = RX pin n<br>Synchronous |                                | or rising edge                       | Delected         |                  |                   |               |

|                 | -                           | is mode – valu                 | e ianored                            |                  |                  |                   |               |

| bit 0           |                             | o-Baud Detect                  |                                      |                  |                  |                   |               |

|                 | Asynchronou                 | us mode:                       |                                      |                  |                  |                   |               |

|                 | -                           |                                | asurement on t                       | the next chara   | acter – requires | s reception of a  | SYNCH field   |

|                 | (55h); cl                   | eared in hardw                 | are upon com                         | pletion          | •                | ·                 |               |

|                 |                             |                                | nt disabled or o                     | completed        |                  |                   |               |

|                 | Synchronous                 |                                | aignered                             |                  |                  |                   |               |

|                 | Unused in th                | is mode – valu                 | e ignorea                            |                  |                  |                   |               |

#### REGISTER 31-3: BAUD1CON: BAUD RATE CONTROL REGISTER