Welcome to **E-XFL.COM**

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 8-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18313-e-sn |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, check with one of the following:

- · Microchip's Worldwide Website; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

TABLE 4-4: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

| Address   | Name       | PIC16(L)F18313 | PIC16(L)F18323 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3          | Bit 2         | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on all<br>other Resets |

|-----------|------------|----------------|----------------|-------|-------|-------|--------|----------------|---------------|-------|-------|-----------------------|------------------------------|

| E21h      | SSP1DATPPS | Х              | _              | _     | _     | _     |        | S              | SSP1DATPPS<4: | 0>    |       | 0 0010                | u uuuu                       |

|           |            | _              | Χ              |       | _     | _     |        | S              | SSP1DATPPS<4: | 0>    |       | 1 0001                | u uuuu                       |

| E22h      | SSP1SSPPS  | Х              | _              |       |       | _     |        | ,              | SSP1SSPPS<4:0 | >     |       | 0 0011                | u uuuu                       |

|           |            | _              | Χ              | _     | _     | _     |        | ;              | SSP1SSPPS<4:0 | >     |       | 1 0011                | u uuuu                       |

| E23h      | _          | _              | -              |       |       |       | Unimpl | emented        |               |       |       | _                     | _                            |

| E24h      | RXPPS      | Χ              | _              | _     | _     | _     |        | RXPPS<4:0>     |               |       |       | 0 0001                | u uuuu                       |

|           |            | _              | Χ              |       |       | _     |        | RXPPS<4:0>     |               |       |       | 0 0101                | u uuuu                       |

| E25h      | TXPPS      | Х              | _              | _     | _     | _     |        | TXPPS<4:0>     |               |       |       | 0 0000                | u uuuu                       |

|           |            | _              | Χ              | _     | _     | _     |        | TXPPS<4:0>     |               |       |       |                       | u uuuu                       |

| E26h      | _          | -              | -              |       |       |       | Unimpl | emented        |               |       |       | _                     | _                            |

| E27h      | _          | _              | -              |       |       |       | Unimpl | emented        |               |       |       | _                     | _                            |

| E28h      | CLCIN0PPS  | Х              | _              |       | _     | _     |        |                | CLCIN0PPS<4:0 | >     |       | 0 0011                | u uuuu                       |

|           |            | _              | Χ              | _     | _     | _     |        |                | CLCIN0PPS<4:0 | >     |       | 1 0011                | u uuuu                       |

| E29h      | CLCIN1PPS  | Х              | _              | _     | _     | _     |        |                | CLCIN1PPS<4:0 | >     |       | 0 0101                | u uuuu                       |

|           |            | _              | Χ              | _     | _     | _     |        | CLCIN1PPS<4:0> |               |       |       |                       | u uuuu                       |

| E2Ah      | CLCIN2PPS  | Х              | _              | _     | _     | _     |        | CLCIN2PPS<4:0> |               |       |       |                       | u uuuu                       |

|           |            | _              | Χ              | _     | _     | _     |        | CLCIN2PPS<4:0> |               |       |       |                       | u uuuu                       |

| E2Bh      | CLCIN3PPS  | Х              | _              | _     | _     | _     |        | CLCIN3PPS<4:0> |               |       |       | 0 0000                | u uuuu                       |

|           |            | _              | Χ              | _     | _     | _     |        |                | CLCIN3PPS<4:0 | >     |       | 0 0101                | u uuuu                       |

| E2Ch-E6Fh | _          | _              | -              |       |       |       | Unimpl | emented        |               |       |       | _                     | _                            |

PIC16(L)F18313/18323

Legend: x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Only on PIC16F18313/18323.

#### 7.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> bits in the OSCCON1 register to switch the system clock source to the internal oscillator during run-time. See

Section 7.3 "Clock Switching" for more information.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that can produce two internal system clock sources.

- The HFINTOSC (High-Frequency Internal Oscillator) is factory-calibrated and operates up to 32 MHz.

- The LFINTOSC (Low-Frequency Internal Oscillator) is factory-calibrated and operates at 31 kHz.

#### 7.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 32 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits in Configuration Word 1 to '110' (1 MHz) or '000' (32 MHz) to set the oscillator upon device Power-up or Poset

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time.

The HFINTOSC frequency can be selected by setting the HFFRQ<3:0> bits of the OSCFRQ register.

The NDIV<3:0> bits of the OSCCON1 register allow for the division of the output of the selected clock source by a range between 1:1 and 1:512.

#### 7.2.2.2 2x PLL

The oscillator module contains a PLL that can be used with the HFINTOSC clock source to provide a system clock source. The input frequency to the PLL is limited to 8, 12, or 16 MHz, which will yield a system clock source of 16, 24, or 32 MHz, respectively. The PLL may be enabled for use by one of two methods:

- Program the RSTOSC bits in the Configuration Word 1 to '000' to enable the HFINTOSC (32 MHz). This setting configures the HFFRQ<3:0> bits to '110' (16 MHz) and activates the 2x PLL.

- Write '000' the NOSC<2:0> bits in the OSCCON1 register to enable the 2x PLL, and write the correct value into the HFFRQ<3:0> bits of the OSCFRQ register to select the desired system clock frequency. See Register 7-6 for more information.

#### REGISTER 8-7: PIRO: PERIPHERAL INTERRUPT STATUS REGISTER 0

| U-0   | U-0         | R/W/HS-0/0 | R-0                  | U-0 | U-0 | U-0 | R/W/HS-0/0 |  |  |

|-------|-------------|------------|----------------------|-----|-----|-----|------------|--|--|

| _     | _           | TMR0IF     | IOCIF <sup>(1)</sup> | _   | _   | _   | INTF       |  |  |

| bit 7 | bit 7 bit 0 |            |                      |     |     |     |            |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS= Hardware Set                                      |

bit 7-6 Unimplemented: Read as '0'

bit 5 TMR0IF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

bit 4 **IOCIF:** Interrupt-on-Change Interrupt Flag bit (read-only)

1 = An enabled edge was detected by the IOC module. One of the IOCF bits is set.

0 = No enabled edge is was detected by the IOC module. None of the IOCF bits is set.

Pins are individually masked via IOCxP and IOCxN.

bit 3-1 **Unimplemented:** Read as '0'

bit 0 INTF: INT External Interrupt Flag bit

1 = The INT external interrupt occurred (must be cleared in software)

0 = The INT external interrupt did not occur

**Note 1:** The IOCIF bit is the logical OR of all the IOCAF-IOCCF flags. Therefore, to clear the IOCIF flag, application firmware must clear all of the IOCAF-IOCCF register bits.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 8-9: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| U-0   | R/W/HS-0/0          | R/W/HS-0/0 | R/W/HS-0/0 | U-0 | U-0 | U-0 | R/W/HS-0/0 |

|-------|---------------------|------------|------------|-----|-----|-----|------------|

| _     | C2IF <sup>(1)</sup> | C1IF       | NVMIF      | -   | _   | _   | NCO1IF     |

| bit 7 |                     |            |            |     |     |     | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set                                     |

| bit 7   | Unimplemented: Read as '0'                                                                                                |

|---------|---------------------------------------------------------------------------------------------------------------------------|

| bit 6   | C2IF: Comparator C2 Interrupt Flag bit <sup>(1)</sup>                                                                     |

|         | 1 = Comparator 2 interrupt asserted<br>0 = Comparator 2 interrupt not asserted                                            |

| bit 5   | C1IF: Comparator C1 Interrupt Flag bit                                                                                    |

|         | <ul><li>1 = Comparator 1 interrupt asserted</li><li>0 = Comparator 1 interrupt not asserted</li></ul>                     |

| bit 4   | <b>NVMIF</b> : NVM Interrupt Flag bit<br>1 = The NVM has completed a programming task<br>0 = NVM interrupt not asserted   |

| bit 3-1 | Unimplemented: Read as '0'                                                                                                |

| bit 0   | <b>NCO1IF:</b> Direct Digital Synthesizer Interrupt Flag bit 1 = The NCO has rolled over 0 = No NCO interrupt is asserted |

Note 1: Comparator C2 not available on PIC16(L)F18313 devices.

| Note: | Interrupt flag bits are set when an interrupt |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |

|       | its corresponding enable bit or the Global    |  |  |  |  |  |

|       | Enable bit, GIE, of the INTCON register.      |  |  |  |  |  |

|       | User software should ensure the               |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear     |  |  |  |  |  |

|       | prior to enabling an interrupt.               |  |  |  |  |  |

## REGISTER 14-3: PMD2: PMD CONTROL REGISTER 2

| U-0   | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0               | R/W-0/0 | U-0   |

|-------|---------|---------|-----|-----|-----------------------|---------|-------|

| _     | DACMD   | ADCMD   | _   | -   | CMP2MD <sup>(1)</sup> | CMP1MD  | _     |

| bit 7 |         |         |     |     |                       |         | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7 Unimplemented: Read as '0' bit 6 DACMD: Disable DAC bit

1 = DAC module disabled 0 = DAC module enabled

bit 5 ADCMD: Disable ADC bit

1 = ADC module disabled0 = ADC module enabled

bit 4-3 Unimplemented: Read as '0'

bit 2 CMP2MD: Disable Comparator C2 bit<sup>(1)</sup>

1 = C2 module disabled0 = C2 module enabled

bit 1 CMP1MD: Disable Comparator C1 bit

1 = C1 module disabled 0 = C1 module enabled

bit 0 Unimplemented: Read as '0'

Note 1: PIC16(L)F18323 only.

## **REGISTER 14-4: PMD3: PMD CONTROL REGISTER 3**

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-----|-----|---------|---------|

| _     | CWG1MD  | PWM6MD  | PWM5MD  | _   | _   | CCP2MD  | CCP1MD  |

| bit 7 |         |         |         |     |     |         | bit 0   |

Legend:

bit 0

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7 Unimplemented: Read as '0'

bit 6 CWG1MD: Disable CWG1 bit

1 = CWG1 module disabled

0 = CWG1 module enabled

bit 5 **PWM6MD:** Disable PWM6 bit

1 = PWM6 module disabled

0 = PWM6 module enabled

bit 4 **PWM5MD:** Disable PWM5 bit

1 = PWM5 module disabled0 = PWM5 module enabled

bit 3-2 **Unimplemented:** Read as '0'

bit 1 CCP2MD: Disable CCP2 bit

1 = CCP2 module disabled0 = CCP2 module enabled

o Coi 2 module enabled

CCP1MD: Disable CCP1bit

1 = CCP1 module disabled0 = CCP1 module enabled

#### 21.1.2 INPUT DATA SELECTION GATES

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND of all enabled inputs.

Table 21-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits and gate polarity bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

TABLE 21-2: DATA GATING LOGIC

| CLCxGLSy | LCxGyPOL | Gate Logic   |

|----------|----------|--------------|

| 0x55     | 1        | 4-input AND  |

| 0x55     | 0        | 4-input NAND |

| 0xAA     | 1        | 4-input NOR  |

| 0xAA     | 0        | 4-input OR   |

| 0x00     | 0        | Logic 0      |

| 0x00     | 1        | Logic 1      |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 21-7)

- Gate 2: CLCxGLS1 (Register 21-8)

- Gate 3: CLCxGLS2 (Register 21-9)

- Gate 4: CLCxGLS3 (Register 21-10)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 21-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

## 21.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- · S-R Latch

- · D Flip-Flop with Set and Reset

- · D Flip-Flop with Reset

- · J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 21-2. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

#### 21.1.4 OUTPUT POLARITY

The last stage in the configurable logic cell is the output polarity. Setting the LCxPOL bit of the CLCxPOL register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

# 22.4 Register Definitions: ADC Control

#### REGISTER 22-1: ADCON0: ADC CONTROL REGISTER 0

| R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|----------|---------|---------|---------|---------|---------|---------|---------|

| CHS<5:0> |         |         |         |         |         | GO/DONE | ADON    |

| bit 7    |         |         |         |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

001111 = Reserved. No channel connected.

•

000101 = ANA5 000100 = ANA4

000011 = Reserved. No channel connected.

000010 = ANA2 000001 = ANA1 000000 = ANA0

bit 1 GO/DONE: ADC Conversion Status bit

1 = ADC conversion cycle in progress. Setting this bit starts an ADC conversion cycle. This bit is automatically cleared by hardware when the ADC conversion has completed.

0 = ADC conversion completed/not in progress

bit 0 **ADON:** ADC Enable bit 1 = ADC is enabled

0 = ADC is disabled and consumes no operating current

Note 1: See Section 24.0 "5-Bit Digital-To-Analog Converter (DAC1) Module" for more information.

2: See Section 16.0 "Fixed Voltage Reference (FVR)" for more information.

3: See Section 17.0 "Temperature Indicator Module" for more information.

4: PIC16(L)F18323 only.

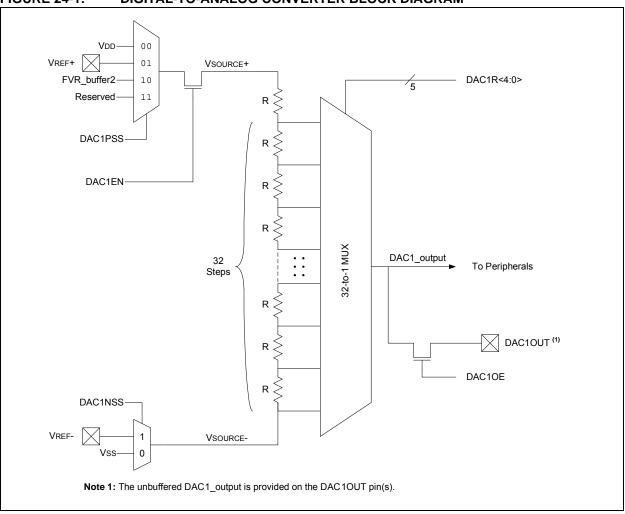

FIGURE 24-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

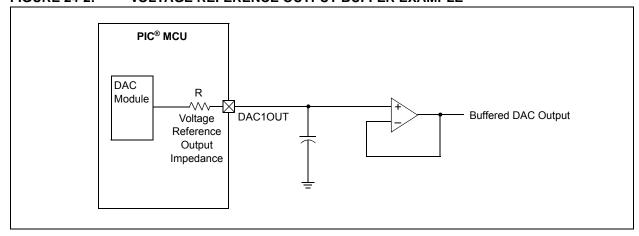

# FIGURE 24-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

# PIC16(L)F18313/18323

### REGISTER 26-3: TOCONO: TIMERO CONTROL REGISTER 0

| R/W-0/0 | U-0 | R-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----|-------|---------|---------|---------|---------|---------|

| T0EN    | _   | T0OUT | T016BIT |         | T0OUTF  | PS<3:0> |         |

| bit 7   |     |       |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 T0EN:TMR0 Enable bit 1 = The module is enabled and operating 0 = The module is disabled and in the lowest-power mode bit 6 Unimplemented: Read as '0' bit 5 T0OUT:TMR0 Output (read-only) bit TMR0 output bit bit 4 T016BIT: TMR0 Operating as 16-bit Timer Select bit 1 = TMR0 is a 16-bit timer 0 = TMR0 is an 8-bit timer bit 3-0 T0OUTPS<3:0>: TMR0 output postscaler (divider) select bits 0000 = 1:1 Postscaler 0001 = 1:2 Postscaler 0010 = 1:3 Postscaler 0011 = 1:4 Postscaler 0100 = 1:5 Postscaler 0101 = 1:6 Postscaler 0110 = 1:7 Postscaler 0111 = 1:8 Postscaler 1000 = 1:9 Postscaler 1001 = 1:10 Postscaler 1010 = 1:11 Postscaler 1011 = 1:12 Postscaler 1100 = 1:13 Postscaler 1101 = 1:14 Postscaler 1110 = 1:15 Postscaler 1111 = 1:16 Postscaler

## REGISTER 27-2: T1GCON: TIMER1 GATE CONTROL REGISTER

| R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W/HC-0/u     | R-x/x  | R/W-0/u | R/W-0/u |

|---------|---------|---------|---------|----------------|--------|---------|---------|

| TMR1GE  | T1GPOL  | T1GTM   | T1GSPM  | T1GGO/<br>DONE | T1GVAL | T1GSS   | S<1:0>  |

| bit 7   |         |         |         |                |        |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

bit 7 TMR1GE: Timer1 Gate Enable bit

If TMR1ON = 0: This bit is ignored If TMR1ON = 1:

1 = Timer1 counting is controlled by the Timer1 gate function

0 = Timer1 is always counting

bit 6 T1GPOL: Timer1 Gate Polarity bit

1 = Timer1 gate is active-high (Timer1 counts when gate is high)0 = Timer1 gate is active-low (Timer1 counts when gate is low)

bit 5 T1GTM: Timer1 Gate Toggle Mode bit

1 = Timer1 Gate Toggle mode is enabled

0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared

Timer1 gate flip-flop toggles on every rising edge.

bit 4 T1GSPM: Timer1 Gate Single-Pulse Mode bit

1 = Timer1 Gate Single-Pulse mode is enabled and is controlling Timer1 gate

0 = Timer1 Gate Single-Pulse mode is disabled

bit 3 **T1GGO/DONE:** Timer1 Gate Single-Pulse Acquisition Status bit

1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge

0 = Timer1 gate single-pulse acquisition has completed or has not been started This bit is automatically cleared when T1GSPM is cleared

bit 2 T1GVAL: Timer1 Gate Value Status bit

Indicates the current state of the Timer1 gate, latched at Q1, provided to TMRxH:TMRxL

Unaffected by Timer1 Gate Enable (TMR1GE)

bit 1-0 T1GSS<1:0>: Timer1 Gate Source Select bits

11 = Comparator 2 optionally synchronized output<sup>(1)</sup>

10 = Comparator 1 optionally synchronized output

01 = Timer0 overflow output

00 = Timer1 gate pin

**Note 1:** PIC16(L)F18323 only; otherwise Reserved – do not use.

SCK SCK SPI Master SDO SDI SPI Slave #1 SDI SDO General I/O SS General I/O General I/O SCK SDI SPI Slave #2 SDO SS SCK SDI SPI Slave SDO SS

FIGURE 30-4: SPI MASTER AND MULTIPLE SLAVE CONNECTION

#### 30.2.1 SPI MODE REGISTERS

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSP1STAT)

- MSSP Control register 1 (SSP1CON1)

- MSSP Control register 3 (SSP1CON3)

- MSSP Data Buffer register (SSP1BUF)

- MSSP Address register (SSP1ADD)

- MSSP Shift register (SSP1SR) (Not directly accessible)

SSP1CON1 and SSP1STAT are the control and status registers in SPI mode operation. The SSP1CON1 register is readable and writable. The lower six bits of the SSP1STAT are read-only. The upper two bits of the SSP1STAT are read/write.

In one SPI master mode, SSP1ADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 30.7 "Baud Rate Generator"**.

SSP1SR is the shift register used for shifting data in and out. SSP1BUF provides indirect access to the SSP1SR register. SSP1BUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSP1SR and SSP1BUF together create a buffered receiver. When SSP1SR receives a complete byte, it is transferred to SSP1BUF and the SSP1IF interrupt is set.

During transmission, the SSP1BUF is not buffered. A write to SSP1BUF will write to both SSP1BUF and SSP1SR.

# 31.6 Register Definitions: EUSART1 Control

#### REGISTER 31-1: TX1STA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0             | R/W-0/0 | R/W-0/0 | R/W-0/0 | R-1/1 | R/W-0/0 |

|---------|---------|---------------------|---------|---------|---------|-------|---------|

| CSRC    | TX9     | TXEN <sup>(1)</sup> | SYNC    | SENDB   | BRGH    | TRMT  | TX9D    |

| bit 7   |         |                     |         |         |         |       | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 CSRC: Clock Source Select bit

Asynchronous mode:

Unused in this mode – value ignored

Synchronous mode:

1 = Master mode (clock generated internally from BRG)

0 = Slave mode (clock from external source)

bit 6 TX9: 9-Bit Transmit Enable bit

1 = Selects 9-bit transmission0 = Selects 8-bit transmission

bit 5 **TXEN:** Transmit Enable bit<sup>(1)</sup>

1 = Transmit enabled

0 = Transmit disabled

bit 4 SYNC: EUSART Mode Select bit

1 = Synchronous mode0 = Asynchronous mode

bit 3 **SENDB:** Send Break Character bit

Asynchronous mode:

1 = Send SYNCH BREAK on next transmission – start bit, followed by 12 '0' bits, followed by Stop bit; cleared by hardware upon completion

0 = SYNCH BREAK transmission disabled or completed

Synchronous mode:

Unused in this mode - value ignored

bit 2 BRGH: High Baud Rate Select bit

Asynchronous mode:

1 = High speed

0 = Low speed

Synchronous mode:

Unused in this mode - value ignored

bit 1 TRMT: Transmit Shift Register Status bit

1 = TSR empty 0 = TSR full

bit 0 **TX9D:** Ninth bit of Transmit Data

Can be address/data bit or a parity bit.

Note 1: SREN/CREN overrides TXEN in Sync mode.

# 34.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                                |

| Operands:        | $ -32 \leq k \leq 31 $ $ n \in [\ 0,\ 1] $                                                              |

| Operation:       | $FSR(n) + k \to FSR(n)$                                                                                 |

| Status Affected: | None                                                                                                    |

| Description:     | The signed 6-bit literal 'k' is added to the contents of the FSRnH:FSRnL register pair.                 |

|                  | FSRn is limited to the range 0000h-FFFFh. Moving beyond these bounds will cause the FSR to wrap-around. |

| ANDLW            | AND literal with W                                                                                        |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ANDLW k                                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                                       |

| Operation:       | (W) .AND. $(k) \rightarrow (W)$                                                                           |

| Status Affected: | Z                                                                                                         |

| Description:     | The contents of W register are AND'ed with the 8-bit literal 'k'. The result is placed in the W register. |

| ADDLW            | Add literal and W                                                                                             |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] ADDLW k                                                                                               |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |

| Operation:       | $(W) + k \rightarrow (W)$                                                                                     |  |  |  |

| Status Affected: | C, DC, Z                                                                                                      |  |  |  |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |  |  |  |

| ANDWF            | AND W with f                                                                                                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ANDWF f,d                                                                                                                                    |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                     |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                              |

| Status Affected: | Z                                                                                                                                                      |

| Description:     | AND the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDWF f,d                                                                                                                                                    |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                     |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                  |

| Status Affected: | C, DC, Z                                                                                                                                                               |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                               |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ASRF f {,d}                                                                                                                                                                                                |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                   |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                                                              |

| Status Affected: | C, Z                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are shifted one bit to the right through the Carry flag. The MSb remains unchanged. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'. |

|                  | ▶ register f                                                                                                                                                                                                         |

| ADDWFC           | ADD W and CARRY bit to f                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDWFC f {,d}                                                                                                                                        |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                             |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                             |

| Status Affected: | C, DC, Z                                                                                                                                                       |

| Description:     | Add W, the Carry flag and data memory location 'f'. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed in data memory location 'f'. |

| BCF              | Bit Clear f                         |  |  |  |

|------------------|-------------------------------------|--|--|--|

| Syntax:          | [ label ] BCF f,b                   |  |  |  |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$   |  |  |  |

| Operation:       | $0 \rightarrow (f < b >)$           |  |  |  |

| Status Affected: | None                                |  |  |  |

| Description:     | Bit 'b' in register 'f' is cleared. |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$                                                                                                                                                                            |

| Operation:       | skip if (f < b >) = 0                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.  If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                               |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] BRA label<br>[ label ] BRA \$+k                                                                                                                                                                                     |  |  |  |  |  |  |

| Operands:        | -256 ≤ label - PC + 1 ≤ 255<br>-256 ≤ k ≤ 255                                                                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + k. This instruction is a 2-cycle instruction. This branch has a limited range. |  |  |  |  |  |  |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                         |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                          |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                        |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed. If bit 'b' is '1', then the next instruction is discarded and a $\mathtt{NOP}$ is executed instead, making this a 2-cycle instruction. |

| BRW              | Relative Branch with W                                                                                                                                                                         |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] BRW                                                                                                                                                                                  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                           |  |  |  |  |  |

| Operation:       | $(PC) + (W) \rightarrow PC$                                                                                                                                                                    |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Add the contents of W (unsigned) to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + (W). This instruction is a 2-cycle instruction. |  |  |  |  |  |

| BSF              | Bit Set f                                                           |  |  |  |

|------------------|---------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] BSF f,b                                                   |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |  |

| Operation:       | $1 \rightarrow (f < b >)$                                           |  |  |  |

| Status Affected: | None                                                                |  |  |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |  |  |  |

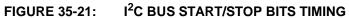

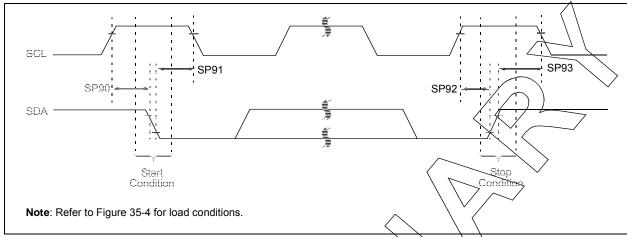

TABLE 35-23: I<sup>2</sup>C BUS START/STOP BITS CHARACTER/IST<del>ICS</del>

| Standard Operating Conditions (unless otherwise stated) |         |                 |              |      |          |               |       |                                    |  |

|---------------------------------------------------------|---------|-----------------|--------------|------|----------|---------------|-------|------------------------------------|--|

| Param.<br>No.                                           | Symbol  | Characteristic  |              | Min. | Typ      | Max           | Units | Conditions                         |  |

| SP90*                                                   | Tsu:sta | Start condition | 100 kHz mode | 4700 | _/       | <i>&gt;</i> _ | ns    | Only relevant for Repeated Start   |  |

|                                                         |         | Setup time      | 400 kHz mode | 600  | 7        | _             |       | condition                          |  |

| SP91*                                                   | THD:STA | Start condition | 100 kHz mode | 4000 | <u> </u> | _             | ns    | After this period, the first clock |  |

|                                                         |         | Hold time       | 400 kHz mode | 600  | _        | _             |       | pulse is generated                 |  |

| SP92*                                                   | Tsu:sto | Stop condition  | 100 kH2 mode | 4700 | _        | _             | ns    |                                    |  |

|                                                         |         | Setup time      | 400 kHz mode | 600  | _        | _             |       |                                    |  |

| SP93                                                    | THD:STO | Stop condition  | 100 kHz mode | 4000 | _        | _             | ns    |                                    |  |

|                                                         |         | Hold time       | 400 kHz mode | 600  | _        | _             |       |                                    |  |

<sup>\*</sup> These parameters are characterized but not tested.

FIGURE 35-22: I<sup>2</sup>C BUS DATA TIMING

# 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |             |             |      |  |  |  |

|--------------------------|-------------|-------------|-------------|------|--|--|--|

| Dimension                | MIN         | NOM         | MAX         |      |  |  |  |

| Number of Pins           | N           |             | 8           |      |  |  |  |

| Pitch                    | е           |             | 1.27 BSC    |      |  |  |  |

| Overall Height           | Α           | =           | -           | 1.75 |  |  |  |

| Molded Package Thickness | A2          | 1.25        | -           | -    |  |  |  |

| Standoff §               | A1          | 0.10        | -           | 0.25 |  |  |  |

| Overall Width            | E           | 6.00 BSC    |             |      |  |  |  |

| Molded Package Width     | E1          | 3.90 BSC    |             |      |  |  |  |

| Overall Length           | D           | 4.90 BSC    |             |      |  |  |  |

| Chamfer (Optional)       | h           | 0.25 - 0.50 |             |      |  |  |  |

| Foot Length              | L           | 0.40        | 0.40 - 1.27 |      |  |  |  |

| Footprint                | L1          | 1.04 REF    |             |      |  |  |  |

| Foot Angle               | φ           | 0°          | -           | 8°   |  |  |  |

| Lead Thickness           | С           | 0.17        | -           | 0.25 |  |  |  |

| Lead Width               | b           | 0.31        | -           | 0.51 |  |  |  |

| Mold Draft Angle Top     | α           | 5° - 15°    |             |      |  |  |  |

| Mold Draft Angle Bottom  | β           | 5° - 15°    |             |      |  |  |  |

## Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-057C Sheet 2 of 2