Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 6                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 8-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18313-i-p |

FIGURE 1-1: PIC16(L)F18313/18323 BLOCK DIAGRAM Program Flash Memory RAM PORTA Timing Generation HFINTOSC/ PORTC<sup>(1)</sup> CPU CLKIN **LFINTOSC**  $\boxtimes \blacktriangleleft$ Oscillator See Figure 3-1 MCLR 🛚 DSM NCO PWM Timer0 Timer1 Timer2 MSSP Comparators **CWG** Temp. ADC CLCs **FVR** DAC CCPs **EUSART** Indicator 10-Bit Note 1: PIC16(L)F18323 only. 2: See applicable chapters for more information on peripherals.

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC16(L)F183XX MICROCONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the PIC16(L)F183XX family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and VSS pins (see Section 2.2 "Power Supply Pins")

- MCLR pin (when configured for external operation)

(see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- ICSPCLK/ICSPDAT pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.4 "ICSP<sup>™</sup> Pins")

- OSC1 and OSC2 pins when an external oscillator source is used

(see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

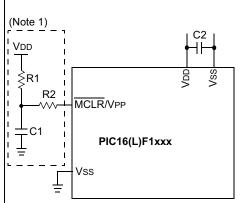

The minimum mandatory connections are shown in Figure 2-1.

## FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

Key (all values are recommendations):

C1 and C2: 0.1  $\mu\text{F}$ , 20V ceramic

R1: 10 kΩ

R2:  $100\Omega$  to  $470\Omega$

Note1: Only when MCLRE configuration bit is 1 and the  $\overline{\text{MCLR}}$  pin does not have a weak pull-up.

### 2.2 Power Supply Pins

### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins (VDD and Vss) is required. All VDD and Vss pins must be connected. None can be left floating.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1 µF (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended to

place the capacitors on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is no greater

than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 μF to 0.001 μF. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1 μF in parallel with 0.001 μF).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ .

TABLE 4-4: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

| Address    | Name                                            | PIC16(L)F18313 | PIC16(L)F18323 | Bit 7  | Bit 6                                                                                    | Bit 5   | Bit 4   | Bit 3    | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on all other Resets |

|------------|-------------------------------------------------|----------------|----------------|--------|------------------------------------------------------------------------------------------|---------|---------|----------|-------|-------|-------|-----------------------|---------------------------|

| Bank 10-11 | Bank 10-11                                      |                |                |        |                                                                                          |         |         |          |       |       |       |                       |                           |

|            | CPU CORE REGISTERS; see Table 4-2 for specifics |                |                |        |                                                                                          |         |         |          |       |       |       |                       |                           |

| 50Ch-51Fh  | _                                               | _              | _              |        | Unimplemented                                                                            |         |         |          |       |       |       | _                     | _                         |

| 58Ch-59Fh  | _                                               | _              | _              |        |                                                                                          |         | Unimp   | lemented |       |       |       | _                     | _                         |

| Bank 12    |                                                 |                |                |        |                                                                                          |         |         |          |       |       |       |                       |                           |

| 60Ch       | _                                               | _              | _              |        | Unimplemented                                                                            |         |         |          |       |       | _     | _                     |                           |

| 60Dh       | _                                               | _              | _              |        | Unimplemented                                                                            |         |         |          |       |       | _     | _                     |                           |

| 60Eh       | _                                               | _              | _              |        | Unimplemented                                                                            |         |         |          |       |       | _     | _                     |                           |

| 60Fh       | _                                               | _              | _              |        | Unimplemented                                                                            |         |         |          |       |       | _     | _                     |                           |

| 610h       | _                                               | _              | _              |        | Unimplemented                                                                            |         |         |          |       |       | _     | _                     |                           |

| 611h       | _                                               | _              | _              |        |                                                                                          |         | Unimpl  | lemented |       |       |       | _                     | _                         |

| 612h       | _                                               | _              | _              |        |                                                                                          |         | Unimpl  | lemented |       |       |       | _                     | _                         |

| 613h       | _                                               | _              | -              |        |                                                                                          |         | Unimpl  | lemented |       |       |       | _                     | _                         |

| 614h       | _                                               | _              | -              |        |                                                                                          |         | Unimpl  | lemented |       |       |       | _                     | _                         |

| 615h       | _                                               | _              | -              |        |                                                                                          |         | Unimpl  | lemented |       |       |       | _                     | _                         |

| 616h       | _                                               | _              | _              |        |                                                                                          |         | Unimpl  | emented  |       |       |       | _                     | _                         |

| 617h       | PWM5DCL                                         |                |                | PWM5D  | C<1:0>                                                                                   | _       | _       | _        | _     | _     | _     | xx                    | uu                        |

| 618h       | PWM5DCH                                         |                |                |        |                                                                                          |         | PWM5    | DC<9:2>  |       |       |       | xxxx xxxx             | uuuu uuuu                 |

| 619h       | PWM5CON                                         |                |                | PWM5EN |                                                                                          | PWM5OUT | PWM5POL | _        | _     | _     | _     | 0-00                  | 0-00                      |

| 61Ah       | PWM6DCL                                         |                |                | PWM6D  | C<1:0>                                                                                   | _       | _       | _        | _     | _     | _     | xx                    | uu                        |

| 61Bh       | PWM6DCH                                         |                |                |        |                                                                                          |         | PWM6    | DC<9:2>  |       |       |       | xxxx xxxx             | uuuu uuuu                 |

| 61Ch       | PWM6CON                                         |                |                | PWM6EN | PWM6EN         —         PWM6OUT         PWM6POL         —         —         —         — |         |         |          |       |       | 0-00  | 0-00                  |                           |

| 61Dh-61Fh  | _                                               | _              | _              |        |                                                                                          |         | Unimpl  | lemented |       |       |       | _                     | _                         |

PIC16(L)F18313/18323

### 4.5 Indirect Addressing

The INDF registers are not physical registers. Any instruction that accesses an INDF register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSR address specifies one of the two INDF registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSR register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into four memory regions:

- · Traditional/Banked Data Memory

- · Linear Data Memory

- Program Flash Memory

- EEPROM

### 4.5.1 TRADITIONAL/BANKED DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

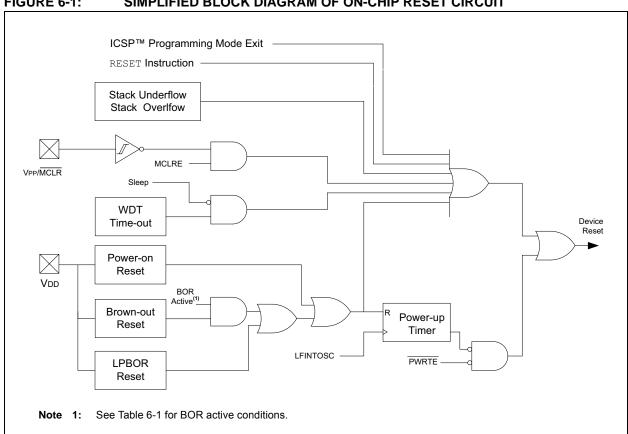

#### 6.0 **RESETS**

There are multiple ways to reset this device:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Low-Power Brown-Out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- · Stack Overflow

- · Stack Underflow

- · Programming mode exit

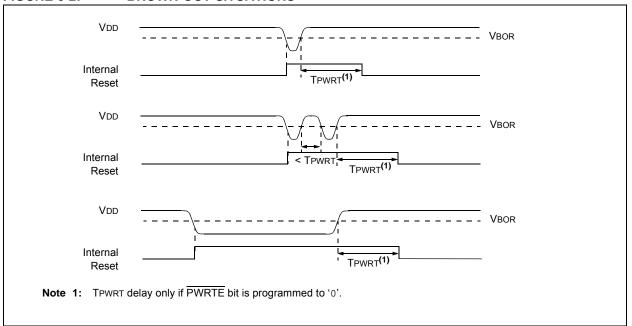

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 6-1.

FIGURE 6-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep, but device wake-up will be delayed until the BOR can determine that the VDD is higher than the BOR threshold. The device wake-up will be delayed until the BOR is ready.

### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device wake from Sleep is not delayed by the BOR ready condition or the VDD level only when the SBOREN bit is cleared in software and the device is starting up from a non POR/BOR reset event.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

### 6.2.4 BOR ALWAYS OFF

When the BOREN bits of Configuration Word 2 are programmed to '00', the BOR is always disabled. In this configuration, setting the SBOREN bit will have no effect on the BOR operation.

### 11.5 Register Definitions: Program Flash Memory Control

### REGISTER 11-1: NVMDATL: NONVOLATILE MEMORY DATA LOW BYTE REGISTER

| R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |

|---------|-------------|---------|---------|---------|---------|---------|---------|--|--|--|--|

|         | NVMDAT<7:0> |         |         |         |         |         |         |  |  |  |  |

| bit 7   | bit 7 bit 0 |         |         |         |         |         |         |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **NVMDAT<7:0>**: Read/write value for Least Significant bits of Program Memory

### REGISTER 11-2: NVMDATH: NONVOLATILE MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|----------|---------|---------|

| _     | _   |         |         | NVMD    | AT<13:8> |         |         |

| bit 7 |     |         |         |         |          |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

bit 5-0 NVMDAT<13:8>: Read/write value for Most Significant bits of Program Memory<sup>(1)</sup>

Note 1: This byte is ignored when writing to EEPROM.

### REGISTER 11-3: NVMADRL: NONVOLATILE MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |

|---------|-------------|---------|---------|---------|---------|---------|---------|--|--|--|--|

|         | NVMADR<7:0> |         |         |         |         |         |         |  |  |  |  |

| bit 7   | bit 7 bit 0 |         |         |         |         |         |         |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **NVMADR<7:0>**: Specifies the Least Significant bits for Program Memory Address

### REGISTER 11-4: NVMADRH: NONVOLATILE MEMORY ADDRESS HIGH BYTE REGISTER

|   | U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0      | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---|-------|---------|---------|---------|--------------|---------|---------|---------|

|   | _     |         |         |         | NVMADR<14:8> | •       |         |         |

| b | oit 7 |         |         |         |              |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 Unimplemented: Read as '1'

bit 6-0 NVMADR<14:8>: Specifies the Most Significant bits for Program Memory Address

### REGISTER 11-5: NVMCON1: NONVOLATILE MEMORY CONTROL 1 REGISTER

| U-0   | R/W-0/0 | R/W-0/0 | R/W/HC-0/0 | R/W/HS-x/q | R/W-0/0 | R/S/HC-0/0 | R/S/HC-0/0 |

|-------|---------|---------|------------|------------|---------|------------|------------|

| _     | NVMREGS | LWLO    | FREE       | WRERR      | WREN    | WR         | RD         |

| bit 7 |         |         |            |            |         |            | bit 0      |

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

S = Bit can only be set

x = Bit is unknown

-n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set

'0' = Bit is cleared

HC = Bit is cleared by hardware

bit 7 Unimplemented: Read as '0'

bit 6 **NVMREGS:** Configuration Select bit

1 = Access EEPROM, Configuration, User ID and Device ID Registers

0 = Access Program Flash Memory

bit 5 LWLO: Load Write Latches Only bit

When FREE = 0:

1 = The next WR command updates the write latch for this word within the row; no memory operation is initiated

0 = The next WR command writes data or erases

Otherwise: The bit is ignored.

bit 4 FREE: Program Flash Memory Erase Enable bit

When NVMREGS:NVMADR points to a Program Flash Memory location:

1 = Performs an erase operation with the next WR command; the 32-word pseudo-row containing the indicated address is erased (to all 1s) to prepare for writing

0 = All erase operations have completed normally

bit 3 WRERR: Program/Erase Error Flag bit (1,2,3)

This bit is normally set by hardware.

1 = A write operation was interrupted by a Reset, or WR was written to one while NVMADR points to a write-protected address.

0 = The program or erase operation completed normally

bit 2 WREN: Program/Erase Enable bit

1 = Allows program/erase cycles

0 = Inhibits programming/erasing of program Flash

bit 1 WR: Write Control bit(4,5,6)

When NVMREG:NVMADR points to a EEPROM location:

1 = Initiates an erase/program cycle at the corresponding EEPROM location

0 = NVM program/erase operation is complete and inactive

When NVMREG:NVMADR points to a Program Flash Memory location:

1 = Initiates the operation indicated by Table 11-4

0 = NVM program/erase operation is complete and inactive

bit 0 **RD**: Read Control bit<sup>(7)</sup>

1 = Initiates a read at address = NVMADR1, and loads data to NVMDAT Read takes one instruction cycle and the bit is cleared when the operation is complete. The bit can only be set (not cleared) in software.

0 = NVM read operation is complete and inactive

Note 1: Bit may change while WR = 1 (during the EEPROM write operation it may be '0' or '1').

2: Bit must be cleared by software; hardware will not clear this bit.

3: Bit may be written to '1' by software in order to implement test sequences.

4: This bit can only be set by following the unlock sequence of Section 11.4.2 "NVM Unlock Sequence".

**5:** Operations are self-timed, and the WR bit is cleared by hardware when complete.

6: Once a write operation is initiated, setting this bit to zero will have no effect.

7: Reading from EEPROM loads only NVMDATL<7:0> (Register 11-1).

## 14.0 PERIPHERAL MODULE DISABLE

The PIC16(L)F18313/18323 provides the ability to disable selected modules, placing them into the lowest possible power mode.

For legacy reasons, all modules are ON by default following any Reset.

### 14.1 Disabling a module

Disabling a module has the following effects:

- All clock and control inputs to the module are suspended; there are no logic transitions, and the module will not function.

- · The module is held in Reset.

- Writing to the SFRs is disabled

- Reads return 00h

- Analog outputs are disabled; Digital outputs read '0'.

### 14.2 Enabling a module

When the register bit is cleared, the module is reenabled and will be in its Reset state; SFR data will reflect the POR Reset values.

Depending on the module, it may take up to one full instruction cycle for the module to become active. There should be no interaction with the module (e.g., writing to registers) for at least one instruction after it has been re-enabled.

### 14.3 System Clock disable

Setting SYSCMD (PMD0, Register 14-1) disables the system clock (Fosc) distribution network to the peripherals. Not all peripherals make use of SYSCLK, so not all peripherals are affected. Refer to the specific peripheral description to see if it will be affected by this bit

### 18.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 35-14 for more details.

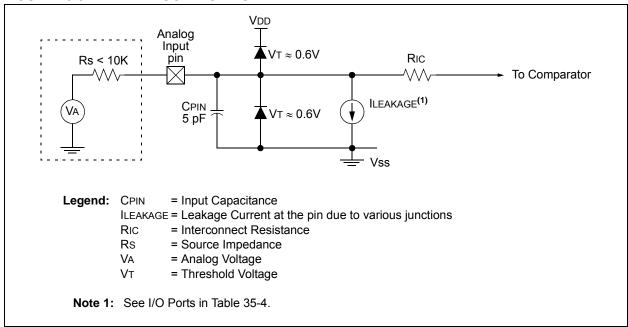

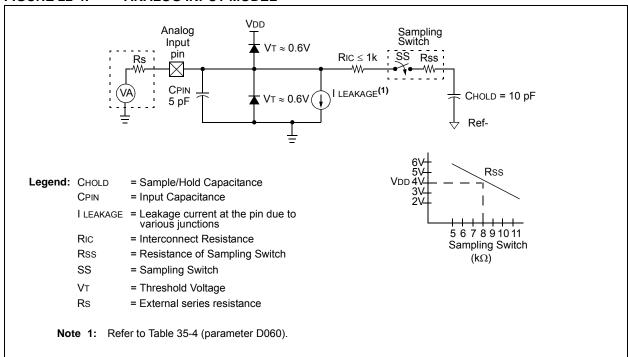

## 18.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 18-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will provide an input based on their level as either a TTL or ST input buffer.

- **2:** Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

FIGURE 18-3: ANALOG INPUT MODEL

FIGURE 22-4: ANALOG INPUT MODEL

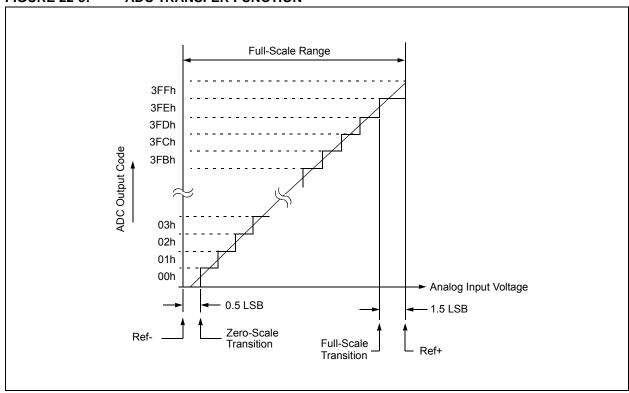

### FIGURE 22-5: ADC TRANSFER FUNCTION

### 25.1 DSM Operation

The DSM module can be enabled by setting the MDEN bit in the MDCON register. Clearing the MDEN bit in the MDCON register, disables the DSM module by automatically switching the carrier high and carrier low signals to the Vss signal source. The modulator signal source is also switched to the MDBIT in the MDCON register. This not only assures that the DSM module is inactive, but that it is also consuming the least amount of current

The values used to select the carrier high, carrier low, and modulator sources held by the Modulation Source, Modulation High Carrier, and Modulation Low Carrier control registers are not affected when the MDEN bit is cleared and the DSM module is disabled. The values inside these registers remain unchanged while the DSM is inactive. The sources for the carrier high, carrier low and modulator signals will once again be selected when the MDEN bit is set and the DSM module is again enabled and active.

The modulated output signal can be disabled without shutting down the DSM module. The DSM module will remain active and continue to mix signals, but the output value will not be sent to the DSM pin. During the time that the output is disabled, the DSM pin will remain low. The modulated output can be disabled by clearing the MDEN bit in the MDCON register.

### 25.2 Modulator Signal Sources

The modulator signal can be supplied from the following sources:

- CCP1 Output

- · CCP2 Output

- PWM5 Output

- · PWM6 Output

- MSSP1 SDO1 (SPI mode only)

- Comparator C1 Output

- Comparator C2 Output (PIC16(L)F18323 only)

- EUSART TX Output

- · External Signal on MDMIN pin

- NCO1 Output

- CLC1 Output

- · CLC2 Output

- · MDBIT bit in the MDCON register

The modulator signal is selected by configuring the MDMS <3:0> bits in the MDSRC register.

### 25.3 Carrier Signal Sources

The carrier high signal and carrier low signal can be supplied from the following sources:

- CCP1 Output

- · CCP2 Output

- PWM5 Output

- · PWM6 Output

- NCO1 Output

- Fosc (system clock)

- HFINTOSC

- · CLC1 output

- CLC2 output

- CLKR

- · External Signal on MDCIN1 pin

- · External Signal on MDCIN2 pin

- Vss

The carrier high signal is selected by configuring the MDCH <3:0> bits in the MDCARH register. The carrier low signal is selected by configuring the MDCL <3:0> bits in the MDCARL register.

### 25.4 Carrier Synchronization

During the time when the DSM switches between carrier high and carrier low signal sources, the carrier data in the modulated output signal can become truncated. To prevent this, the carrier signal can be synchronized to the modulator signal. When the modulator signal transitions away from the synchronized carrier, the unsynchronized carrier source is immediately active, while the synchronized carrier remains active until its next falling edge. When the modulator signal transitions back to the synchronized carrier, the unsynchronized carrier is immediately disabled, and the modulator waits until the next falling edge of the synchronized carrier before the synchronized carrier becomes active.

Synchronization is enabled separately for the carrier high and carrier low signal sources. Synchronization for the carrier high signal is enabled by setting the MDCHSYNC bit in the MDCARH register. Synchronization for the carrier low signal is enabled by setting the MDCLSYNC bit in the MDCARL register.

Figure 25-1 through Figure 25-6 show timing diagrams of using various synchronization methods.

### REGISTER 25-4: MDCARL: MODULATION LOW CARRIER CONTROL REGISTER

| U-0   | R/W-x/u | R/W-x/u  | U-0 | R/W-x/u                  | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|---------|----------|-----|--------------------------|---------|---------|---------|

| _     | MDCLPOL | MDCLSYNC | -   | MDCL<3:0> <sup>(1)</sup> |         |         |         |

| bit 7 |         |          |     |                          |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| hit 7   | Unimplemented, Reed as '0'                                                                                              |  |  |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| bit 7   | Unimplemented: Read as '0'                                                                                              |  |  |  |  |  |  |  |

| bit 6   | MDCLPOL: Modulator Low Carrier Polarity Select bit                                                                      |  |  |  |  |  |  |  |

|         | 1 = Selected low carrier signal is inverted                                                                             |  |  |  |  |  |  |  |

|         | 0 = Selected low carrier signal is not inverted                                                                         |  |  |  |  |  |  |  |

| bit 5   | MDCLSYNC: Modulator Low Carrier Synchronization Enable bit                                                              |  |  |  |  |  |  |  |

|         | 1 = Modulator waits for a falling edge on the low time carrier signal before allowing a switch to the high time carrier |  |  |  |  |  |  |  |

|         | 0 = Modulator Output is not synchronized to the low time carrier signal <sup>(1)</sup>                                  |  |  |  |  |  |  |  |

| bit 4   | Unimplemented: Read as '0'                                                                                              |  |  |  |  |  |  |  |

| bit 3-0 | MDCL<3:0> Modulator Data High Carrier Selection bits (1)                                                                |  |  |  |  |  |  |  |

|         | 1111 = Reserved. No channel connected.                                                                                  |  |  |  |  |  |  |  |

|         | 1110 = Reserved. No channel connected.                                                                                  |  |  |  |  |  |  |  |

|         | 1101 = CLC2 output                                                                                                      |  |  |  |  |  |  |  |

|         | 1100 = CLC1 output                                                                                                      |  |  |  |  |  |  |  |

|         | 1011 = HFINTOSC                                                                                                         |  |  |  |  |  |  |  |

|         | 1010 = Fosc                                                                                                             |  |  |  |  |  |  |  |

|         | 1001 = Reserved. No channel connected.                                                                                  |  |  |  |  |  |  |  |

|         | 1000 = NCO1 output                                                                                                      |  |  |  |  |  |  |  |

|         | 0111 = PWM6 output                                                                                                      |  |  |  |  |  |  |  |

|         | 0110 = PWM5 output                                                                                                      |  |  |  |  |  |  |  |

|         | 0101 = CCP2 output (PWM Output mode only)                                                                               |  |  |  |  |  |  |  |

|         | 0100 = CCP1 output (PWM Output mode only)                                                                               |  |  |  |  |  |  |  |

|         | 0011 = Reference clock module signal (CLKR)                                                                             |  |  |  |  |  |  |  |

|         | 0010 = MDCIN2PPS                                                                                                        |  |  |  |  |  |  |  |

|         | 0001 = MDCIN1PPS                                                                                                        |  |  |  |  |  |  |  |

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

0000 = Vss

### 28.1 Timer2 Operation

The clock input to the Timer2 modules is the system instruction clock (Fosc/4).

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, T2CKPS<1:0> of the T2CON register. The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output "Timer2 counter/postscaler (see Section 28.2 Interrupt").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, whereas the PR2 register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- · a write to the TMR2 register

- · a write to the T2CON register

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- · Watchdog Timer (WDT) Reset

- Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

Note: TMR2 is not cleared when T2CON is written

### 28.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2-to-PR2 match) provides the input for the 4-bit counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF of the PIR1 register. The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE, of the PIE1 register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0>, of the T2CON register.

### 28.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 30.0 "Master Synchronous Serial Port (MSSP) Module".

### 28.4 Timer2 Operation During Sleep

The Timer2 timers cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and PR2 registers will remain unchanged while the processor is in Sleep mode.

### REGISTER 29-4: CCPRxH REGISTER: CCPx REGISTER HIGH BYTE

| R/W-x/x | R/W-x/x     | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |  |  |  |

|---------|-------------|---------|---------|---------|---------|---------|---------|--|--|--|

|         | CCPRx<15:8> |         |         |         |         |         |         |  |  |  |

| bit 7   | bit 7 bit 0 |         |         |         |         |         |         |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Reset

'1' = Bit is set '0' = Bit is cleared

bit 7-0 CCPxMODE = Capture Mode

CCPRxH<7:0>: Captured value of TMR1H

CCPxMODE = Compare Mode

**CCPRxH<7:0>:** MS Byte compared to TMR1H <u>CCPxMODE = PWM Modes when CCPxFMT = 0</u>

CCPRxH<7:2>: Not used

CCPRxH<1:0>: Pulse-width Most Significant two bits CCPxMODE = PWM Modes when CCPxFMT = 1

CCPRxH<7:0>: Pulse-width Most Significant eight bits

### 30.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

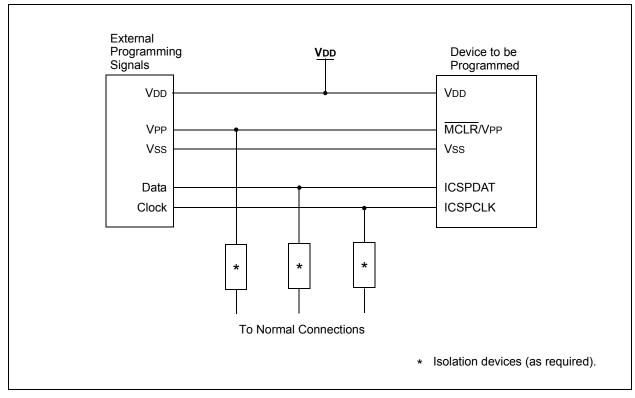

FIGURE 33-2: PICkit™ PROGRAMMER STYLE CONNECTOR INTERFACE

FIGURE 33-3: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

### 35.0 ELECTRICAL SPECIFICATIONS

### 35.1 Absolute Maximum Ratings<sup>(†)</sup>

Ambient temperature under bias -40°C to +125°C Storage temperature ......-65°C to +150°C Voltage on pins with respect to Vss on VDD pin -0.3V to +6.5V PIC16F18313/18323 ..... PIC16LF18313/18323 ..... -0.3V to +4.0V -0.3V to +9.0V on MCLR pin ..... ..........0.3V to (VDD + 0.3V) on all other pins Maximum current on Vss pin<sup>(1)</sup>  $-40^{\circ}\text{C} < \text{TA} < +85^{\circ}\text{C}$ ..... 250 mA  $85^{\circ}C < TA \le +125^{\circ}C$  ..... on V<sub>DD</sub> pin<sup>(1)</sup>  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ 85°C < TA ≤ +125°C ..... on any I/O pin current sourced...... Clamp current, Ik (VPIN < 0 or VPIN > VDD) ...... Total power dissipation<sup>(2)</sup>.....

Note 1: Maximum current rating requires even load distribution across I/O pins. Maximum current rating may be limited by the device package power dissipation characterizations, see Table 35-3 to calculate device specifications.

2: Power dissipation is calculated as follows:

PDIS = VDD x {IDD  $-\Sigma$  IOH}  $+\Sigma$  {(VDD -VOH) x IOH} +  $\Sigma$  (VOI x IOL)

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

### 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units  | MILLIMETERS |          |      |  |

|--------------------------|--------|-------------|----------|------|--|

| Dimension                | Limits | MIN         | NOM      | MAX  |  |

| Number of Pins           | N      |             | 8        |      |  |

| Pitch                    | е      |             | 1.27 BSC |      |  |

| Overall Height           | Α      | =           | -        | 1.75 |  |

| Molded Package Thickness | A2     | 1.25        | -        | -    |  |

| Standoff §               | A1     | 0.10        | -        | 0.25 |  |

| Overall Width            | Е      | 6.00 BSC    |          |      |  |

| Molded Package Width     | E1     | 3.90 BSC    |          |      |  |

| Overall Length           | D      |             | 4.90 BSC |      |  |

| Chamfer (Optional)       | h      | 0.25        | -        | 0.50 |  |

| Foot Length              | L      | 0.40        | -        | 1.27 |  |

| Footprint                | L1     |             | 1.04 REF |      |  |

| Foot Angle               | φ      | 0°          | -        | 8°   |  |

| Lead Thickness           | С      | 0.17        | -        | 0.25 |  |

| Lead Width               | b      | 0.31        | -        | 0.51 |  |

| Mold Draft Angle Top     | α      | 5°          | -        | 15°  |  |

| Mold Draft Angle Bottom  | β      | 5°          | -        | 15°  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-057C Sheet 2 of 2

### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2015-2016, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-1197-0