Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 8-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18313-i-sn |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                                                               | Function | Input<br>Type    | Output<br>Type | Description                                                   |

|------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------------|---------------------------------------------------------------|

| RA0/ANA0/C1IN0+/                                                                                                                   | RA0      | TTL/ST           | CMOS           | General purpose I/O.                                          |

| DAC1OUT/CLCIN3 <sup>(1)</sup> /MDCIN1 <sup>(1)</sup> /<br>ICSPDAT/ICDDAT                                                           | ANA0     | AN               |                | ADC Channel A0 input.                                         |

| ICSPDAT/ICDDAT                                                                                                                     | C1IN0+   | AN               | _              | Comparator C1 positive input.                                 |

|                                                                                                                                    | DAC10UT  | _                | AN             | Digital-to-Analog Converter output.                           |

|                                                                                                                                    | CLCIN3   | TTL/ST           | _              | Configurable Logic Cell source input.                         |

|                                                                                                                                    | MDCIN1   | TTL/ST           | _              | Modular Carrier input 1.                                      |

|                                                                                                                                    | ICSPDAT  | TTL/ST           | CMOS           | ICSP™ Data I/O.                                               |

|                                                                                                                                    | ICDDAT   | TTL/ST           | CMOS           | In-Circuit Debug Data I/O.                                    |

| RA1/ANA1/VREF+/C1IN0-/                                                                                                             | RA1      | TTL/ST           | CMOS           | General purpose I/O.                                          |

| MDMIN <sup>(1)</sup> /CLCIN2 <sup>(1)</sup> /SCK <sup>(3)</sup> /<br>SCL <sup>(3)</sup> /RX <sup>(1)</sup> /DAC1 <sub>REF</sub> +/ | ANA1     | AN               | _              | ADC Channel A1 input.                                         |

| ICSPCLK/ICDCLK                                                                                                                     | VREF+    | AN               | _              | ADC Voltage Reference Positive input.                         |

|                                                                                                                                    | C1IN0-   | AN               | _              | Comparator C1 negative input.                                 |

|                                                                                                                                    | MDMIN    | TTL/ST           | _              | Modulator Source Input.                                       |

|                                                                                                                                    | CLCIN2   | TTL/ST           | _              | Configurable Logic Cell source input.                         |

|                                                                                                                                    | SCK      | TTL/ST           | _              | SPI clock.                                                    |

|                                                                                                                                    | SCL      | l <sup>2</sup> C | OD             | I <sup>2</sup> C clock input/output.                          |

|                                                                                                                                    | RX       | TTL/ST           | _              | EUSART asynchronous input.                                    |

|                                                                                                                                    | DAC1REF+ | AN               | —              | Digital-to-Analog Converter positive reference voltage input. |

|                                                                                                                                    | ICSPCLK  | TTL/ST           | CMOS           | Serial Programming Clock.                                     |

|                                                                                                                                    | ICDCLK   | TTL/ST           | CMOS           | In-Circuit Debug Clock.                                       |

| RA2/ANA2/VREF-/DAC1REF-/                                                                                                           | RA2      | TTL/ST           | CMOS           | General purpose I/O.                                          |

| SDI <sup>(1,3)</sup> /SDA <sup>(1,3)</sup> /T0CKI <sup>(1)</sup> /<br>CWG1IN <sup>(1)</sup> /INT <sup>(1)</sup>                    | ANA2     | AN               | _              | ADC Channel A3 input.                                         |

|                                                                                                                                    | VREF-    | AN               |                | ADC Voltage Reference Negative input.                         |

|                                                                                                                                    | DAC1REF- | AN               |                | Digital-to-Analog Converter negative reference voltage input. |

|                                                                                                                                    | SDI      | TTL/ST           | CMOS           | SPI Data Input.                                               |

|                                                                                                                                    | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C clock input/output.                          |

|                                                                                                                                    | TOCKI    | TTL/ST           | _              | TMR0 clock input.                                             |

|                                                                                                                                    | CWG1IN   | TTL/ST           | -              | Complementary Waveform Generator input.                       |

|                                                                                                                                    | INT      | TTL/ST           | _              | External interrupt.                                           |

| RA3/MCLR/VPP/SS <sup>(1)</sup> /CLCIN0 <sup>(1)</sup>                                                                              | RA3      | TTL/ST           | CMOS           | General purpose I/O.                                          |

|                                                                                                                                    | MCLR     | TTL/ST           | _              | Master Clear with internal pull-up.                           |

|                                                                                                                                    | Vpp      | HV               |                | Programming voltage.                                          |

|                                                                                                                                    | SS       | TTL/ST           | _              | Slave Select input.                                           |

|                                                                                                                                    | CLCIN0   | TTL/ST           | _              | Configurable Logic Cell source input.                         |

| <b>TABLE 1-2:</b> | PIC16(L)F18313 PINOUT DESCRIPTION |

|-------------------|-----------------------------------|

|-------------------|-----------------------------------|

Legend: AN = Analog input or output TTL = TTL compatible input HV = High Voltage

CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

OD = Open-Drain

HV = High Voltage

XTAL = Crystal levels

I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 13-1.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-2.

**3:** These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

| Name                                                           | Function | Input<br>Type | Output<br>Type | Description                                                      |

|----------------------------------------------------------------|----------|---------------|----------------|------------------------------------------------------------------|

| RA0/ANA0/C1IN0+/                                               | RA0      | TTL/ST        | CMOS           | General purpose I/O.                                             |

| DAC1OUT/ICSPDAT/ICDDAT                                         | ANA0     | AN            | _              | ADC Channel A0 input.                                            |

|                                                                | C1IN0+   | AN            |                | Comparator C1 positive input.                                    |

|                                                                | DAC1OUT  | _             | AN             | Digital-to-Analog Converter output.                              |

|                                                                | ICSPDAT  | TTL/ST        | CMOS           | ICSP™ Data I/O.                                                  |

|                                                                | ICDDAT   | TTL/ST        | CMOS           | In-Circuit Debug Data I/O.                                       |

| RA1/ANA1/VREF+/C1IN0-/                                         | RA1      | TTL/ST        | CMOS           | General purpose I/O.                                             |

| C2IN0-/DAC1REF+/ICSPCLK/                                       | ANA1     | AN            | _              | ADC Channel A1 input.                                            |

| ICDCLK                                                         | VREF+    | AN            | _              | ADC Voltage Reference input.                                     |

|                                                                | C1IN0-   | AN            | _              | Comparator C1 negative input.                                    |

|                                                                | C2IN0-   | AN            |                | Comparator C2 negative input.                                    |

|                                                                | DAC1REF+ | AN            | _              | Digital-to-Analog Converter positive reference voltage input.    |

|                                                                | ICSPCLK  | TTL/ST        | CMOS           | Serial Programming Clock.                                        |

|                                                                | ICDCLK   | TTL/ST        | CMOS           | In-Circuit Debug Clock.                                          |

| RA2/ANA2/VREF-/DAC1REF-/                                       | RA2      | TTL/ST        | CMOS           | General purpose I/O.                                             |

| 0CKI <sup>(1)</sup> /CWG1IN <sup>(1)</sup> /INT <sup>(1)</sup> | ANA2     | AN            |                | ADC Channel A2 input.                                            |

|                                                                | VREF-    | AN            |                | ADC Negative Voltage Reference input.                            |

|                                                                | DAC1REF- | AN            |                | Digital-to-Analog Converter negative reference voltage<br>input. |

|                                                                | T0CKI    | TTL/ST        | _              | TMR0 clock input.                                                |

|                                                                | CWG1IN   | TTL/ST        |                | Complementary Waveform Generator input.                          |

|                                                                | INT      | TTL/ST        | _              | External interrupt.                                              |

| RA3/MCLR/Vpp                                                   | RA3      | TTL/ST        | CMOS           | General purpose I/O.                                             |

|                                                                | MCLR     | TTL/ST        |                | Master Clear with internal pull-up.                              |

|                                                                | Vpp      | HV            | _              | Programming voltage.                                             |

| RA4/ANA4/T1G <sup>(1)</sup> /SOSCO/                            | RA4      | TTL/ST        | CMOS           | General purpose I/O.                                             |

| OSC2/CLKOUT                                                    | ANA4     | AN            |                | ADC Channel A4 input.                                            |

|                                                                | T1G      | TTL/ST        | _              | TMR1 gate input.                                                 |

|                                                                | SOSCO    | —             | XTAL           | Secondary Oscillator Connection.                                 |

|                                                                | OSC2     | —             | XTAL           | Crystal/Resonator (LP, XT, HS modes).                            |

|                                                                | CLKOUT   | —             | CMOS           | Fosc/4 output.                                                   |

| RA5/ANA5/T1CKI <sup>(1)</sup> /CLCIN3 <sup>(1)</sup> /         | RA5      | TTL/ST        | CMOS           | General purpose I/O.                                             |

| SOSCI/SOSCIN/OSC1/CLKIN                                        | ANA5     | AN            |                | ADC Channel A5 input.                                            |

|                                                                | T1CKI    | TTL/ST        | _              | TMR1 clock input.                                                |

|                                                                | CLCIN3   | TTL/ST        | —              | Configurable Logic Cell source input.                            |

|                                                                | SOSCI    | XTAL          | _              | Secondary Oscillator Connection.                                 |

|                                                                | SOSCIN   | TTL/ST        | _              | Secondary Oscillator Input Connection.                           |

|                                                                | OSC1     | XTAL          | _              | Crystal/Resonator (LP, XT, HS modes).                            |

|                                                                | CLKIN    | TTL/ST        | _              | External clock input.                                            |

#### TABLE 1-3: PIC16(L)F18323 PINOUT DESCRIPTION

Legend:

AN = Analog input or output

CMOS = CMOS compatible input or output

OD = Open-Drain

TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage

XTAL = Crystal levels

XTAL = Crystal levels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 13-2.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-2.

**3:** These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

| Name               | Function           | Input<br>Type | Output<br>Type | Description                                           |

|--------------------|--------------------|---------------|----------------|-------------------------------------------------------|

| OUT <sup>(2)</sup> | C1OUT              | —             | CMOS           | Comparator output.                                    |

|                    | C2OUT              | —             | CMOS           | Comparator output.                                    |

|                    | CCP1               | —             | CMOS           | Capture/Compare/PWM1 output.                          |

|                    | CCP2               | —             | CMOS           | Capture/Compare/PWM2 output.                          |

|                    | PWM5               | _             | CMOS           | PWM5 output.                                          |

|                    | PWM6               | _             | CMOS           | PWM6 output.                                          |

|                    | CWG1A              | —             | CMOS           | Complementary Waveform Generator Output A.            |

|                    | CWG1B              | —             | CMOS           | Complementary Waveform Generator Output B.            |

|                    | CWG1C              | —             | CMOS           | Complementary Waveform Generator Output C.            |

|                    | CWG1D              | —             | CMOS           | Complementary Waveform Generator Output D.            |

|                    | SDA <sup>(3)</sup> | _             | OD             | I <sup>2</sup> C data input/output.                   |

|                    | SDO                | _             | CMOS           | SPI data output.                                      |

|                    | SCK                | —             | CMOS           | SPI clock output.                                     |

|                    | SCL <sup>(3)</sup> | _             | OD             | I <sup>2</sup> C clock output.                        |

|                    | TX/CK              | —             | CMOS           | EUSART asynchronous TX data/synchronous clock output. |

|                    | DT                 | _             | CMOS           | EUSART synchronous data output.                       |

|                    | CLC10UT            | —             | CMOS           | Configurable Logic Cell 1 source output.              |

|                    | CLC2OUT            |               | CMOS           | Configurable Logic Cell 2 source output.              |

|                    | NCO1               |               | CMOS           | Numerically controlled oscillator output.             |

|                    | DSM                |               | CMOS           | Data Signal Modulator output.                         |

|                    | TMR0               | —             | CMOS           | TMR0 clock output.                                    |

#### TABLE 1-3: PIC16(L)F18323 PINOUT DESCRIPTION (CONTINUED)

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible inputST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HV = High VoltageXTAL = Crystal levels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 13-2.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-2.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

# PIC16(L)F18313/18323

### 7.2.1.4 4x PLL

The oscillator module contains a PLL that can be used with external clock sources to provide a system clock source. The input frequency for the PLL must fall within specifications. See the PLL Clock Timing Specifications in Table 35-9.

The PLL may be enabled for use by one of two methods:

- 1. Program the RSTOSC bits in the Configuration Word 1 to enable the EXTOSC with 4x PLL.

- 2. Write the NOSC bits in the OSCCON1 register to enable the EXTOSC with 4x PLL.

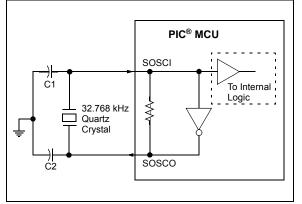

### 7.2.1.5 Secondary Oscillator

The secondary oscillator is a separate oscillator block that can be used as an alternate system clock source. The secondary oscillator is optimized for 32.768 kHz, and can be used with an external crystal oscillator connected to the SOSCI and SOSCO device pins, or an external clock source connected to the SOSCIN pin. The secondary oscillator can be selected during run-time using clock switching. Refer to **Section 7.3** "**Clock Switching**" for more information.

#### FIGURE 7-5: QUARTZ CRYSTAL OPERATION (SECONDARY OSCILLATOR)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices (DS00826)

- AN849, *Basic PIC*<sup>®</sup> Oscillator Design (DS00849)

- AN943, Practical PIC<sup>®</sup> Oscillator Analysis and Design (DS00943)

- AN949, *Making Your Oscillator Work* (DS00949)

- TB097, Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS (DS91097)

- AN1288, Design Practices for Low-Power External Oscillators (DS01288)

#### 11.4.7 NVMREG EEPROM, USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS

Instead of accessing Program Flash Memory, the EEPROM, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when NVMREGS = 1 in the NVMCON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 11-3.

When read access is initiated on an address outside the parameters listed in Table 11-3, the NVMDATH: NVMDATL register pair is cleared, reading back '0's.

# TABLE 11-3: EEPROM, USER ID, DEV/REV ID AND CONFIGURATION WORD ACCESS (NVMREGS = 1)

| Address     | Function                | Read Access | Write Access |

|-------------|-------------------------|-------------|--------------|

| 8000h-8003h | User IDs                | Yes         | Yes          |

| 8005h-8006h | Device ID/Revision ID   | Yes         | No           |

| 8007h-800Ah | Configuration Words 1-4 | Yes         | No           |

| F000h-F0FFh | EEPROM                  | Yes         | Yes          |

# 13.8 Register Definitions: PPS Input Selection

#### REGISTER 13-1: xxxPPS: PERIPHERAL xxx INPUT SELECTION

| U-0              | U-0                           | U-0                                              | R/W-q/u | U-0          | R/W-q/u          | R/W-q/u          | R/W-q/u      |  |  |  |  |

|------------------|-------------------------------|--------------------------------------------------|---------|--------------|------------------|------------------|--------------|--|--|--|--|

| _                | —                             | —                                                |         |              | xxxPPS<4:0>      |                  |              |  |  |  |  |

| bit 7            |                               |                                                  |         |              |                  |                  | bit 0        |  |  |  |  |

|                  |                               |                                                  |         |              |                  |                  |              |  |  |  |  |

| Legend:          |                               |                                                  |         |              |                  |                  |              |  |  |  |  |

| R = Readable     | bit                           | W = Writable                                     | bit     | U = Unimple  | mented bit, read | as '0'           |              |  |  |  |  |

| u = Bit is unch  | anged                         | x = Bit is unkr                                  | nown    | -n/n = Value | at POR and BO    | R/Value at all o | other Resets |  |  |  |  |

| '1' = Bit is set |                               | '0' = Bit is clea                                | ared    | q = value de | pends on periph  | eral             |              |  |  |  |  |

|                  | Unimplomen                    | ted. Dood oo '                                   | o'      |              |                  |                  |              |  |  |  |  |

| bit 7-5          | -                             | ted: Read as '                                   |         |              |                  |                  |              |  |  |  |  |

| bit 4-0          |                               | xxxPPS<4:0>: Peripheral xxx Input Selection bits |         |              |                  |                  |              |  |  |  |  |

|                  | 11xxx = Reserved. Do not use. |                                                  |         |              |                  |                  |              |  |  |  |  |

|                  | 1011x = Reserved. Do not use. |                                                  |         |              |                  |                  |              |  |  |  |  |

|                  |                               | pheral input is l                                |         |              |                  |                  |              |  |  |  |  |

|                  |                               | pheral input is                                  |         |              |                  |                  |              |  |  |  |  |

|                  |                               | pheral input is l                                |         |              |                  |                  |              |  |  |  |  |

|                  |                               | pheral input is  <br>pheral input is             |         |              |                  |                  |              |  |  |  |  |

|                  |                               | pheral input is                                  |         |              |                  |                  |              |  |  |  |  |

|                  |                               |                                                  |         |              |                  |                  |              |  |  |  |  |

|                  | 01xxx = Reserved. Do not use. |                                                  |         |              |                  |                  |              |  |  |  |  |

|                  | •••                           |                                                  |         |              |                  |                  |              |  |  |  |  |

|                  | 0011x = Reserved. Do not use. |                                                  |         |              |                  |                  |              |  |  |  |  |

|                  |                               | pheral input is                                  |         |              |                  |                  |              |  |  |  |  |

|                  |                               | pheral input is<br>pheral input is               |         |              |                  |                  |              |  |  |  |  |

|                  |                               | pheral input is l                                |         |              |                  |                  |              |  |  |  |  |

|                  |                               | pheral input is                                  |         |              |                  |                  |              |  |  |  |  |

|                  |                               | pheral input is                                  |         |              |                  |                  |              |  |  |  |  |

Note 1: PIC16(L)F18323 only.

| U-0             | U-0                | U-0                                                                      | R/W-0/u             | R/W-0/u        | R/W-0/u          | R/W-0/u          | R/W-0/u      |  |  |  |  |

|-----------------|--------------------|--------------------------------------------------------------------------|---------------------|----------------|------------------|------------------|--------------|--|--|--|--|

| _               |                    | _                                                                        |                     |                | RxyPPS<4:0>      |                  |              |  |  |  |  |

| bit 7           |                    |                                                                          |                     |                |                  |                  | bit          |  |  |  |  |

|                 |                    |                                                                          |                     |                |                  |                  |              |  |  |  |  |

| Legend:         |                    |                                                                          |                     |                |                  |                  |              |  |  |  |  |

| R = Readab      |                    | W = Writable                                                             | e bit               | U = Unimplen   | nented bit, read | l as '0'         |              |  |  |  |  |

| u = Bit is und  | changed            | x = Bit is un                                                            | known               | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |  |  |

| '1' = Bit is se | et                 | ʻ0' = Bit is cl                                                          | eared               |                |                  |                  |              |  |  |  |  |

| bit 7-5         | Unimplem           | ented: Read as                                                           | ʻ0'                 |                |                  |                  |              |  |  |  |  |

| bit 4-0         | -                  | : <b>0&gt;:</b> Pin Rxy Ou                                               |                     | election bits  |                  |                  |              |  |  |  |  |

|                 | •                  | xy source is DS                                                          | •                   |                |                  |                  |              |  |  |  |  |

|                 | 11110 <b>= R</b> : | xy source is CL                                                          | KR                  |                |                  |                  |              |  |  |  |  |

|                 |                    | xy source is NC                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 |                    | xy source is TM                                                          | R0                  |                |                  |                  |              |  |  |  |  |

|                 | 11011 <b>= R</b> e |                                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 | 11010 <b>= R</b>   |                                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 |                    | y source is SDO/SDA <sup>(1)</sup><br>y source is SCK/SCL <sup>(1)</sup> |                     |                |                  |                  |              |  |  |  |  |

|                 |                    | xy source is SC<br>xy source is C2                                       |                     |                |                  |                  |              |  |  |  |  |

|                 |                    | xy source is C2                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 |                    | xy source is DT                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 |                    | xy source is TX                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 |                    | 2                                                                        |                     |                |                  |                  |              |  |  |  |  |

|                 | 01101 <b>= R</b> : | xy source is CC                                                          | P2                  |                |                  |                  |              |  |  |  |  |

|                 | 01100 <b>= R</b> : | xy source is CC                                                          | P1                  |                |                  |                  |              |  |  |  |  |

|                 |                    | xy source is CW                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 |                    | xy source is CW                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 |                    | xy source is CW                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 | 01000 <b>= R</b> : | xy source is CW                                                          | /G1A <sup>(1)</sup> |                |                  |                  |              |  |  |  |  |

|                 | •••                |                                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 | 00111 <b>= R</b>   |                                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 | 00110 <b>=</b> R   |                                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 |                    | xy source is CL                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 |                    | xy source is CL                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 |                    | xy source is PW                                                          |                     |                |                  |                  |              |  |  |  |  |

|                 | 00010 = R          | xy source is PN                                                          | GINID               |                |                  |                  |              |  |  |  |  |

|                 | 00001 - R          |                                                                          |                     |                |                  |                  |              |  |  |  |  |

| Note 1: ⊺       |                    | overridden by th                                                         |                     |                |                  |                  |              |  |  |  |  |

## REGISTER 13-2: RxyPPS: PIN Rxy OUTPUT SOURCE SELECTION REGISTER

- **Note 1:** TRIS control is overridden by the peripheral as required.

- 2: PIC16(L)F18323 only.

| Name                  | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2       | Bit 1       | Bit 0    | Register<br>on Page |

|-----------------------|----------|----------|----------|----------|----------|-------------|-------------|----------|---------------------|

| ANSELA                | -        | -        | ANSA5    | ANSA4    | _        | ANSA2       | ANSA1       | ANSA0    | 133                 |

| TRISA                 | _        | _        | TRISA5   | TRISA4   | _(2)     | TRISA2      | TRISA1      | TRISA0   | 132                 |

| ANSELC <sup>(1)</sup> | _        | _        | ANSC5    | ANSC4    | ANSC3    | ANSC2       | ANSC1       | ANSC0    | 139                 |

| TRISC <sup>(1)</sup>  | -        | _        | TRISC5   | TRISC4   | TRISC3   | TRISC2      | TRISC1      | TRISC0   | 138                 |

| INTCON                | GIE      | PEIE     | _        | —        | -        | -           | _           | INTEDG   | 90                  |

| PIR3                  | OSFIF    | CSWIF    | —        | —        | —        | —           | CLC2IF      | CLC1IF   | 99                  |

| PIE3                  | OSFIE    | CSWIE    | —        | —        | —        | —           | CLC2IE      | CLC1IE   | 94                  |

| CLC1CON               | LC1EN    | —        | LC10UT   | LC1INTP  | LC1INTN  |             | LC1MODE<2:0 | >        | 203                 |

| CLC1POL               | LC1POL   | —        | —        | —        | LC1G4POL | LC1G3POL    | LC1G2POL    | LC1G1POL | 204                 |

| CLC1SEL0              | -        | —        | —        |          |          | LC1D1S<4:0  | >           |          | 205                 |

| CLC1SEL1              | -        | _        | _        |          |          | LC1D2S<4:0  | <b>,</b>    |          | 205                 |

| CLC1SEL2              | _        | —        | —        |          |          | LC1D3S<4:02 | >           |          | 205                 |

| CLC1SEL3              | -        | —        | —        |          |          | LC1D4S<4:0  | <b>`</b>    |          | 205                 |

| CLC1GLS0              | LC1G1D4T | LC1G1D4N | LC1G1D3T | LC1G1D3N | LC1G1D2T | LC1G1D2N    | LC1G1D1T    | LC1G1D1N | 206                 |

| CLC1GLS1              | LC1G2D4T | LC1G2D4N | LC1G2D3T | LC1G2D3N | LC1G2D2T | LC1G2D2N    | LC1G2D1T    | LC1G2D1N | 207                 |

| CLC1GLS2              | LC1G3D4T | LC1G3D4N | LC1G3D3T | LC1G3D3N | LC1G3D2T | LC1G3D2N    | LC1G3D1T    | LC1G3D1N | 208                 |

| CLC1GLS3              | LC1G4D4T | LC1G4D4N | LC1G4D3T | LC1G4D3N | LC1G4D2T | LC1G4D2N    | LC1G4D1T    | LC1G4D1N | 209                 |

| CLC2CON               | LC2EN    | —        | LC2OUT   | LC2INTP  | LC2INTN  |             | LC2MODE<2:0 | >        | 203                 |

| CLC2POL               | LC2POL   | —        | —        | —        | LC2G4POL | LC2G3POL    | LC2G2POL    | LC2G1POL | 204                 |

| CLC2SEL0              | -        | —        | —        |          |          | LC2D1S<4:0  | >           |          | 205                 |

| CLC2SEL1              | _        | —        | —        |          |          | LC2D2S<4:02 | >           |          | 205                 |

| CLC2SEL2              | _        | —        | —        |          |          | LC2D3S<4:02 | >           |          | 205                 |

| CLC2SEL3              | -        | —        | —        |          |          | LC2D4S<4:0  | <b>`</b>    |          | 205                 |

| CLC2GLS0              | LC2G1D4T | LC2G1D4N | LC2G1D3T | LC2G1D3N | LC2G1D2T | LC2G1D2N    | LC2G1D1T    | LC2G1D1N | 206                 |

| CLC2GLS1              | LC2G2D4T | LC2G2D4N | LC2G2D3T | LC2G2D3N | LC2G2D2T | LC2G2D2N    | LC2G2D1T    | LC2G2D1N | 207                 |

| CLC2GLS2              | LC2G3D4T | LC2G3D4N | LC2G3D3T | LC2G3D3N | LC2G3D2T | LC2G3D2N    | LC2G3D1T    | LC2G3D1N | 208                 |

| CLC2GLS3              | LC2G4D4T | LC2G4D4N | LC2G4D3T | LC2G4D3N | LC2G4D2T | LC2G4D2N    | LC2G4D1T    | LC2G4D1N | 209                 |

| CLCDAT                | -        | —        | —        | —        | —        | —           | MLC2OUT     | MLC1OUT  | 210                 |

| CLCIN0PPS             | -        | —        | —        |          | . (      | CLCIN0PPS<4 | 0>          |          | 143                 |

| CLCIN1PPS             | —        | —        | —        |          | (        | CLCIN1PPS<4 | 0>          |          | 143                 |

| CLCIN2PPS             | -        | _        | —        |          | (        | CLCIN2PPS<4 | 0>          |          | 143                 |

| CLCIN3PPS             | -        | _        | —        |          | (        | CLCIN3PPS<4 | 0>          |          | 143                 |

| CLC10UTPPS            | _        | —        | —        |          | С        | LC10UTPPS<  | 4:0>        |          | 143                 |

| CLC2OUTPPS            | _        | _        | _        |          | С        | LC2OUTPPS<  | 4:0>        |          | 143                 |

# TABLE 21-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx

Note 1: PIC16(L)F18323 only.

## 23.5 Interrupts

When the accumulator overflows (NCO\_overflow), the NCO1 Interrupt Flag bit, NCO1IF, of the PIR2 register is set. To enable the interrupt event (NCO\_interrupt), the following bits must be set:

- N1EN bit of the NCO1CON register

- NCO1IE bit of the PIE2 register

- · PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt must be cleared by software by clearing the NCO1IF bit in the Interrupt Service Routine.

# 23.6 Effects of a Reset

All of the NCO1 registers are cleared to zero as the result of a Reset.

### 23.7 Operation in Sleep

The NCO1 module operates independently from the system clock and will continue to run during Sleep, provided that the clock source selected remains active.

The HFINTOSC remains active during Sleep when the NCO1 module is enabled and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the NCO1 clock source, when the NCO1 is enabled, the CPU will go idle during Sleep, but the NCO1 will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current

#### 24.6 **Register Definitions: DAC Control**

#### **REGISTER 24-1:** DACCON0: VOLTAGE REFERENCE CONTROL REGISTER 0

|                         |                                                |                                                                             | -                |                 |                      | -                |          |

|-------------------------|------------------------------------------------|-----------------------------------------------------------------------------|------------------|-----------------|----------------------|------------------|----------|

| R/W-0/0                 | U-0                                            | R/W-0/0                                                                     | U-0              | R/W-0/0         | R/W-0/0              | U-0              | R/W-0/0  |

| DAC1EN                  | —                                              | DAC10E                                                                      | _                | DAC1F           | PSS<1:0>             | _                | DAC1NSS  |

| bit 7                   |                                                | •                                                                           |                  | •               |                      |                  | bit (    |

| Legend:                 |                                                |                                                                             |                  |                 |                      |                  |          |

| R = Readable            | bit                                            | W = Writable bi                                                             | t                | U = Unimpleme   | ented bit, read as ' | ʻ0'              |          |

| u = Bit is unch         | anged                                          | x = Bit is unkno                                                            | wn               | -n/n = Value at | POR and BOR/Va       | alue at all othe | r Resets |

| '1' = Bit is set        |                                                | '0' = Bit is clear                                                          | ed               |                 |                      |                  |          |

| bit 7<br>bit 6<br>bit 5 | 1 = DAC volta                                  | abled<br>sabled<br>ed: Read as '0'<br>C1 Voltage Outpu<br>ge level is outpu | t on the DAC1C   | •               |                      |                  |          |

| bit 4                   | Unimplemente                                   | ge level is discor                                                          | inected from the | e DACTOUT pin   |                      |                  |          |

| bit 3-2                 | •                                              | >: DAC1 Positive<br>d, do not use<br>put                                    | e Source Select  | bits            |                      |                  |          |

| bit 1                   | Unimplemente                                   | ed: Read as '0'                                                             |                  |                 |                      |                  |          |

| bit 0                   | <b>DAC1NSS:</b> DA<br>1 = VREF- pin<br>0 = VSS | C1 Negative Sou                                                             | urce Select bits |                 |                      |                  |          |

|                         |                                                |                                                                             |                  |                 |                      |                  |          |

### **REGISTER 24-2: DACCON1: VOLTAGE REFERENCE CONTROL REGISTER 1**

| U-0                               | U-0 | U-0               | R/W-0/0    | R/W-0/0                                               | R/W-0/0            | R/W-0/0 | R/W-0/0 |  |  |  |

|-----------------------------------|-----|-------------------|------------|-------------------------------------------------------|--------------------|---------|---------|--|--|--|

| —                                 | —   | —                 | DAC1R<4:0> |                                                       |                    |         |         |  |  |  |

| bit 7                             |     |                   |            |                                                       |                    |         |         |  |  |  |

|                                   |     |                   |            |                                                       |                    |         |         |  |  |  |

| Legend:                           |     |                   |            |                                                       |                    |         |         |  |  |  |

| R = Readable bit W = Writable bit |     |                   |            | U = Unimpleme                                         | ented bit, read as | '0'     |         |  |  |  |

| u = Bit is unchan                 | ged | x = Bit is unknow | n          | -n/n = Value at POR and BOR/Value at all other Resets |                    |         |         |  |  |  |

bit 7-5 Unimplemented: Read as '0'

'1' = Bit is set

bit 4-0 DAC1R<4:0>: DAC1 Voltage Output Select bits VOUT = (VSRC+ - VSRC-)\*(DAC1R<4:0>/32) + VSRC

'0' = Bit is cleared

#### **TABLE 24-1:** SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC1 MODULE

| Name    | Bit 7       | Bit 6         | Bit 5       | Bit 4                    | Bit 3        | Bit 2          | Bit 1        | Bit 0   | Register<br>on page |

|---------|-------------|---------------|-------------|--------------------------|--------------|----------------|--------------|---------|---------------------|

| DACCON0 | DAC1EN      |               | DAC10E      | - DAC1PSS<1:0> - DAC1NSS |              |                |              | DAC1NSS | 239                 |

| DACCON1 | _           | _             | —           |                          |              | DAC1R<4        | 4:0>         |         | 239                 |

| CMxCON1 | CxINTP      | CxINTN        | (           | CxPCH<2:0> CxNCH<2:0>    |              |                |              |         | 167                 |

| ADCON0  |             |               | CHS<        | CHS<5:0> GO/DONE ADON    |              |                |              |         | 220                 |

| Lonondi | - Unimpland | optod looptio | n read as ' | ) Cheded                 | alla ara nat | upped with the | o DAC modulo |         |                     |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

| U-0                               | R/W-x/u                  | R/W-x/u               | U-0          | R/W-x/u            | R/W-x/u           | R/W-x/u              | R/W-x/u          |

|-----------------------------------|--------------------------|-----------------------|--------------|--------------------|-------------------|----------------------|------------------|

|                                   | MDCLPOL                  | MDCLSYNC              | _            |                    | MDCL<             | <3:0> <sup>(1)</sup> |                  |

| oit 7                             |                          |                       |              |                    |                   |                      | bit 0            |

|                                   |                          |                       |              |                    |                   |                      |                  |

| L <b>egend:</b><br>R = Readable I | nit                      | W = Writable bi       | +            | II – Unimplem      | nented bit, read  | l ac 'O'             |                  |

| u = Bit is uncha                  |                          | x = Bit is unkno      | -            | •                  | it POR and BO     |                      | thar Pacata      |

| 1' = Bit is set                   | angeu                    | '0' = Bit is clean    |              |                    |                   |                      |                  |

| I – DILIS SEL                     |                          |                       | eu           |                    |                   |                      |                  |

| oit 7                             | Unimplemen               | nted: Read as '0'     |              |                    |                   |                      |                  |

| oit 6                             | MDCLPOL:                 | Modulator Low Ca      | arrier Polar | ity Select bit     |                   |                      |                  |

|                                   | 1 = Selected             | l low carrier signa   | l is inverte | d                  |                   |                      |                  |

|                                   | 0 = Selected             | l low carrier signa   | I is not inv | erted              |                   |                      |                  |

| oit 5                             | MDCLSYNC                 | : Modulator Low       | Carrier Syr  | hchronization En   | able bit          |                      |                  |

|                                   | 1 = Modulate             | or waits for a fallin | g edge on    | the low time carr  | ier signal before | e allowing a sw      | itch to the high |

|                                   | time carr                |                       |              |                    |                   | 1)                   |                  |

|                                   |                          | or Output is not s    | ynchronize   | d to the low time  | carrier signal    | ")                   |                  |

| oit 4                             | -                        | nted: Read as '0'     |              |                    |                   |                      |                  |

| oit 3-0                           | MDCL<3:0>                | Modulator Data H      | ligh Carrie  | r Selection bits ( | 1)                |                      |                  |

|                                   |                          | erved. No channe      |              |                    |                   |                      |                  |

|                                   |                          | erved. No chann       | el connecte  | ed.                |                   |                      |                  |

|                                   | 1101 = CLC               |                       |              |                    |                   |                      |                  |

|                                   | 1100 = CLC<br>1011 = HFI |                       |              |                    |                   |                      |                  |

|                                   | 1010 = Fos               |                       |              |                    |                   |                      |                  |

|                                   |                          | erved. No chann       | el connecte  | ed.                |                   |                      |                  |

|                                   | 1000 = NCC               | D1 output             |              |                    |                   |                      |                  |

|                                   | 0111 = PWI               | •                     |              |                    |                   |                      |                  |

|                                   | 0110 = PWI               |                       | _            |                    |                   |                      |                  |

|                                   |                          | P2 output (PWM (      |              |                    |                   |                      |                  |

|                                   |                          | P1 output (PWM (      | •            | • ·                |                   |                      |                  |

|                                   | 0011 = Refe0010 = MD0    | erence clock mod      | ule signal   | (ULKK)             |                   |                      |                  |

|                                   |                          |                       |              |                    |                   |                      |                  |

|                                   | 0001 = MD0               | CIN1PPS               |              |                    |                   |                      |                  |

# REGISTER 25-4: MDCARL: MODULATION LOW CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

| Name                  | Bit 7   | Bit 6   | Bit 5   | Bit 4                 | Bit 3                   | Bit 2        | Bit 1    | Bit 0  | Register on<br>Page |  |

|-----------------------|---------|---------|---------|-----------------------|-------------------------|--------------|----------|--------|---------------------|--|

| TRISA                 | _       | —       | TRISA5  | TRISA4                | _(2)                    | TRISA2       | TRISA1   | TRISA0 | 132                 |  |

| ANSELA                | _       | _       | ANSA5   | ANSA4                 | _                       | ANSA2        | ANSA1    | ANSA0  | 133                 |  |

| TRISC <sup>(1)</sup>  | -       | —       | TRISC5  | TRISC4                | TRISC3                  | TRISC2       | TRISC1   | TRISC0 | 138                 |  |

| ANSELC <sup>(1)</sup> | _       | _       | ANSC5   | ANSC4                 | ANSC3                   | ANSC2        | ANSC1    | ANSC0  | 139                 |  |

| INTCON                | GIE     | PEIE    | _       | _                     | _                       | —            | _        | INTEDG | 90                  |  |

| PIR1                  | TMR1GIF | ADIF    | RCIF    | TXIF                  | SSP1IF                  | BCL1IF       | TMR2IF   | TMR1IF | 97                  |  |

| PIE1                  | TMR1GIE | ADIE    | RCIE    | TXIE                  | SSP1IE                  | BCL1IE       | TMR2IE   | TMR1IE | 92                  |  |

| T1CON                 | TMR1C   | CS<1:0> | T1CKP   | S<1:0>                | T1SOSC                  | T1SYNC       | —        | TMR10N | 266                 |  |

| T1GCON                | TMR1GE  | T1GPOL  | T1GTM   | T1GSPM                | T <u>1GGO</u> /<br>DONE | T1GVAL       | T1GS     | S<1:0> | 267                 |  |

| TMR1L                 |         |         | 1       | TMR1                  | L<7:0>                  |              |          |        | 268                 |  |

| TMR1H                 |         |         |         | TMR1                  | H<7:0>                  |              |          |        | 268                 |  |

| T1CKIPPS              | —       | —       | —       |                       |                         | T1CKIPPS<4:0 | )>       |        | 143                 |  |

| T1GPPS                | —       | —       | —       |                       |                         | T1GPPS<4:0>  | <b>`</b> |        | 143                 |  |

| T0CON0                | T0EN    | —       | TOOUT   | T016BIT               |                         | TOOUT        | PS<3:0>  |        | 255                 |  |

| CMxCON0               | CxON    | CxOUT   | —       | CxPOL                 | _                       | CxSP         | CxHYS    | CxSYNC | 281                 |  |

| CCPTMRS               | —       | —       | —       | —                     | _                       | C2TSEL       | —        | C1TSEL | 283                 |  |

| CCPxCON               | CCPxEN  | —       | CCPxOUT | CCPxFMT CCPxMODE<3:0> |                         |              |          |        |                     |  |

| CLCxSELy              | -       | —       | —       |                       | -                       | LCxDyS<4:0>  |          |        | 205                 |  |

| ADACT                 | —       | —       | —       | —                     | — ADACT<3:0>            |              |          |        |                     |  |

## TABLE 27-5: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by Timer1 module.

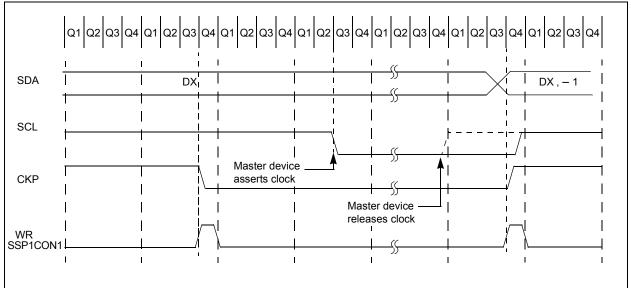

#### 30.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low, effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSP1CON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

#### 30.5.6.1 Normal Clock Stretching

Following an ACK if the R/W bit of SSP1STAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSP1BUF with data to transfer to the master. If the SEN bit of SSP1CON2 is set, the slave hardware will always stretch the clock after the ACK sequence. Once the slave is ready; CKP is set by software and communication resumes.

#### 30.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSP1ADD.

**Note:** Previous versions of the module did not stretch the clock if the second address byte did not match.

#### 30.5.6.3 Byte NACKing

When AHEN bit of SSP1CON3 is set; CKP is cleared by hardware after the eighth falling edge of SCL for a received matching address byte. When DHEN bit of SSP1CON3 is set; CKP is cleared after the eighth falling edge of SCL for received data.

Stretching after the eighth falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

# 30.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 30-23).

### FIGURE 30-23: CLOCK SYNCHRONIZATION TIMING

# 30.8 Register Definitions: MSSP Control

# REGISTER 30-1: SSP1STAT: SSP STATUS REGISTER

| R/W-0/0           | R/W-0/0                                                                                                                                                                   | R/HS/HC-0/0                                                                                                                                       | R/HS/HC-0/0                                | R/HS/HC-0/0                                   | R/HS/HC-0/0              | R/HS/HC-0/0         | R/HS/HC-0/0         |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------|--------------------------|---------------------|---------------------|

| SMP               | CKE <sup>(1)</sup>                                                                                                                                                        | D/A                                                                                                                                               | P <sup>(2)</sup>                           | S <sup>(2)</sup>                              | R/W                      | UA                  | BF                  |

| bit 7             |                                                                                                                                                                           |                                                                                                                                                   |                                            |                                               |                          |                     | bit C               |

|                   |                                                                                                                                                                           |                                                                                                                                                   |                                            |                                               |                          |                     |                     |

| Legend:           |                                                                                                                                                                           |                                                                                                                                                   |                                            |                                               |                          |                     |                     |

| R = Readable bit  | t                                                                                                                                                                         | W = Writable bit                                                                                                                                  |                                            | U = Unimplemen                                | ted bit, read as '0'     |                     |                     |

| u = Bit is unchan | nged                                                                                                                                                                      | x = Bit is unknow                                                                                                                                 | n                                          | -n/n = Value at P                             | OR and BOR/Value         | at all other Resets |                     |

| '1' = Bit is set  |                                                                                                                                                                           | '0' = Bit is cleared                                                                                                                              |                                            | HS/HC = Hardwa                                | are set/clear            |                     |                     |

| bit 7             | 0 = Input data sa<br>SPI Slave mode<br>SMP must be clo                                                                                                                    | e:<br>ampled at end of dat<br>ampled at middle of                                                                                                 | data output time<br>sed in Slave mode      |                                               |                          |                     |                     |

|                   |                                                                                                                                                                           | ontrol disabled for Si<br>ontrol enabled for Hi                                                                                                   |                                            |                                               | I MHZ)                   |                     |                     |

| bit 6             | In SPI Master or<br>1 = Transmit occ<br>0 = Transmit occ<br>In I <sup>2</sup> C mode only<br>1 = Enable input                                                             | Edge Select bit (SP<br>Slave mode:<br>curs on transition fro<br>curs on transition fro<br><u>c</u><br>togic so that thresh<br>Bus specific inputs | m active to Idle cl<br>m Idle to active cl | ock state                                     | ification                |                     |                     |

| bit 5             | <ol> <li>1 = Indicates that</li> </ol>                                                                                                                                    | ess bit (I <sup>2</sup> C mode on<br>at the last byte receiv<br>at the last byte receiv                                                           | ed or transmitted                          |                                               |                          |                     |                     |

| bit 4             | 1 = Indicates that                                                                                                                                                        | This bit is cleared w<br>at a Stop bit has bee<br>not detected last                                                                               |                                            |                                               |                          |                     |                     |

| bit 3             | <ol> <li>I = Indicates that</li> </ol>                                                                                                                                    | This bit is cleared w<br>at a Start bit has bee<br>not detected last                                                                              | hen the MSSP mo<br>n detected last (th     | odule is disabled, S<br>his bit is '0' on Res | SPEN is cleared.)<br>et) |                     |                     |

| bit 2             | This bit holds the<br>bit, Stop bit, or n<br>In I <sup>2</sup> C Slave mor<br>1 = Read<br>0 = Write<br>In I <sup>2</sup> C Master m<br>1 = Transmit is<br>0 = Transmit is | <u>de:</u><br>ode:<br>s in progress                                                                                                               | following the last                         |                                               | ·                        |                     | ch to the next Star |

| bit 1             | 1 = Indicates that                                                                                                                                                        | Iress bit (10-bit $I^2C$ r<br>at the user needs to<br>as not need to be up                                                                        | update the addres                          | ss in the SSP1ADE                             | ) register               |                     |                     |

| bit 0             | 0 = Receive not<br><u>Transmit (I<sup>2</sup>C me</u><br>1 = Data transm                                                                                                  | <u>d I<sup>2</sup>C modes):</u><br>nplete, SSP1BUF is<br>complete, SSP1BUI                                                                        | F is empty<br>not include th <u>e AC</u>   |                                               |                          |                     |                     |

|                   | plarity of clock state in<br>is bit is cleared on R                                                                                                                       |                                                                                                                                                   |                                            | register.                                     |                          |                     |                     |

#### REGISTER 30-2: SSP1CON1: SSP CONTROL REGISTER 1