Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 10x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-TQFP                                                                    |

| Supplier Device Package    | 32-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20e15a-ant |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Writing a one to this bit will clear the corresponding INTFLAGC interrupt flag.

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAGC<br>0x1C [ID-00000<br>0x000000<br> | )a18]   |         |         |         |         |       |

|--------|-----------------------------------------|--------------------------------------------|---------|---------|---------|---------|---------|-------|

| Bit    | 31                                      | 30                                         | 29      | 28      | 27      | 26      | 25      | 24    |

|        |                                         |                                            |         |         |         |         |         |       |

| Access |                                         |                                            | ·       |         |         |         |         |       |

| Reset  |                                         |                                            |         |         |         |         |         |       |

| Bit    | 23                                      | 22                                         | 21      | 20      | 19      | 18      | 17      | 16    |

|        | CCL                                     | PTC                                        | DAC     | AC      | SDADC   | ADC1    | ADC0    | TC4   |

| Access | R/W                                     | R/W                                        | R/W     | R/W     | R/W     | R/W     | R/W     | R/W   |

| Reset  | 0                                       | 0                                          | 0       | 0       | 0       | 0       | 0       | 0     |

|        |                                         |                                            |         |         |         |         |         |       |

| Bit    | 15                                      | 14                                         | 13      | 12      | 11      | 10      | 9       | 8     |

|        | TC3                                     | TC2                                        | TC1     | TC0     | TCC2    | TCC1    | TCC0    |       |

| Access | R/W                                     | R/W                                        | R/W     | R/W     | R/W     | R/W     | R/W     |       |

| Reset  | 0                                       | 0                                          | 0       | 0       | 0       | 0       | 0       |       |

|        |                                         |                                            |         |         |         |         |         |       |

| Bit    | 7                                       | 6                                          | 5       | 4       | 3       | 2       | 1       | 0     |

|        | CAN0                                    | SERCOM5                                    | SERCOM4 | SERCOM3 | SERCOM2 | SERCOM1 | SERCOM0 | EVSYS |

| Access | R/W                                     | R/W                                        | R/W     | R/W     | R/W     | R/W     | R/W     | R/W   |

| Reset  | 0                                       | 0                                          | 0       | 0       | 0       | 0       | 0       | 0     |

## Bit 23 – CCL: Interrupt Flag for CCL

Bit 22 – PTC: Interrupt Flag for PTC

- Bit 21 DAC: Interrupt Flag for DAC

- Bit 20 AC: Interrupt Flag for AC

- Bit 19 SDADC: Interrupt Flag for SDADC

- Bits 17, 18 ADC: Interrupt Flag for ADCn [n=1..0]

- Bits 12, 13, 14, 15, 16 TC: Interrupt Flag for TCn [n = 4..0]

- Bits 9, 10, 11 TCC: Interrupt Flag for TCCn [n = 2..0]

- Bit 7 CAN: Interrupt Flag for CAN

- Bits 1, 2, 3, 4, 5, 6 SERCOM: Interrupt Flag for SERCOMn [n = 5..0]

- Bit 0 EVSYS: Interrupt Flag for EVSYS

- 11.7.9 Peripheral Interrupt Flag Status and Clear D

| Bit    | 31 | 30 | 29 | 28   | 27     | 26 | 25 | 24 |

|--------|----|----|----|------|--------|----|----|----|

| DIL    | 31 |    | 29 |      |        | 20 | 25 |    |

|        |    |    |    | END[ | 31:24] |    |    |    |

| Access | R  | R  | R  | R    | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0    | 0      | 0  | 0  | 0  |

|        |    |    |    |      |        |    |    |    |

| Bit    | 23 | 22 | 21 | 20   | 19     | 18 | 17 | 16 |

|        |    |    |    | END[ | 23:16] |    |    |    |

| Access | R  | R  | R  | R    | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0    | 0      | 0  | 0  | 0  |

|        |    |    |    |      |        |    |    |    |

| Bit    | 15 | 14 | 13 | 12   | 11     | 10 | 9  | 8  |

|        |    |    |    | END  | [15:8] |    |    |    |

| Access | R  | R  | R  | R    | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0    | 0      | 0  | 0  | 0  |

|        |    |    |    |      |        |    |    |    |

| Bit    | 7  | 6  | 5  | 4    | 3      | 2  | 1  | 0  |

|        |    |    |    | END  | [7:0]  |    |    |    |

| Access | R  | R  | R  | R    | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0    | 0      | 0  | 0  | 0  |

|        |    |    |    |      |        |    |    |    |

# Bits 31:0 – END[31:0]: End Marker

Indicates the end of the CoreSight ROM table entries.

# 13.13.13 CoreSight ROM Table Memory Type

| Name:       | MEMTYPE    |  |  |  |

|-------------|------------|--|--|--|

| Offset:     | 0x1FCC     |  |  |  |

| Reset:      | 0x0000000x |  |  |  |

| Property: - |            |  |  |  |

## 16.6.5.2 Minimize Power Consumption in Standby

The following table identifies when a Clock Generator is off in Standby Mode, minimizing the power consumption:

| Request for Clock n present | GENCTRLn.RUNSTDB<br>Y | GENCTRLn.OE | Clock Generator n |

|-----------------------------|-----------------------|-------------|-------------------|

| yes                         | -                     | -           | active            |

| no                          | 1                     | 1           | active            |

| no                          | 1                     | 0           | OFF               |

| no                          | 0                     | 1           | OFF               |

| no                          | 0                     | 0           | OFF               |

## Table 16-2. Clock Generator n Activity in Standby Mode

## 16.6.5.3 Entering Standby Mode

There may occur a delay when the device is put into Standby, until the power is turned off. This delay is caused by running Clock Generators: if the Run in Standby bit in the Generator Control register (GENCTRLn.RUNSTDBY) is '0', GCLK must verify that the clock is turned of properly. The duration of this verification is frequency-dependent.

## **Related Links**

PM – Power Manager

## 16.6.6 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

An exception is the Channel Enable bit in the Peripheral Channel Control registers (PCHCTRLm.CHEN). When changing this bit, the bit value must be read-back to ensure the synchronization is complete and to assert glitch free internal operation. Note that changing the bit value under ongoing synchronization will *not* generate an error.

The following registers are synchronized when written:

- Generic Clock Generator Control register (GENCTRLn)

- Control A register (CTRLA)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

#### **Related Links**

CTRLA

**Register Synchronization**

PCHCTRL0, PCHCTRL1, PCHCTRL2, PCHCTRL3, PCHCTRL4, PCHCTRL5, PCHCTRL6, PCHCTRL7, PCHCTRL8, PCHCTRL9, PCHCTRL10, PCHCTRL11, PCHCTRL12, PCHCTRL13, PCHCTRL14, PCHCTRL15, PCHCTRL16, PCHCTRL17, PCHCTRL18, PCHCTRL19, PCHCTRL20, PCHCTRL21, PCHCTRL22, PCHCTRL23, PCHCTRL24, PCHCTRL25, PCHCTRL26, PCHCTRL27, PCHCTRL28, PCHCTRL29, PCHCTRL30, PCHCTRL31, PCHCTRL32, PCHCTRL33, PCHCTRL34, PCHCTRL35, PCHCTRL36, PCHCTRL37, PCHCTRL38, PCHCTRL39, PCHCTRL40, PCHCTRL41, PCHCTRL42, PCHCTRL43, PCHCTRL44, PCHCTRL45

| Value     | Name     | Description              |

|-----------|----------|--------------------------|

| 0x06      | OSC48M   | OSC48M oscillator output |

| 0x07      | DPLL96M  | DPLL96M output           |

| 0x08-0x1F | Reserved | Reserved for future use  |

A Power Reset will reset all GENCTRLn registers. the Reset values of the GENCTRLn registers are shown in table below.

#### Table 16-5. GENCTRLn Reset Value after a Power Reset

| GCLK Generator | Reset Value after a Power Reset |

|----------------|---------------------------------|

| 0              | 0x0000106                       |

| others         | 0x0000000                       |

A User Reset will reset the associated GENCTRL register unless the Generator is the source of a locked Peripheral Channel (PCHCTRLm.WRTLOCK=1). The reset values of the GENCTRL register are as shown in the table below.

#### Table 16-6. GENCTRLn Reset Value after a User Reset

| GCLK Generator | Reset Value after a User Reset                                                                       |

|----------------|------------------------------------------------------------------------------------------------------|

| 0              | 0x0000106                                                                                            |

| others         | No change if the generator is used by a Peripheral Channel m with PCHCTRLm.WRTLOCK=1 else 0x00000000 |

#### Related Links

PCHCTRL0, PCHCTRL1, PCHCTRL2, PCHCTRL3, PCHCTRL4, PCHCTRL5, PCHCTRL6, PCHCTRL7, PCHCTRL8, PCHCTRL9, PCHCTRL10, PCHCTRL11, PCHCTRL12, PCHCTRL13, PCHCTRL14, PCHCTRL15, PCHCTRL16, PCHCTRL17, PCHCTRL18, PCHCTRL19, PCHCTRL20, PCHCTRL21, PCHCTRL22, PCHCTRL23, PCHCTRL24, PCHCTRL25, PCHCTRL26, PCHCTRL27, PCHCTRL28, PCHCTRL29, PCHCTRL30, PCHCTRL31, PCHCTRL32, PCHCTRL33, PCHCTRL34, PCHCTRL35, PCHCTRL36, PCHCTRL37, PCHCTRL38, PCHCTRL39, PCHCTRL40, PCHCTRL41, PCHCTRL42, PCHCTRL43, PCHCTRL44, PCHCTRL45

#### 16.8.4 Peripheral Channel Control

PCHTRLm controls the settings of Peripheral Channel number m (m=0..45).

Name: PCHCTRL0, PCHCTRL1, PCHCTRL2, PCHCTRL3, PCHCTRL4, PCHCTRL5, PCHCTRL6, PCHCTRL7, PCHCTRL8, PCHCTRL9, PCHCTRL10, PCHCTRL11, PCHCTRL12, PCHCTRL13, PCHCTRL14, PCHCTRL15, PCHCTRL16, PCHCTRL17, PCHCTRL18, PCHCTRL19, PCHCTRL20, PCHCTRL21, PCHCTRL22, PCHCTRL23, PCHCTRL24, PCHCTRL25, PCHCTRL26, PCHCTRL27, PCHCTRL28, PCHCTRL29, PCHCTRL30, PCHCTRL31, PCHCTRL32, PCHCTRL33, PCHCTRL34, PCHCTRL35, PCHCTRL36,

| index(m) | Name              | Description  |

|----------|-------------------|--------------|

| 41       | GCLK_SERCOM6_CORE | SERCOM6_CORE |

| 42       | GCLK_SERCOM7_CORE | SERCOM7_CORE |

| 43       | GCLK_TC5          | TC5          |

| 44       | GCLK_TC6          | TC6          |

| 45       | GCLK_TC7          | TC7          |

| Bit    | 15  | 14  | 13  | 12   | 11      | 10  | 9   | 8   |

|--------|-----|-----|-----|------|---------|-----|-----|-----|

| ĺ      |     |     |     | COMF | P[15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |     |     |     |      |         |     |     |     |

| Bit    | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   |

|        |     |     |     | COM  | P[7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

# Bits 15:0 - COMP[15:0]: Compare Value

The 16-bit value of COMPn is continuously compared with the 16-bit COUNT value. When a match occurs, the Compare n interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.CMPn) is set on the next counter cycle.

descriptor. The benefit of having descriptor memory and write-back memory in the same section is that it requires less SRAM. In addition, the latency from fetching the first descriptor of a transaction to the first burst transfer is executed, is reduced.

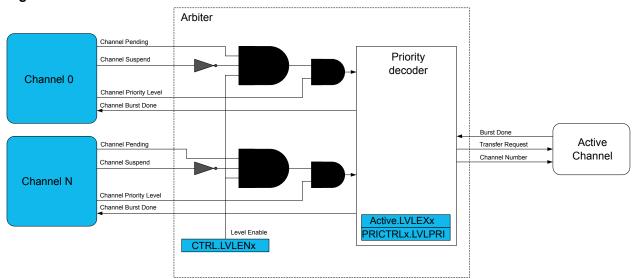

#### 25.6.2.4 Arbitration

If a DMA channel is enabled and not suspended when it receives a transfer trigger, it will send a transfer request to the arbiter. When the arbiter receives the transfer request it will include the DMA channel in the queue of channels having pending transfers, and the corresponding Pending Channel x bit in the Pending Channels registers (PENDCH.PENDCHx) will be set. Depending on the arbitration scheme, the arbiter will choose which DMA channel will be the next active channel. The active channel is the DMA channel being granted access to perform its next burst transfer. When the arbiter has granted a DMA channel access to the DMAC, the corresponding bit PENDCH.PENDCHx will be cleared. See also the following figure.

If the upcoming burst transfer is the first for the transfer request, the corresponding Busy Channel x bit in the Busy Channels register will be set (BUSYCH.BUSYCHx=1), and it will remain '1' for the subsequent granted burst transfers.

When the channel has performed its granted burst transfer(s) it will be either fed into the queue of channels with pending transfers, set to be waiting for a new transfer trigger, suspended, or disabled. This depends on the channel and block transfer configuration. If the DMA channel is fed into the queue of channels with pending transfers, the corresponding BUSYCH.BUSYCHx will remain '1'. If the DMA channel is set to wait for a new transfer trigger, suspended, or disabled, the corresponding BUSYCH.BUSYCHx will be cleared.

If a DMA channel is suspended while it has a pending transfer, it will be removed from the queue of pending channels, but the corresponding PENDCH.PENDCHx will remain set. When the same DMA channel is resumed, it will be added to the queue of pending channels again.

If a DMA channel gets disabled (CHCTRLA.ENABLE=0) while it has a pending transfer, it will be removed from the queue of pending channels, and the corresponding PENDCH.PENDCHx will be cleared.

# **Priority Levels**

When a channel level is pending or the channel is transferring data, the corresponding Level Executing bit is set in the Active Channel and Levels register (ACTIVE.LVLEXx).

Writing a '1' to this bit will set the Channel Transfer Error Interrupt Enable bit, which enables the Channel Transfer Error interrupt.

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | The Channel Transfer Error interrupt is disabled. |

| 1     | The Channel Transfer Error interrupt is enabled.  |

## 25.8.22 Channel Interrupt Flag Status and Clear

This register affects the DMA channel that is selected in the Channel ID register (CHID.ID).

| Name:     | CHINTFLAG          |

|-----------|--------------------|

| Offset:   | 0x4E [ID-00001ece] |

| Reset:    | 0x00               |

| Property: | -                  |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2    | 1     | 0    |

|--------|---|---|---|---|---|------|-------|------|

|        |   |   |   |   |   | SUSP | TCMPL | TERR |

| Access |   |   |   |   |   | R/W  | R/W   | R/W  |

| Reset  |   |   |   |   |   | 0    | 0     | 0    |

## Bit 2 – SUSP: Channel Suspend

This flag is cleared by writing a '1' to it.

This flag is set when a block transfer with suspend block action is completed, when a software suspend command is executed, when a suspend event is received or when an invalid descriptor is fetched by the DMA.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Channel Suspend interrupt flag for the corresponding channel.

For details on available software commands, refer to CHCTRLB.CMD.

For details on available event input actions, refer to CHCTRLB.EVACT.

For details on available block actions, refer to BTCTRL.BLOCKACT.

## Bit 1 – TCMPL: Channel Transfer Complete

This flag is cleared by writing a '1' to it.

This flag is set when a block transfer is completed and the corresponding interrupt block action is enabled.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Transfer Complete interrupt flag for the corresponding channel.

## Bit 0 – TERR: Channel Transfer Error

This flag is cleared by writing a '1' to it.

This flag is set when a bus error is detected during a beat transfer or when the DMAC fetches an invalid descriptor.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Transfer Error interrupt flag for the corresponding channel.

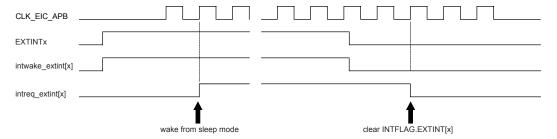

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the EIC is reset. See the INTFLAG register for details on how to clear interrupt flags. The EIC has one common interrupt request line for all the interrupt sources, and one interrupt request line for the NMI. The user must read the INTFLAG (or NMIFLAG) register to determine which interrupt condition is present.

Note: Interrupts must be globally enabled for interrupt requests to be generated.

**Note:** If an external interrupts (EXTINT) is common on two or more I/O pins, only one will be active (the first one programmed).

#### **Related Links**

Processor and Architecture

## 26.6.7 Events

The EIC can generate the following output events:

• External event from pin (EXTINTx).

Setting an Event Output Control register (EVCTRL.EXTINTEO) enables the corresponding output event. Clearing this bit disables the corresponding output event. Refer to *Event System* for details on configuring the Event System.

When the condition on pin EXTINTx matches the configuration in the CONFIGn register, the corresponding event is generated, if enabled.

#### **Related Links**

EVSYS – Event System

#### 26.6.8 Sleep Mode Operation

In sleep modes, an EXTINTx pin can wake up the device if the corresponding condition matches the configuration in CONFIG0, CONFIG1, CONFIG2, CONFIG3 register, and the corresponding bit in the Interrupt Enable Set register (INTENSET) is written to '1'.

## Figure 26-5. Wake-up Operation Example (High-Level Detection, No Filter, Interrupt Enable Set)

#### 26.6.9 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in control register (CTRLA.SWRST)

- Enable bit in control register (CTRLA.ENABLE)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

| Bit    | 31    | 30       | 29 | 28     | 27       | 26     | 25     | 24     |

|--------|-------|----------|----|--------|----------|--------|--------|--------|

|        | HWSEL | WRPINCFG |    | WRPMUX |          | PMU    | ([3:0] |        |

| Access | W     | W        |    | W      | W        | W      | W      | W      |

| Reset  | 0     | 0        |    | 0      | 0        | 0      | 0      | 0      |

|        |       |          |    |        |          |        |        |        |

| Bit    | 23    | 22       | 21 | 20     | 19       | 18     | 17     | 16     |

|        |       | DRVSTR   |    |        |          | PULLEN | INEN   | PMUXEN |

| Access |       | W        |    |        |          | W      | W      | W      |

| Reset  |       | 0        |    |        |          | 0      | 0      | 0      |

|        |       |          |    |        |          |        |        |        |

| Bit    | 15    | 14       | 13 | 12     | 11       | 10     | 9      | 8      |

|        |       |          |    | PINMAS | SK[15:8] |        |        |        |

| Access | W     | W        | W  | W      | W        | W      | W      | W      |

| Reset  | 0     | 0        | 0  | 0      | 0        | 0      | 0      | 0      |

|        |       |          |    |        |          |        |        |        |

| Bit    | 7     | 6        | 5  | 4      | 3        | 2      | 1      | 0      |

|        |       |          |    | PINMA  | SK[7:0]  |        |        |        |

| Access | W     | W        | W  | W      | W        | W      | W      | W      |

| Reset  | 0     | 0        | 0  | 0      | 0        | 0      | 0      | 0      |

#### Bit 31 – HWSEL: Half-Word Select

This bit selects the half-word field of a 32-PORT group to be reconfigured in the atomic write operation.

This bit will always read as zero.

|   | /alue | Description                                             |

|---|-------|---------------------------------------------------------|

| ( | )     | The lower 16 pins of the PORT group will be configured. |

|   | 1     | The upper 16 pins of the PORT group will be configured. |

#### Bit 30 – WRPINCFG: Write PINCFG

This bit determines whether the atomic write operation will update the Pin Configuration register (PINCFGy) or not for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits.

Writing '0' to this bit has no effect.

Writing '1' to this bit updates the configuration of the selected pins with the written WRCONFIG.DRVSTR, WRCONFIG.PULLEN, WRCONFIG.INEN, WRCONFIG.PMUXEN, and WRCONFIG.PINMASK values.

This bit will always read as zero.

| Value | Description                                                     |

|-------|-----------------------------------------------------------------|

| 0     | The PINCFGy registers of the selected pins will not be updated. |

| 1     | The PINCFGy registers of the selected pins will be updated.     |

## Bit 28 – WRPMUX: Write PMUX

This bit determines whether the atomic write operation will update the Peripheral Multiplexing register (PMUXn) or not for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits.

Writing '0' to this bit has no effect.

Writing '1' to this bit updates the pin multiplexer configuration of the selected pins with the written WRCONFIG. PMUX value.

This bit will always read as zero.

# 32.7 Register Summary

| Offset   | Name     | Bit Pos. |          |         |       |        |           |        |             |           |

|----------|----------|----------|----------|---------|-------|--------|-----------|--------|-------------|-----------|

| 0x00     |          | 7:0      | RUNSTDBY |         |       |        | MODE[2:0] |        | ENABLE      | SWRST     |

| 0x01     |          | 15:8     |          |         |       |        |           |        |             | IBON      |

| 0x02     | CTRLA    | 23:16    |          |         | DIPC  | D[1:0] |           |        | DOPO        | D[1:0]    |

| 0x03     |          | 31:24    |          | DORD    | CPOL  | CPHA   |           | FOR    | V[3:0]      |           |

| 0x04     |          | 7:0      |          | PLOADEN |       |        |           |        | CHSIZE[2:0] |           |

| 0x05     | CTRLB    | 15:8     | AMOD     | E[1:0]  | MSSEN |        |           |        | SSDE        |           |

| 0x06     | CIRLB    | 23:16    |          |         |       |        |           |        | RXEN        |           |

| 0x07     |          | 31:24    |          |         |       |        |           |        |             |           |

| 0x08     |          |          |          |         |       |        |           |        |             |           |

|          | Reserved |          |          |         |       |        |           |        |             |           |

| 0x0B     |          |          |          |         |       |        |           |        |             |           |

| 0x0C     | BAUD     | 7:0      |          |         |       | BAU    | D[7:0]    |        |             |           |

| 0x0D     |          |          |          |         |       |        |           |        |             |           |

|          | Reserved |          |          |         |       |        |           |        |             |           |

| 0x13     |          |          |          |         |       |        | -         |        |             |           |

| 0x14     | INTENCLR | 7:0      | ERROR    |         |       |        | SSL       | RXC    | TXC         | DRE       |

| 0x15     | Reserved |          |          |         |       |        | -         |        |             |           |

| 0x16     | INTENSET | 7:0      | ERROR    |         |       |        | SSL       | RXC    | TXC         | DRE       |

| 0x17     | Reserved |          |          |         |       |        | -         |        |             |           |

| 0x18     | INTFLAG  | 7:0      | ERROR    |         |       |        | SSL       | RXC    | TXC         | DRE       |

| 0x19     | Reserved |          |          |         |       |        |           |        |             |           |

| 0x1A     | STATUS   | 7:0      |          |         |       |        |           | BUFOVF |             |           |

| 0x1B     |          | 15:8     |          |         |       |        |           |        |             |           |

| 0x1C     |          | 7:0      |          |         |       |        |           | CTRLB  | ENABLE      | SWRST     |

| 0x1D     | SYNCBUSY | 15:8     |          |         |       |        |           |        |             |           |

| 0x1E     |          | 23:16    |          |         |       |        |           |        |             |           |

| 0x1F     |          | 31:24    |          |         |       |        |           |        |             |           |

| 0x20     |          |          |          |         |       |        |           |        |             |           |

|          | Reserved |          |          |         |       |        |           |        |             |           |

| 0x23     |          |          |          |         |       |        |           |        |             |           |

| 0x24     |          | 7:0      |          |         |       | ADD    | R[7:0]    |        |             |           |

| 0x25     | ADDR     | 15:8     |          |         |       |        |           |        |             |           |

| 0x26     |          | 23:16    |          |         |       | ADDRM  | IASK[7:0] |        |             |           |

| 0x27     |          | 31:24    |          |         |       | D.17   | A[7:0]    |        |             |           |

| 0x28     | DATA     | 7:0      |          |         |       | DAL    | A[7:0]    |        |             | DATAIOO   |

| 0x29     |          | 15:8     |          |         |       |        |           |        |             | DATA[8:8] |

| 0x2A     | Deecrard |          |          |         |       |        |           |        |             |           |

| <br>0x2F | Reserved |          |          |         |       |        |           |        |             |           |

|          | DRCCTPI  | 7:0      |          |         |       |        |           |        |             | DRCSTOR   |

| 0x30     | DBGCTRL  | 7:0      |          |         |       |        |           |        |             | DBGSTOP   |

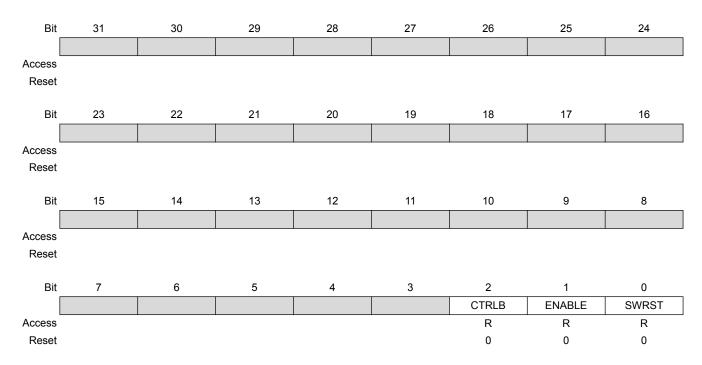

Name:

SYNCBUSY

Offset:

0x1C [ID-00000e74]

Reset:

0x00000000

Property:

## Bit 2 – CTRLB: CTRLB Synchronization Busy

Writing to the CTRLB when the SERCOM is enabled requires synchronization. Ongoing synchronization is indicated by SYNCBUSY.CTRLB=1 until synchronization is complete. If CTRLB is written while SYNCBUSY.CTRLB=1, an APB error will be generated.

| Value | Description                        |

|-------|------------------------------------|

| 0     | CTRLB synchronization is not busy. |

| 1     | CTRLB synchronization is busy.     |

## Bit 1 – ENABLE: SERCOM Enable Synchronization Busy

Enabling and disabling the SERCOM (CTRLA.ENABLE) requires synchronization. Ongoing synchronization is indicated by SYNCBUSY.ENABLE=1 until synchronization is complete.

Writes to any register (except for CTRLA.SWRST) while enable synchronization is on-going will be discarded and an APB error will be generated.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Enable synchronization is not busy. |

| 1     | Enable synchronization is busy.     |

## Bit 0 – SWRST: Software Reset Synchronization Busy

Resetting the SERCOM (CTRLA.SWRST) requires synchronization. Ongoing synchronization is indicated by SYNCBUSY.SWRST=1 until synchronization is complete.

Writes to any register while synchronization is on-going will be discarded and an APB error will be generated.

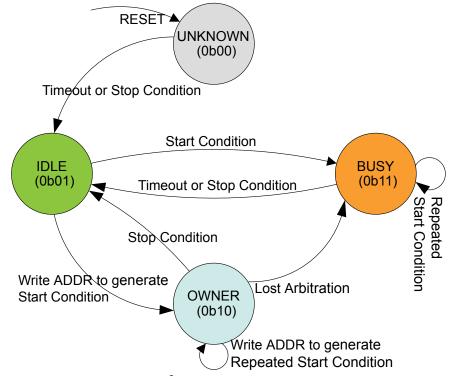

Figure 33-4. Bus State Diagram

The bus state machine is active when the  $I^2C$  master is enabled.

After the I<sup>2</sup>C master has been enabled, the bus state is UNKNOWN (0b00). From the UNKNOWN state, the bus will transition to IDLE (0b01) by either:

- Forcing by writing 0b01 to STATUS.BUSSTATE

- A stop condition is detected on the bus

- If the inactive bus time-out is configured for SMBus compatibility (CTRLA.INACTOUT) and a timeout occurs.

Note: Once a known bus state is established, the bus state logic will not re-enter the UNKNOWN state.

When the bus is IDLE it is ready for a new transaction. If a start condition is issued on the bus by another I<sup>2</sup>C master in a multi-master setup, the bus becomes BUSY (0b11). The bus will re-enter IDLE either when a stop condition is detected, or when a time-out occurs (inactive bus time-out needs to be configured).

If a start condition is generated internally by writing the Address bit group in the Address register (ADDR.ADDR) while IDLE, the OWNER state (0b10) is entered. If the complete transaction was performed without interference, i.e., arbitration was not lost, the I<sup>2</sup>C master can issue a stop condition, which will change the bus state back to IDLE.

However, if a packet collision is detected while in OWNER state, the arbitration is assumed lost and the bus state becomes BUSY until a stop condition is detected. A repeated start condition will change the bus state only if arbitration is lost while issuing a repeated start.

**Note:** Violating the protocol may cause the I<sup>2</sup>C to hang. If this happens it is possible to recover from this state by a software reset (CTRLA.SWRST='1').

Related Links CTRLA

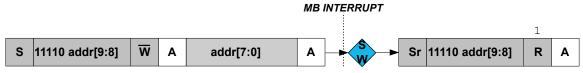

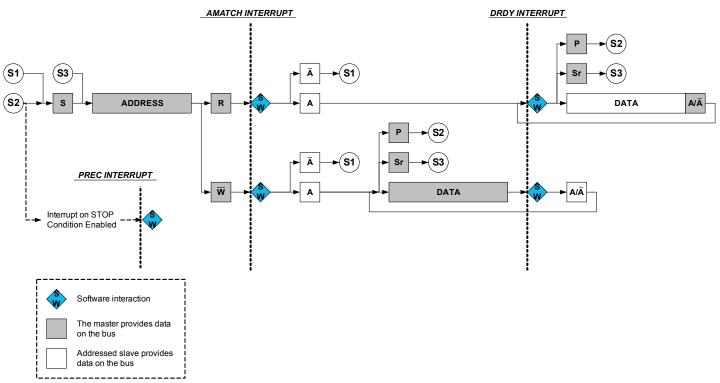

## Figure 33-9. 10-bit Address Transmission for a Read Transaction

This implies the following procedure for a 10-bit read operation:

- 1. Write the 10-bit address to ADDR.ADDR[10:1]. ADDR.TENBITEN must be '1', the direction bit (ADDR.ADDR[0]) must be '0' (can be written simultaneously with ADDR).

- 2. Once the Master on Bus interrupt is asserted, Write ADDR[7:0] register to '11110 address[9:8] 1'. ADDR.TENBITEN must be cleared (can be written simultaneously with ADDR).

- 3. Proceed to transmit data.

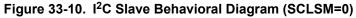

## 33.6.2.5 I<sup>2</sup>C Slave Operation

The I<sup>2</sup>C slave is byte-oriented and interrupt-based. The number of interrupts generated is kept at a minimum by automatic handling of most events. The software driver complexity and code size are reduced by auto-triggering of operations, and a special smart mode, which can be enabled by the Smart Mode Enable bit in the Control A register (CTRLA.SMEN).

The I<sup>2</sup>C slave has two interrupt strategies.

When SCL Stretch Mode bit (CTRLA.SCLSM) is '0', SCL is stretched before or after the acknowledge bit. In this mode, the I<sup>2</sup>C slave operates according to I<sup>2</sup>C Slave Behavioral Diagram (SCLSM=0). The circles labelled "Sn" (S1, S2..) indicate the nodes the bus logic can jump to, based on software or hardware interaction.

This diagram is used as reference for the description of the I<sup>2</sup>C slave operation throughout the document.

In the second strategy (CTRLA.SCLSM=1), interrupts only occur after the ACK bit is sent as shown in Slave Behavioral Diagram (SCLSM=1). This strategy can be used when it is not necessary to check

# SAM C20/C21

| Bit    | 31  | 30  | 29  | 28   | 27             | 26  | 25  | 24  |

|--------|-----|-----|-----|------|----------------|-----|-----|-----|

|        |     |     |     |      |                |     |     |     |

| Access |     |     |     |      |                |     |     |     |

| Reset  |     |     |     |      |                |     |     |     |

|        |     |     |     |      |                |     |     |     |

| Bit    | 23  | 22  | 21  | 20   | 19             | 18  | 17  | 16  |

|        |     |     |     |      |                |     |     |     |

| Access |     |     |     |      |                |     |     |     |

| Reset  |     |     |     |      |                |     |     |     |

|        |     |     |     |      |                |     |     |     |

| Bit    | 15  | 14  | 13  | 12   | 11             | 10  | 9   | 8   |

|        |     |     |     | RBSA | [15:8]         |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W            | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0              | 0   | 0   | 0   |

|        |     |     |     |      |                |     |     |     |

| Bit    | 7   | 6   | 5   | 4    | 3              | 2   | 1   | 0   |

|        |     |     |     | RBS  | <b>A</b> [7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W            | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0              | 0   | 0   | 0   |

## Bits 15:0 – RBSA[15:0]: Rx Buffer Start Address

Configures the start address of the Rx Buffers section in the Message RAM. Also used to reference debug message A,B,C. When the CAN module addresses the Message RAM it addresses 32-bit words, not single bytes. The configurable start addresses are 32-bit word addresses, i.e. only bits 15 to 2 are evaluated, the two least significant bits are ignored. Bits 1 to 0 will always be read back as "00".

## 34.8.31 Rx FIFO 1 Configuration

This register is write-restricted and only writable if bit fields CCCR.CCE = 1 and CCCR.INIT = 1.

Name:RXF1COffset:0xB0 [ID-0000a4bb]Reset:0x00000000Property:Write-restricted

- Dead-time insertion

- Swap

- Pattern generation

See also Figure 36-1.

The output matrix (OTMX) can distribute and route out the TCC waveform outputs across the port pins in different configurations, each optimized for different application types. The Dead-Time Insertion (DTI) unit splits the four lower OTMX outputs into two non-overlapping signals: the non-inverted low side (LS) and inverted high side (HS) of the waveform output with optional dead-time insertion between LS and HS switching. The SWAP unit can swap the LS and HS pin outputs, and can be used for fast decay motor control.

The pattern generation unit can be used to generate synchronized waveforms with constant logic level on TCC UPDATE conditions. This is useful for easy stepper motor and full bridge control.

The non-recoverable fault module enables event controlled fault protection by acting directly on the generated waveforms of the timer/counter compare channel outputs. When a non-recoverable fault condition is detected, the output waveforms are forced to a preconfigured value that is safe for the application. This is typically used for instant and predictable shut down and disabling high current or voltage drives.

The count event sources (TCE0 and TCE1) are shared with the non-recoverable fault extension. The events can be optionally filtered. If the filter options are not used, the non-recoverable faults provide an immediate asynchronous action on waveform output, even for cases where the clock is not present. For further details on how to configure asynchronous events routing, refer to section *EVSYS – Event System*.

## **Related Links**

EVSYS – Event System

## 36.6.2 Basic Operation

#### 36.6.2.1 Initialization

The following registers are enable-protected, meaning that they can only be written when the TCC is disabled(CTRLA.ENABLE=0):

- Control A (CTRLA) register, except Run Standby (RUNSTDBY), Enable (ENABLE) and Software Reset (SWRST) bits

- Recoverable Fault n Control registers (FCTRLA and FCTRLB)

- Waveform Extension Control register (WEXCTRL)

- Drive Control register (DRVCTRL)

- Event Control register (EVCTRL)

Enable-protected bits in the CTRLA register can be written at the same time as CTRLA.ENABLE is written to '1', but not at the same time as CTRLA.ENABLE is written to '0'. Enable-protection is denoted by the "Enable-Protected" property in the register description.

Before the TCC is enabled, it must be configured as outlined by the following steps:

- 1. Enable the TCC bus clock (CLK\_TCCx\_APB).

- 2. If Capture mode is required, enable the channel in capture mode by writing a '1' to the Capture Enable bit in the Control A register (CTRLA.CPTEN).

Optionally, the following configurations can be set before enabling TCC:

- 1. Select PRESCALER setting in the Control A register (CTRLA.PRESCALER).

- 2. Select Prescaler Synchronization setting in Control A register (CTRLA.PRESCSYNC).

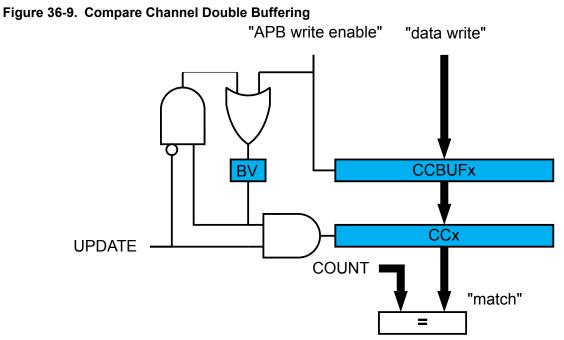

Both the registers (PATT/WAVE/PER/CCx) and corresponding buffer registers (PATTBUF/WAVEBUFV/ PERBUF/CCBUFx) are available in the I/O register map, and the double buffering feature is not mandatory. The double buffering is disabled by writing a '1' to CTRLSET.LUPD.

**Note:** In NFRQ, MFRQ or PWM down-counting counter mode (CTRLBSET.DIR=1), when double buffering is enabled (CTRLBCLR.LUPD=1), PERBUF register is continuously copied into the PER independently of update conditions.

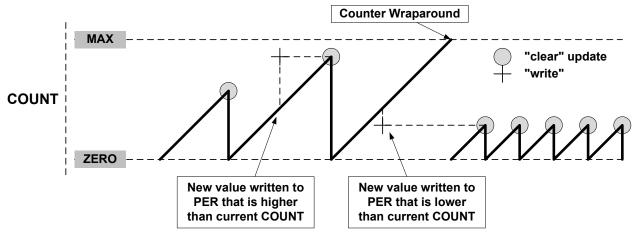

# Changing the Period

The counter period can be changed by writing a new Top value to the Period register (PER or CC0, depending on the waveform generation mode), any period update on registers (PER or CCx) is effective after the synchronization delay, whatever double buffering enabling is.

| Figure 36-10. Unbuffered Single-Slope Up-Counting Operation | Figure 36-10. | Unbuffered | Single-Slope | <b>Up-Counting</b> | Operation |

|-------------------------------------------------------------|---------------|------------|--------------|--------------------|-----------|

|-------------------------------------------------------------|---------------|------------|--------------|--------------------|-----------|

- 2.2. Select the required voltage for the internal voltage reference INTREF by writing to the Voltage Reference Selection bits (SUPC.VREF.SEL). The required value can be found in the Electrical Characteristics.

- 2.3. Enable routing INTREF to the ADC by writing a '1' to the Voltage Reference Output Enable bit (SUPC.VREF.VREFOE).

- 3. Configure the ADC:

- 3.1. Select the internal voltage reference INTREF as ADC reference voltage by writing to the Reference Control register (ADC.REFCTRL.REFSEL).

- 3.2. Select the temperature sensor vs. internal GND as input by writing TEMP and GND to the positive and negative MUX Input Selection bit fields (ADC.INPUTCTRL.MUXNEG and .MUXPOS, respectively).

- 3.3. Configure the remaining ADC parameters according to the Electrical Characteristics.

- 3.4. Enable the ADC and acquire a value, ADC<sub>m</sub>.

## **Calculation Parameter Values**

The temperature sensor behavior is linear, but it is sensitive to several parameters such as the internal voltage reference - which itself depends on the temperature. To take this into account, each device contains a Temperature Log row with individual calibration data measured and written during the production tests. These calibration values are read by software to infer the most accurate temperature readings possible.

The Temperature Log Row basically contains the following parameter set for two different temperatures ("ROOM" and "HOT"):

- Calibration temperatures in °C. One at room temperature temp<sub>R</sub>, one at a higher temperature temp<sub>H</sub>:

- ROOM\_TEMP\_VAL\_INT and ROOM\_TEMP\_VAL\_DEC contain the measured temperature at room insertion, *temp*<sub>R</sub>, in °C, separated in integer and decimal value.

Example: For ROOM\_TEMP\_VAL\_INT=0x19=25 and ROOM\_TEMP\_VAL\_DEC=2, the measured temperature at room insertion is 25.2°C.

- HOT\_TEMP\_VAL\_INT and HOT\_TEMP\_VAL\_DEC contain the measured temperature at hot insertion, *temp*<sub>H</sub>, in °C. The integer and decimal value are also separated.

- For each temperature, the corresponding sensor value at the ADC in 12-bit, ADC<sub>R</sub> and ADC<sub>H</sub>:

- ROOM\_ADC\_VAL contains the 12-bit ADC value, ADC<sub>R</sub>, corresponding to *temp*<sub>R</sub>. Its conversion to Volt is denoted V<sub>ADCR</sub>.

- HOT\_ADC\_VAL contains the 12-bit ADC value, ADC<sub>H</sub>, corresponding to *temp*<sub>H</sub>. Its conversion to Volt is denoted V<sub>ADCH</sub>.

- Actual reference voltages at each calibration temperature in Volt, INT1V<sub>R</sub> and INT1V<sub>H</sub>, respectively:

- ROOM\_INT1V\_VAL is the 2's complement of the internal 1V reference value at *temp*<sub>R</sub>: INT1V<sub>R</sub>.

- HOT\_INT1V\_VAL is the 2's complement of the internal 1V reference value at  $temp_{H}$ : INT1V<sub>H</sub>.

- Both ROOM\_INT1V\_VAL and HOT\_INT1V\_VAL values are centered around 1V with a 0.001V step. In other words, the range of values [0,127] corresponds to [1V, 0.873V] and the range of values [-1, -127] corresponds to [1.001V, 1.127V]. INT1V == 1 (VAL/1000) is valid for both ranges.

## Calculating the Temperature by Linear Interpolation

Using the data pairs (*temp*<sub>R</sub>,  $V_{ADCR}$ ) and (*temp*<sub>H</sub>,  $V_{ADCH}$ ) for a linear interpolation, we have the following equation:

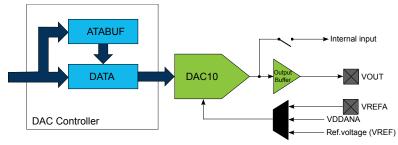

# 41. DAC – Digital-to-Analog Converter

# 41.1 Overview

The Digital-to-Analog Converter (DAC) converts a digital value to a voltage. The DAC has one channel with 10-bit resolution, and it is capable of converting up to 350,000 samples per second (350ksps).

# 41.2 Features

- DAC with 10-bit resolution

- Up to 350ksps conversion rate

- Hardware support for 14-bit using dithering

- Multiple trigger sources

- High-drive capabilities

- Output can be used as input to the Analog Comparator (AC), ADC or SDADC

- DMA support

# 41.3 Block Diagram

## Figure 41-1. DAC Block Diagram

# 41.4 Signal Description

| Signal Name | Туре          | Description        |

|-------------|---------------|--------------------|

| VOUT        | Analog output | DAC output         |

| VREFA       | Analog input  | External reference |

## **Related Links**

I/O Multiplexing and Considerations

# 41.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

## 41.5.1 I/O Lines

Using the DAC Controller's I/O lines requires the I/O pins to be configured using the port configuration (PORT).

## 41.5.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except the following registers:

- Interrupt Flag Status and Clear (INTFLAG) register

- Data Buffer (DATABUF) register

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger

#### **Related Links**

PAC - Peripheral Access Controller

## 41.5.9 Analog Connections

The DAC has one output pin (VOUT) and one analog input pin (VREFA) that must be configured first.

When internal input is used, it must be enabled before DAC Controller is enabled.

# 41.6 Functional Description

#### 41.6.1 Principle of Operation

The DAC converts the digital value located in the Data register (DATA) into an analog voltage on the DAC output (VOUT).

A conversion is started when new data is written to the Data register. The resulting voltage is available on the DAC output after the conversion time. A conversion can also be started by input events from the Event System.

#### 41.6.2 Basic Operation

#### 41.6.2.1 Initialization

The following registers are enable-protected, meaning they can only be written when the DAC is disabled (CTRLA.ENABLE is zero):

- Control B register (CTRLB)

- Event Control register (EVCTRL)

Enable-protection is denoted by the Enable-Protected property in the register description.

Before enabling the DAC, it must be configured by selecting the voltage reference using the Reference Selection bits in the Control B register (CTRLB.REFSEL).

#### 41.6.2.2 Enabling, Disabling and Resetting

The DAC Controller is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The DAC Controller is disabled by writing a '0' to CTRLA.ENABLE.

The DAC Controller is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the DAC will be reset to their initial state, and the DAC Controller will be disabled. Refer to the CTRLA register for details.

#### 41.6.2.3 Enabling the Output Buffer

To enable the DAC output on the  $V_{OUT}$  pin, the output driver must be enabled by writing a one to the External Output Enable bit in the Control B register (CTRLB.EOEN).